#### Introduction

The LR3220 Read-Write Buffer enhances the performance of MIPS architecture-based systems by buffering write and read operations. Using the Read-Write Buffer, the system can perform memory write operations at the cycle rate of the processor, instead of stalling the processor to write data to memory. On memory read operations, the system uses the Read-Write Buffer to pass the read address to main memory, and latch the read data from memory. The Read-Write Buffer generates parity, and then passes the data and parity to the processor. A single LR3220 provides six-deep write buffering and one level of read buffering for 32 bits of address and 32 bits of data. It operates at the system clock rate, and is available at 25 and 33.33 MHz to support the requirements of LR3000-based systems.

#### **LR3220 Die**

#### **Features**

- Combines the functionality of four LR3020 Write Buffers

- Minimizes additional loading on the address and data buses with on-chip data and address latches for read operations

- Supports big endian and little endian byteorder addressing

- Uses byte mask outputs to ease system design

- Performs block-mode conflict detection for block sizes of eight words or less

- Offers separate enable signals for all address and data buses

- Supports fast page-mode writes for 1MBit DRAM-based memory implementations

- Provides six-deep write buffering of data and addresses

- Supports two operating modes:

- 1) LR3000 mode

- compatible with the LR3000's staggered Address and Tag bus timing - decodes AccTyp [1:0] and AdrLo [1:0] inputs for byte ordering

- 2) Harvard mode

- uses synchronous address latching on the rising edge of the clock

- -uses byte mask inputs for byte ordering

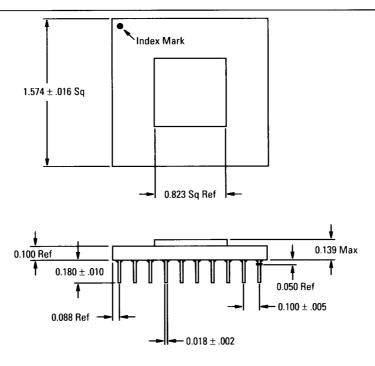

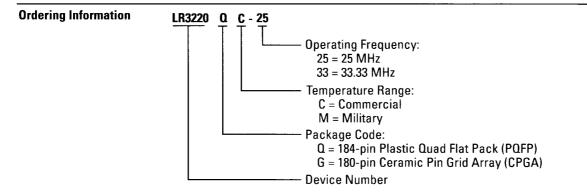

- Offered in both 180-pin CPGA and compact 184-pin PQFP packages

#### **Overview of Operation**

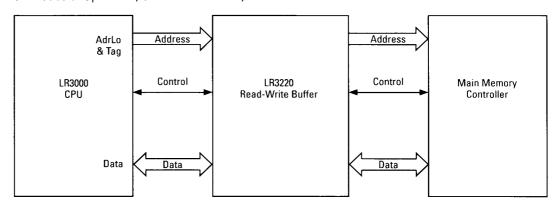

Figure 1 shows an LR3220 in an LR3000-based system. Data and address transfers between the processor and the Read-Write Buffer occur synchronously at the cycle rate of the processor. The Read-Write Buffer and main memory controller exchange handshake signals to coordinate the transfer of data between the LR3220 and main memory. Refer to the LR3220/CPU Interface and LR3220/Main Memory Interface sections, below, for more specific information on these interfaces.

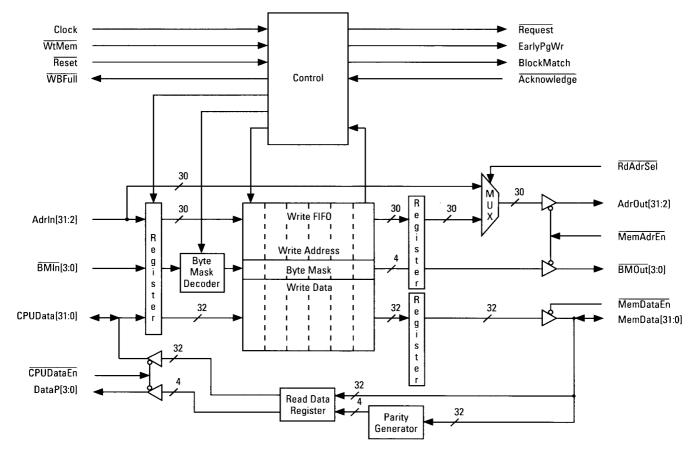

Figure 2 presents a functional block diagram of the LR3220. For write operations, the LR3220 latches the write address, data, and byte mask information from the processor, and decodes the byte mask bits if appropriate. The Read-Write Buffer FIFO has six ranks, to hold up to six address/data pairs while it waits to pass the data to main memory. For read operations, the Read-Write Buffer passes the read address from the processor to the memory controller, latches the read data from memory,

©1989, 1990 LSI Logic Corporation. All rights reserved.

September 1990

Order Number LR3220

**Overview of Operation** (Continued)

generates parity, and passes the data and parity to the processor. Refer to the discussions on Modes of Operation, Conflict Resolution,

Write Timing, and Read Timing, below, for more details on read and write operations.

Figure 1. The LR3220 in an LR3000-based System

Figure 2. The LR3220 Functional Block Diagram

#### LR3220 Read-Write Buffer Preliminary

#### **Modes of Operation**

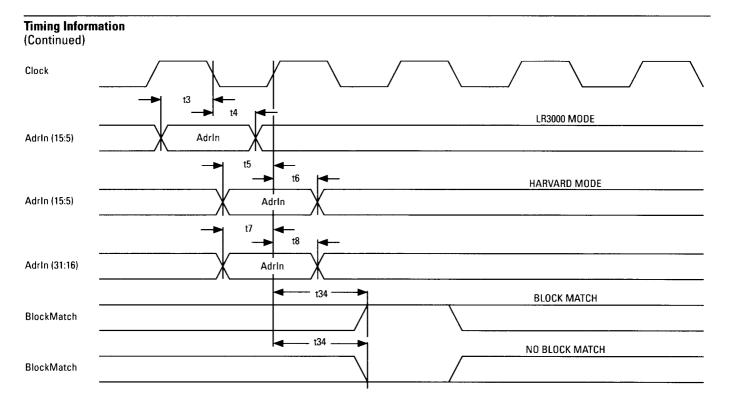

The LR3220 supports two operating modes, LR3000 mode and Harvard mode, selectable at reset. The modes differ in two ways: processor interface timing and byte mask bit interpretation, as explained below. Note that the selected mode only effects transfers between the LR3220 and the processor during write operations. Read transfers, and transfers between the LR3220 and main memory, are identical in both modes.

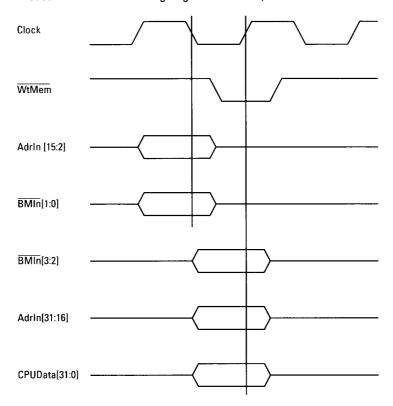

With regard to processor interface timing, in LR3000 mode the LR3220 latches AdrIn[15:2] and BMIn[1:0] into the input staging register on the falling edge of Clock, and AdrIn[31:16], BMIn[3:2], and CPUData on the rising edge of Clock, to correspond with the staggered timing on the LR3000's AdrLo, Tag, AccTyp, and Data

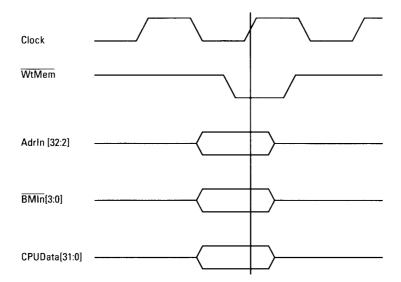

buses. In Harvard mode, the Read-Write Buffer latches the Adrln, BMIn, and CPUData buses on the rising edge of the Clock.

For byte mask bit interpretation, in LR3000 mode the Read-Write Buffer accepts AdrLo[1:0] and AccTyp[1:0] from the LR3000 on the byte mask input lines, BMIn[3:0]. The LR3220 then combines these bits with the appropriate endian byte ordering (big or little) determined during reset, translates them into the byte mask output bits, and stores them with the write data in the buffer ranks. In Harvard mode, the LR3220 stores BMIn[3:0] unmodified in the ranks, for use as the byte mask output bits. A later section of this data sheet, "Resetting the LR3220", discusses how to define the operating mode at reset time.

#### **Pin Description**

This section describes the LR3220 interface signals.

#### Clock

This signal from the processor synchronizes data transfers. In LR3000 mode, where Clock is an inverted version of the LR3000's SysOut signal, the Read-Write Buffer uses the trailing edge of the Clock to latch the contents of the AdrLo bus, and uses the leading edge to latch the contents of the Data and Tag buses. In Harvard mode, the leading edge of the Clock must latch the address, byte mask bits, and data. In both modes, the LR3220 uses the leading edge of Clock to latch data during memory read cycles.

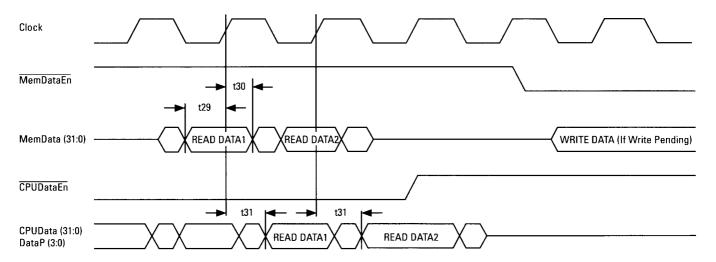

#### **CPUData[31:0]**

These 32 bidirectional data lines connect the processor's data bus with the Read-Write Buffer.

#### DataP[3:0]

The LR3220 generates these four parity bits on read operations. In LR3000-based systems, these lines connect directly to the LR3000's DataP[3:0] signals. Note that the Read-Write Buffer does not store the parity; it generates it for read operations and ignores it on write operations.

#### Adrln[31:2]

These 30 signals are the Read-Write Buffer's address inputs. In LR3000-based systems, the LR3000's AdrLo and Tag buses provide the LR3220 AdrIn[31:2] input signals.

#### **BMIn**[3:0]

The byte mask input signals define the byte ordering for the input data. In LR3000 mode, the

LR3000's AdrLo[1:0] and AccTyp[1:0] outputs provide the byte-mask input, and the LR3220 decodes these signals and stores them as the byte mask. In Harvard mode, the Read-Write Buffer simply stores the byte mask inputs.

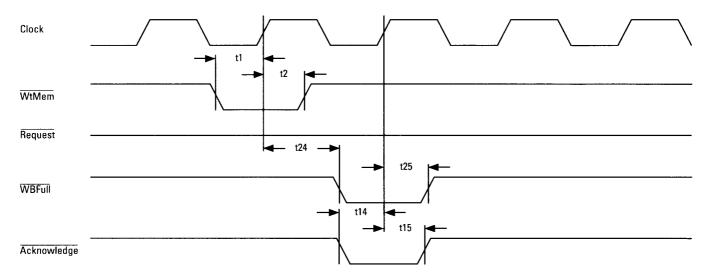

#### WtMem

The processor should assert this input whenever the processor performs a store operation. In LR3000-based systems, WtMem connects to the LR3000's MemWr output.

#### Request

When the LR3220 has an address/data pair available for a memory write, it asserts this signal to request a write operation to main memory. In an LR3000-based system, Request may also connect to the CpCond0 input of the LR3000. Because the LR3220 asserts Request only when it contains a valid address/data pair, system software can use Request to determine whether a previous write operation, for example a write to an I/O device, is complete before initiating a read to that device.

#### **WBFull**

The LR3220 asserts this signal when it cannot accept any more data; that is, when all six address/data registers in the buffer are occupied. If a processor attempts a write when WBFull is asserted, the LR3220 ignores it. For LR3000-based systems, WBFull connects to WrBusy. If the LR3000 needs to store data while WBFull is asserted, it performs a write busy stall until WBFull is deasserted.

#### AdrOut[31:2]

These 30 address lines are output from the LR3220 to the memory system address bus.

:

### Pin Description (Continued)

#### MemData[31:0]

These 32 bidirectional data lines connect the LR3220 to the memory system data bus.

#### **BMOut**[3:0]

These byte mask output signals identify the valid data bytes for the memory system during memory write operations.

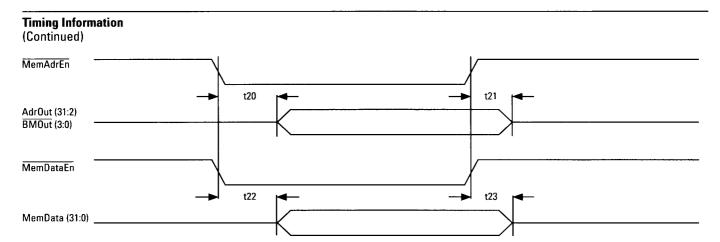

#### MemAdrEn

The memory system asserts this input to enable the Read-Write Buffer's AdrOut and BMOut bus outputs.

#### MemDataEn

The memory system asserts this input to enable the Read-Write Buffer's MemData bus outputs.

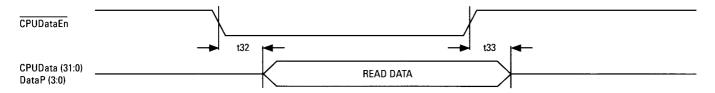

#### **CPUDataEn**

The processor uses this input to control the LR3220's CPUData and DataP buses. When the processor asserts this signal, the LR3220 sends read data and the generated parity to the processor. In LR3000-based <a href="mailto:systems">systems</a>, CPUDataEn connects to the LR3000's XEn signal.

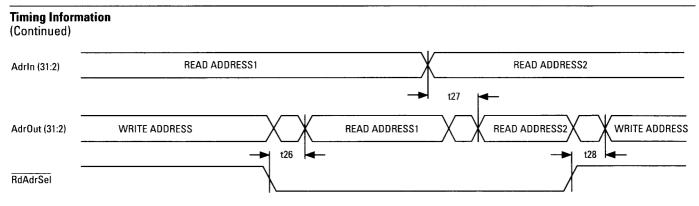

#### **RdAdrSel**

This input selects between the read address and the current write address. When the main memory controller asserts RdAdrSel, the read address on the processor's address bus, which is available at the AdrIn[31:2] inputs of the LR3220, becomes available on the LR3220 AdrOut bus. When the main memory controller deasserts RdAdrSel, the current write address becomes available on AdrOut. In either case, the memory system must assert MemAdrEn to enable the AdrOut bus.

#### **Acknowledge**

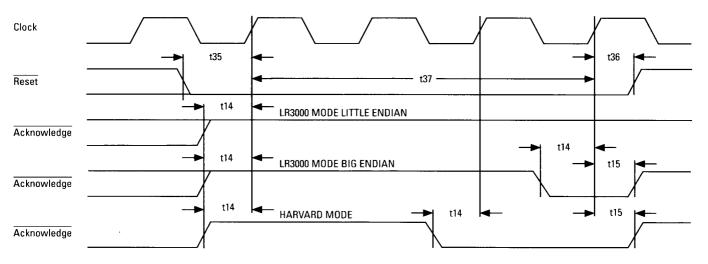

The main memory system asserts this signal when it has captured the data presented by the LR3220. The LR3220 also uses this signal during reset to determine the operating mode of the Read-Write Buffer: big or little endian LR3000 mode, or Harvard mode, as illustrated in the reset timing diagram of Figure 18.

#### EarlyPgWr

For systems with a 1MBit DRAM-based memory implementation, this output signals to the memory controller that the next write operation is to the same memory page as the current write. To check the page address, the LR3220 compares the FIFO's next-write-address bits 31 through 12 with the current-write-address bits 31 through 12. If no write is currently active, EarlyPgWr signals whether or not a page write will occur during the next write cycle, regardless of how long ago the previous write occurred. EarlyPgWr is undefined during the cycle immediately preceding the first write operation after a reset.

#### **BlockMatch**

This output signals to the memory controller that the processor has requested a read operation at a memory location for which a write operation is pending. The LR3220 asserts this output when address input bits Adrln[31:5] match address bits 31 through 5 of any valid address/data pair in the Read-Write Buffer.

#### Reset

This signal initializes the Read-Write Buffer to a known state and clears the contents of all of its registers.

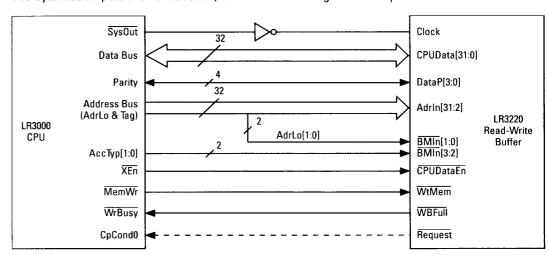

#### LR3220/CPU Interface

Figure 3 illustrates the interface between the LR3000 CPU and the LR3220. A single LR3220 implements the full 32-bit, buffered interface. The AdrLo bus and Tag bus bits from the processor combine to form the 32-bit physical address (AdrIn[31:2] and \$\overline{BMIn}[1:0]\$) for the LR3220. Thirty-two bits of data and two access type bits from the processor become the CPUData[31:0] and \$\overline{BMIn}[3:2]\$ inputs to the LR3220. On write operations, the LR3220 does not store or pass to main memory the processor's parity bits. On read operations, however, the Read-Write Buffer generates parity and passes it on to the processor.

Later sections in this datasheet provide an overview of the write timing for both the

LR3000 and Harvard operating modes and a discussion of the input byte mask decoding for LR3000 mode.

In LR3000 mode, the LR3220 latches AdrLo[15:0], the 16 low-order address bits from the processor, on the trailing edge of the Clock signal. The 16 high-order address bits (Tag[31:16]), the data bits (D[31:0]), and the access type bits (AccTyp[1:0]) are latched on the rising edge of the Clock. AdrLo[1:0] and AccTyp[1:0] from the LR3000 are input on the BMIn[3:0] lines and are decoded by the LR3220 as defined in Table 1. This table shows how the byte masks are decoded, based both on these inputs and on the endian byte ordering specified at reset time.

## **LR3220 Read-Write Buffer**Preliminary

LR3220/CPU Interface (Continued)

In Harvard mode, the LR3220 latches the complete Adrln bus on the rising edge of Clock, along with the data and byte mask signals. The byte mask inputs are not decoded, but

they indicate which bytes are valid. The LR3220 stores the BMIn[3:0] inputs with the address/data pairs, and then passes them to memory during the write operation.

Figure 3. LR3000 to LR3220 Interface

Table 1. Byte Mask Decoding in LR3000 Mode

| Byte I        | Mask In | puts        |    | Byte Mask Outputs |            |                    |               |       |            |                  |   |  |  |

|---------------|---------|-------------|----|-------------------|------------|--------------------|---------------|-------|------------|------------------|---|--|--|

| 3             | 2       | 1           | 0  | 3                 | 2          | 1                  | 0             | 3     | 2          | 1                | 0 |  |  |

| (AccTyp[1:0]) |         | (AdrLo[1:0] | 1) | 31                | (Big-En    | dian) <sup>1</sup> | 0             | 31    | ittle-Endi | an) <sup>1</sup> | C |  |  |

| 1<br>(word)   | 1       | 0           | 0  | <b>4</b>          |            | 建设建                | <b>15</b> 200 |       | 1 2        |                  |   |  |  |

| 1             | 0       | 0           | 0  | 0                 | 1 1        | 2                  |               |       | 2          | 1                | 0 |  |  |

| (tri-byte)    |         | 0           | 1  |                   | 7.5        | 7 - 2              | 17.5          | 3     |            | ,44 July         |   |  |  |

| 0             | 1       | 0           | 0  |                   | <b>基本国</b> |                    |               |       | I          | I V              | 0 |  |  |

| (halfwor      | d)      | 1           | 0  |                   |            | 2                  | 8             | \$8.0 | 1 2-       |                  |   |  |  |

| 0             | 0       | 0           | 0  | <b>12.0</b>       |            |                    |               |       | 1          |                  | 6 |  |  |

| (byte)        |         | 0           | 1  |                   | 1          |                    |               |       |            |                  |   |  |  |

|               |         | 1           | 0  |                   | 1          | 72                 |               |       | 72/        |                  |   |  |  |

|               |         | 1           | 1  |                   |            | 1                  | 8             | 3     |            |                  | i |  |  |

#### Notes

- 1. Determined at reset.

- 2. Indicates BMOut asserted (LOW).

#### LR3220 Read-Write Buffer Preliminary

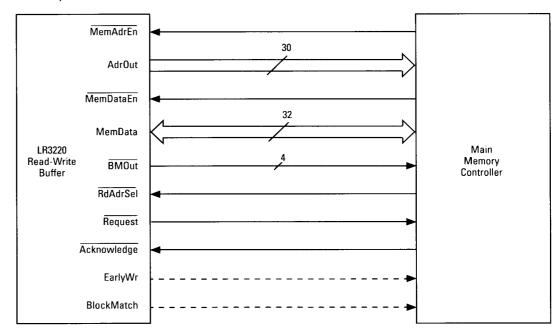

#### LR3220/Main Memory Interface

Figure 4 shows the signals which comprise the LR3220 interface to main memory. The interface is essentially decoupled from the LR3220/processor interface and is identical in both LR3000 and Harvard modes. The handshaking signals between the LR3220 and main memory have no direct connection with the LR3220/processor interface.

The byte mask outputs, BMOut[3:0], indicate which bytes of the 32-bit MemData bus are

involved in the current transfer, to simplify external hardware design. Specifically, they indicate whether the transfer is a byte, halfword, tri-byte, or word transfer. The byte mask signals indicate valid data as follows:

BMOut3 applies to MemData[31:24]

BMOut2 applies to MemData[23:16]

BMOut1 applies to MemData[15:8]

BMOut0 applies to MemData[7:0]

Figure 4. Main Memory to LR3220 Interface

#### **Conflict Resolution**

A conflict occurs when the processor requests a memory read operation from a memory location for which a write is pending; completing the read operation prior to the write would result in stale data being returned to the processor.

When the processor puts an address on the system address bus, the LR3220 checks for potential conflicts by comparing the 27 high-order address bits from the processor, available at Adrln[31:5], with the corresponding address bits of the address/data pairs currently stored in the ranks. If these high-order address bits match, then the two addresses are aligned within the same eight-word block in memory and the LR3220 asserts BlockMatch to signal the potential conflict to the memory controller. If the address bits do not match, then there is no conflict.

When it detects a conflict, the memory controller should hold off the read operation until it has written the conflicting data to memory and the LR3220 has deasserted BlockMatch; then it can complete the memory read operation. Because the LR3220 performs address matching on eight-word-block boundaries, systems which support multiple-word transfers can use BlockMatch to ensure that memory reads of up to eight-word blocks do not result in stale data being returned to the processor. Note that although the LR3220 asserts BlockMatch whenever an address match occurs, the memory controller should only sample BlockMatch during read operations to detect conflicts; no conflicts occur on write operations.

#### LR3220 Read-Write Buffer Preliminary

#### **Write Timing**

Transfers between the processor and the buffer occur synchronously at the cycle rate of the processor. As mentioned previously, in LR3000 mode the LR3220 uses the inverted SysOut signal from the LR3000 as the Clock to latch the address and data information into the buffer's six address/data ranks.

Figure 5 illustrates the relative write timing in LR3000 mode. On the trailing edge of the Clock,

the LR3220 latches the low-order address bits (AdrIn[15:2] and BMIn[1:0]) into its input staging registers. On the rising edge of Clock, the LR3220 latches the high-order address and byte mask bits (AdrIn[31:16] and BMIn[3:2]) and the contents of the data bus into the input staging registers. When the processor asserts WtMem, the assembled address/data pair in the input staging registers is written into one of the LR3220's six address/data ranks.

Figure 5. Processor to LR3220 Write Timing in LR3000 Mode

Figure 6 shows the relative write timing in Harvard mode. The LR3220 latches the address, data, and byte mask inputs on the rising edge of the Clock.

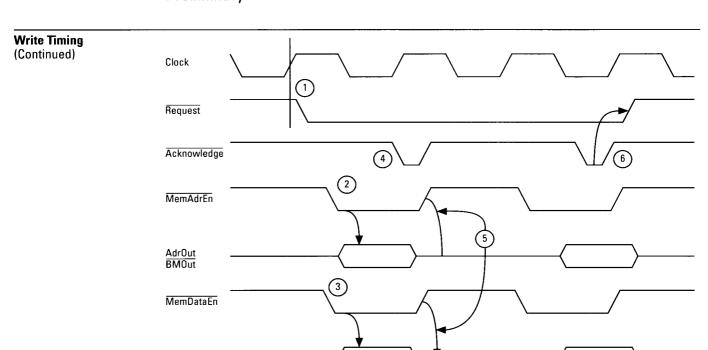

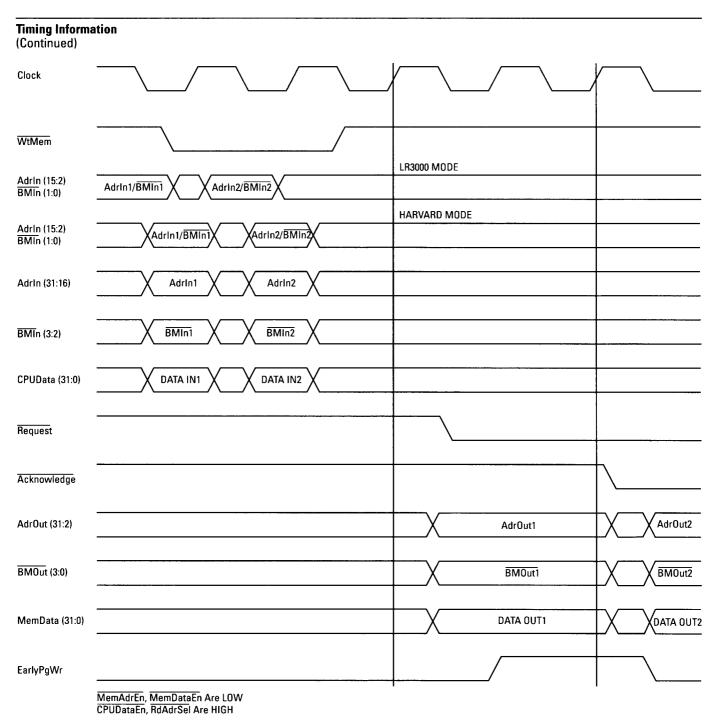

Figure 7 illustrates the data transfer timing from the LR3220 to the main memory system; this timing is identical for both the LR3000 and the Harvard operating modes. The sequence is as follows:

1. When the LR3220 has an address/data pair to transfer to the memory system, it asserts the Request signal.

- 2. When the memory system is ready to handle the address and byte mask, it asserts MemAdrEn to enable the LR3220's address and byte mask outputs onto the system address bus.

- 3. When the memory system is ready to handle the data, it asserts MemDataEn to enable the LR3220's data bus outputs onto the system data bus.

- 4. When the memory system no longer requires the Read-Write Buffer's current address and data outputs, it asserts the Acknowledge

### Write Timing (Continued)

signal. The LR3220 responds to this signal by discarding the address/data pair that was just output; that pair's rank is then available for reuse.

5. Next, the memory system can deassert MemAdrEn and MemDataEn to return the Read-Write Buffer's address and data outputs to a three-state condition. In the timing diagram shown in Figure 7, however, the Request signal remains asserted because another address/data write is pending. The memory system then reasserts the MemAdrEn and MemDataEn signals to enable the next address/data pair onto the system buses.

6. When the memory system has accepted the second address/data pair, it again asserts the Acknowledge signal. If the Read-Write Buffer has no other write operations pending, it responds by deasserting the Request signal. Note that the Read-Write Buffer's interface to main memory is not completely asynchronous. The buffer asserts the Request signal sychronous with the rising edge of the Clock, and the Acknowledge signal input from the memory system has a minimum setup and hold time relative to the Clock.

Figure 6. Processor to LR3220 Write Timing in Harvard Mode

#### LR3220 Read-Write Buffer Preliminary

Figure 7. Main Memory Write Timing

MemData

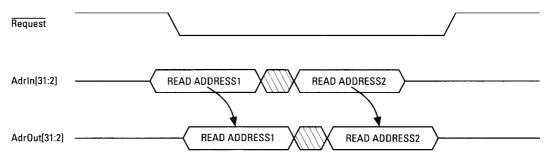

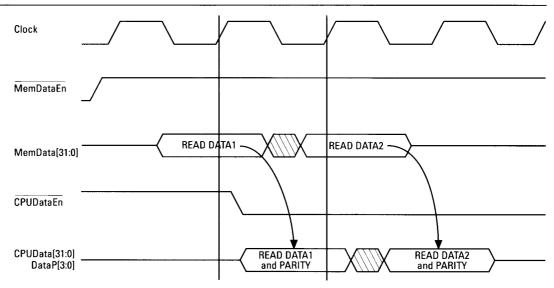

Figure 8 illustrates the read address timing for the LR3220. After the processor initiates a read operation, the main memory controller asserts RdAdrSel. This signal transfers the read address, available at the LR3220's AdrIn inputs, to the LR3220's AdrOut bus outputs for access by the memory system. If MemAdrEn is not already asserted, then the main memory controller asserts this signal to enable the read address onto the memory address bus.

The memory system returns the read data on the Read-Write Buffer's MemData bus when

MemDataEn is HIGH. The LR3220 generates even parity and strobes all 36 bits of data and parity into its internal read latch on the rising edge of the Clock. The data and parity are then available on the CPUData and DataP buses when the processor asserts the CPUDataEn signal. Note that MemDataEn should go HIGH at least one cycle before CPUDataEn goes LOW. Figure 9 shows the relative timing for read data transfers from the LR3220 to the CPU.

Figure 8. Read Address Timing

Figure 9. Read Data Timing

#### Resetting the LR3220

The Reset signal is the initialization input to the LR3220. Reset must be asserted for a minimum of four cycles to guarantee device initialization. The logic levels on the Acknowledge signal during the four cycles prior to the deassertion of Reset select the operating mode for the LR3220: Table 2 summarizes the mode selec-

tion. The Z cycle is the last cycle before the deassertion of Reset. W, X, and Y are the fourth, third, and second cycles, respectively, prior to the deassertion of Reset. Note that Acknowledge must be held HIGH during the W and X cycles to ensure compatibility with future versions of the Read-Write Buffer.

**Table 2. Reset Mode Selection**

| Mode                     | W Cycle | X Cycle | Y Cycle | Z Cycle |

|--------------------------|---------|---------|---------|---------|

| LR3000,<br>Little Endian | HIGH    | нібн    | HIGH    | HIGH    |

| LR3000,<br>Big Endian    | HIGH    | HIGH    | HIGH    | LOW     |

| Harvard                  | HIGH    | HIGH    | LOW     | LOW     |

### Absolute Maximum Rating

Table 3 shows the absolute maximum ratings for the LR3220. Note that stresses beyond those listed in this table may cause permanent damage to the device. The values in Table 3 are stress ratings only, and functional operation of the device at these or any other condi-

tions beyond those indicated under Recommended Operating Conditions, below, is not implied. Exposure to absolute-maximumrated conditions for extended periods may affect device reliability.

**Table 3. Absolute Maximum Ratings**

| Ratings               | Symbol | Value            | Units |

|-----------------------|--------|------------------|-------|

| Supply Voltage        | VCC    | -0.5 to +6.0     | V     |

| Input Voltage         | VIN    | -0.5 to VCC +0.5 | ٧     |

| Operating Temperature | TA     | 0 to 70          | °C    |

| Storage Temperature   | TSTG   | -40 to 125       | °C    |

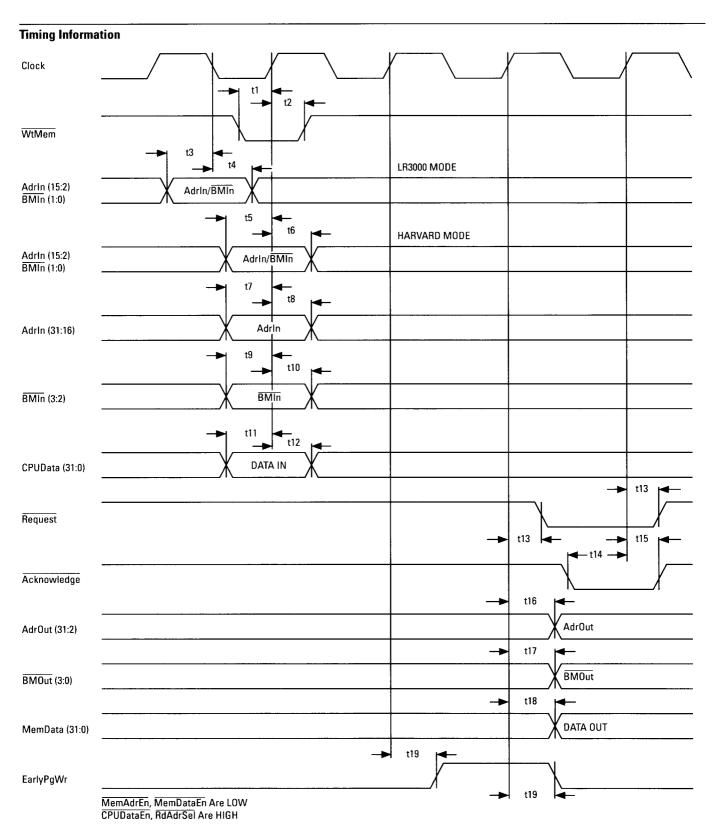

Recommended Operating Conditions Tables 4 and 5 illustrate the DC and AC electrical characteristics for the LR3220. Figures 10

through 18, which follow, are timing diagrams which illustrate the AC characteristics.

**Table 4. DC Electrical Characteristics**

|           |                     |                        | 25   | MHZ | 33.33 | MHZ |       |

|-----------|---------------------|------------------------|------|-----|-------|-----|-------|

| Parameter | Description         | Test Conditions        | Min  | Max | Min   | Max | Units |

| V0H       | Output High Voltage | VCC = Min, IOH = -4 mA | 2.4  |     | 2.4   |     | ٧     |

| V0L       | Output Low Voltage  | VCC = Min, IOL = 4 mA  |      | 0.4 |       | 0.4 | V     |

| VIH       | Input High Voltage  | VIN = VDD or GND       | 2    | vcc | 2     | VCC | V     |

| VIL       | Input Low Voltage   | VOUT = VDD or GND      | -0.5 | 0.8 | -0.5  | 0.8 | ν     |

| VIHC      | Input High Voltage  |                        | 3.5  |     | 3.5   |     | ν     |

| VILC      | Input Low Voltage   |                        |      | 0.4 |       | 0.4 | V     |

| CIN       | Input Capacitance   |                        |      | 8   |       | 8   | pF    |

| COUT      | Output Capacitance  |                        |      | 8   |       | 8   | pF    |

| CINC      | Input Capacitance   |                        |      | 15  |       | 15  | pF    |

| COUTC     | Output Capacitance  |                        |      | 15  |       | 15  | pF    |

| IIN       | Input Leakage       |                        | -10  | 10  | -10   | 10  | μА    |

| IOZ       | Output Leakage      |                        | -10  | 10  | -10   | 10  | μΑ    |

| ICC       | Supply Current      |                        |      | 160 |       | 170 | mA.   |

Note: VIHC, VILC, CINC, and COUTC apply to CPUDataEn and Clock Only.

Recommended Operating Conditions (Continued)

#### **Table 5. AC Electrical Characteristics**

|                 |                                                    | 25  | MHZ  | 33.33 | MHZ  |        |

|-----------------|----------------------------------------------------|-----|------|-------|------|--------|

| Parameter       | Description                                        | Min | Max  | Min   | Max  | Units  |

| t1              | WtMem to Clock rising setup                        | 6   |      | 5     |      | ns     |

| t2              | WtMem from Clock rising hold                       | 0   |      | 0     |      | ns     |

| t32             | Adrln(15:2)/BMIn(1:0) to Clock falling setup       | 5   |      | 5     | =    | ns     |

| t4 <sup>2</sup> | Adrln(15:2)/BMIn(1:0) to Clock falling hold        | 1.5 |      | 1.5   |      | ns     |

| t5 <sup>3</sup> | Adrln(15:2)/BMIn(1:0) to Clock rising setup        | 3   |      | 3     |      | ns     |

| t6 <sup>3</sup> | Adrln(15:2)/BMIn(1:0) to Clock rising hold         | 2   |      | 2     |      | ns     |

| t7              | Adrln(31:16) to Clock rising setup                 | 4   |      | 2     |      | ns     |

| t8              | Adrln(31:16) to Clock rising hold                  | 1.5 |      | 1.5   |      | ns     |

| t9              | BMIn(3:2) to Clock rising setup                    | 2   |      | 2     |      | ns     |

| t10             | BMIn(3:2) to Clock rising hold                     | 4   |      | 4     |      | ns     |

| t11             | CPUData(31:0) to Clock rising setup                | 4   |      | 2     |      | ns     |

| t12             | CPUData(31:0) to Clock rising hold                 | 1.5 |      | 1.5   |      | ns     |

| t13             | Request valid from Clock rising                    |     | 14   |       | 14   | ns     |

| t14             | Acknowledge to Clock rising setup                  | 8   |      | 7     |      | ns     |

| t15             | Acknowledge to Clock rising hold                   | 3   |      | 3     |      | ns     |

| t16             | AdrOut(31:2) from Clock rising                     |     | 22   |       | 20   | ns     |

| t17             | BMOut(3:0) from Clock rising                       |     | 19   |       | 15   | ns     |

| t18             | MemData(31:0) from Clock rising                    |     | 22   |       | 20   | ns     |

| t19             | EarlyPgWr from Clock rising                        |     | 22   |       | 20   | ns     |

| t20             | MemAdrEn low to AdrOut(31:2)/BMOut(3:0) valid      |     | 20   |       | 18   | ns     |

| t21             | MemAdrEn high to AdrOut(31:2)/BMOut(3:0) 3-state   |     | 20   |       | 18   | ns     |

| t22             | MemAdrEn low to MemData(31:0) valid                |     | 20   |       | 18   | ns     |

| t23             | MemAdrEn high to MemData(31:0) 3-state             |     | 20   |       | 18   | ns     |

| t24             | WBFull active from Clock rising                    |     | 16   |       | 15   | ns     |

| t25             | WBFull inactive from Clock rising                  |     | 11.5 |       | 11.5 | ns     |

| t26             | RdAdrSel low to read address valid                 |     | 20   |       | 15   | ns     |

| t27             | Adrln(31:2) to AdrOut(31:2) valid                  |     | 18   |       | 12   | ns     |

| t28             | RdAdrSel high to write address valid               |     | 22   |       | 15   | ns     |

| t29             | MemData(31:0) to Clock rising setup                |     | 12   |       | 8    | ns     |

| t30             | MemData(31:0) to Clock rising hold                 |     | 0    |       | 0    | ns     |

| t31             | CPUData(31:0)/DataP(3:0) from Clock rising         |     | 11.5 |       | 10   | ns     |

| t32             | CPUDataEn low to CPUData(31:0)/DataP(3:0) valid    |     | 11   |       | 6    | ns     |

| t33             | CPUDataEn high to CPUData(31:0)/DataP(3:0) 3-state |     | 7.5  |       | 7.5  | ns     |

| t34             | BlockMatch valid from Clock rising                 |     | 27   |       | 22   | ns     |

| t35             | Reset to Clock rising setup                        | 10  |      | 10    |      | ns     |

| t36             | Reset from Clock rising hold                       | 3   |      | 3     |      | ns     |

| t37             | Reset pulse width                                  | 4   |      | 4     |      | cycles |

#### Notes

- 1. Test conditions were 70°C, VCC = 4.75 V, output loading 50 pF TTL (except CPUData/DataP 65 pF TTL).

- 2. t3 and t4 are valid in LR3000 mode only.

- 3. t5 and t6 are valid in Harvard mode only.

Figure 10. Memory Write Timing with Page Write

Figure 11. Back-to-Back Writes; Second Write is a Page Write

Figure 12. Main Memory 3-State Output Timing

Figure 13. Write Buffer Full Timing

Figure 14. Read Address Output Timing

Figure 15. Read Data Input and Output Timing Relative to Clock

Figure 16. Read Data Output Timing Relative to CPUDataEn

Figure 17. BlockMatch Timing

Figure 18. Reset and Configure Timing

#### Pinout and Package Information

#### Table 6. 180-Pin Ceramic Pin Grid Array (CPGA) Pin List

| Signal<br>Name       | Pin<br>Number | Signal<br>Name | Pin<br>Number | Signal<br>Name | Pin<br>Number | Signal<br>Name | Pin<br>Number |

|----------------------|---------------|----------------|---------------|----------------|---------------|----------------|---------------|

| Acknowledge          | C11           | AdrOut19       | L2            | CPUData23      | £15           | RdAdrSel       | C7            |

| Adrln2               | C4            | AdrOut20       | M2            | CPUData24      | D15           | Request        | P6            |

| Adrin3               | C3            | AdrOut21       | N2            | CPUData25      | C15           |                |               |

| Adrina<br>Adrina     | B8            | AdrOut22       | P2            | CPUData26      | B15           | Reset          | D6            |

| Adrin5               | B7            | AdrOut23       | J1            | CPUData27      | A15           | WBFull         | P7            |

| Adrin6               | B6            | AdrOut24       | M1            | CPUData28      | D11           | WtMem          | C10           |

| Adrin7               | B5            | AdrOut25       | N1            | CPUData29      | D10           |                |               |

| Adrin8               | B4            | AdrOut26       | P1            | CPUData30      | A13           | VCC            | A9            |

| Adrin9               | B3            | AdrOut27       | R1            | CPUData31      | A12           | VCC            | B9<br>D9      |

| Adrin10              | B2            | AdrOut28       | M5            | DataP0         | A11           | VCC<br>VCC     | D9<br>E14     |

| Adrin11              | A8            | AdrOut29       | M6            | DataP1         | A10           |                |               |

| Adrin12              | A7            | AdrOut30       | M7            | DataP2         | B12           | VCC<br>VCC     | G12           |

| Adrin13              | A6            | AdrOut31       | R2            | DataP3         | B11           | VCC            | J4<br>K1      |

| Adrin14              | A5            | BlockMatch     | P5            |                | P3            |                |               |

| Adrin15              | A4            |                |               | EarlyPgWr      |               | VCC            | M10           |

| Adrin16              | A3            | BMIn0          | C6            | MemAdrEn       | C8            | VCC            | M14           |

| Adrin17              | A2            | BMIn1          | C5            | MemDataEn      | D5            | VCC            | P13           |

| Adrin18              | A1            | BMIn2          | C9            | MemData0       | N4            | GND            | A14           |

| Adrin19              | B1            | BMIn3          | D8            | MemData1       | N5            | GND            | B10           |

| Adrin20              | C1            | BMOut0         | R3            | MemData2       | N6            | GND            | B13           |

| Adrin21              | D1            | BMOut1         | R4            | MemData3       | N7            | GND            | D3            |

| Adrin22              | E1            | BMOut2         | R5            | MemData4       | M8            | GND            | D4            |

| Adrin23              | F1            | BMOut3         | R6            | MemData5       | M9            | GND            | E8            |

| Adrin24              | G1            | Clock          | D7            | MemData6       | M12           | GND            | F13           |

| Adrln25              | H1            | CPUDataEn      | C12           | MemData7       | N8            | GND            | F14           |

| Adrln26              | C2            |                |               | MemData8       | N9            | GND            | G15           |

| Adrln27              | D2            | CPUData0       | K14           | MemData9       | N10           | GND            | H5            |

| Adrln28              | E2            | CPUData1       | J14           | MemData10      | N11           | GND            | H11           |

| Adrln29              | F2            | CPUData2       | H14           | MemData11      | N12           | GND            | J2            |

| Adrln30              | G2            | CPUData3       | M13           | MemData12      | P8            | GND            | K13           |

| Adrin31              | H2            | CPUData4       | L13           | MemData13      | P9            | GND            | L1            |

| AdrOut2              | E3            | CPUData5       | J13           | MemData14      | P10           | GND            | L8            |

| AdrOut3              | F3            | CPUData6       | H13           | MemData15      | P11           | GND            | L14           |

| AdrOut4              | G3            | CPUData7       | L12           | MemData16      | P12           | GND            | M11           |

| AdrOut5              | H3            | CPUData8       | K12           | MemData17      | R8            | GND            | N13           |

| AdrOut6              | нз<br>Е4      | CPUData9       | J12           | MemData18      | R9            | GND            | P14           |

| AdrOut7              | F4            | CPUData10      | H12           | MemData19      | R10           | GND            | P15           |

| Adrout/<br>AdrOut8   | F4<br>G4      | CPUData11      | F12           | MemData20      | R11           | GND            | R7            |

|                      | H4            | CPUData12      | E12           | MemData21      | R12           | reserved       | P4            |

| AdrOut9              |               | CPUData13      | D12           | MemData22      | R13           |                | , ,           |

| AdrOut10             | K4            | CPUData14      | G13           | MemData23      | R14           |                |               |

| AdrOut11             | L4<br>M4      | CPUData15      | E13           | MemData24      | R15           |                |               |

| AdrOut12<br>AdrOut13 |               | CPUData16      | D13           | MemData25      | N15           |                |               |

|                      | J3            | CPUData17      | C13           | MemData26      | M15           |                |               |

| AdrOut14             | K3            | CPUData18      | G14           | MemData27      | L15           |                |               |

| AdrOut15             | L3            | CPUData19      | D14           | MemData28      | K15           |                |               |

| AdrOut16             | M3            | CPUData20      | C14           | MemData29      | J15           |                |               |

| AdrOut17             | N3            | CPUData21      | B14           | MemData30      | H15           |                |               |

| AdîOut18             | K2            | CPUData22      | F15           | MemData31      | N14           |                |               |

| Pinout and Package         |   | 1            | 2            | 3             | 4             | 5              | 6            | 7            | 8             | 9             | 10            | 11                             | 12                   | 13             | 14            | 15            |

|----------------------------|---|--------------|--------------|---------------|---------------|----------------|--------------|--------------|---------------|---------------|---------------|--------------------------------|----------------------|----------------|---------------|---------------|

| Information<br>(Continued) | Α | Adrin<br>18  | Adrln<br>17  | Adrin<br>16   | Adrln<br>15   | AdrIn<br>14    | Adrln<br>13  | Adrln<br>12  | Adrln<br>11   | vcc           | DataP<br>1    | DataP<br>0                     | CPU<br>Data31        | CPU<br>Data30  | GND           | CPU<br>Data27 |

|                            | В | Adrln<br>19  | Adrln<br>10  | Adrin<br>9    | Adrin<br>8    | Adrln<br>7     | AdrIn<br>6   | Adrln<br>5   | Adrin<br>4    | vcc           | GND           | DataP<br>3                     | DataP<br>2           | GND            | CPU<br>Data21 | CPU<br>Data26 |

|                            | С | Adrln<br>20  | AdrIn<br>26  | AdrIn<br>3    | Adrln<br>2    | BMIn1          | BMIn0        | RdAdr<br>Sel | Mem<br>AdrEn  | BMIn2         | WtMem         | Ac-<br>k <u>now</u> l-<br>edge | <u>CPU</u><br>DataEn | CPU<br>Data17  | CPU<br>Data20 | CPU<br>Data25 |

|                            | D | Adrln<br>21  | Adrin<br>27  | GND           | GND           | Mem<br>DataEn  | Reset        | Clock        | BMIn3         | vcc           | CPU<br>Data29 | CPU<br>Data28                  | CPU<br>Data13        | CPU<br>Data16  | CPU<br>Data19 | CPU<br>Data24 |

|                            | E | Adrln<br>22  | Adrin<br>28  | AdrOut<br>2   | AdrOut<br>6   |                |              |              | GND           |               |               |                                | CPU<br>Data12        | CPU<br>Data 15 | vcc           | CPU<br>Data23 |

|                            | F | Adrln<br>23  | Adrln<br>29  | AdrOut<br>3   | AdrOut<br>7   |                | Extra Pin    | ı            |               |               |               |                                | CPU<br>Data11        | GND            | GND           | CPU<br>Data22 |

|                            | G | Adrin<br>24  | Adrln<br>30  | AdrOut<br>4   | AdrOut<br>8   |                |              |              |               |               |               |                                | vcc                  | CPU<br>Data14  | CPU<br>Data18 | GND           |

|                            | Н | Adrln<br>25  | AdrIn<br>31  | AdrOut<br>5   | AdrOut<br>9   | GND            |              |              | Top Viev      | v             | ,             | GND                            | CPU<br>Data10        | CPU<br>Data6   | CPU<br>Data2  | Mem<br>Data30 |

|                            | J | AdrOut<br>23 | GND          | AdrOut<br>13  | vcc           |                |              |              |               |               |               |                                | CPU<br>Data9         | CPU<br>Data5   | CPU<br>Data1  | Mem<br>Data29 |

|                            | K | vcc          | AdrOut<br>18 | AdrOut<br>14  | AdrOut<br>10  |                |              |              |               |               |               |                                | CPU<br>Data8         | GND            | CPU<br>Data0  | Mem<br>Data28 |

|                            | L | GND          | AdrOut<br>19 | AdrOut<br>15  | AdrOut<br>11  |                |              |              | GND           |               |               |                                | CPU<br>Data7         | CPU<br>Data4   | GND           | Mem<br>Data27 |

|                            | M | AdrOut<br>24 | AdrOut<br>20 | AdrOut<br>16  | AdrOut<br>12  | AdrOut<br>28   | AdrOut<br>29 | AdrOut<br>30 | Mem<br>Data4  | Mem<br>Data5  | vcc           | GND                            | Mem<br>Data6         | CPU<br>Data3   | vcc           | Mem<br>Data26 |

|                            | N | AdrOut<br>25 | AdrOut<br>21 | AdrOut<br>17  | Mem<br>Data0  | Mem<br>Data1   | Mem<br>Data2 | Mem<br>Data3 | Mem<br>Data7  | Mem<br>Data8  | Mem<br>Data9  | Mem<br>Data10                  | Mem<br>Data11        | GND            | Mem<br>Data31 | Mem<br>Data25 |

|                            | Р | AdrOut<br>26 | AdrOut<br>22 | Early<br>PgWr | Re-<br>served | Block<br>Match | Re-<br>quest | WBFull       | Mem<br>Data12 | Mem<br>Data13 | Mem<br>Data14 | Mem<br>Data15                  | Mem<br>Data16        | vcc            | GND           | GND           |

|                            | R | AdrOut<br>27 | AdrOut<br>31 | BMOut<br>0    | BMOut<br>1    | BMOut<br>2     | BMOut<br>3   | GND          | Mem<br>Data17 | Mem<br>Data18 | Mem<br>Data19 | Mem<br>Data20                  | Mem<br>Data21        | Mem<br>Data22  | Mem<br>Data23 | Mem<br>Data24 |

Figure 19. 180-Pin Ceramic Pin Grid Array (CPGA) Pin Diagram

Pinout and Package Information (Continued)

#### Notes:

- 1. Ceramic packages meet Mil-Std-38510, Revision H.

- 2. Controlling dimension-inch.

Figure 20. 180-Pin Ceramic Pin Grid Array (CPGA) Mechanical Drawing

Pinout and Package Information (Continued)

#### Table 7. 184-Pin Plastic Quad Flat Pack (PQFP) Pin List

| Signal<br>Name | Pin<br>Number | Signal<br>Name | Pin<br>Number | Signal<br>Name | Pin<br>Number | Signal<br>Name | Pin<br>Number |

|----------------|---------------|----------------|---------------|----------------|---------------|----------------|---------------|

| Acknowledge    | 154           | AdrOut19       | 36            | CPUData23      | 134           | RdAdrSel       | 165           |

|                |               | AdrOut20       | 37            | CPUData24      | 135           |                |               |

| Adrin2         | 168           | AdrOut21       | 38            | CPUData25      | 136           | Request        | 59            |

| Adrin3         | 169           | AdrOut22       | 39            | CPUData26      | 137           | Reset          | 159           |

| Adrin4         | 170           | AdrOut23       | 40            | CPUData27      | 138           | WBFull         | 60            |

| Adrin5         | 171           | AdrOut24       | 43            | CPUData28      | 139           | ļ              |               |

| Adrin6         | 172           | AdrOut25       | 44            | CPUData29      | 140           | WtMem          | 155           |

| Adrln7         | 173           | AdrOut26       | 45            | CPUData30      | 143           | VCC            | 25            |

| Adrin8         | 174           | AdrOut27       | 46            | CPUData31      | 144           | VCC            | 41            |

| Adrin9         | 175           | AdrOut28       | 47            |                |               | ∮ vcc          | 67            |

| Adrln10        | 176           | AdrOut29       | 48            | DataP0         | 145           | VCC            | 83            |

| Adrln11        | 177           | AdrOut30       | 49            | DataP1         | 146           | VCC            | 101           |

| Adrln12        | 178           | AdrOut31       | 50            | DataP2         | 149           | VCC            | 117           |

| Adrin13        | 179           |                |               | DataP3         | 150           | vcc            | 128           |

| Adrln14        | 180           | BlockMatch     | 58            | EarlyPgWr      | 56            | l vcc          | 141           |

| Adrln15        | 181           | BMIn0          | 166           | MemAdrEn       | 164           | vcc            | 147           |

| Adrln16        | 182           | BMIn1          | 167           | MemDataEn      | 160           | vcc            | 152           |

| Adrln17        | 183           | BMIn2          | 156           |                |               | GND            | 14            |

| Adrin18        | 184           | BMIn3          | 157           | MemData0       | 61            | GND            | 23            |

| Adrin19        | 1             | BMOut0         | 51            | MemData1       | 62            | GND            | 23<br>24      |

| Adrin20        | 2             |                |               | MemData2       | 63            |                | 24<br>34      |

| Adrin21        | 3             | BMOut1         | 52            | MemData3       | 64            | GND            |               |

| Adrln22        | 4             | BMOut2         | 53            | MemData4       | 65            | GND            | 42            |

| Adrln23        | 5             | BM0ut3         | 54            | MemData5       | 66            | GND            | 55            |

| Adrln24        | 6             | Clock          | 158           | MemData6       | 71            | GND            | 68            |

| Adrln25        | 7             | CPUDataEn      | 153           | MemData7       | 72            | GND            | 69            |

| Adrln26        | 8             |                |               | MemData8       | 73            | GND            | 70            |

| Adrln27        | 9             | CPUData0       | 103           | MemData9       | 74            | GND            | 77            |

| Adrln28        | 10            | CPUData1       | 104           | MemData10      | 75            | GND            | 84            |

| Adrln29        | 11            | CPUData2       | 105           | MemData11      | 76            | GND            | 93            |

| Adrln30        | 12            | CPUData3       | 106           | MemData12      | 78            | GND            | 102           |

| Adrln31        | 13            | CPUData4       | 107           | MemData13      | 79            | GND            | 108           |

| AdrOut2        | 15            | CPUData5       | 109           | MemData14      | 80            | GND            | 115           |

|                |               | CPUData6       | 110           | MemData15      | 81            | GND            | 116           |

| AdrOut3        | 16            | CPUData7       | 111           | MemData16      | 82            | GND            | 122           |

| AdrOut4        | 17            | CPUData8       | 112           | MemData17      | 85            | GND            | 127           |

| AdrOut5        | 18            | CPUData9       | 113           | MemData18      | 86            | GND            | 132           |

| AdrOut6        | 19            | CPUData10      | 114           | MemData19      | 87            | GND            | 142           |

| AdrOut7        | 20            | CPUData11      | 118           | MemData20      | 88            | GND            | 148           |

| AdrOut8        | 21            | CPUData12      | 119           | MemData21      | 89            | GND            | 151           |

| AdrOut9        | 22            | CPUData13      | 120           | MemData22      | 90            | GND            | 161           |

| AdrOut10       | 26            | CPUData14      | 121           | MemData23      | 91            | GND            | 162           |

| AdrOut11       | 27            | CPUData15      | 123           | MemData24      | 92            | GND            | 163           |

| AdrOut12       | 28            | CPUData16      | 124           | MemData25      | 92<br>94      | reserved       | 57            |

| AdrOut13       | 29            | CPUData17      | 125           | MemData25      | 94<br>95      | reserveu       | 5/            |

| AdrOut14       | 30            | CPUData18      | 126           | MemData26      | 95<br>96      |                |               |

| AdrOut15       | 31            | CPUData19      | 129           |                |               |                |               |

| AdrOut16       | 23            | CPUData20      | 130           | MemData28      | 97            |                |               |

| AdrOut17       | 33            | CPUData21      | 131           | MemData29      | 98            |                |               |

| AdrOut18       | 35            | CPUData22      | 133           | MemData30      | 99            |                |               |

|                | •             | Croparazz      | 100           | MemData31      | 100           |                |               |

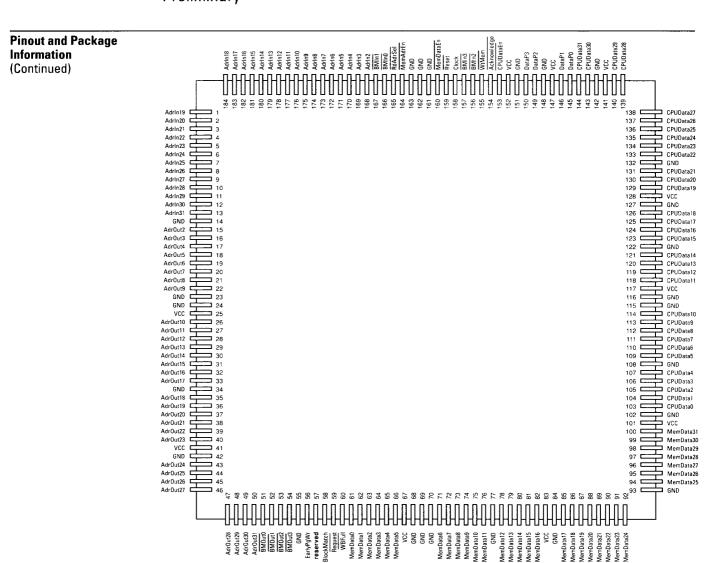

Figure 21. 184-Pin Plastic Quad Flat Pack (PQFP) Pin Diagram

#### LR3220 Read-Write Buffer Preliminary

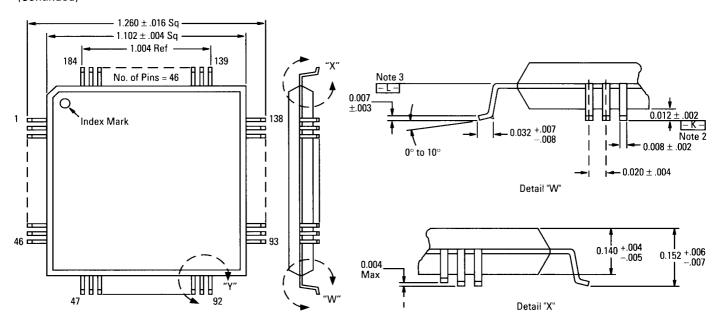

### Pinout and Package Information

(Continued)

#### Notes:

- 1. Controlling dimension—inch, rounded to the nearest .001".

- Coplanarity of all leads shall be within .004" (difference between the highest and lowest lead with seating plane --K- as reference).

- 3. Lead pitch determined at -L-.

Figure 22. 184-Pin Plastic Quad Flat Pack (PQFP) Mechanical Drawing

**Sales Offices** and Design **Resource Centers**  **LSI Logic** Corporation Headquarters Milpitas CA

408.433.8000

Alabama 205.883.3527

Arizona

602.951.4560

California San Jose

408.954.1561

Irvine

714.553.5600

San Diego 619.541.7092

Encino

**818.379.2400**

Colorado 303.756.8800

Florida

**Altamonte Springs** 407.339.2242

**Boca Raton 407.395.6200**

> Georgia 404.448.4898

Illinois

**708.773.0111**

Maryland Bethesda

**301.897.5800**

Columbia 301.740.5664 Massachusetts

■ 617.890.0180 (Design Ctr) 617.890.0161 (Sales Ofc)

Michigan 313.930.6975

Minnesota

612.921.8300

**New Jersey**

201.549.4500

New York 914.226.1620

North Carolina

**919.872.8400**

Oregon 503.645.9882

Pennsylvania 215.638.3010

Texas Austin 512.892.7276

Dallas 214.788.2966

Washington

**206.822.4384**

**LSI Logic Corporation** of Canada, Inc. Headquarters

Calgary **403.262.9292**

Edmonton

**403.450.4400**

**Ottawa**

613.592.1263

Montreal

**514.694.2417**

Toronto

**416.620.7400**

Vancouver 604.433.5705

France

LSI Logic S.A. **33.1.46206600**

Israel **LSI Logic Limited**

972.3.5403741/4

Italy

LSI Logic SPA **39.39.6056881**

Japan LSI Logic K.K. Tokyo

**81.3.589.2711**

Tsukuba-Shi **81.298.52.8371**

**Osaka**

81.6.947.5281

Yokohama 81.45.902.4111

LSI Logic Corporation of Korea Limited

82.2.561.2921

Netherlands LSI Logic/Arcobel

**31.4120.30335**

Scotland LSI Logic Limited 44.506.416767

LSI Logic Export AB 46.8.703.4680

**Switzerland**

LSI Logic/Sulzer **41.32.515441**

Sweden

Taiwan **LSI Logic Corporation**

**886.2.755.3433**

**United Kingdom** LSI Logic Limited Bracknell

**44.344.426544**

Sidcup

**44**.1.302.8282

**West Germany** LSI Logic GmbH Headquarters Munich

49.89.926903.0

Dusseldorf **49.211.5961066**

Stuttgart

**49.711.2262151**

**AE Advanced Electronics**

Hannover **49.511.3681756**

**AE Advanced Electronics** Munich

**49.89.93009855**

■ Sales Offices with Design Resource Centers

LSI Logic Corporation reserves the right to make changes to any products and services herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase, lease, or use of a product or service from LSI Logic control of the cont vey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or of third parties. All rights reserved.

Printed in USA 070.7721.6538.025.10K.DTP.J

LSI Logic logo design is a registered trademark of LSI Logic Corporation. MIPS is a trademark of MIPS Computer Systems.