# 68HC05BD7 68HC705BD7 68HC05BD2

SPECIFICATION

REV 2.0

(General Release)

© January 20, 1998

Technical Operation Taiwan Taipei, Taiwan

# **TABLE OF CONTENTS**

| SECTION ' | 1 G                | ENERAL DESCRIPTION                           | . 1      |

|-----------|--------------------|----------------------------------------------|----------|

|           | 1.1                | Features                                     | 1        |

|           | 1.1.1              | Hardware Features                            |          |

|           | 1.1.2              | Software Features                            |          |

|           | 1.2                | Signal Description                           |          |

|           | 1.2.1              | VDD and VSS                                  |          |

|           | 1.2.2              | IRQ/VPP                                      |          |

|           | 1.2.3              | EXTAL, XTAL                                  |          |

|           | 1.2.3.1            | Crystal Oscillator                           |          |

|           | 1.2.4              | RESET                                        |          |

|           | 1.2.5              | PA0-PA7                                      | 8        |

|           | 1.2.6              | PB0-PB5                                      |          |

|           | 1.2.7              | PC0*/PWM8*-PC1*/PWM9*                        | 8        |

|           | 1.2.8              | PC2/PWM10/ADC0- PC5/PWM13/ADC3               | 8        |

|           | 1.2.9              | PC6/PWM14/VSYNO, PC7/PWM15/HSYNO             | 8        |

|           | 1.2.10             | PD0*/SDA*, PD1*/SCL*                         |          |

|           | 1.2.11             | PD2***/CLAMP, PD3*/SOG                       |          |

|           | 1.2.12             | PWM0**-PWM7**                                |          |

|           | 1.2.13             | HSYNC, VSYNC                                 | 9        |

|           | 1.3                | Options                                      | 9        |

| SECTION 2 | 2 M                | EMORY                                        | 11       |

|           | 2.1                | COP                                          | 15       |

|           | 2.2                | ROM                                          |          |

|           | 2.3                | EPROM                                        |          |

|           | 2.4                | RAM                                          |          |

| SECTION : | 3 CI               | PU CORE1                                     | 17       |

|           | 3.1                | Registers                                    | 17       |

|           | 3.1.1              | Accumulator (A)                              |          |

|           | 3.1.2              | Index Register (X)                           |          |

|           | 3.1.3              | Stack Pointer (SP)                           | 18       |

|           | 3.1.4              | Program Counter (PC)                         |          |

|           | 3.1.5              | Condition Code Register (CCR)                |          |

|           | 3.1.5.1            | Half Carry Bit (H-Bit)                       |          |

|           | 3.1.5.2            | Interrupt Mask (I-Bit)                       | 19       |

|           | 3.1.5.3            | Negative Bit (N-Bit)                         | 19       |

|           | 3.1.5.4<br>3.1.5.5 | Zero Bit (Z-Bit)<br>Carry/Borrow Bit (C-Bit) | 19<br>19 |

| SECTION 4 |                    | TERRUPTS                                     |          |

|           | 4.1                | CPU Interrupt Processing                     |          |

|           | 4.1                | Reset Interrupt Sequence                     |          |

|           | 4.2                | Software Interrupt (SWI)                     |          |

|           | <del>7</del> .∪    |                                              |          |

|           |                |                                          | www.DataSheet4U.com |

|-----------|----------------|------------------------------------------|---------------------|

|           | 4.4            | Hardware Interrupts                      |                     |

|           | 4.4.1<br>4.4.2 | External Interrupt (IRQ)                 | 23                  |

|           |                | VSYNC Interrupt                          |                     |

|           | 4.4.3          | DDC12AB Interrupt                        |                     |

|           | 4.4.4          | Multi-Function Timer Interrupt (MFT)     | 25                  |

| SECTION ! | 5              | RESETS                                   | 27                  |

|           | 5.1            | External Reset (RESET)                   | 27                  |

|           | 5.2            | Internal Resets                          |                     |

|           | 5.2.1          | Power-On Reset (POR)                     | 27                  |

|           | 5.2.2          | Computer Operating Properly Reset (COPR) | 27                  |

|           | 5.2.3          | Illegal Address (ILADR) Reset            | 28                  |

| SECTION ( | 6              | OPERATING MODES                          | 29                  |

|           | 6.1            | User Mode                                | 29                  |

|           | 6.2            | SELF-CHECK MODE                          |                     |

|           | 6.3            | Bootstrap Mode                           |                     |

|           | 6.4            | Mode Entry                               |                     |

|           | 6.5            | EPROM Programming                        |                     |

|           | 6.5.1          | Programming Sequence                     | 30                  |

|           | 6.5.2          | Programming Control Register (PCR)       | 31                  |

|           | 6.6            | Low Power Modes                          | 31                  |

|           | 6.6.1          | STOP Instruction                         |                     |

|           | 6.6.2          | WAIT Instruction                         | 31                  |

|           | 6.7            | COP Watchdog Timer Considerations        | 32                  |

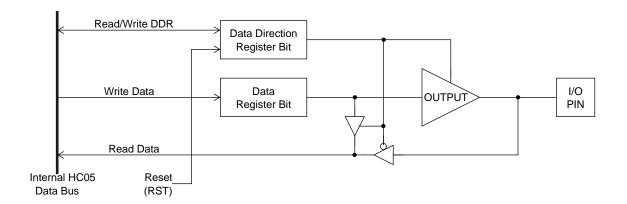

| SECTION 7 | 7              | INPUT/OUTPUT PORTS                       | 33                  |

|           | 7.1            | Port A                                   | 33                  |

|           | 7.2            | Port B                                   |                     |

|           | 7.3            | Port C                                   |                     |

|           | 7.4            | Port D                                   | 33                  |

|           | 7.5            | Input/Output Programming                 |                     |

|           | 7.6            | Port C and D Configuration Register      | 35                  |

| SECTION 8 | 8              | PULSE WIDTH MODULATION                   | 37                  |

|           | 8.1            | Operation of 8-Bit PWM                   | 37                  |

|           | 8.2            | Open-Drain Option Register               |                     |

| SECTION S | 9              | DDC12AB INTERFACE                        | 39                  |

|           | 9.1            | Introduction                             | 39                  |

|           | 9.2            | DDC12AB Features                         |                     |

|           | 9.3            | Registers                                |                     |

|           | 9.3.1          | DDC Address Register (DADR)              |                     |

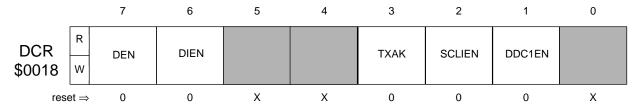

|           | 9.3.2          | DDC Control Register (DCR)               | 40                  |

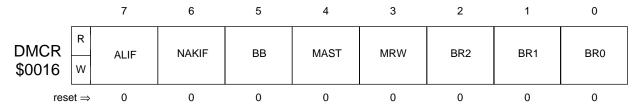

|           | 9.3.3          | DDC Master Control Register (DMCR)       | 41                  |

|           | 9.3.4          | DDC Status Register (DSR)                | 43                  |

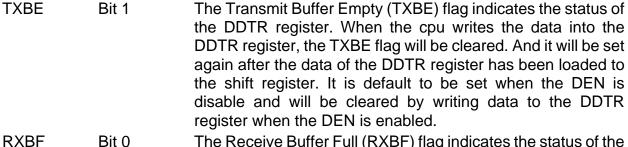

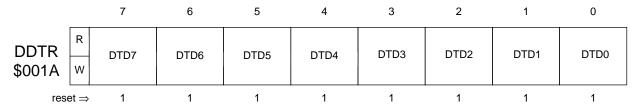

|           | 9.3.5          | DDC Data Transmit Register (DDTR)        |                     |

|         | 0.2.6                                                                                                                                                        | DDC Data Bassiya Basistar (DDDD)                                                                                                                                                                                                                                                                                                                         | U.com                                                                      |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|         | 9.3.6<br>9.4                                                                                                                                                 | DDC Data Receive Register (DDRR)                                                                                                                                                                                                                                                                                                                         |                                                                            |

|         | 9.5                                                                                                                                                          | Program Algorithm                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| SECTION | 10 S                                                                                                                                                         | YNC PROCESSOR                                                                                                                                                                                                                                                                                                                                            | 49                                                                         |

|         | 10.1                                                                                                                                                         | Introduction                                                                                                                                                                                                                                                                                                                                             | 49                                                                         |

|         | 10.2                                                                                                                                                         | Functional Blocks                                                                                                                                                                                                                                                                                                                                        | 49                                                                         |

|         | 10.2.1                                                                                                                                                       | Polarity Detection                                                                                                                                                                                                                                                                                                                                       | 49                                                                         |

|         | 10.2.2                                                                                                                                                       | Sync Signal Counters                                                                                                                                                                                                                                                                                                                                     |                                                                            |

|         | 10.2.3                                                                                                                                                       | Polarity Controlled HSYNO/VSYNO Outputs                                                                                                                                                                                                                                                                                                                  |                                                                            |

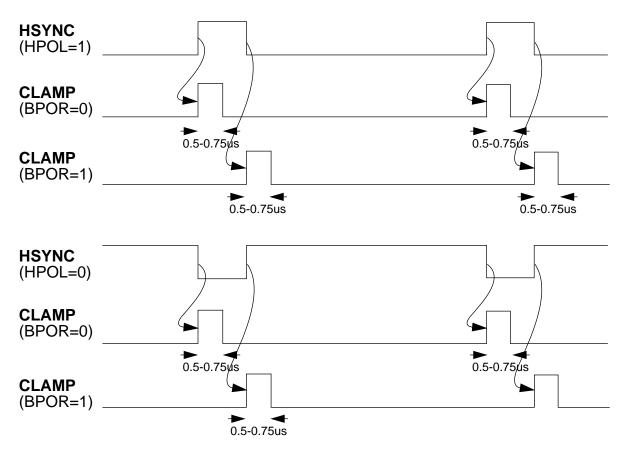

|         | 10.2.4                                                                                                                                                       | CLAMP Pulse Output                                                                                                                                                                                                                                                                                                                                       |                                                                            |

|         | 10.3                                                                                                                                                         | Registers                                                                                                                                                                                                                                                                                                                                                |                                                                            |

|         | 10.3.1<br>10.3.2                                                                                                                                             | Sync Processor Control and Status Register (SPCSR) Sync Processor Input/Output Control Register (SPIOCR)                                                                                                                                                                                                                                                 |                                                                            |

|         | 10.3.2                                                                                                                                                       | Vertical Frequency Registers (VFRs)                                                                                                                                                                                                                                                                                                                      |                                                                            |

|         | 10.3.4                                                                                                                                                       | Hsync Frequency Registers (HFRs)                                                                                                                                                                                                                                                                                                                         |                                                                            |

|         | 10.4                                                                                                                                                         | System Operation                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| SECTION |                                                                                                                                                              | IULTI-FUNCTION TIMER                                                                                                                                                                                                                                                                                                                                     |                                                                            |

| SECTION |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

|         | 11.1                                                                                                                                                         | Introduction                                                                                                                                                                                                                                                                                                                                             |                                                                            |

|         | 11.2<br>11.2.1                                                                                                                                               | Register                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

|         | 11.2.1                                                                                                                                                       | Multi-function Timer Control/status Register MFT Timer Counter Register                                                                                                                                                                                                                                                                                  |                                                                            |

|         | 11.2.2                                                                                                                                                       | Wil 1 Tilliel Couliter Negloter                                                                                                                                                                                                                                                                                                                          |                                                                            |

| _       |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| SECTION | 12 A                                                                                                                                                         | /D CONVERTER                                                                                                                                                                                                                                                                                                                                             | 61                                                                         |

| SECTION | 12.1                                                                                                                                                         | /D CONVERTERIntroduction                                                                                                                                                                                                                                                                                                                                 | _                                                                          |

| SECTION | 12.1<br>12.2                                                                                                                                                 | IntroductionInput                                                                                                                                                                                                                                                                                                                                        | 61<br>61                                                                   |

| SECTION | 12.1<br>12.2<br>12.2.1                                                                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                             | 61<br>61                                                                   |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3                                                                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                             | 61<br>61<br>61                                                             |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                             | 61<br>61<br>61<br>62                                                       |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                             | 61<br>61<br>62<br>62                                                       |

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4                                                                                                   | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example                                                                                                                                                                                                                                                  | 61<br>61<br>62<br>62<br>63                                                 |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4                                                                                                   | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example  LECTRICAL SPECIFICATIONS                                                                                                                                                                                                                        | 61<br>61<br>62<br>62<br>62                                                 |

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b>                                                                                    | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example  LECTRICAL SPECIFICATIONS Maximum Ratings                                                                                                                                                                                                        | 61<br>61<br>62<br>62<br>63                                                 |

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2                                                                    | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example  LECTRICAL SPECIFICATIONS Maximum Ratings Thermal Characteristics                                                                                                                                                                                | 61<br>61<br>62<br>62<br>63<br>63                                           |

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3                                                            | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example  LECTRICAL SPECIFICATIONS  Maximum Ratings Thermal Characteristics DC Electrical Characteristics                                                                                                                                                 | 61<br>61<br>62<br>62<br>63<br>63                                           |

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3<br>13.4                                                    | Introduction Input                                                                                                                                                                                                                                                                                                                                       | 61<br>61<br>62<br>62<br>63<br>63<br>65<br>65                               |

|         | 12.1<br>12.2<br>12.2.1<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5                                                    | Introduction Input                                                                                                                                                                                                                                                                                                                                       | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>65                         |

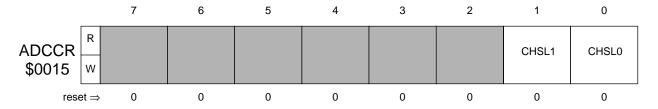

|         | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1                                  | Introduction Input ADC0-ADC3 Registers ADC Control/status Register ADC Channel Register Program Example  LECTRICAL SPECIFICATIONS  Maximum Ratings Thermal Characteristics DC Electrical Characteristics Control Timing DDC12AB TIMING DDC12AB Interface Input Signal Timing                                                                             | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>66<br>66                   |

|         | 12.1<br>12.2<br>12.2.1<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1<br>13.5.2                                | Introduction Input  ADC0-ADC3 Registers  ADC Control/status Register  ADC Channel Register  Program Example  LECTRICAL SPECIFICATIONS  Maximum Ratings  Thermal Characteristics  DC Electrical Characteristics  Control Timing  DDC12AB TIMING  DDC12AB Interface Input Signal Timing  DDC12AB Interface Output Signal Timing                            | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>66<br>67                   |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3.1<br>12.3.2<br>12.4<br><b>13 E</b><br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1<br>13.5.2<br>13.6                        | Introduction Input  ADC0-ADC3  Registers  ADC Control/status Register  ADC Channel Register  Program Example  LECTRICAL SPECIFICATIONS  Maximum Ratings  Thermal Characteristics  DC Electrical Characteristics  Control Timing  DDC12AB TIMING  DDC12AB Interface Input Signal Timing  DDC12AB Interface Output Signal Timing  HSYNC/VSYNC Input Timing | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>66<br>67<br>68<br>68       |

|         | 12.1<br>12.2<br>12.2.1<br>12.3.1<br>12.3.2<br>12.4<br><b>13</b> E<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1<br>13.5.2<br>13.6                        | Introduction Input                                                                                                                                                                                                                                                                                                                                       | 61<br>62<br>62<br>63<br>65<br>65<br>65<br>65<br>66<br>67<br>68<br>68       |

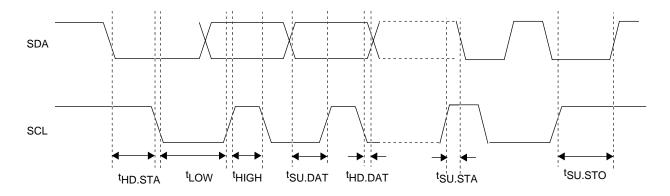

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3<br>12.3.1<br>12.3.2<br>12.4<br><b>13</b> E<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1<br>13.5.2<br>13.6<br><b>14</b> M | Introduction Input                                                                                                                                                                                                                                                                                                                                       | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>66<br>68<br>68<br>68       |

| SECTION | 12.1<br>12.2<br>12.2.1<br>12.3.1<br>12.3.2<br>12.4<br><b>13</b> E<br>13.1<br>13.2<br>13.3<br>13.4<br>13.5<br>13.5.1<br>13.5.2<br>13.6                        | Introduction Input                                                                                                                                                                                                                                                                                                                                       | 61<br>61<br>62<br>62<br>63<br>65<br>65<br>65<br>66<br>68<br>68<br>68<br>68 |

MC68HC05BD7 RevFreescale Semiconductoral Inches Executive IION

**SECTION 15**

### www.DataSheet4U.com

# **LIST OF FIGURES**

| Figure 1-1: I | MC68HC05BD7 Block Diagram                                                | .4  |

|---------------|--------------------------------------------------------------------------|-----|

| Figure 1-2: I | MC68HC05BD7/BD2 40-Pin DIP Pin Assignment                                | .5  |

| Figure 1-3: I | MC68HC05BD7/BD2 42-Pin SDIP Pin Assignment                               | .6  |

| Figure 1-4: ( | Oscillator Connections                                                   | . 7 |

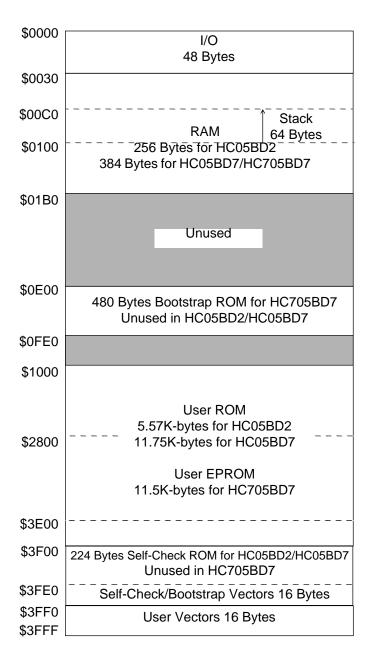

| Figure 2-1:   | The 16K Memory Map of the MC68HC05BD7                                    | 11  |

| Figure 2-2: I | MC68HC05BD7 I/O Register \$00-\$0F                                       | 12  |

| Figure 2-3: I | MC68HC05BD7 I/O Register \$10-\$1F                                       | 13  |

| Figure 2-4: I | MC68HC05BD7 I/O Register \$20-\$2F                                       | 14  |

| Figure 3-1: I | MC68HC05 Programming Model                                               | 17  |

| Figure 4-1: I | Interrupt Processing Flowchart                                           | 22  |

| Figure 4-2: I | External Interrupt                                                       | 24  |

| Figure 6-1: I | Mode Entry Diagram                                                       | 30  |

| Figure 6-2: \ | WAIT Flowcharts                                                          | 32  |

| Figure 7-1: I | Port I/O Circuitry                                                       | 34  |

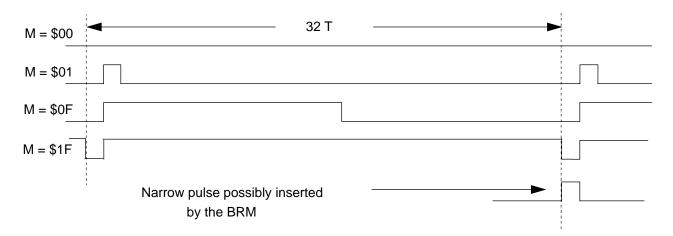

| Figure 8-1: I | PWM Data Register                                                        | 37  |

| Figure 8-2: I | Relationship Between 5-Bit PWM and 3-Bit BRM                             | 38  |

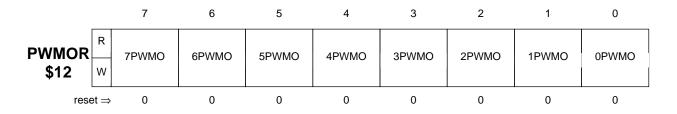

| Figure 8-3: I | PWM Open-Drain Option Register                                           | 38  |

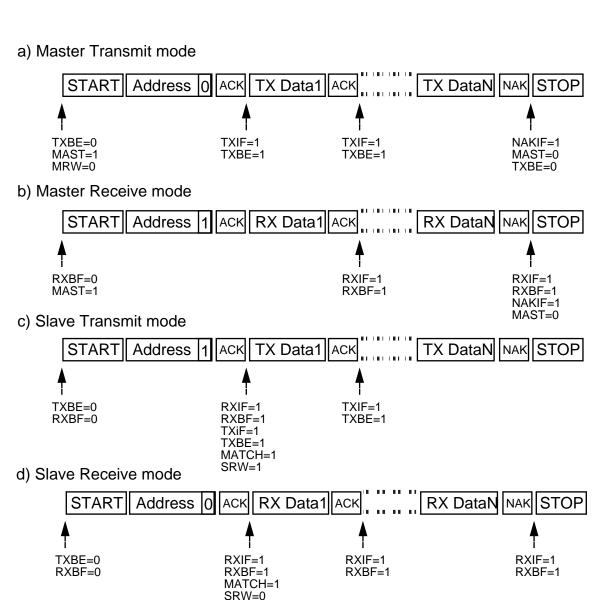

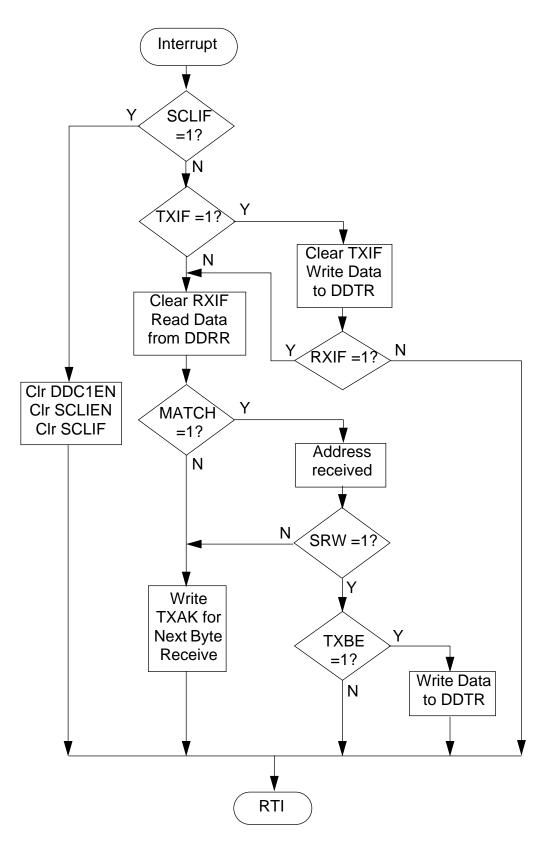

| Figure 9-1:   | Software Flowchart of Slave Mode Interrupt Routine                       | 47  |

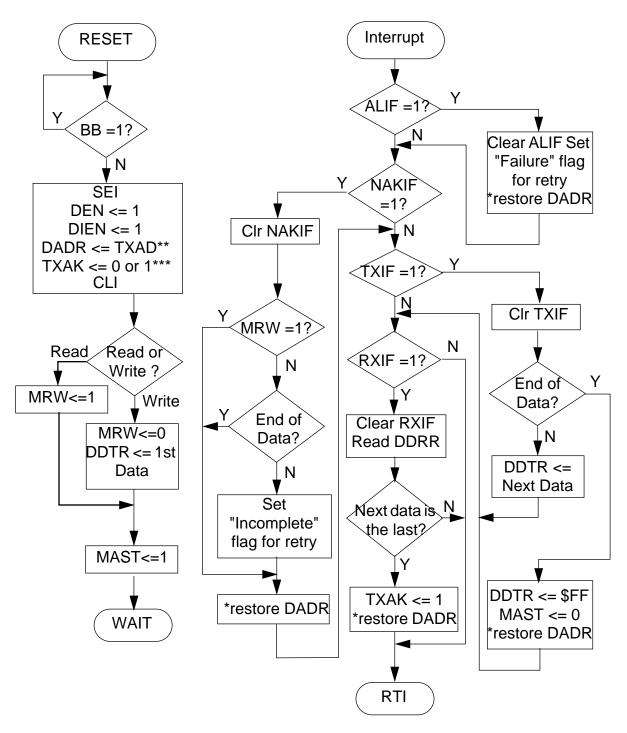

| Figure 9-2:   | Software Flowchart in Master mode: (a) Mode setup. (b) Interrupt routine | 48  |

| Figure 10-1:  | : CLAMP output waveform                                                  | 50  |

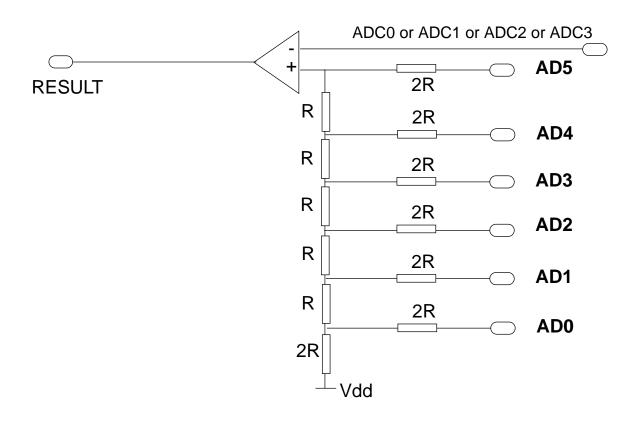

| Figure 12-1:  | : Structure of A/D Converter                                             | 61  |

# reescale Semiconductor, Inc.

### www.DataSheet4U.com

# **LIST OF TABLES**

| Table 4-1: Vector Address for Interrupts and Reset | 21 |

|----------------------------------------------------|----|

| Table 6-1: Mode Select Summary                     | 30 |

| Table 7-1: I/O Pin Functions                       | 35 |

| Table 9-1: Pre-scaler of Master Clock Baudrate     | 42 |

| Table 11-1: COP Reset Rates and RTI Rates          | 59 |

THIS PAGE INTENTIONALLY LEFT BLANK

### **SECTION 1**

### **GENERAL DESCRIPTION**

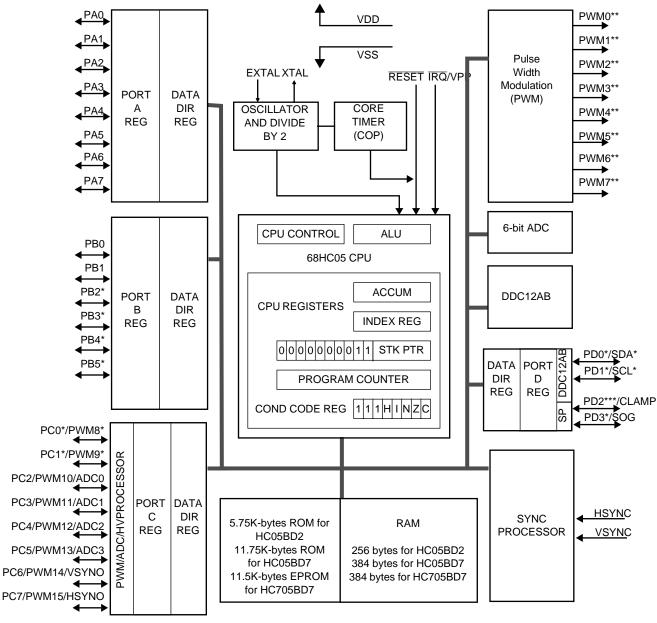

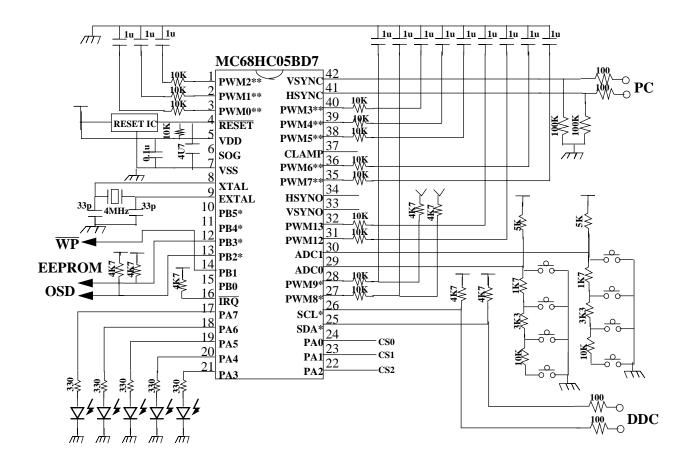

The MC68HC05BD7 HCMOS microcontroller is a member of the M68HC05 Family of low-cost single-chip microcontrollers. It is particularly suitable as multi-sync computer monitor controller. This 8-bit microcontroller unit (MCU) contains an on-chip oscillator, CPU, RAM, ROM, DDC12AB module, parallel I/O, Pulse Width Modulator, Multi-Function Timer, 6-bit ADC, and SYNC Processor.

### 1.1 Features

### 1.1.1 Hardware Features

- HC05 Core

- Low cost, HCMOS technology

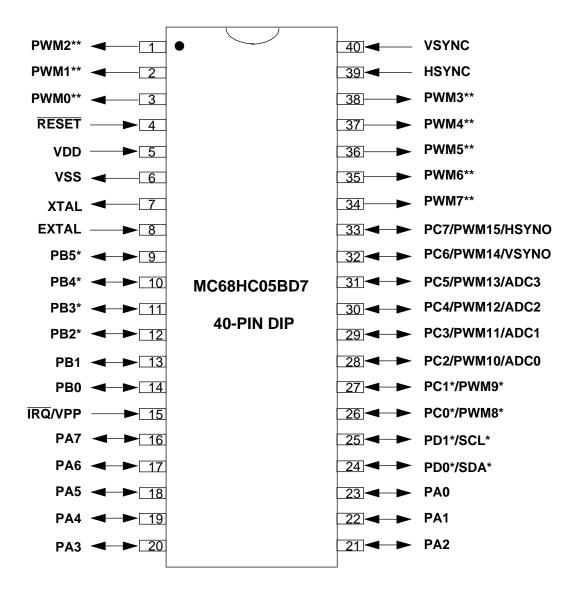

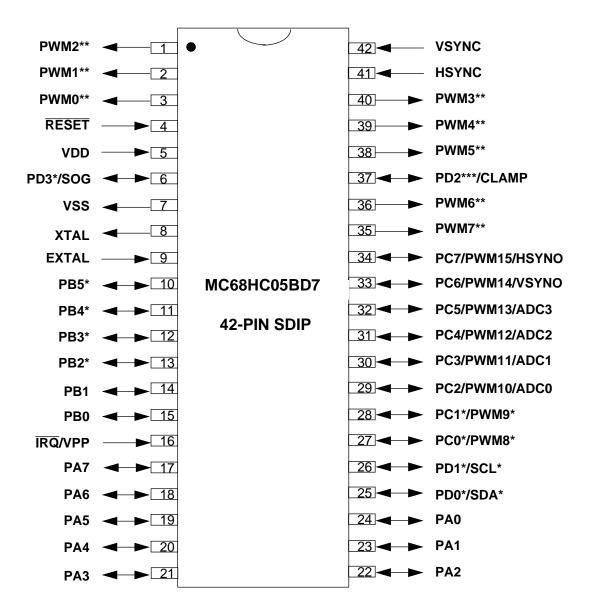

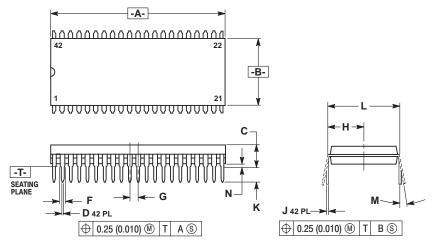

- 40-pin DIP and 42-pin SDIP packages

- 256 Bytes of RAM for HC05BD2

- 384 Bytes of RAM for HC05BD7HC705BD7

- 5.75K-Bytes of User ROM for HC05BD2

- 11.75K-Bytes of User ROM for HC05BD7

- 11.5K-Bytes of User EPROM for HC705BD7

- 26 Bidirectional I/O lines: 14 dedicated and 12 multiplexed I/O lines. 4 of the 14 dedicated I/O lines and 6 of the 12 multiplexed I/O lines have max. +12V or +5V open-drain output buffers

- 16 x 8-bit PWM channels: Two 8-bit PWM channels have +12V opendrain outputs: 8 dedicated 8-bit PWM channels have +5V open-drain output options

- 6-bit ADC with 4 selectable input channels

- Multi-Function Timer (MFT) with Periodic Interrupt

- Sync Signal Processor module for processing horizontal, vertical, composite, and SOG SYNC signals; frequency counting; polarity detection; polarity controlled HSYNO and VSYNO or extracted VSYNC outputs, and CLAMP pulse output

- DDC12AB<sup>†</sup> module contains DDC1 hardware and multi-master I<sup>2</sup>C<sup>††</sup> hardware for DDC2AB protocol

- Software maskable Edge-Sensitive or Edge and Level-Sensitive External Interrupt

**SECTION 1: GENERAL DESCRIPTION**

<sup>&</sup>lt;sup>†</sup>DDC is a standard defined by VESA.

<sup>&</sup>lt;sup>††</sup>I<sup>2</sup>C-bus is a proprietary Philips interface bus.

www.DataSheet4U.com

- COP watchdog Reset

- Power-On Reset

- Power Saving WAIT Mode; STOP Mode not implemented

www.DataSheet4U.con

### 1.1.2 Software Features

- Similar to MC6800

- 8 X 8 unsigned multiply instruction

- Efficient use of program space

- · Versatile interrupt handling

- Software programmable external interrupt options

- True bit manipulation

- Addressing modes with indexed addressing for tables

- Efficient instruction set

- Memory mapped I/O

- Upward software compatible with the MC146805 CMOS family

<sup>\*\*\*: +5</sup>V open-drain

IRQ/VPP: VPP valid for HC705 version only, not used for HC05 version

Figure 1-1: MC68HC05BD7 Block Diagram

<sup>\*\*: +5</sup>V open-drain option

<sup>\*: +12</sup>V open-drain

<sup>\*\*: +5</sup>V open-drain option

IRQ/VPP: VPP valid for HC705 version only, not used for HC05 version

Figure 1-2: MC68HC05BD7/BD2 40-Pin DIP Pin Assignment

<sup>\*: +12</sup>V open-drain

<sup>\*\*\*: +5</sup>V open-drain option

IRQ/VPP: VPP valid for HC705 version only, not used for HC05 version

Figure 1-3: MC68HC05BD7/BD2 42-Pin SDIP Pin Assignment

<sup>\*\*: +5</sup>V open-drain option

<sup>\*: +12</sup>V open-drain

### 1.2 Signal Description

### 1.2.1 VDD and VSS

VDD is the positive supply pin and VSS is the ground pin.

### 1.2.2 **IRQ/VPP**

This pin has two functions. While in user mode, this pin serves as  $\overline{IRQ}$ , a general purpose interrupt input which is software programmable for two choices of interrupt triggering sensitivity. These options are: 1) negative edge-sensitive triggering only, or 2) both negative edge-sensitive and level-sensitive triggering. In the latter case, either type of input to the  $\overline{IRQ}$  pin will produce the interrupt. This interrupt can be inhibited by setting the INHIRQ bit in the MFT register. While in bootstrap mode, this pin is used as VPP pin for HC705 version. It is used to supply high voltage needed for programming the user EPROM.

### 1.2.3 EXTAL, XTAL

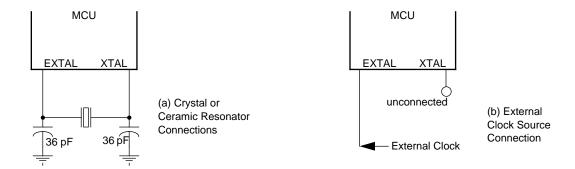

The EXTAL and XTAL pins are the connections for the on-chip oscillator. The EXTAL, and XTAL pins can accept the following sets of components:

- 1. A crystal as shown in Figure 1-4(a)

- 2. An external clock signal as shown in **Figure 1-4(b)**

The frequency,  $f_{OSC}$ , of the oscillator or external clock source is divided by two to produce the internal operating frequency,  $f_{OP}$ .

### 1.2.3.1 Crystal Oscillator

The circuit in shows **Figure 1-4(a)** a typical oscillator circuit for an AT-cut, parallel resonant crystal. The crystal manufacturer's recommendations should be followed, as the crystal parameters determine the external component values required to provide maximum stability and reliable start-up. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for start-up stabilization and to minimize output distortion. An **internal start-up resistor** of approximately **2 M** $\Omega$  is provided between EXTAL and XTAL for the crystal type oscillator.

**Figure 1-4: Oscillator Connections**

**SECTION 1: GENERAL DESCRIPTION**

### **1.2.4 RESET**

This active low input-only pin is used to reset the MCU to a known start-up state. The RESET pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See **SECTION 5** for more details.

### 1.2.5 PA0-PA7

These eight I/O lines comprise Port A. The state of any pin is software programmable and all Port A lines are configured as inputs during Reset. See **SECTION 7** for a detailed description of I/O programming.

### 1.2.6 PB0-PB5

These six I/O lines comprise Port B. The state of any pin is software programmable and all Port B lines are configured as inputs during Reset. PB2 to PB5 are +12V open-drain pins. See **SECTION 7** for a detailed description of I/O programming.

### 1.2.7 PC0\*/PWM8\*-PC1\*/PWM9\*

These two +12V open-drain pins are either 8-bit PWM channels 8 to 9 outputs or general purpose I/O port C. The state of any pin is software programmable and all Port C lines are configured as inputs during Reset. See **SECTION 7** for a detailed description of I/O programming.

### 1.2.8 PC2/PWM10/ADC0- PC5/PWM13/ADC3

These four pins can be selected as general purpose I/O of port C, PWM or ADC input channel 0-2. See **SECTION 7** for how to configure the pins. Also see **SECTION 8** and **SECTION 12** for a detailed description of these modules.

### 1.2.9 PC6/PWM14/VSYNO, PC7/PWM15/HSYNO

These two pins can be selected as general purpose I/O of port C, PWM or sync signal outputs. See **SECTION 7** for how to configure the pins. Also see **SECTION 8** and **SECTION 10** for a detailed description of these modules.

### 1.2.10 PD0\*/SDA\*, PD1\*/SCL\*

These pins are either general purpose I/O pins of port D or the data line (SDA) and clock line (SCL) of DDC12AB. These two pins are open-drain pins. See **SECTION 7** for how to configure the pins. See **SECTION 9** for a detailed description.

### 1.2.11 PD2\*\*\*/CLAMP, PD3\*/SOG

The PD2\*\*\* is +5V open-drain general purpose I/O pin and the PD3\* is +12V open-drain general purpose I/O pin. The PD2 pin could become the CLAMP pulse push-pull output to Pre-AMP IC and the PD3 pin could become the SOG digital input of the Sync Processor when the corresponding enable bit in SPIOCR register is set. These two pins will not be bonded out in 40-pin DIP package.

### 1.2.12 PWM0\*\*-PWM7\*\*

These pins are dedicated for 8-bit PWM channels 0 to 7, which have +5V open-drain software options. See **SECTION 8** for a detailed description.

### 1.2.13 HSYNC, VSYNC

These two input pins are for video sync signals input from the host computer. The signals will be used for video mode detection and output to **HSYNO** and **VSYNO**. The host computer can also send a composite sync signal to the **HSYNC** input. This composite signal will be separated internally. The polarity of the input signals can be either positive or negative. These two pins contain internal Schmitt triggers as part of their inputs to improve noise immunity. See **SECTION 10** for a detail description.

### 1.3 Options

MC68HC05BD7 provides an option for  $\overline{IRQ}$  interrupt edge only sensitivity or edge and level sensitivity and one option register for individual PWM channels 0 to 7 to be programmed as open-drain type output. The IRQ option is selected by setting the appropriate bit in the MFTCSR register at address \$0008 and the PWM open-drain option register is located at address \$0012.

**SECTION 1: GENERAL DESCRIPTION**

reescale Semiconductor, Inc

## **SECTION 2**

### **MEMORY**

The MC68HC05BD7 has a 16K byte memory map, consisting of user ROM/EPROM, RAM, Self-Check/Bootstrap ROM, and I/O as shown in **Figure 2-1**.

Figure 2-1: The 16K Memory Map of the MC68HC05BD7

| ADDR   | DECICIED                        | EAD    | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|---------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| \$0000 | PORT A DATA<br>PORTA            | R<br>W | PA7    | PA6    | PA5    | PA4    | PA3    | PA2    | PA1    | PA0    |

| \$0001 | PORT B DATA<br>PORTB            | R<br>W |        |        | PB5    | PB4    | PB3    | PB2    | PB1    | PB0    |

| \$0002 | PORT C DATA<br>PORTC            | R<br>W | PC7    | PC6    | PC5    | PC4    | PC3    | PC2    | PC1    | PC0    |

| \$0003 | PORT D DATA<br>PORTD            | R<br>W |        |        |        |        | PD3    | PD2    | PD1    | PD0    |

| \$0004 | PORT A DATA DIRECTION<br>DDRA   | R<br>W | DDRA7  | DDRA6  | DDRA5  | DDRA4  | DDRA3  | DDRA2  | DDRA1  | DDRA0  |

| \$0005 | PORT B DATA DIRECTION DDRB      | R<br>W |        |        | DDRB5  | DDRB4  | DDRB3  | DDRB2  | DDRB1  | DDRB0  |

| \$0006 | PORT C DATA DIRECTION DDRC      | R<br>W | DDRC7  | DDRC6  | DDRC5  | DDRC4  | DDRC3  | DDRC2  | DDRC1  | DDRC0  |

| \$0007 | PORT D DATA DIRECTION DDRD      | R<br>W |        |        |        |        | DDRD3  | DDRD2  | DDRD1  | DDRD0  |

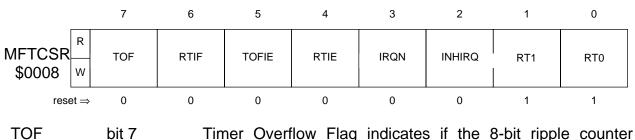

| \$0008 | MFT CTRL/STATUS REG<br>MFTCSR   | R<br>W | TOF    | RTIF   | TOFIE  | RTIE   | IRQN   | INHIRQ | RT1    | RT0    |

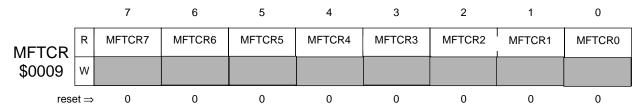

| \$0009 | MFT TIMER COUNTER REG<br>MFTCR  | R<br>W | MFTCR7 | MFTCR6 | MFTCR5 | MFTCR4 | MFTCR3 | MFTCR2 | MFTCR1 | MFTCR0 |

| \$000A | CONFIGURATION REG 1<br>CR1      | R<br>W | PWM15  | PWM14  | PWM13  | PWM12  | PWM11  | PWM10  | PWM9   | PWM8   |

| \$000B | CONFIGURATION REG 2<br>CR2      | R<br>W | HSYNO  | VSYNO  | ADC3   | ADC2   | ADC1   | ADC0   | SCL    | SDA    |

| \$000C | SP CONTROL & STATUS<br>SPCSR    | R<br>W | VSIE   | VEDGE  | VSIF   | COMP   | VINVO  | HINVO  | VPOL   | HPOL   |

| \$000D | VERT FREQUENCY HIGH REG<br>VFHR | R<br>W | VOF    | 0      | 0      | VF12   | VF11   | VF10   | VF9    | VF8    |

| \$000E | VERT FREQUENCY LOW REG<br>VFLR  | R<br>W | VF7    | VF6    | VF5    | VF4    | VF3    | VF2    | VF1    | VF0    |

| \$000F | HOR FREQUENCY HIGH REG<br>HFHR  | R<br>W | HOVER  | HFH6   | HFH5   | HFH4   | HFH3   | HFH2   | HFH1   | HFH0   |

UNIMPLEMENTED RESERVED

Figure 2-2: MC68HC05BD7 I/O Register \$00-\$0F

| ADDR    | REGISTER                       | REAI<br>WRIT | 1 7    | 6      | 5     | 4     | 3     | 2      | 1      | 0      |

|---------|--------------------------------|--------------|--------|--------|-------|-------|-------|--------|--------|--------|

| \$0010  | HOR FREQUENCY LOW RE           | EG F         | 0      | 0      | 0     | HFL4  | HFL3  | HFL2   | HFL1   | HFL0   |

|         | HFLR                           | V            |        |        |       |       |       |        |        |        |

| \$0011  | SP IO CONTROL REG              | F            | VSYNCS | HSYNCS | COINV |       | SOGIN | CLAMP  | BPOR   | SOUT   |

| 400     | SPIOCR                         | V            | /      |        |       | ///// | 000   |        |        |        |

| \$0012  | PWM OPEN-DRAIN OPTION REGISTER | N F          | 4 PWMO | 6PWMO  | 5PWMO | 4PWMO | зРШМО | 2PWMO  | 1PWMO  | 0PWMO  |

|         | UNIMPLEMENTED                  | F            |        |        |       |       |       |        |        |        |

| \$0013  | ONIMI ELIMENTED                | v            | 7      |        |       |       |       |        |        |        |

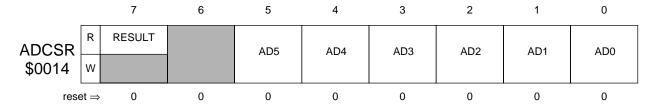

| 00044   | ADC CONTROL/STATUS R           | EG F         | RESULT | -      | ADE   | AD4   | AD2   | ADO    | A D4   | A D0   |

| \$0014  |                                | V            | /      |        | AD5   | AD4   | AD3   | AD2    | AD1    | AD0    |

| \$0015  | ADC CHANNEL REGISTER           | F            | 2      |        |       |       |       |        | CHSL1  | CHSL0  |

| \$0015  |                                | ٧            | /      |        |       |       |       |        | OHIOLI | 011020 |

| \$0016  | DDC MASTER CONTROL F           | REG F        | ALIF   | NAKIF  | ВВ    | MAST  | MRW   | BR2    | BR1    | BR0    |

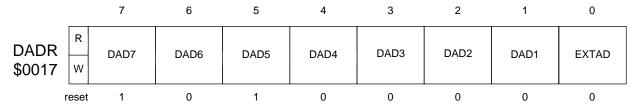

|         | DDC ADDRESS REGISTER           | F            |        |        |       |       | 2.20  | 5.150  | 5.15.  | 5\/T45 |

| \$0017  | DADR                           |              | DAD7   | DAD6   | DAD5  | DAD4  | DAD3  | DAD2   | DAD1   | EXTAD  |

| \$0018  | DDC CONTROL REGISTER           | ę F          | → DEN  | DIEN   |       |       | TXAK  | SCLIEN | DDC1EN |        |

|         | DDC STATUS REGISTER            | F            | RXIF   | TXIF   | MATCH | RW    | RXAK  | SCLIF  | TXBE   | RXBF   |

| \$0019  | DSR                            | V            | 1      |        |       |       |       |        |        |        |

| 00044   | DDC DATA TRANSMIT REC          | 3 F          | DTD7   | DTD6   | DTD5  | DTD4  | DTD3  | DTD2   | DTD1   | DTD0   |

| \$001A  | DDTR                           | V            |        | DIDO   | 0103  | 0104  | 0103  | 0102   |        | D100   |

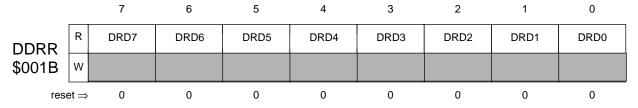

| \$001B  | DDC DATA RECEIVE REG           | F            | DRD7   | DRD6   | DRD5  | DRD4  | DRD3  | DRD2   | DRD1   | DRD0   |

| \$00 IB | DDRR                           | ٧            | /      |        |       |       |       |        |        |        |

| \$001C  | UNIMPLEMENTED                  | F            |        |        |       |       |       |        |        |        |

| ψ0010   |                                | V            | 1      |        |       |       |       |        |        |        |

| \$001D  | RESERVED FOR EPROM             | F            |        |        |       |       |       |        | ELAT   | PGM    |

| \$5515  | CONTROL PCR                    | V            |        | /////  | ///// |       | ///// | /////  |        | 2      |

| \$001E  | UNIMPLEMENTED                  | F            | -      |        |       |       |       |        |        |        |

| \$001F  | RESERVED                       | F            |        |        |       |       | 1111  |        |        |        |

| ΦUUTE   |                                | V            |        |        |       |       |       |        |        |        |

Figure 2-3: MC68HC05BD7 I/O Register \$10-\$1F

UNIMPLEMENTED

**SECTION 2: MEMORY**

RESERVED

| ADDR   | REGISTER                      | READ<br>WRITE | 1 7    | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|-------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

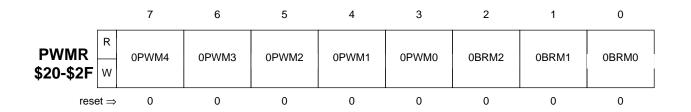

| \$0020 | PULSE WIDTH MODULATO<br>OPWM  | R R<br>W      | 0PWM4  | 0PWM3  | 0PWM2  | 0PWM1  | 0PWM0  | 0BRM2  | 0BRM1  | 0BRM0  |

| \$0021 | PULSE WIDTH MODULATO<br>1PWM  | R R<br>W      | 1PWM4  | 1PWM3  | 1PWM2  | 1PWM1  | 1PWM0  | 1BRM2  | 1BRM1  | 1BRM0  |

| \$0022 | PULSE WIDTH MODULATO<br>2PWM  | R R<br>W      | 2PWM4  | 2PWM3  | 2PWM2  | 2PWM1  | 2PWM0  | 2BRM2  | 2BRM1  | 2BRM0  |

| \$0023 | PULSE WIDTH MODULATO<br>3PWM  | R R<br>W      | 3PWM4  | 3PWM3  | 3PWM2  | 3PWM1  | 3PWM0  | 3BRM2  | 3BRM1  | 3BRM0  |

| \$0024 | PULSE WIDTH MODULATO<br>4PWM  | R R<br>W      | 4PWM4  | 4PWM3  | 4PWM2  | 4PWM1  | 4PWM0  | 4BRM2  | 4BRM1  | 4BRM0  |

| \$0025 | PULSE WIDTH MODULATO<br>5PWM  | R R<br>W      | 5PWM4  | 5PWM3  | 5PWM2  | 5PWM1  | 5PWM0  | 5BRM2  | 5BRM1  | 5BRM0  |

| \$0026 | PULSE WIDTH MODULATO<br>6PWM  | R R           | 6PWM4  | 6PWM3  | 6PWM2  | 6PWM1  | 6PWM0  | 6BRM2  | 6BRM1  | 6BRM0  |

| \$0027 | PULSE WIDTH MODULATO<br>7PWM  | R R<br>W      | 7PWM4  | 7PWM3  | 7PWM2  | 7PWM1  | 7PWM0  | 7BRM2  | 7BRM1  | 7BRM0  |

| \$0028 | PULSE WIDTH MODULATO<br>8PWM  | R R<br>W      | 8PWM4  | 8PWM3  | 8PWM2  | 8PWM1  | 8PWM0  | 8BRM2  | 8BRM1  | 8BRM0  |

| \$0029 | PULSE WIDTH MODULATO<br>9PWM  | R R<br>W      | 9PWM4  | 9PWM3  | 9PWM2  | 9PWM1  | 9PWM0  | 9BRM2  | 9BRM1  | 9BRM0  |

| \$002A | PULSE WIDTH MODULATO<br>10PWM | R R<br>W      | 10PWM4 | 10PWM3 | 10PWM2 | 10PWM1 | 10PWM0 | 10BRM2 | 10BRM1 | 10BRM0 |

| \$002B | PULSE WIDTH MODULATO<br>11PWM | R R<br>W      | 11PWM4 | 11PWM3 | 11PWM2 | 11PWM1 | 11PWM0 | 11BRM2 | 11BRM1 | 11BRM0 |

| \$002C | PULSE WIDTH MODULATO<br>12PWM | R R<br>W      | 12PWM4 | 12PWM3 | 12PWM2 | 12PWM1 | 12PWM0 | 12BRM2 | 12BRM1 | 12BRM0 |

| \$002D | PULSE WIDTH MODULATO<br>13PWM | R R           | 13PWM4 | 13PWM3 | 13PWM2 | 13PWM1 | 13PWM0 | 13BRM2 | 13BRM1 | 13BRM0 |

| \$002E | PULSE WIDTH MODULATO<br>14PWM | R R<br>W      | 14PWM4 | 14PWM3 | 14PWM2 | 14PWM1 | 14PWM0 | 14BRM2 | 14BRM1 | 14BRM0 |

| \$002F | PULSE WIDTH MODULATO          | R R           | 15PWM4 | 15PWM3 | 15PWM2 | 15PWM1 | 15PWM0 | 15BRM2 | 15BRM1 | 15BRM0 |

UNIMPLEMENTED RESERVED RESERVED

Figure 2-4: MC68HC05BD7 I/O Register \$20-\$2F

www.DataSheet4U.com

### 2.1 COP

The COP time-out is prevented by writing a '0' to bit 0 of address \$3FF0. See **SECTION 11** for detail.

### 2.2 **ROM**

For MC68HC05BD7, the user ROM consists of 11.75K bytes of ROM from \$1000 through \$3EFF and 16 bytes of user vectors from \$3FF0 through \$3FFF. For MC68HC05BD2, the user ROM consists of 5.75K bytes of ROM from \$2800 through \$3EFF and 16 bytes of user vectors from \$3FF0 through \$3FFF. The Self-Check ROM is located from \$3F00 through \$3FE0 and Self-Check vectors are located from \$3FE0 through \$3FEF.

### 2.3 EPROM

For MC68HC705BD7, the user EPROM consists of 11.5K bytes of EPROM from \$1000 through \$3DFF and 16 bytes of user vectors from \$3FF0 through \$3FFF. The Bootstrap ROM is located from \$0E00 through \$0FDF and Bootstrap vectors are located from \$3FE0 through \$3FEF, at the same location as Self-Check vectors.

### 2.4 RAM

The user RAM consists of 384 bytes from \$0030 to \$01AF for HC05BD7/HC705BD7. User RAM consists of 256 bytes from \$30 to \$12F for HC05BD2. The stack pointer can access 64 bytes of RAM from \$00FF to \$00C0. See **Section 3.1.3, Stack Pointer (SP)**.

NOTE: Using the stack area for data storage or temporary work locations requires care to prevent it from being overwritten due to stacking from an interrupt or subroutine call.

THIS PAGE INTENTIONALLY LEFT BLANK

**SECTION 3**

### **CPU CORE**

The MC68HC05BD7 has a 16K memory map. Therefore it uses only the lower 14 bits of the address bus. In the following discussion the upper 2 bits of the address bus can be ignored. The stack has only 64 bytes. Therefore, the stack pointer has been reduced to only 6 bits and will only decrement down to \$00C0 and then wrap-around to \$00FF. All other instructions and registers behave as described in this chapter.

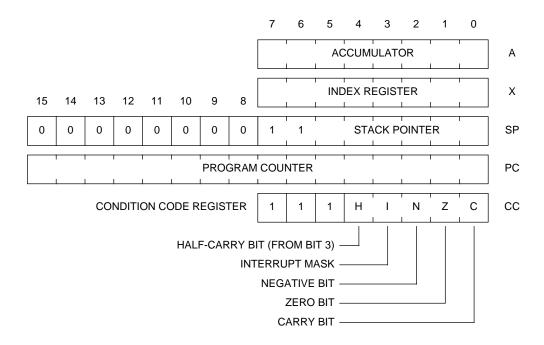

### 3.1 Registers

The MCU contains five registers which are hard-wired within the CPU and are not part of the memory map. These five registers are shown in **Figure 3-1** and are described in the following paragraphs.

Figure 3-1: MC68HC05 Programming Model

### 3.1.1 Accumulator (A)

The accumulator is a general purpose 8-bit register as shown in **Figure 3-1**. The CPU uses the accumulator to hold operands and results of arithmetic calculations or non-arithmetic operations. The accumulator is not affected by a reset of the device.

**SECTION 3: CPU CORE**

### 3.1.2 Index Register (X)

The index register shown in **Figure 3-1** is an 8-bit register that can perform two functions:

- Indexed addressing

- Temporary storage

In indexed addressing with no offset, the index register contains the low byte of the operand address, and the high byte is assumed to be \$00. In indexed addressing with an 8-bit offset, the CPU finds the operand address by adding the index register content to an 8-bit immediate value. In indexed addressing with a 16-bit offset, the CPU finds the operand address by adding the index register content to a 16-bit immediate value.

The index register can also serve as an auxiliary accumulator for temporary storage. The index register is not affected by a reset of the device.

### 3.1.3 Stack Pointer (SP)

The stack pointer shown in **Figure 3-1** is a 16-bit register. In MCU devices with memory space less than 64K bytes the unimplemented upper address lines are ignored. The stack pointer contains the address of the next free location on the stack. During a reset or the reset stack pointer (RSP) instruction, the stack pointer is set to \$00FF. The stack pointer is then decremented as data is pushed onto the stack and incremented as data is pulled off the stack.

When accessing memory, the ten most significant bits are permanently set to 0000000011. The six least significant register bits are appended to these ten fixed bits to produce an address within the range of \$00FF to \$00C0. Subroutines and interrupts may use up to 64 (\$40) locations. If 64 locations are exceeded, the stack pointer wraps around and overwrites the previously stored information. A subroutine call occupies two locations on the stack and an interrupt uses five locations.

### 3.1.4 Program Counter (PC)

The program counter shown in **Figure 3-1** is a 16-bit register. In MCU devices with memory space less than 64K bytes the unimplemented upper address lines are ignored. The program counter contains the address of the next instruction or operand to be fetched.

Normally, the address in the program counter increments to the next sequential memory location every time an instruction or operand is fetched. Jump, branch, and interrupt operations load the program counter with an address other than that of the next sequential location.

### 3.1.5 Condition Code Register (CCR)

The CCR shown in **Figure 3-1** is a 5-bit register in which four bits are used to indicate the results of the instruction just executed. The fifth bit is the interrupt mask. These bits can be individually tested by a program, and specific actions can be taken as a result of their states. The condition code register should be thought of as having three additional upper bits that are always ones. Only the interrupt mask is affected by a reset of the device. The following paragraphs explain the functions of the lower five bits of the condition code register.

**SECTION 3: CPU CORE**

www.DataSheet4U.com

### 3.1.5.1 Half Carry Bit (H-Bit)

When the half-carry bit is set, it means that a carry occurred between bits 3 and 4 of the accumulator during the last ADD or ADC (add with carry) operation. The half-carry bit is required for binary-coded decimal (BCD) arithmetic operations.

### 3.1.5.2 Interrupt Mask (I-Bit)

When the interrupt mask is set, the internal and external interrupts are disabled. Interrupts are enabled when the interrupt mask is cleared. When an interrupt occurs, the interrupt mask is automatically set after the CPU registers are saved on the stack, but before the interrupt vector is fetched. If an interrupt request occurs while the interrupt mask is set, the interrupt request is latched. Normally, the interrupt is processed as soon as the interrupt mask is cleared.

A return from interrupt (RTI) instruction pulls the CPU registers from the stack, restoring the interrupt mask to its state before the interrupt was encountered. After any reset, the interrupt mask is set and can only be cleared by the Clear I-Bit (CLI), or WAIT instructions.

### 3.1.5.3 Negative Bit (N-Bit)

The negative bit is set when the result of the last arithmetic operation, logical operation, or data manipulation was negative. (Bit 7 of the result was a logical one.)

The negative bit can also be used to check an often tested flag by assigning the flag to bit 7 of a register or memory location. Loading the accumulator with the contents of that register or location then sets or clears the negative bit according to the state of the flag.

### 3.1.5.4 Zero Bit (Z-Bit)

The zero bit is set when the result of the last arithmetic operation, logical operation, data manipulation, or data load operation was zero.

### 3.1.5.5 Carry/Borrow Bit (C-Bit)

The carry/borrow bit is set when a carry out of bit 7 of the accumulator occurred during the last arithmetic operation, logical operation, or data manipulation. The carry/borrow bit is also set or cleared during bit test and branch instructions and during shifts and rotates. This bit is neither set by an INC nor by a DEC instruction.

**SECTION 3: CPU CORE**

THIS PAGE INTENTIONALLY LEFT BLANK

### **SECTION 4**

### **INTERRUPTS**

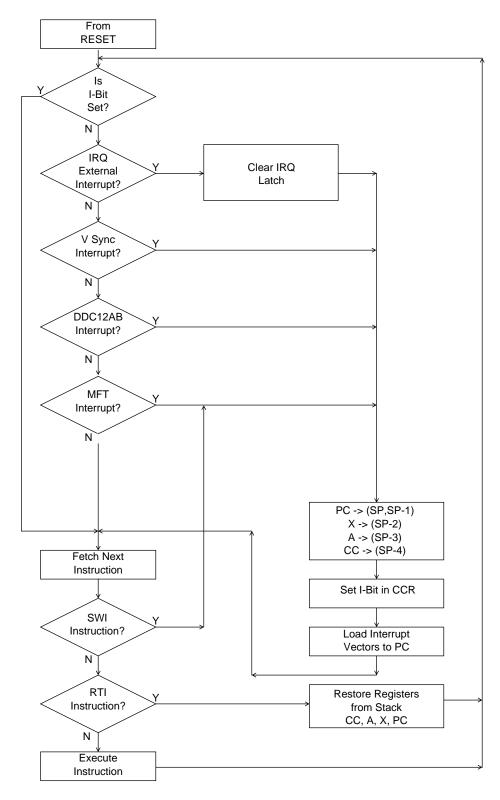

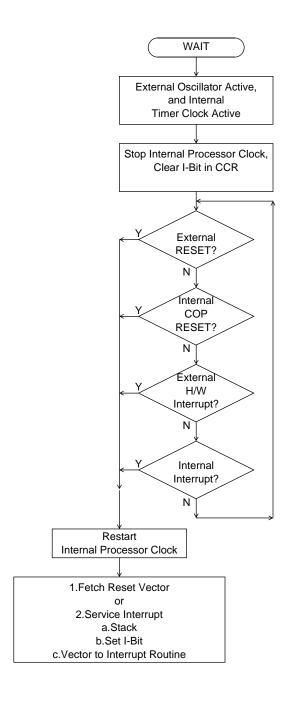

### 4.1 CPU Interrupt Processing

Interrupts cause the processor to save register contents on the stack and to set the interrupt mask (I-bit) to prevent additional interrupts. Unlike RESET, hardware interrupts do not cause the current instruction execution to be halted, but are considered pending until the current instruction is complete.

If interrupts are not masked (I-bit in the CCR is cleared) and the corresponding interrupt enable bit is set the processor will proceed with interrupt processing. Otherwise, the next instruction is fetched and executed. If an interrupt occurs the processor completes the current instruction, then stacks the current CPU register states, sets the I-bit to inhibit further interrupts, and finally checks the pending hardware interrupts. If more than one interrupt is pending following the stacking operation, the interrupt with the highest vector location shown in **Table 4-1** will be serviced first. The SWI is executed the same as any other instruction, regardless of the I-bit state.

When an interrupt is to be processed the CPU fetches the address of the appropriate interrupt software service routine from the vector table at locations \$3FF0 thru \$3FFF as defined in **Table 4-1**.

Table 4-1: Vector Address for Interrupts and Reset

| Register | Flag  | Interrupts          | CPU Int | Vector Adds.  |

|----------|-------|---------------------|---------|---------------|

| N/A      | N/A   | Reset               | RESET   | \$3FFE-\$3FFF |

| N/A      | N/A   | Software            | SWI     | \$3FFC-\$3FFD |

| N/A      | N/A   | External Interrupt  | IRQ     | \$3FFA-\$3FFB |

| SPCSR    | VSIF  | VSINT               | SP      | \$3FF8-\$3FF9 |

| DMCR     | TXIF  | DDC12AB interrupt   | DDC12AB | \$3FF6-\$3FF7 |

| DSR      | RXIF  |                     |         |               |

|          | ALIF  |                     |         |               |

|          | NAKIF |                     |         |               |

|          | SCLIF |                     |         |               |

| MFTCSR   | TOF   | Timer Overflow      | MFT     | \$3FF4-\$3FF5 |

|          | RTIF  | Real Time Interrupt |         |               |

| N/A      | N/A   | N/A                 | N/A     | \$3FF2-\$3FF3 |

| N/A      | N/A   | N/A                 | N/A     | \$3FF0-\$3FF1 |

An RTI instruction is used to signify when the interrupt software service routine is completed. The RTI instruction causes the register contents to be recovered from the stack and normal processing to resume at the next instruction that was to be executed when the interrupt took place. **Figure 4-1** shows the sequence of events that occur during interrupt processing.

Figure 4-1: Interrupt Processing Flowchart

### 4.2 Reset Interrupt Sequence

The RESET function is not in the strictest sense an interrupt; however, it is acted upon in a similar manner. A low level input on the RESET pin or an internally generated reset signal causes the program to vector to its starting address which is specified by the contents of \$3FFE and \$3FFF. The I-bit in the condition code register is also set. The MCU is configured to a known state during this type of reset as described in **SECTION 5**.

### 4.3 Software Interrupt (SWI)

The SWI is an executable instruction and a non-maskable interrupt since it is executed regardless of the state of the I-bit in the CCR. If the I-bit is zero (interrupts enabled), the SWI instruction executes after interrupts which were pending before the SWI was fetched, or before interrupts generated after the SWI was fetched. The interrupt service routine address is specified by the contents of \$3FFC and \$3FFD.

### 4.4 Hardware Interrupts

All hardware interrupts except RESET are maskable by the I-bit in the CCR. If the I-bit is set, all hardware interrupts (internal and external) are disabled. Clearing the I-bit enables the hardware interrupts. There are four types of hardware interrupts which are explained in the following sections.

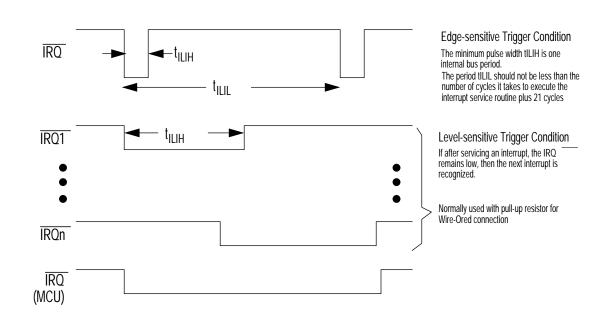

### 4.4.1 External Interrupt (IRQ)

If the IRQ option is edge and level sensitive triggering (IRQN=0), a low level at the IRQ pin and a cleared interrupt mask bit of the condition code register will cause an EXTERNAL INTERRUPT to occur. If the MCU has finished with the interrupt service routine, but the IRQ pin is still low, the EXTERNAL INTERRUPT will start again. In fact, the MCU will keep on servicing the EXTERNAL INTERRUPT as long as the IRQ pin is low. If the IRQ pin goes low for a while and resumes to high (a negative pulse) before the interrupt mask bit is cleared, the MCU will not recognize there was an interrupt request, and no interrupt will occur after the interrupt mask bit is cleared.

If the IRQ option is negative edge sensitive triggering (IRQN=1), a negative edge occurs at the IRQ pin and a cleared interrupt mask bit of the condition code register will cause an EXTERNAL INTERRUPT to occur. If the MCU has finished with the interrupt service routine, but the IRQ pin has not returned back to high, no further interrupt will be generated. The interrupt logic recognizes negative edge transitions and pulses (special case of negative edges) only. If the negative edge occurs while the interrupt mask bit is set, the interrupt signal will be latched, and interrupt will occur as soon as the interrupt mask bit is cleared. The latch will be cleared by RESET or cleared automatically during fetch of the EXTERNAL INTERRUPT vectors. Therefore, one (and only one) external interrupt edge could be latched while the interrupt mask bit is set. If the INHIRQ bit in the MFT register is set, no IRQ interrupt can be generated.

The service routine address is specified by the contents of \$3FFA and \$3FFB. **Figure 4-2** shows the two methods for the interrupt line ( $\overline{IRQ}$ ) to be recognized by the processor. The first method is single pulses on the interrupt line spaced far apart enough to be serviced. The minimum time between pulses is a function of the number of cycles required to execute

the interrupt service routine plus 21 cycles. Once a pulse occurs, the next pulse should not occur until the MCU software has exited the routine (an RTI occurs). The second configuration shows several interrupt line "wire-ANDed" to perform the interrupts at the processor. Thus, if after servicing one interrupt and the interrupt line remains low, then the next interrupt is recognized.

NOTE: IRQN is located at bit 3 of the Multi-function Timer Register at \$0008, and is cleared by reset.

Figure 4-2: External Interrupt

### 4.4.2 VSYNC Interrupt

The VSYNC interrupt is generated when a specific edge of VSYNC input is detected as described in **SECTION 10**. The interrupt enable bit, VSIE, for the VSYNC interrupt is located at bit 7 of SYNC Processor Control and Status Register (SPCSR) at \$000C. The I-bit in the CCR must be cleared in order for the VSYNC interrupt to be enabled. This interrupt will vector to the interrupt service routine located at the address specified by the contents of \$3FF8 and \$3FF9. The VSYNC Interrupt Flag (VSIF) must be cleared by writing '0' to it in the interrupt routine.

### 4.4.3 DDC12AB Interrupt

The DDC12AB interrupt is generated by the DDC12AB circuit as described in **SECTION 9**. The interrupt enable bit for the DDC12AB interrupt is located at bit 6 of DDC12AB Control Register (DCR) at \$0018. The I-bit in the CCR must be cleared in order for the DDC12AB interrupt to be enabled. This interrupt will vector to the interrupt service routine located at the address specified by the contents of \$3FF6 and \$3FF7.

www.DataSheet4U.com

### 4.4.4 Multi-Function Timer Interrupt (MFT)

There are two different Multi-Function Timer (MFT) interrupt flags that will cause an interrupt whenever they are set and enabled. The interrupt flags and enable bits are located in the MFT Control and Status Register. Either of these interrupts will vector to the same interrupt service routine, located at the address specified by the contents of \$3FF4 and \$3FF5. See **Section SECTION 11, MULTI-FUNCTION TIMER** for more informations on MFT interrupts.

THIS PAGE INTENTIONALLY LEFT BLANK

SECTION 5 RESETS

The MCU can be reset from four sources—1 external and 3 internal:

- External RESET pin

- Power-On-Reset (POR)

- Computer Operating Properly Watchdog Reset (COPR)

- Illegal Address Reset (ILADR)

# 5.1 External Reset (RESET)

The RESET pin is the only external reset source. This pin is connected to a Schmitt trigger input gate to provide an upper and lower threshold voltage separated by a minimum amount of hysteresis. This external reset occurs whenever the RESET pin is pulled below the lower threshold and remains in reset until the RESET pin rises above the upper threshold. This active low input will generate the RST signal and reset the CPU and peripherals. Termination of the external RESET input can alter the operating mode of the MCU.

NOTE: Activation of the RST signal is generally referred to as reset of the device, unless otherwise specified.

### 5.2 Internal Resets

The three internally generated resets are the initial power-on reset, the COP Watchdog Timer reset, and the illegal address reset

### 5.2.1 Power-On Reset (POR)

The internal POR is generated on power-up to allow the clock oscillator to stabilize. The POR is strictly for power-on condition and is not able to detect a drop in the power supply voltage (brown-out). There is an oscillator stabilization delay of 4065 internal processor bus clock cycles (PH2) after the oscillator becomes active.

The POR will generate the RST signal which will reset the CPU. If any other reset function is active at the end of this 4065 cycles delay, the RST signal will remain in the reset condition until the other reset condition(s) end.

### 5.2.2 Computer Operating Properly Reset (COPR)

The internal COPR reset is generated automatically (if enabled) by a time-out of the COP Watchdog Timer. This time-out occurs if the counter in the COP Watchdog Timer is not reset (cleared) within a specific time by a program reset sequence. Refer to **SECTION 11** for more information on this time-out feature.

**SECTION 5: RESETS**

### 5.2.3 Illegal Address (ILADR) Reset

The MCU monitors all opcode fetches. If an illegal address is accessed during an opcode fetch, an internal reset is generated. Illegal address space consists of all unused locations within the memory space and the I/O registers. (See **Figure 2-1 : The 16K Memory Map of the MC68HC05BD7**.) Because the internal reset signal is used, the MCU comes out of an ILADR Reset in the same operating mode it was in when the opcode was fetched. The ILADR Reset is disabled in Test (Non User) Mode.

**SECTION 5: RESETS**

# **SECTION 6**

# **OPERATING MODES**

The HC05BD7/HC05BD2 has the following operating modes: single-chip mode (SCM) and self-check mode.

The HC705BD7 has the following operating modes: User mode and bootstrap mode.

### 6.1 User Mode

In this mode, all address and data bus activity occurs within the MCU so no external pins are required for these functions.

### 6.2 SELF-CHECK MODE

In this mode, the reset vector is fetched from the 240-byte internal self-check ROM at \$3F00:\$3FEF. The self-check ROM contains a self-check program to test the functions of internal modules.

# 6.3 Bootstrap Mode

In this mode, the reset vector is fetched from the 480-byte internal bootstrap ROM at \$0E00:\$0FDF. The bootstrap ROM contains a small program which reads a program into internal RAM and then passes control to execute EPROM programming.

# 6.4 Mode Entry

The mode entry is done at the rising edge of the RESET pin. Once the device enters one of the operating modes, the mode can only be changed by an external reset.

At the rising edge of the RESET pin, the device latches the states of IRQ and PB5 pins and places itself in the specified mode. While the RESET pin is low, all pins are configured as Single Chip Mode. The following table shows the states of IRQ and PB5 pins for each mode entry.

| Table | 6-1: | Mode | Select | Summary |

|-------|------|------|--------|---------|

|-------|------|------|--------|---------|

| MODE                 | RESET | ĪRQ              | PB5 |

|----------------------|-------|------------------|-----|

| USER MODE            |       | L or H           | X   |

| SELF CHECK/BOOTSTRAP |       | V <sub>TST</sub> | H   |

$V_{TST} = 1.8 \times VDD$

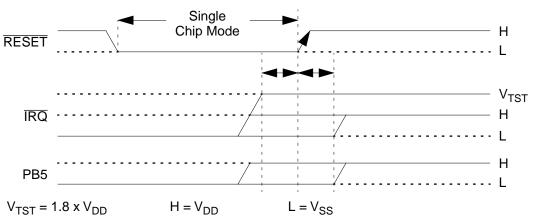

Figure 6-1: Mode Entry Diagram

### 6.5 EPROM Programming

The 11.5K bytes of USER EPROM is positioned at \$1000 through \$3DFF with the vector space from \$3FF0 to \$3FFF. The erased state of EPROM is read as \$FF and EPROM power is supplied from VPP and VDD pins.

The Programming Control Register (PCR) is provided for the EPROM programming. The function of EPROM depends on the device operating mode.

In the User Mode, ELAT and PGM bits in the PCR are available for the user read/write and the remaining test bits become read only bits.

Please contact Motorola for Programming boards availability.

### 6.5.1 Programming Sequence

The EPROM programming is as follows:

- Set the ELAT bit

- Write the data to the address to be programmed

- Set the PGM bit

- Delay for the appropriate amount of time

- Clear the PGM and the ELAT bit

The last item may be done on a single CPU write. It is important to remember that an external programming voltage must be applied to the VPP pin while programming, but it should remain between VDD and VSS during normal operation.

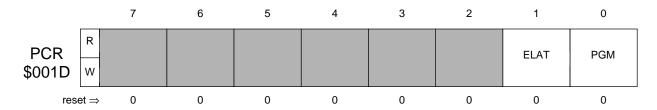

### 6.5.2 Programming Control Register (PCR)

Program control register is provided for EPROM programming the device.

### **ELAT—EPROM Latch Control**

- 0 EPROM address and data bus configured for normal read.

- 1 EPROM address and data bus configured for programming (writes to EPROM cause address and data to be latched). EPROM is in programming mode and can not be read. This bit is not writable to 1 when no VPP voltage is applied to the VPP pin.

### PGM—EPROM Program Command

- 0 Programming power to EPROM array is switched off.

- 1 Programming power to EPROM array is switched on.

### 6.6 Low Power Modes

The MC68HC05BD7 has ONLY ONE low-power operational mode. The WAIT instruction provides the only mode that reduces the power required for the MCU by stopping CPU internal clock. The WAIT instruction is not normally used if the COP Watchdog Timer is enabled. **The STOP instruction is not implemented in its normal sense**. The STOP instruction will be interpreted as the NOP instruction by the CPU if it is ever encountered. The flow of the WAIT mode is shown in **Figure 6-2**.

### 6.6.1 STOP Instruction

Since the execution of a normal STOP instruction results in the stoppage of clocks to all modules, including the COP Watchdog Timer, this instruction is hence not implemented in its usual way to make COP Watchdog Timer meaningful in monitor applications. Execution of the STOP instruction will be the same as that of the NOP instruction. Hence, I bit in the Condition Code Register will not be cleared.

### 6.6.2 WAIT Instruction

In the WAIT Mode the internal processor clock is halted, suspending all processor and internal bus activity. Other Internal clocks remain active, permitting interrupts to be generated from the Multi-Function Timer, or a reset to be generated from the COP Watchdog Timer. The Timer may be used to generate a periodic exit from the WAIT Mode. Execution of the WAIT instruction automatically clears the I-bit in the Condition Code Register, so that any hardware interrupt can wake up the MCU. All other registers, memory, and input/output lines remain in their previous states.