#### **CRYSTAL-LESS SOC RF TRANSMITTER**

#### Single Coin-cell Battery Transmitter

- Supply voltage: 1.8 to 3.6 V

- Standby current < 10 nA</li>

- Crystal-less operation

- Temperature range –40 to +85 °C

- Automotive quality option, AEC-Q100

- 10-pin MSOP/14-pin SOIC

- Pb free/RoHS compliant

#### **RF Transmitter**

- Frequency range: 27—960 MHz

- +10 dBm output power, adjustable

- Automatic antenna tuning

- Symbol rate up to 100 kbps

- FSK/OOK modulation

- Manchester, NRZ, 4/5 encoder

#### **Analog Peripherals**

- LDO regulator with POR circuit

- Integrated temperature sensor

- Battery voltage monitor

#### High-Speed 8051 µC Core

- Pipeline instruction architecture

- 70% of instructions in 1 or 2 clocks

- Up to 24 MIPs with 24 MHz clock

#### Memory

- 4 kB RAM/8kB NVM

- 128 bit EEPROM

- 256 byte of internal data RAM

- 256 byte of external data RAM (XREG)

- 12 kB ROM embedded functions

- 8 byte low leakage RAM

#### **Digital Peripherals**

- 128 bit AES Accelerator

- 4/8 GPIO with wakeup functionality

- 1 LED driver

- Data serializer

- High-speed frequency counter

- RTC, Timers 2, 3

- On-chip debugging C2

#### **Clock Sources**

- High-speed crystal-less VCO

- Programmable low-power osc LPOSC

- Ultra low-power sleep timer

- Optional crystal oscillator input

#### Applications

- Garage and gate door openers

- Home automation and security

- Remote keyless entry

# Si4010

# TABLE OF CONTENTS

| 1. System Overview                                                               |    |

|----------------------------------------------------------------------------------|----|

| 2. Test Circuit                                                                  | 13 |

| 3. Typical Application Schematic                                                 |    |

| 3.1. Si4010 Used in a 5-Button RKE System with LED Indicator                     | 14 |

| 3.2. Si4010 with an External Crystal in a 4-Button RKE System with LED Indicator |    |

| 4. Ordering Information                                                          |    |

| 5. Pin Definitions                                                               |    |

| 5.1. MSOP, Application                                                           | 16 |

| 5.2. MSOP, Programming/Debug Mode                                                | 17 |

| 5.3. SOIC Package, Application                                                   |    |

| 5.4. SOIC Package, Programming/debug Mode                                        | 19 |

| 6. Package Specifications                                                        |    |

| 6.1. 10-Pin MSOP                                                                 |    |

| 6.2. 14-pin SOIC Package                                                         | 21 |

| 7. PCB Land Pattern 10-Pin MSOP                                                  | 22 |

| 8. PCB Land Pattern 14-pin SOIC Package                                          | 24 |

| 9. Electrical Characteristics                                                    | 26 |

| 10. System Description                                                           | 33 |

| 10.1. Overview                                                                   |    |

| 10.2. Setting Basic Si4010 Transmit Parameters                                   | 35 |

| 10.2.1. Package Type                                                             |    |

| 10.2.2. Output Power                                                             | 35 |

| 10.2.3. Modulation, Encoding, and Data Rate                                      | 37 |

| 10.2.4. Output Frequency                                                         |    |

| 10.2.5. Battery Life Calculation                                                 |    |

| 10.3. Applications Programming Interface (API) Commands                          |    |

| 11. Power Amplifier                                                              |    |

| 11.1. Register Description                                                       | 44 |

| 12. Output Data Serializer (ODS)                                                 | 46 |

| 12.1. Description                                                                | 46 |

| 12.2. Timing                                                                     | 46 |

| 12.3. Register Description                                                       |    |

| 13. LC Oscillator (LCOSC)                                                        | 52 |

| 13.1. Register Description                                                       | 52 |

| 14. Low Power Oscillator and System Clock Generator                              | 53 |

| 14.1. Register Description                                                       | 53 |

| 15. Crystal Oscillator (XO)                                                      | 55 |

| 15.1. Register Description                                                       | 55 |

| 16. Frequency Counter                                                            | 56 |

| 16.1. Register Description                                                       |    |

| 17. Sleep Timer                                                                  |    |

| 18. Bandgap and LDO                                                              | 60 |

| 19. Low Leakage HVRAM                                                            |    |

| 20. Temperature Sensor                               | 60  |

|------------------------------------------------------|-----|

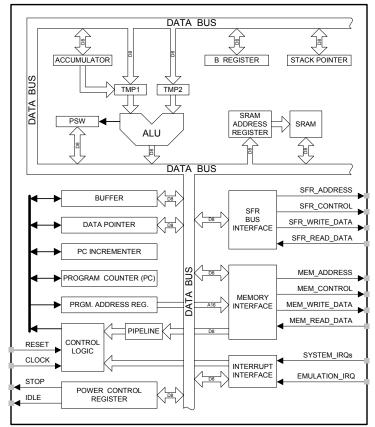

| 21. CIP-51 Microcontroller                           | 61  |

| 21.1. Instruction Set                                | 62  |

| 21.1.1. Instruction and CPU Timing                   | 62  |

| 21.2. CIP-51 Register Descriptions                   | 67  |

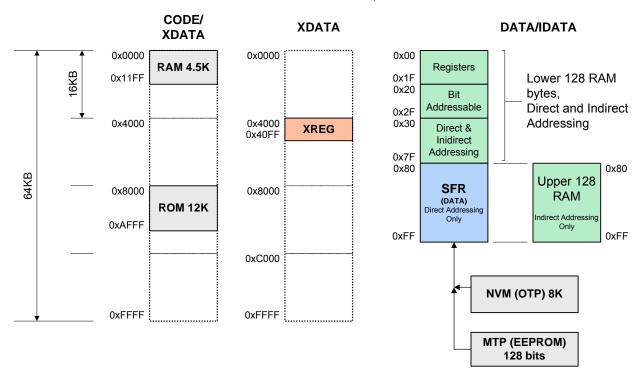

| 22. Memory Organization                              |     |

| 22.1. Program Memory                                 |     |

| 22.2. Internal Data Memory                           | 72  |

| 22.3. External Data Memory                           | 72  |

| 22.4. General Purpose Registers                      | 72  |

| 22.5. Bit Addressable Locations                      | 73  |

| 22.6. Stack                                          | 73  |

| 22.7. Special Function Registers (SFR)               | 73  |

| 22.8. Registers Mapped to XDATA Address Space (XREG) | 73  |

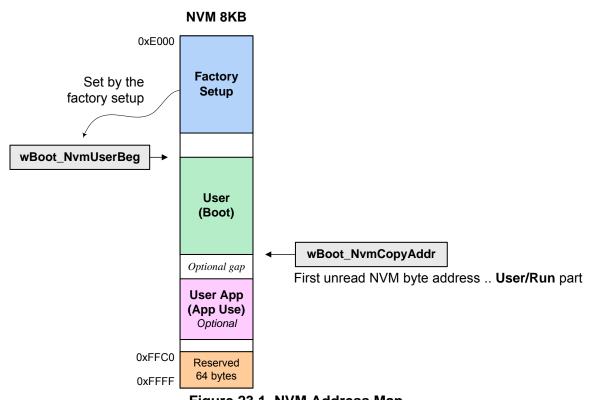

| 22.9. NVM (OTP) Memory                               | 73  |

| 22.10. MTP (EEPROM) Memory                           | 74  |

| 23. System Boot and NVM Programming                  | 75  |

| 23.1. Startup Overview                               |     |

| 23.2. Reset                                          | 76  |

| 23.3. Chip Program Levels                            | 76  |

| 23.4. NVM Organization                               | 77  |

| 23.5. Device Boot Process                            |     |

| 23.6. Error Handling During Boot                     | 79  |

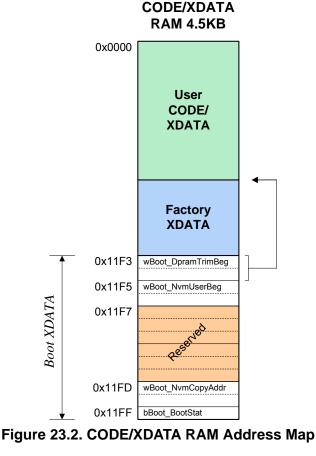

| 23.7. CODE/XDATA RAM Address Map                     | 79  |

| 23.8. Boot Status Variables                          |     |

| 23.9. Boot Routine Destination Address Space         | 84  |

| 23.10. NVM Programming.                              | 85  |

| 23.11. Retest and Retest Configuration               | 86  |

| 23.12. Boot and Retest Protection Control Register   | 88  |

| 23.13. Chip Protection Control Register              | 89  |

| 24. On-Chip Registers                                |     |

| 24.1. Special Function Registers                     | 90  |

| 24.2. XREG Registers                                 | 93  |

| 25. Interrupts                                       |     |

| 25.1. MCU Interrupt Sources and Vectors              | 97  |

| 25.2. Interrupt Priorities                           |     |

| 25.3. Interrupt Latency                              | 97  |

| 25.4. Interrupt Register Descriptions                |     |

| 25.5. External Interrupts                            |     |

| 26. Power Management Modes                           |     |

| 26.1. Idle Mode                                      |     |

| 26.2. Stop Mode                                      |     |

| 27. AES Hardware Accelerator                         |     |

| 27.1. AES SFR Registers                              |     |

| 28. Reset Sources                                    |     |

| 28.1. Device Boot Outline                            | 111 |

# Si4010

| 28.2. External Reset                                                    |     |

|-------------------------------------------------------------------------|-----|

| 28.3. Software Reset                                                    |     |

| 29. Port Input/Output                                                   |     |

| 29.1. GPIO Pin Special Roles                                            | 115 |

| 29.2. Pullup Roff Option                                                | 116 |

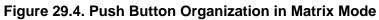

| 29.3. Matrix Mode Option                                                |     |

| 29.4. Pullup Roff and Matrix Mode Option Control                        | 118 |

| 29.5. Special GPIO Modes Control                                        | 119 |

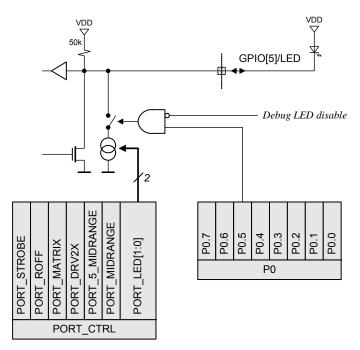

| 29.6. LED Driver on GPIO[5]                                             | 121 |

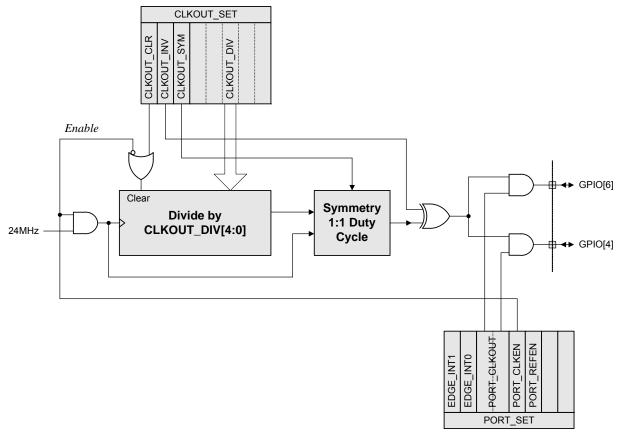

| 30. Clock Output Generation                                             | 127 |

| 30.1. Register Description                                              | 128 |

| 31. Control and System Setting Registers                                | 130 |

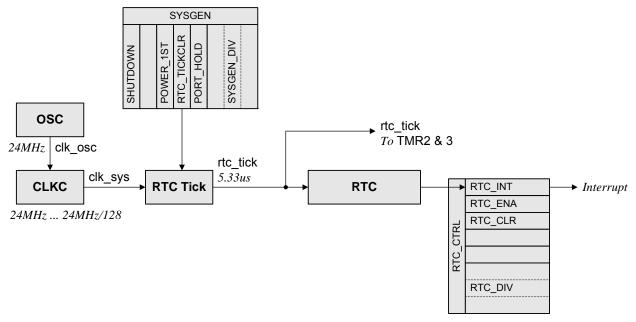

| 32. Real Time Clock Timer                                               |     |

| 32.1. RTC Interrupt Flag Time Uniformity                                | 133 |

| 32.2. Register Description                                              |     |

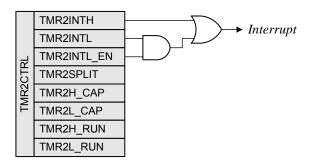

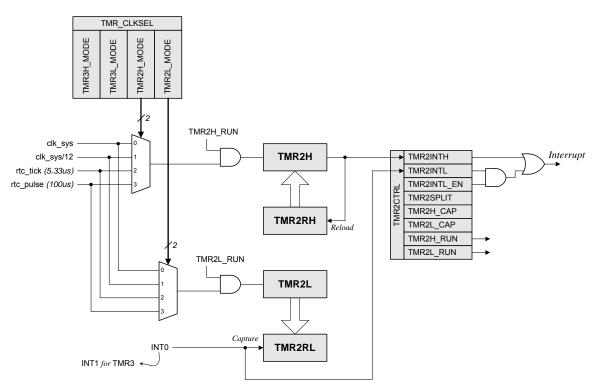

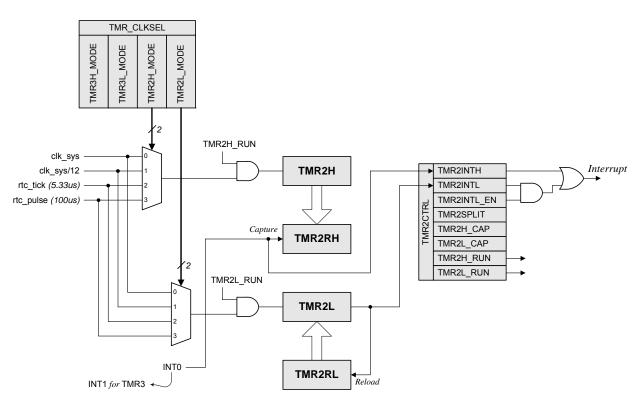

| 33. Timers 2 and 3                                                      |     |

| 33.1. Interrupt Flag Generation                                         |     |

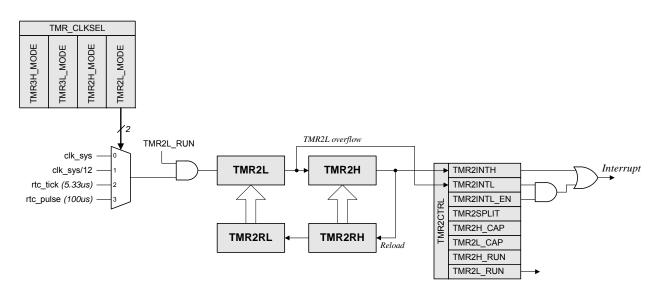

| 33.2. 16-bit Timer with Auto Reload (Wide Mode)                         | 137 |

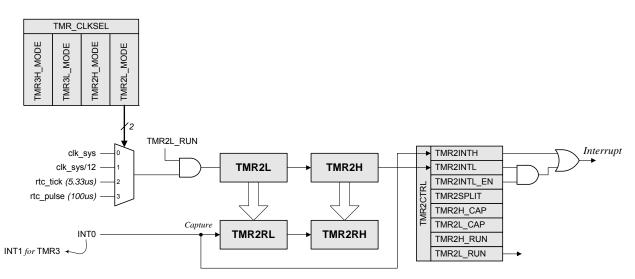

| 33.3. 16-bit Capture Mode (Wide Mode)                                   |     |

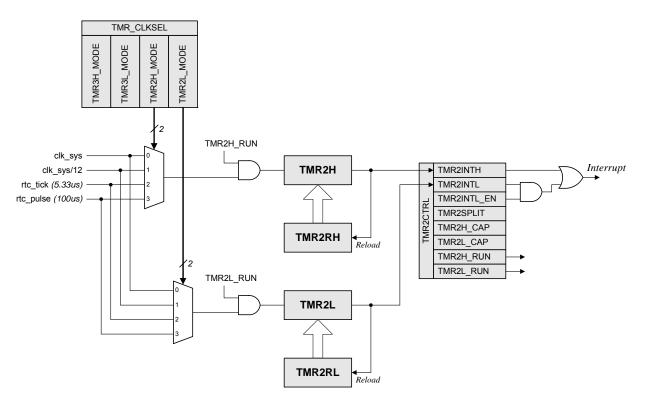

| 33.4. 8-bit Timer/Timer Mode (Split Mode)                               |     |

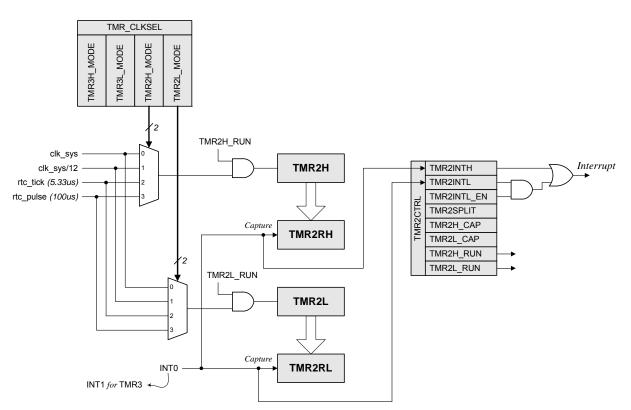

| 33.5. 8-bit Capture/Capture Mode (Split Mode)                           |     |

| 33.6. 8-bit Timer/Capture Mode (Split Mode)                             |     |

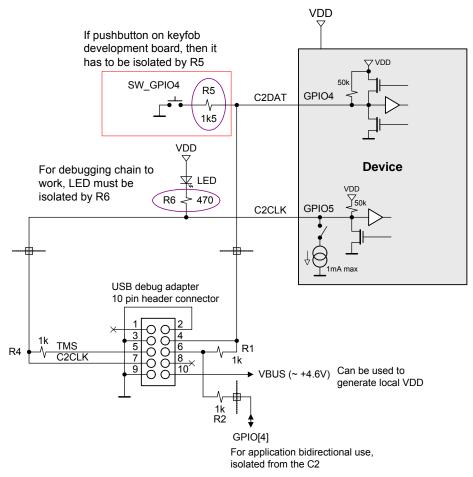

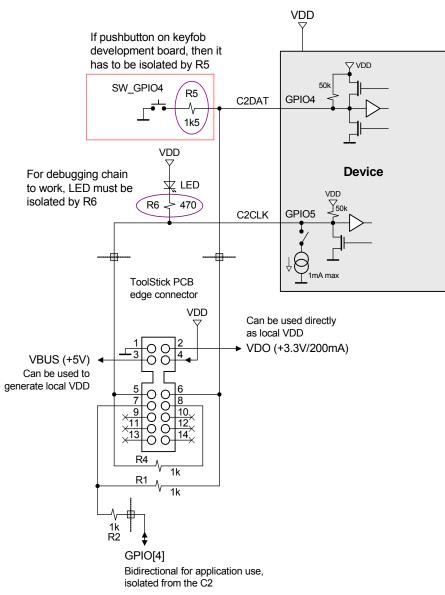

| 34. C2 Interface                                                        |     |

| 34.1. C2 Pin Sharing                                                    |     |

| 35. IDE Development Environment and Debugging Chain                     |     |

| 35.1. Functionality Limitations While Using IDE Development Environment |     |

| 35.2. Chip Shutdown Limitation                                          |     |

| 35.3. LED Driver Usage while Using IDE Debugging Chain                  |     |

| 35.4. LED Driver and Application Development Issues                     |     |

| 36. Additional Reference Resources                                      |     |

| Document Change List                                                    |     |

| Contact Information                                                     | 160 |

|                                                                         |     |

# LIST OF FIGURES

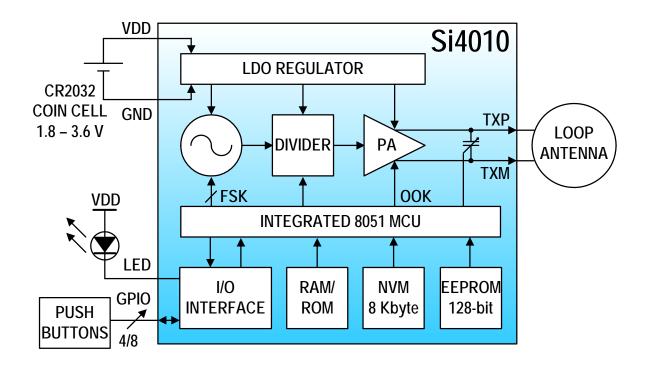

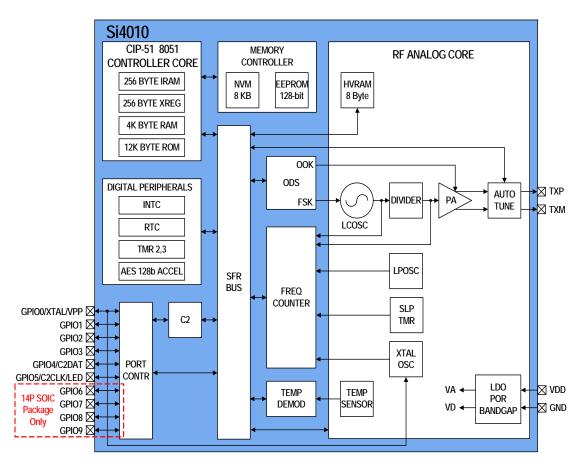

| Figure 1.1. Si4010 Block Diagram                                                        | .12             |

|-----------------------------------------------------------------------------------------|-----------------|

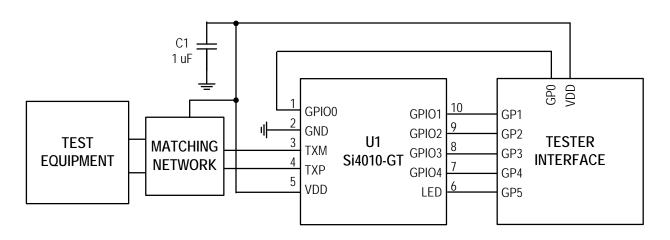

| Figure 2.1. Test Block Diagram with 10-pin MSOP                                         | .13             |

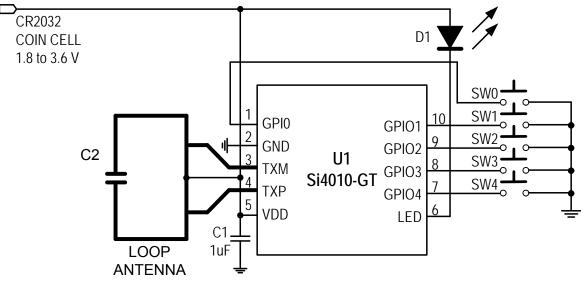

| Figure 3.1. Si4010 Used in a 5-button RKE System with LED Indicator                     |                 |

| Figure 3.2. Si4010 with an External Crystal in a 4-button RKE System with LED Indicator | <sup>.</sup> 14 |

| Figure 6.1. 10-pin MSOP Package                                                         | .20             |

| Figure 6.2. 14-pin SOIC Package                                                         | .21             |

| Figure 7.1. 10-Pin MSOP Recommended PCB Land Pattern                                    | .22             |

| Figure 8.1. 14-pin SOIC Recommended PCB Land Pattern                                    | .24             |

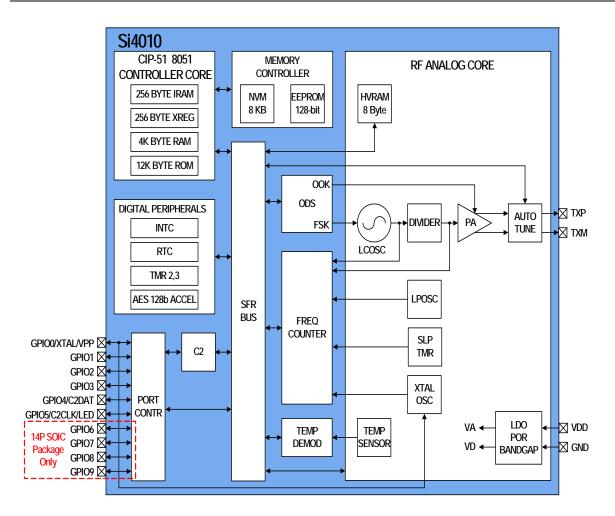

| Figure 10.1. Functional Block Diagram                                                   | .33             |

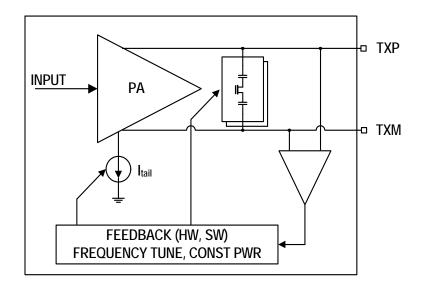

| Figure 11.1. Simplified PA Block Diagram                                                | .42             |

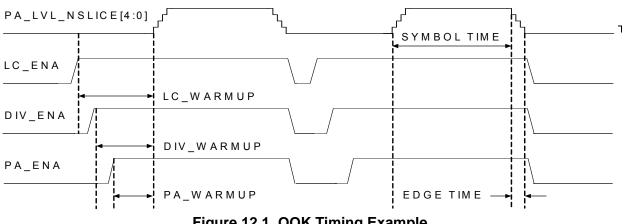

| Figure 12.1. OOK Timing Example                                                         | .46             |

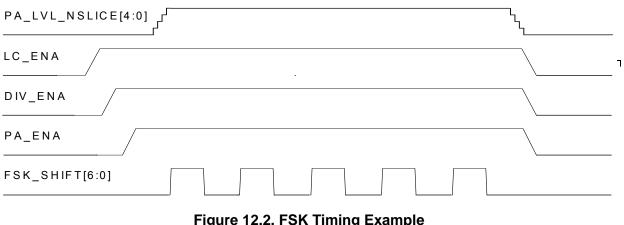

| Figure 12.2. FSK Timing Example                                                         | .46             |

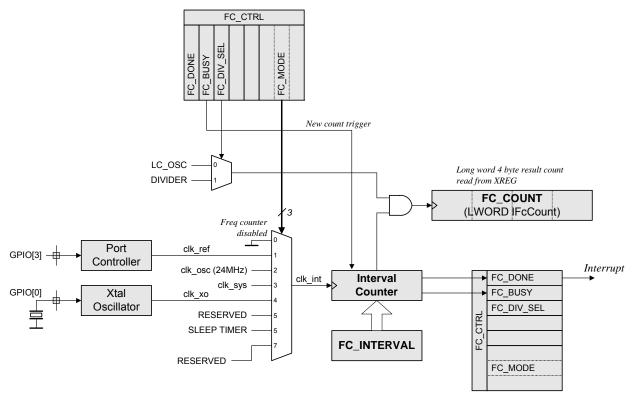

| Figure 16.1. Frequency Counter Block Diagram                                            | .56             |

| Figure 21.1. CIP-51 Block Diagram                                                       |                 |

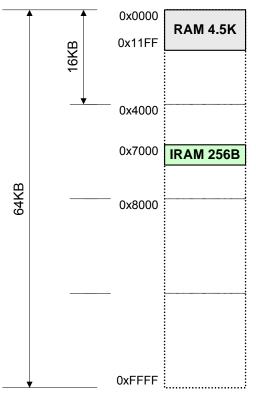

| Figure 22.1. Address Space Map after the Boot                                           | .71             |

| Figure 23.1. NVM Address Map                                                            | .78             |

| Figure 23.2. CODE/XDATA RAM Address Map                                                 |                 |

| Figure 23.3. Boot Routine Destination CPU Address Space for Copy from NVM               | .84             |

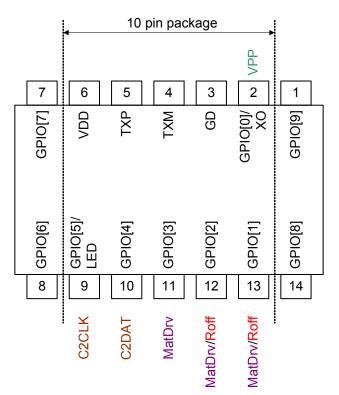

| Figure 29.1. Device Package and Port Assignments                                        | 112             |

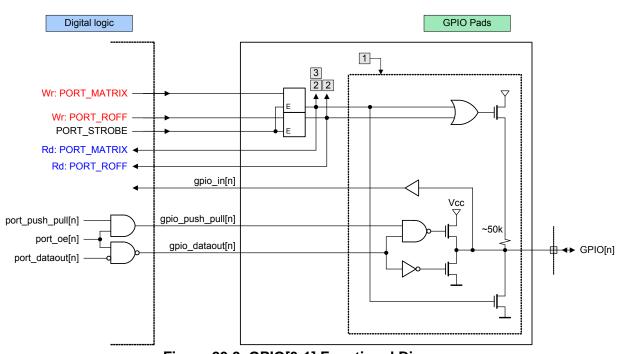

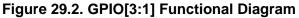

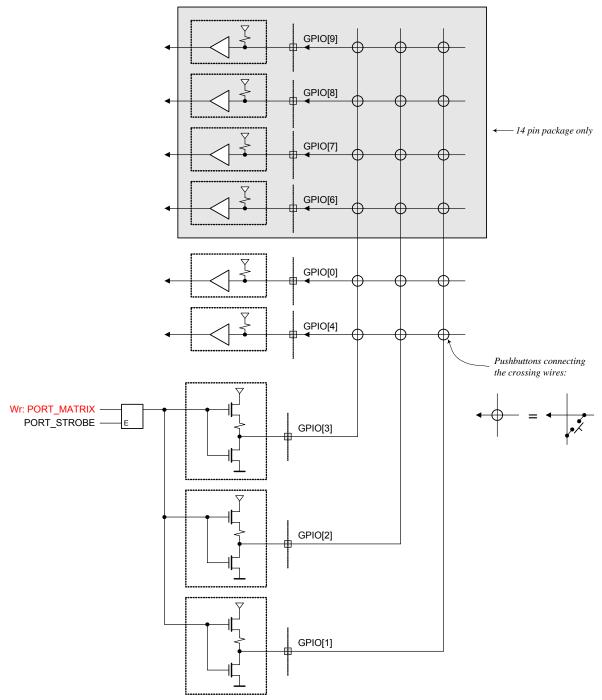

| Figure 29.2. GPIO[3:1] Functional Diagram                                               |                 |

| Figure 29.3. Other GPIO Functional Diagram                                              | 114             |

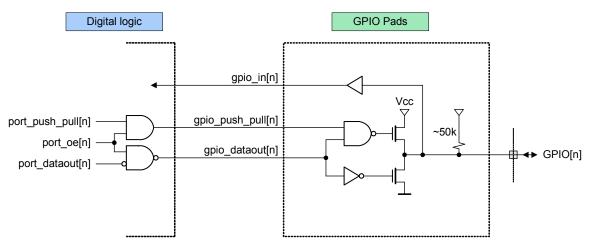

| Figure 29.4. Push Button Organization in Matrix Mode                                    | 117             |

| Figure 29.5. GPIO[5] LED Driver Block Diagram                                           |                 |

| Figure 30.1. Output Clock Generator Block Diagram                                       | 127             |

| Figure 32.1. RTC Timer Block Diagram                                                    | 132             |

| Figure 33.1. Timer Interrupt Generation                                                 | 136             |

| Figure 33.2. Timer 16-bit Mode Block Diagram (Wide Mode)                                | 137             |

| Figure 33.3. Capture 16-bit Mode Block Diagram (Wide Mode)                              | 138             |

| Figure 33.4. Two 8-bit Timers in Timer/Timer Configuration (Split Mode)                 | 139             |

| Figure 33.5. Two 8-bit Timers in Capture/Capture Configuration (Split Mode)             | 140             |

| Figure 33.6. Two 8-bit TImers in Timer/Capture Configuration (Split Mode)               |                 |

| Figure 33.7. Two 8-bit Timers In Capture/Timer Configuration (Split Mode)               | 142             |

| Figure 34.1. 10-pin C2 USB Debugging Adapter Connection to Device                       |                 |

| Figure 34.2. 14-pin C2 ToolStick Connection to Device                                   | 154             |

# LIST OF TABLES

| Table 4.1. Product Selection Guide                              | 15  |

|-----------------------------------------------------------------|-----|

| Table 6.1. Package Dimensions                                   | 20  |

| Table 6.2. Package Dimensions                                   | 21  |

| Table 7.1. 10-Pin MSOP Dimensions                               | 23  |

| Table 8.1. PCB Land Pattern Dimensions                          |     |

| Table 9.1. Recommended Operating Conditions                     | 26  |

| Table 9.2. Absolute Maximum Ratings <sup>1</sup> , <sup>2</sup> | 26  |

| Table 9.3. DC Characteristics                                   | 27  |

| Table 9.4. Si4010 RF Transmitter Characteristics                |     |

| Table 9.5. Low Battery Detector Characteristics                 |     |

| Table 9.6. Optional Crystal Oscillator Characteristics          | 31  |

| Table 9.7. EEPROM Characteristics                               | 31  |

| Table 9.8. Low Power Oscillator Characteristics                 | 32  |

| Table 9.9. Sleep Timer Characteristics                          | 32  |

| Table 21.1. CIP-51 Instruction Set Summary                      | 63  |

| Table 23.1. Boot XDATA Status Variables                         | 81  |

| Table 23.2. Run Chip Retest Protection Flags: NVM Programmer    | 86  |

| Table 24.1. Special Function Register (SFR) Memory Map          |     |

| Table 24.2. Special Function Registers                          |     |

| Table 24.3. XREG Register Memory Map in External Memory         | 94  |

| Table 24.4. XREG Registers                                      | 95  |

| Table 25.1. Interrupt Summary                                   | 98  |

| Table 29.1. 10–Pin Mode                                         | 113 |

| Table 29.2. 14–Pin Mode                                         | 113 |

| Table 29.3. GPIO Special Roles                                  | 115 |

| Table 29.4. GPIO Special Roles Control and Order                | 120 |

# LIST OF XREG REGISTERS

| XREG Definition 11.2. wPA_CAP         | 44 |

|---------------------------------------|----|

| XREG Definition 11.3. bPA TRIM        |    |

| XREG Definition 14.1. bLPOSC_TRIM     |    |

| XREG Definition 15.1. bXO CTRL        |    |

| XREG Definition 16.3. IFC COUNT       | 59 |

| XREG Definition 22.1. abMTP_RDATA[16] | 74 |

# LIST OF SFR REGISTERS

| SFR | Definition | 11.1. | PA_LVL        | 44 |

|-----|------------|-------|---------------|----|

| SFR | Definition | 12.1. | ODS_CTRL      | 47 |

| SFR | Definition | 12.2. | ODS_TIMING    | 48 |

| SFR | Definition | 12.3. | ODS_DATA      | 49 |

| SFR | Definition | 12.4. | ODS_RATEL     | 49 |

| SFR | Definition | 12.5. | ODS_RATEH     | 50 |

| SFR | Definition | 12.6. | ODS_WARM1     | 50 |

|     |            |       | ODS_WARM2     |    |

|     |            |       | LC_FSK        |    |

|     |            |       | SYSGEN        |    |

|     |            |       | FC_CTRL       |    |

|     |            |       | FC_INTERVAL   |    |

|     |            |       | DPL           |    |

|     |            |       | DPH           |    |

|     |            |       | SP            |    |

| -   |            |       | ACC           |    |

|     |            |       | В             |    |

|     |            |       | PSW           |    |

|     |            |       | BOOT_BOOTSTAT |    |

|     |            |       | BOOT_FLAGS    |    |

| SFR | Definition | 23.3. | PROT3_CTRL    | 88 |

|     |            |       | PROTO_CTRL    |    |

|     |            |       | IE            |    |

|     |            |       | IP1           |    |

|     |            |       | EIE11         |    |

|     |            |       | EIP1          |    |

|     |            |       | INT_FLAGS     |    |

|     |            |       | PORT_INTCFG1  |    |

| -   |            | -     | PCON          | -  |

|     |            |       | GFM_DATA1     |    |

|     |            |       | GFM_CONST1    |    |

|     |            |       | SBOX_DATA1    |    |

|     |            |       | P0            |    |

|     |            |       | P0CON         |    |

|     |            |       | P1            |    |

|     |            |       | P1CON         |    |

|     |            |       | P2            |    |

|     |            |       | PORT_CTRL     |    |

|     |            |       | PORT_SET      |    |

|     |            |       | CLKOUT_SET1   |    |

|     |            |       | GPR_CTRL1     |    |

|     |            |       | GPR_DATA1     |    |

| SFR | Definition | 31.3. | RBIT_DATA1    | 31 |

| 134 |

|-----|

| 143 |

| 144 |

| 146 |

| 146 |

| 147 |

| 147 |

| 148 |

| 150 |

| 150 |

| 151 |

| 151 |

|     |

### 1. System Overview

The Si4010 is a fully integrated crystal-less CMOS SoC RF transmitter with an embedded CIP-51 8051 MCU designed for the sub 1 GHz ISM frequency bands. This chip is optimized for battery powered applications with operating voltages from 1.8 to 3.6 V and ultra-low current consumption with a standby current of less than 10 nA. The high power amplifier can supply up to +10 dBm output power with 19.5 dB of programmable range. Moreover, the SoC transmitter includes a patented antenna tuning circuit that automatically fine tunes the resonance frequency and impedance matching between the PA output and the connected antenna for optimum transmit efficiency and low harmonic content. FSK and OOK modulation is supported with symbol rates up to 100 kbps. Like all wireless devices, users are responsible for complying with applicable local regulatory requirements for radio transmissions.

The embedded CIP-51 8051 MCU provides the core functionality of the Si4010. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings. A space of 8 kB of on-chip one-time programmable NVM memory is available to store the user program and can also store unique transmit IDs. In case of power outages due to battery removal, 128 bits of EEPROM is available for counter or other operations providing non-volatile storage capability. A library of useful software functions such as AES encryption, a patented 32-bit counter providing 1 M cycles of read/write endurance, and many other functions are included in the 12 kB of ROM to reduce user design time and code space. General purpose input/output pins with push button wake-on touch capability, a programmable system clock, and ultra low power timers are also available to further reduce current consumption.

The Si4010 includes Silicon Laboratories' 2-wire C2 Debug and Programming interface. This debug logic supports memory inspection, viewing and modification of special function registers (SFR), setting break points, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

The device leverages Silicon Labs' patented and proven crystal-less oscillator technology and offers better than  $\pm 150$  ppm carrier frequency stability over the temperature range of 0 to + 70 °C and  $\pm 250$  ppm carrier frequency stability over the industrial range of -40 to + 85 °C without the use of an external crystal or frequency reference. The internal MCU automatically calibrates the on-chip voltage controlled oscillator (LCOSC) which forms the output carrier frequency for process and temperature variations. An external 1-pin crystal oscillator option is available for applications requiring tighter frequency tolerances.

Digital integration reduces the amount of required external components compared to traditional offerings, resulting in a solution that only requires a printed circuit board (PCB) implementation area of approximately 25 by 50 mm (including battery, switches, and 25 mm<sup>2</sup> antenna). The high integration of the Si4010 improves the system manufacturing reliability and quality and minimizes costs. This chip offers industry leading RF performance, high integration, flexibility, low BOM, small board area, and ease of design. No production alignment is necessary as all RF functions are integrated into the device.

Figure 1.1. Si4010 Block Diagram

### 2. Test Circuit

Figure 2.1. Test Block Diagram with 10-Pin MSOP

### 3. Typical Application Schematic

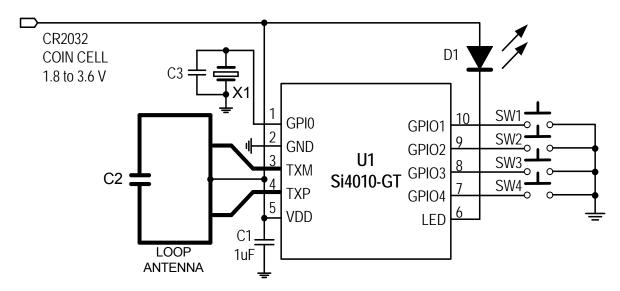

### 3.1. Si4010 Used in a 5-Button RKE System with LED Indicator

#### Figure 3.1. Si4010 Used in a 5-button RKE System with LED Indicator

### 3.2. Si4010 with an External Crystal in a 4-Button RKE System with LED Indicator

#### Figure 3.2. Si4010 with an External Crystal in a 4-button RKE System with LED Indicator

### 4. Ordering Information

| Ordering Part Number <sup>1</sup> | MIPS (Peak) | NVM (OTP) Memory (Bytes) | RAM (Bytes) | <b>Embedded ROM Functions</b> | Internal Data RAM (Bytes) | HVRAM (Bytes) | EEPROM (Bits) | 128-bit AES Accelerator | GPIO with Wakeup <sup>2</sup> | LED Driver | Sleep Timer | +10 dBm RF Transmitter | LDO with POR Circuit | Integrated Temperature Sensor | Low Battery Detector | Automotive Qualified | Lead-free (RoHS Compliant) | Package |

|-----------------------------------|-------------|--------------------------|-------------|-------------------------------|---------------------------|---------------|---------------|-------------------------|-------------------------------|------------|-------------|------------------------|----------------------|-------------------------------|----------------------|----------------------|----------------------------|---------|

| Si4010-C2-GT                      | 24          | 8k                       | 4k          | Υ                             | 256                       | 8             | 128           | Υ                       | 4                             | 1          | Y           | Υ                      | Y                    | Υ                             | Υ                    |                      | Y                          | MSOP-10 |

| Si4010-C2-GS                      | 24          | 8k                       | 4k          | Y                             | 256                       | 8             | 128           | Y                       | 8                             | 1          | Y           | Y                      | Y                    | Y                             | Y                    | _                    | Y                          | SOIC-14 |

| Si4010-C2-AT                      | 24          | 8k                       | 4k          | Y                             | 256                       | 8             | 128           | Y                       | 4                             | 1          | Y           | Y                      | Y                    | Y                             | Y                    | Y                    | Y                          | MSOP-10 |

| Si4010-C2-AS                      | 24          | 8k                       | 4k          | Y                             | 256                       | 8             | 128           | Y                       | 8                             | 1          | Y           | Y                      | Y                    | Y                             | Y                    | Y                    | Y                          | SOIC-14 |

Table 4.1. Product Selection Guide

**1.** Add an "(R)" at the end of the device part number to denote tape and reel option.

2. Assumes LED driver is used and no external crystal.

### 5. Pin Definitions

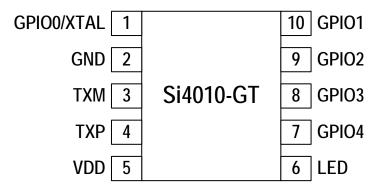

### 5.1. MSOP, Application

| Pin Number(s) | Name       | Description                                                                    |

|---------------|------------|--------------------------------------------------------------------------------|

| 1             | GPIO0/XTAL | General purpose input pin.<br>Can be configured as an input pin for a crystal. |

| 2             | GND        | Ground. Connect to ground plane on PCB.                                        |

| 3, 4          | TXM, TXP   | Transmitter differential outputs.                                              |

| 5             | VDD        | Power.                                                                         |

| 6             | LED        | Dedicated LED driver.                                                          |

| 7, 8, 9, 10   | GPIO[4:1]  | General purpose input/output pins.                                             |

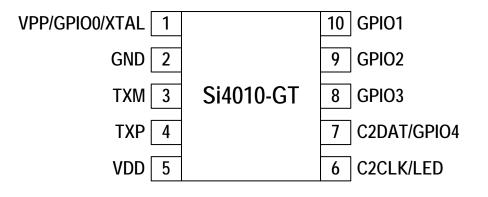

### 5.2. MSOP, Programming/Debug Mode

| Pin Number(s) | Name      | Description                                       |

|---------------|-----------|---------------------------------------------------|

| 1             | VPP       | +6.5 V required for NVM (OTP) Memory programming. |

| 2             | GND       | Ground. Connect to ground plane on PCB.           |

| 3             | TXM       | Transmitter differential output.                  |

| 4             | TXP       | Transmitter differential output.                  |

| 5             | VDD       | Power.                                            |

| 6             | C2CLK     | C2 clock interface.                               |

| 7             | C2DAT     | C2 data input/output pin.                         |

| 8, 9, 10      | GPIO[3:1] | General purpose input/output pins.                |

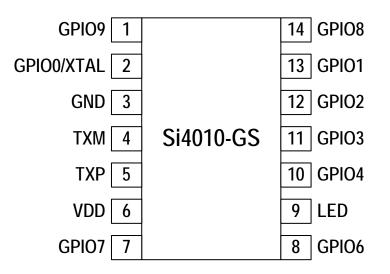

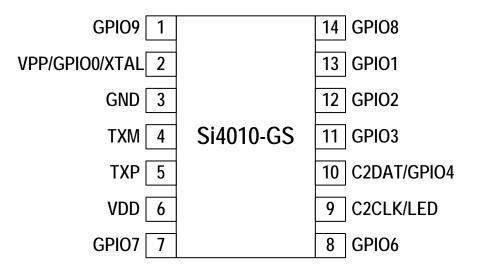

### 5.3. SOIC Package, Application

| Pin<br>Number(s) | Name       | Description                                                                |

|------------------|------------|----------------------------------------------------------------------------|

| 1                | GPIO9      | General purpose input/output pin                                           |

| 2                | GPIO0/XTAL | General purpose input pin. Can be configured as an input pin for a crystal |

| 3                | GND        | Ground. Connect to ground plane on PCB                                     |

| 4,5              | TXM, TXP   | Transmitter differential outputs                                           |

| 6                | VDD        | Power                                                                      |

| 7,8              | GPIO[7:6]  | General purpose input/output pins                                          |

| 9                | LED        | Dedicated LED driver                                                       |

| 10,11,12,13      | GPIO[4:1]  | General purpose input/output pins                                          |

| 14               | GPIO8      | General purpose input/output pin                                           |

### 5.4. SOIC Package, Programming/debug Mode

| Pin<br>Number(s) | Name      | Description                                      |

|------------------|-----------|--------------------------------------------------|

| 1                | GPIO9     | General purpose input/output pin                 |

| 2                | VPP       | +6.5 V required for NVM (OTP) Memory programming |

| 3                | GND       | Ground. Connect to ground plane on PCB           |

| 4,5              | TXM, TXP  | Transmitter differential outputs                 |

| 6                | VDD       | Power                                            |

| 7,8              | GPIO[7:6] | General purpose input/output pins                |

| 9                | C2CLK     | C2 clock interface                               |

| 10               | C2DAT     | C2 data input/output pin                         |

| 11,12,13         | GPIO[4:1] | General purpose input/output pins                |

| 14               | GPIO8     | General purpose input/output pin                 |

### 6. Package Specifications

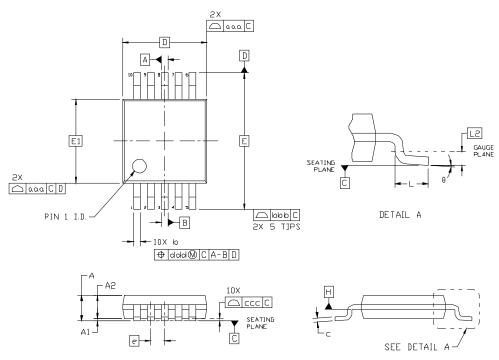

### 6.1. 10-Pin MSOP

Figure 6.1 illustrates the package details for the Si4010, 10-pin MSOP package. Table 6.1 lists the values for the dimensions shown in the illustration.

Figure 6.1. 10-Pin MSOP Package

| Symbol |          | Millimeters |      |  |  |  |

|--------|----------|-------------|------|--|--|--|

|        | Min      | Nom         | Max  |  |  |  |

| А      |          |             | 1.10 |  |  |  |

| A1     | 0.00     |             | 0.15 |  |  |  |

| A2     | 0.75     | 0.85        | 0.95 |  |  |  |

| b      | 0.17     |             | 0.33 |  |  |  |

| С      | 0.08     |             | 0.23 |  |  |  |

| D      | 3.00 BSC |             |      |  |  |  |

| E      | 4.90 BSC |             |      |  |  |  |

| E1     |          | 3.00 BSC    |      |  |  |  |

#### Table 6.1. Package Dimensions

| Symbol | Millimeters |          |      |  |  |  |

|--------|-------------|----------|------|--|--|--|

|        | Min         | Max      |      |  |  |  |

| е      |             | 0.50 BSC |      |  |  |  |

| L      | 0.40        | 0.80     |      |  |  |  |

| L2     | 0.25 BSC    |          |      |  |  |  |

| q      | 0° —        |          | 8°   |  |  |  |

| aaa    |             |          | 0.20 |  |  |  |

| bbb    | —           |          |      |  |  |  |

| CCC    | _           | 0.10     |      |  |  |  |

| ddd    |             |          |      |  |  |  |

#### Notes:

1. All dimensions are shown in millimeters (mm).

2. Dimensioning and tolerancing per ASME Y14.5M-1994.

3. This drawing conforms to JEDEC Outline MO-187, Variation "BA."

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

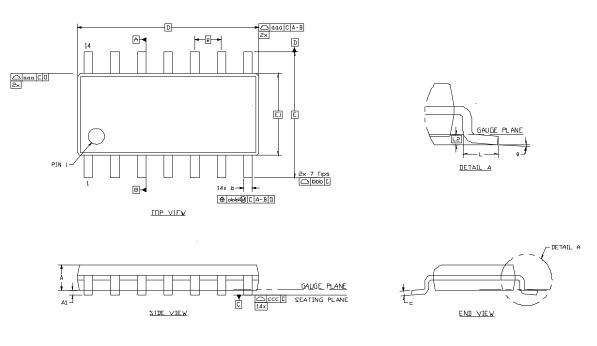

#### 6.2. 14-pin SOIC Package

Figure 6.2 illustrates the package details for the Si4010, 14-pin SOIC package. Table 6.2 lists the values for the dimensions shown in the illustration.

| Symbol | Min      | Max  |  |

|--------|----------|------|--|

| Α      |          | 1.75 |  |

| A1     | 0.10     | 0.25 |  |

| b      | 0.33     | 0.51 |  |

| С      | 0.17     | 0.25 |  |

| D      | 8.65     | BSC  |  |

| E      | 6.00     | BSC  |  |

| E1     | 3.90 BSC |      |  |

| е      | 1.27     | BSC  |  |

Table 6.2. Package Dimensions

| Symbol | Min  | Мах  |  |  |

|--------|------|------|--|--|

| L      | 0.40 | 1.27 |  |  |

| L2     | 0.25 | BSC  |  |  |

| Q      | 0°   | 8°   |  |  |

| aaa    | 0.10 |      |  |  |

| bbb    | 0.20 |      |  |  |

| CCC    | 0.10 |      |  |  |

| ddd    | 0.25 |      |  |  |

Notes:

**1.** All dimensions are shown in millimeters (mm).

2. Dimensioning and tolerancing per ASME Y14.5M-1994.

3. This drawing conforms to JEDEC Outline MS012, variation AB."

**4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

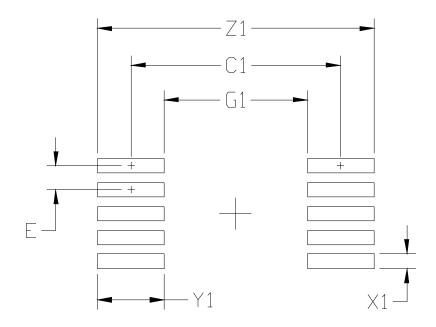

# 7. PCB Land Pattern 10-Pin MSOP

Figure 7.1. 10-Pin MSOP Recommended PCB Land Pattern

### Table 7.1. 10-Pin MSOP Dimensions

| Dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                       | МАХ  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|--|--|--|

| C1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4 40                      | REF  |  |  |  |

| F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | BSC  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                           | 500  |  |  |  |

| G1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.00                      | —    |  |  |  |

| X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                         | 0.30 |  |  |  |

| Y1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.40                      | REF  |  |  |  |

| Z1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                         | 5.80 |  |  |  |

| <ul> <li>Notes:</li> <li><u>General</u> <ol> <li>All dimensions shown are in millimeters (mm) unless otherwise noted.</li> <li>Dimensioning and Tolerancing per ASME Y14.5M-1994.</li> <li>This Land Pattern Design is based on the IPC-7351 guidelines.</li> <li>All dimensions shown are at Maximum Material Condition (MMC).<br/>Least Material Condition (LMC) is calculated based on a Fabrication<br/>Allowance of 0.05mm.</li> </ol> </li> <li>Solder Mask Design <ol> <li>All metal pads are to be non-solder mask defined (NSMD). Clearance<br/>between the solder mask and the metal pad is to be 60 m minimum, all</li> </ol> </li> </ul> |                           |      |  |  |  |

| the way around the<br><u>Stencil Design</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |      |  |  |  |

| <ol> <li>A stainless steel, laser-cut and electro-polished stencil with<br/>trapezoidal walls should be used to assure good solder paste release.</li> <li>The stencil thickness should be 0.125mm (5 mils).</li> <li>The ratio of stencil aperture to land pad size should be 1:1.</li> <li><u>Card Assembly</u></li> </ol>                                                                                                                                                                                                                                                                                                                         |                           |      |  |  |  |

| 1. A No-Clean, Type-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3 solder paste is recomme |      |  |  |  |

**2.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 8. PCB Land Pattern 14-pin SOIC Package

| -  | C1 |  |

|----|----|--|

|    |    |  |

|    |    |  |

|    |    |  |

|    |    |  |

|    |    |  |

|    |    |  |

| Y1 |    |  |

Figure 8.1. 14-Pin SOIC Recommended PCB Land Pattern

#### Table 8.1. PCB Land Pattern Dimensions

| Dimension | MIN       | MAX  |  |  |

|-----------|-----------|------|--|--|

| C1        | 5.30      | 5.40 |  |  |

| E         | 1.27 BSC  |      |  |  |

| X1        | 0.50 0.60 |      |  |  |

| Y1        | 1.45 1.55 |      |  |  |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on the IPC-7351 guidelines.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- $\ensuremath{\text{2. The stencil thickness should be } 0.125 \mbox{ mm (5 mils)}. } \label{eq:masses}$

- **3.** The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 9. Electrical Characteristics

#### **Table 9.1. Recommended Operating Conditions**

| Parameter                    | Symbol                                                                                                    | Test Condition             | Min  | Тур | Max                      | Unit |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|------|-----|--------------------------|------|--|

| Supply Voltage               | V <sub>DD</sub>                                                                                           |                            | 1.8  | _   | 3.6                      | V    |  |

| Supply Voltage Slew Rate     |                                                                                                           | Initial Battery Insertion* | 20   |     | 650                      | mV/  |  |

|                              |                                                                                                           |                            |      |     |                          | us   |  |

| Ambient Temperature          | T <sub>A</sub>                                                                                            |                            | -40  | 25  | 85                       | °C   |  |

| Digital Input Range          |                                                                                                           | Digital Input Signals      | -0.3 | _   | V <sub>DD</sub> +<br>0.3 | V    |  |

| *Note: Recommend bypass capa | * <b>Note:</b> Recommend bypass capacitor = 1 $\mu$ F; slew rate measured 1 V < V <sub>DD</sub> ,< 1.7 V. |                            |      |     |                          |      |  |

### Table 9.2. Absolute Maximum Ratings<sup>1,2</sup>

| Parameter                  | Symbol           | Value                           | Unit |

|----------------------------|------------------|---------------------------------|------|

| Supply Voltage             | V <sub>DD</sub>  | -0.5 to 3.9                     | V    |

| Input Current <sup>3</sup> | I <sub>IN</sub>  | 10                              | mA   |

| Input Voltage <sup>4</sup> | V <sub>IN</sub>  | –0.3 to (V <sub>DD</sub> + 0.3) | V    |

| Junction Temperature       | T <sub>OP</sub>  | -40 to 90                       | °C   |

| Storage Temperature        | T <sub>STG</sub> | -55 to 125                      | °C   |

Notes:

1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure beyond recommended operating conditions for extended periods may affect device reliability.

2. Handling and assembly of these devices should only be done at ESD-protected workstations.

3. All input pins besides  $V_{DD}$ .

4. For GPIO pins configured as inputs.

### Table 9.3. DC Characteristics

(TA = 25° C, VDD = 3.3 V, RL = 550  $\Omega$ , unless otherwise noted)

| Parameter                                                            | Symbol           | Test Condition                      | Min | Тур                        | Max | Unit |

|----------------------------------------------------------------------|------------------|-------------------------------------|-----|----------------------------|-----|------|

| Supply Current                                                       | I <sub>VDD</sub> | +10 dBm output, OOK,<br>Manchester  | -   | 14.2                       | _   | mA   |

|                                                                      |                  | +6.5 dBm output, OOK,<br>Manchester | _   | 11.3                       | —   | mA   |

|                                                                      |                  | +10 dBm, FSK                        | —   | 19.8                       |     | mA   |

|                                                                      |                  | +6.5 dBm output, FSK                | —   | 14.1                       | —   | mA   |

| Sleep Timer Mode                                                     | I <sub>ST</sub>  | Only sleep timer is enabled         | —   | 700                        |     | nA   |

| Standby Supply Current                                               | I <sub>SB</sub>  | All GPIO floating or held high      | —   | 10                         | _   | nA   |

| LED Sink Current                                                     | I <sub>LED</sub> | V <sub>OUT</sub> > 200 mV           | —   | 0.68                       | _   | mA   |

| GPIO[0-9] Pull Up Resis-<br>tance                                    | R <sub>PU</sub>  |                                     | 48  | 55                         | 62  | kΩ   |

| High Level Input Voltage <sup>1</sup>                                | V <sub>IH</sub>  | Trip point at 0.45 x $V_{DD}$       |     | 0.506<br>x V <sub>DD</sub> |     | V    |

| Low Level Input Voltage <sup>1</sup>                                 | V <sub>IL</sub>  | Trip point at 0.45 x $V_{DD}$       |     | 0.42 x<br>V <sub>DD</sub>  |     | V    |

| High Level Input Current <sup>1</sup>                                | I <sub>IH</sub>  | V <sub>IN</sub> = V <sub>DD</sub>   | _   | TBD                        | _   | μA   |

| Low Level Input Current <sup>1</sup>                                 | I <sub>IL</sub>  | V <sub>IN</sub> = 0                 | _   | TBD                        | _   | μA   |

| High Level Output Voltage <sup>2</sup>                               | V <sub>OH</sub>  | I <sub>SOURCE</sub> = TBD           | _   | TBD                        | _   | V    |

| Low Level Output Voltage <sup>2</sup>                                | V <sub>OL</sub>  | I <sub>SINK</sub> = TBD             | _   | TBD                        | _   | V    |

| Notes:<br>1. For GPIO pins configured<br>2. For GPIO pins configured | •                |                                     |     |                            |     |      |

#### Table 9.4. Si4010 RF Transmitter Characteristics

(TA =  $25^{\circ}$  C, VDD = 3.3 V, RL =  $550 \Omega$ , SOIC package unless otherwise noted)

| Parameter                          | Symbol          | Test Condition                                                 | Min   | Тур    | Max  | Unit   |

|------------------------------------|-----------------|----------------------------------------------------------------|-------|--------|------|--------|

| Frequency Range <sup>1</sup>       | F <sub>RF</sub> |                                                                | 27    |        | 960  | MHz    |

| Frequency Noise (rms) <sup>2</sup> |                 | Allen deviation, measured<br>across 1 ms interval              | —     | 0.3    | —    | ppm    |

| Phase Noise @ 915 MHz              |                 | 10 kHz offset                                                  | —     | -70    | —    | dBc/Hz |

|                                    |                 | 100 kHz offset                                                 | —     | -100   | —    | dBc/Hz |

|                                    |                 | 1 MHz offset                                                   | —     | -105   | —    | dBc/Hz |

| Frequency Tuning Time              |                 |                                                                | —     | 5      | _    | ms     |

| Selected Frequencies in            |                 | Discrete frequencies                                           | —     | 100    | —    | MHz    |

| Range of 27–960 MHz                |                 |                                                                | —     | 315    | —    | MHz    |

|                                    |                 |                                                                | —     | 390    | —    | MHz    |

|                                    |                 |                                                                | _     | 433.92 | —    | MHz    |

|                                    |                 |                                                                | _     | 868    | —    | MHz    |

|                                    |                 |                                                                | _     | 915    | _    | MHz    |

| Carrier Frequency                  |                 | 0°C ≤ T <sub>A</sub> ≤ 70° C                                   | -150  |        | +150 | ppm    |

| Accuracy                           |                 | –40°C ≤ T <sub>A</sub> ≤ 85° C                                 | -250  |        | +250 | ppm    |

|                                    |                 | F <sub>RF</sub> = 100 MHz<br>0°C ≤ T <sub>A</sub> ≤ 70° C      | -15   | —      | 15   | kHz    |

|                                    |                 | F <sub>RF</sub> = 100 MHz<br>40°C ≤ T <sub>A</sub> ≤ 85° C     | -25   | _      | 25   | kHz    |

|                                    |                 | F <sub>RF</sub> = 315 MHz<br>0°C ≤ T <sub>A</sub> ≤ 70° C      | -47.3 | —      | 47.3 | kHz    |

|                                    |                 | F <sub>RF</sub> = 315 MHz<br>–40°C ≤ T <sub>A</sub> ≤ 85° C    | -78.8 | —      | 78.8 | kHz    |

|                                    |                 | F <sub>RF</sub> = 433.92 MHz<br>0°C ≤ T <sub>A</sub> ≤ 70° C   | -65.1 | —      | 65.1 | kHz    |

|                                    |                 | F <sub>RF</sub> = 433.92 MHz<br>–40°C ≤ T <sub>A</sub> ≤ 85° C | -108  | —      | 108  | kHz    |

|                                    |                 | F <sub>RF</sub> = 868 MHz<br>0°C ≤ T <sub>A</sub> ≤ 70° C      | -130  | —      | 130  | kHz    |

|                                    |                 | F <sub>RF</sub> = 868 MHz<br>–40°C ≤ T <sub>A</sub> ≤ 85° C    | -217  | —      | 217  | kHz    |

|                                    |                 | F <sub>RF</sub> = 915 MHz<br>0°C ≤ T <sub>A</sub> ≤ 70° C      | -137  | -      | 137  | kHz    |

|                                    |                 | F <sub>RF</sub> = 915 MHz<br>40°C ≤ T <sub>A</sub> ≤ 85° C     | -229  | —      | 229  | kHz    |

#### Notes:

**1.** The frequency range is continuous over the specified range.

2. The frequency step size is limited by the frequency noise.

3. Optimum differential load is equal to 4 V/(11.5mA/2 \* 4/PI) = 550  $\Omega$ . Therefore the antenna load resistance in parallel with the Si4010 differential output resistance should equal 50  $\Omega$ .

4. Total NVM copy time = 2 ms + (NVM copy Boot Time per kB) x (NVM data in kB).

#### Table 9.4. Si4010 RF Transmitter Characteristics(Continued)

(TA = 25° C, VDD = 3.3 V, RL = 550  $\Omega$ , SOIC package unless otherwise noted)

| Parameter                                                | Symbol | Test Condition                                                                                    | Min  | Тур  | Max  | Unit  |

|----------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------|------|------|------|-------|

| Frequency Error<br>Contribution with<br>External Crystal |        |                                                                                                   | -10  | _    | +10  | ppm   |

| Transmit Power <sup>3</sup>                              |        | Maximum programmed Tx<br>power, with optimum differen-<br>tial load, Vdd > 2.2 V                  | _    | 10   | —    | dBm   |

|                                                          |        | Minimum programmed TX<br>power, with optimum differen-<br>tial load,<br>V <sub>DD</sub> > 2.2 V   | _    | –13  | _    | dBm   |

|                                                          |        | Power variation vs temp and<br>supply, with optimum<br>differential load, V <sub>DD</sub> > 2.2 V | -1.0 | —    | 0.5  | dB    |

|                                                          |        | Power variation vs temp and<br>supply, with optimum<br>differential load, V <sub>DD</sub> > 1.8 V | -2.5 | _    | 0.5  | dB    |

|                                                          |        | Transmit power step size<br>from –13 to 10 dBm                                                    |      | 0.25 |      | dB    |

| PA Edge Ramp Rate<br>Programmable Range                  |        | OOK mode                                                                                          | 0.34 | _    | 10.7 | us    |

| Data Rate                                                |        | OOK                                                                                               | 0.1  | —    | 50   | kBaud |

|                                                          |        | FSK                                                                                               | 0.1  | _    | 100  | kBaud |

Notes:

**1.** The frequency range is continuous over the specified range.

2. The frequency step size is limited by the frequency noise.

**3.** Optimum differential load is equal to 4 V/(11.5mA/2 \* 4/PI) = 550  $\Omega$ . Therefore the antenna load resistance in parallel with the Si4010 differential output resistance should equal 50  $\Omega$ .

4. Total NVM copy time = 2 ms + (NVM copy Boot Time per kB) x (NVM data in kB).

#### Table 9.4. Si4010 RF Transmitter Characteristics(Continued)

(TA = 25° C, VDD = 3.3 V, RL = 550  $\Omega$ , SOIC package unless otherwise noted)

| Parameter                                            | Symbol | Test Condition                         | Min | Тур  | Max  | Unit      |

|------------------------------------------------------|--------|----------------------------------------|-----|------|------|-----------|

| FSK Deviation                                        |        | Max frequency deviation                |     | 300  |      | ppm       |

|                                                      |        | Deviation resolution                   | —   | 2    | _    | ppm       |

|                                                      |        | Deviation accuracy                     |     | TBD  |      | ppm       |

|                                                      |        | Max frequency deviation,<br>100 MHz    | _   | 30   | —    | kHz       |

|                                                      |        | Deviation resolution,<br>100 MHz       | —   | 200  | —    | Hz        |

|                                                      |        | Max frequency deviation,<br>315 MHz    | -   | 95   | —    | kHz       |

|                                                      |        | Deviation resolution,<br>315 MHz       | -   | 630  | —    | Hz        |

|                                                      |        | Max frequency deviation,<br>433.92 MHz | -   | 130  | —    | kHz       |

|                                                      |        | Deviation resolution,<br>433.92 MHz    | —   | 868  | —    | Hz        |

|                                                      |        | Max frequency deviation,<br>868 MHz    | _   | 260  | —    | kHz       |

|                                                      |        | Deviation resolution,<br>868 MHz       | —   | 1740 | —    | Hz        |

|                                                      |        | Max frequency deviation,<br>915 MHz    | -   | 275  | —    | kHz       |

|                                                      |        | Deviation resolution,<br>915 MHz       | -   | 1830 | —    | Hz        |

| OOK Modulation depth                                 |        |                                        | 60  | _    | —    | dB        |

| Antenna Tuning<br>Capacitive Range<br>(Differential) |        | 315 MHz                                | 2.4 |      | 12.5 | pF        |

| NVM Copy Boot Time<br>per kB <sup>4</sup>            |        |                                        |     | 3.6  | —    | ms/<br>kB |

Notes:

**1.** The frequency range is continuous over the specified range.

2. The frequency step size is limited by the frequency noise.

3. Optimum differential load is equal to 4 V/(11.5mA/2 \* 4/PI) = 550  $\Omega$ . Therefore the antenna load resistance in parallel with the Si4010 differential output resistance should equal 50  $\Omega$ .

4. Total NVM copy time = 2 ms + (NVM copy Boot Time per kB) x (NVM data in kB).

### Table 9.5. Low Battery Detector Characteristics

(TA = 25° C, VDD = 3.3 V, RL = 550  $\Omega$ , unless otherwise noted)

| Parameter                               | Symbol | Test Condition | Min | Тур | Мах | Unit |

|-----------------------------------------|--------|----------------|-----|-----|-----|------|

| Battery Voltage Measurement<br>Accuracy |        |                | —   | 2   | —   | %    |

#### Table 9.6. Optional Crystal Oscillator Characteristics

(TA = 25° C, VDD = 3.3 V, RL = 600  $\Omega$ , unless otherwise noted)

| Parameter                 | Symbol | Test Condition                                               | Min | Тур | Max | Unit |

|---------------------------|--------|--------------------------------------------------------------|-----|-----|-----|------|

| Crystal Frequency Range   |        | GPI0 configured as crystal<br>oscillator                     | 10  | —   | 13  | MHz  |

| Input Capacitance (GPIO0) |        | GPI0 configured as crystal<br>oscillator                     | —   | 5   | _   | pF   |

| Crystal ESR               |        | GPI0 configured as crystal<br>oscillator                     | —   | —   | 50  | Ω    |

| Start-up Time             |        | Crystal oscillator only,<br>60 mH motional arm<br>inductance | —   | 9   | —   | ms   |

#### Table 9.7. EEPROM Characteristics

| Parameter                                                                         | Conditions                                    | Min   | Тур     | Max | Units  |  |  |

|-----------------------------------------------------------------------------------|-----------------------------------------------|-------|---------|-----|--------|--|--|

| Program Time                                                                      | Independent of number of bits changing values | —     | 8       | 40  | ms     |  |  |

| Maximum Count per Counter                                                         | Using API                                     |       | 1000000 |     | cycles |  |  |

| Write Endurance (per bit)*                                                        |                                               | 50000 | —       | —   | cycles |  |  |

| Note: *API uses coding technique to achieve write endurance of 1M cycles per bit. |                                               |       |         |     |        |  |  |

#### Table 9.8. Low Power Oscillator Characteristics

$V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                       | Conditions                                    | Min   | Тур | Max | Units |

|---------------------------------|-----------------------------------------------|-------|-----|-----|-------|

| Programmable Frequency<br>Range | Programmable divider in powers of 2 up to 128 | .1875 | —   | 24  | MHz   |

| Frequency Accuracy              |                                               | –1    | —   | +1  | %     |

Table 9.9. Sleep Timer Characteristics $V_{DD}$  = 1.8 to 3.6 V;  $T_A$  = -40 to +85 °C unless otherwise specified. Use factory-calibrated settings.

| Parameter                 | Conditions                 | Min  | Тур | Max  | Units |

|---------------------------|----------------------------|------|-----|------|-------|

| Maximum Programmable Time |                            | —    | —   | 6800 | S     |

| Time Accuracy             | Using API to program timer | -1.5 | —   | 1.5  | %     |

### **10. System Description**

Figure 10.1. Functional Block Diagram

#### 10.1. Overview

The Si4010 is a fully integrated crystal-less CMOS SoC RF transmitter with an embedded CIP-51 8051 MCU as the core processor of the system. The device is designed for low power battery applications with standby currents of less than 10 nA to optimize battery life. Upon power up, the device immediately enters standby mode. In this mode, all blocks are powered down except for the low leakage high-voltage RAM (HVRAM) which provides 8 bytes of memory that retains its state as long as the battery voltage is applied and above 1.8 V. The Si4010 is awakened from standby mode by a falling edge to ground on any one of the GPIO pins. In addition, the Si4010 has a low-power sleep timer for applications where the device is required to wake up and periodically check for events instead of being wakened by a GPIO falling edge.

Upon wake up, the boot loader copies data from the one time programmable (OTP) NVM to CODE/XDATA RAM (4 kB) because the MCU can only operate with programs stored in RAM or ROM. The copy process occurs on each wake-up event and requires approximately 2 ms of fixed time plus 3.6 ms per kB of data or 16.4 ms to fill the full 4 kB of CODE/XDATA RAM. After the NVM boot copy process is completed, the MCU runs the user program in RAM and can also run functions from ROM that are called by the user program such as button service routines to facilitate button debouncing, button time stamps, etc. A complete list of all the API functions is given in Section 10.3 and a detailed description is given in application note "AN370: Si4010 Software Programming Guide."

# Si4010

The Si4010 has three timing sources. The LCOSC is the most accurate timing source native to the chip. Each device is factory trimmed and programmed at Silicon Labs to produce a frequency accuracy of better than ±150 ppm over the temperature range of 0 to + 70 °C and ±250 ppm over the industrial range of -40 to +85 °C. The LCOSC is fitted to a multiple-degree polynomial to compensate for temperature variations both from the on-chip power amplifier (PA) and also from the external environment. This LCOSC oscillates around 3.9 GHz and provides the clock (via the DIVIDER) used to modulate the PA for OOK and FSK transmission. The low power oscillator (LPOSC) is the second timing source and operates at 24 MHz. The LPOSC is always the source of clocking for the MCU and is turned off only in standby mode. The system clock is programmable allowing the MCU to operate with lower clock frequencies while waiting between packets to save power. The RTC and timers 2 and 3 are derived from the LPOSC. The last clock source is the crystal oscillator (XTALOSC). This crystal oscillator is unused in many customer applications and used only when a highly accurate carrier frequency is desired. When enabled, it is used before the beginning of a transmission to correct the frequency of the LCOSC and is then shutdown to save power. An internal frequency counter is implemented in hardware to allow for quick frequency ratio measurements to calibrate the different clock sources.

The high efficiency PA is a CMOS open drain output driver capable of producing 4 Vpk differential output swing with a supply voltage of 2.2 V or higher. The PA output has 2.4 to 12.5 pF of differential variable capacitance that is automatically adjusted to resonate the antenna at the start of each packet transmission. This automatic adjustment is realized with a firmware algorithm in the ROM and some additional hardware in the PA. Maximum power can be transferred to the inductive antenna load when the antenna and output driver are at resonance and the real component of the load is equal to the optimum load resistance of V<sub>pk</sub>/(4/Pi \* I<sub>tail</sub>/2) where V<sub>pk</sub> is the peak differential voltage and I<sub>tail</sub> is the tail current of the PA. At higher resistances the PA is voltage limited and at lower resistances the PA is current limited. The PA tail current is programmable from 810 uA up to 7.67 mA in 0.25 dB steps and there is a boost current bit that multiplies the tail current by 1.5 times allowing it to go up to 11.5 mA. With an antenna load resistance of about 550  $\Omega$  an output power of +10 dBm is achievable. Edge rate control is also included for OOK mode to reduce harmonics that may otherwise violate government regulations.

The on-chip temperature sensor (TEMP SENSOR) measures the internal temperature of the chip and temperature demodulator (TEMP DEMOD) converts the TEMP SENSORs' output into a binary number representing temperature and is used to compensate the frequency of the LCOSC when the temperature changes. Each device is frequency and temperature calibrated in the factory.

The output data serializer (ODS) is responsible for synchronizing the output data to the required data rate and maintaining a steady data flow when data is available. This block produces the edge rate control for the PA in OOK mode and the frequency deviation in FSK mode. The block also schedules the power on/off times of the LCOSC, DIVIDER, and PA to conserve battery power during transmission.

Power management is provided on chip with low-drop-out (LDO) regulators for the internal analog and digital supplies, VA and VD, respectively. The power-on reset (POR) circuit monitors the power applied to the chip and generates a reset signal to set the chip into a known state. The bandgap produces voltage and current references for the analog blocks in the chip and can be shut down when the analog blocks are not used.

The embedded CIP-51 8051 MCU provides the core functionality of the Si4010. User software has complete control of all peripherals, and may individually shut down any or all peripherals for power savings. 8K bytes of on-chip one-time programmable NVM memory is available to store the user program and can also store unique transmit IDs. 128 bits of EEPROM is available for counter or other operations providing nonvolatile storage capability in case of power outages due to battery removal. A library of useful software functions such as AES encryption, a patented 32-bit counter providing 1M cycles of read/write endurance, and many other functions are included in the 12 kB of ROM to reduce user design time and code space. General purpose input/output pins with push button wake-on touch capability are available to further reduce current consumption.

The Si4010 includes Silicon Laboratories' 2-wire C2 Debug and Programming interface. This debug logic supports inspection memory, viewing and modification of special function registers (SFR), setting break points, single stepping, and run and halt commands. All analog and digital peripherals are fully functional while debugging using C2. The two C2 interface pins can be shared with user functions, allowing in-system debugging without occupying package pins.

#### 10.2. Setting Basic Si4010 Transmit Parameters

The basic transmit parameters such as output power, modulation type, data rate, and operating frequency are set by using applications programming interface (API) function commands. When using these functions certain parameters are determined by using a calculator spread sheet. The Si4010 development kit (part number 4010-DKKF 434) includes a calculator spread sheet that helps developers set the API function arguments to meet their desired design requirements. A summary of the calculator operations are given below and more detailed descriptions are given in the individual sections of this data sheet and in AN370: Si4010 Software Programming Guide.

#### 10.2.1. Package Type

The Si4010 has two package type options: 10-pin MSOP or 14-pin SOIC. The customer should choose the package type they are using to properly model the Si4010 RF behavior.

#### 10.2.2. Output Power

The output power of the Si4010 depends on many parameters including the antenna impedance, the output impedance of the PA, the nominal varactor setting, the battery supply voltage, and the bias current of the PA. The calculator spreadsheet can calculate the required antenna impedance needed to achieve the desired output power or it can estimate the output power given the antenna impedance. It has the following input parameters:

#### Power Setup:

- Power Target (dBm): This is the desired output power in dBm. The spreadsheet will always try and hit this target.

- Choose One of the Following: Maximize Radiated Power or Minimize PA current while Maximizing Radiated Power. If only radiated power is to be maximized, the PA current is maximized and an antenna impedance is found that maximizes the possible radiated power. Usually, this tends to minimize the antenna impedance relative to the chip impedance. If the PA current is to be minimized while still maximizing radiated power, the solution tends to equalize the antenna and on-chip impedances. This increases the effective impedance of the system, which saves PA current at the expense of radiation efficiency (as more power will now be consumed on-chip).

- Frequency (MHz): The RF frequency of operation, range is 27 to 960 MHz.

- Nominal Cap Word: This is the nominal setting of the power amplifier varactor that is part of the antenna tuning circuit, range is 0 to 511.

- External Diff Cap (pF): This is an external capacitor placed across the TXP and TXM pins. Assuming this has a much larger quality factor than the on-chip varactor, there may be antenna efficiency advantages of using this external component.

- Q-Factor External Cap: This is the quality factor of the external capacitor. Typical values would be 250-300.

#### Antenna Setup:

- Alpha (bLevel/deg C): The sensitivity of the antenna resistance vs temperature change. If constant

radiated power vs temperature is desired, this constant may be used to compensate the PA drive

strength. See the API section on power control.

- Approx Efficiency (%): The approximate antenna efficiency used to estimate radiated power.

# Si4010

- Manual Impedance Entry: Determines if the antenna impedance is calculated to meet a desired output power or if the antenna impedance is entered and the spread sheet calculates the resulting impedance. The current drive is adjusted to meet the power target (if possible).

- Antenna Real(Z) (Ohms): The antenna resistance at the operating frequency.

- Antenna Imag(Z) (Ohms): The antenna reactance at the operating frequency.

These parameters are discussed in more detail in the Power Amplifier section of the data sheet. Based on these input parameters the calculator will provide the following outputs:

#### PA Design Values:

- lout Target (mA): Theoretical output current that meets the power target.

- Attenuation Factor: Theoretical attenuation factor due to losses from the chip

- Actual lout (mA): The actual output current delivered to the antenna that accounts for quantization effects and chip losses.

- Rdif at PA (Ohms): Theoretical optimum differential load resistance that includes chip, antenna, and external capacitance loading.

- Total Power (dBm): The estimated output power based on all loss mechanisms.

- Max Diff Vpk at PA (V): The calculated peak differential voltage swing.

#### Antenna Targets:

- Real\_Z (Ohms): The required resistance of the antenna at the frequency of operation to meet the desired output power.

- Imag\_Z (Ohms): The required reactance of the antenna at the frequency of operation to meet the desired output power.

- Power dissipated in Antenna (dBm): The expected power delivered to the antenna.

- Expected Radiated Power (dBm): The expected radiated power of the device given the antenna efficiency

#### **Chip Impedance:**

- Total Diff Cap due to Chip + External Load (pF): The equivalent differential capacitance seen looking into the package pins. It includes the on-chip varactor, the package and external differential capacitor (if used).