# 650MHz Differential ADC Driver/Dual Selectable Gain Amplifier

### **FEATURES**

- 650MHz –3dB Small-Signal Bandwidth

- 600MHz -3dB Large-Signal Bandwidth

- High Slew Rate: 3300V/µs

- Easily Configured for Single-Ended to Differential Conversion

- 200MHz ±0.1dB Bandwidth

- www\_blsenSelectable Gain of +1, +2 and -1

- No External Resistors Required

- 46.5dBm Equivalent OIP3 at 30MHz When Driving an ADC

- IM3 with 2V<sub>P-P</sub> Composite, Differential Output: -87dBc at 30MHz, -83dBc at 70MHz

- -77dB SFDR at 30MHz, 2V<sub>P-P</sub> Differential Output

- 6ns 0.1% Settling Time for 2V Step

- Low Supply Current: 8mA per Ampifier

- Differential Gain of 0.02%, Differential Phase of 0.01°

- 50dB Channel Separation at 100MHz

- Wide Supply Range: ±2.25V (4.5V) to ±6.3V (12.6V)

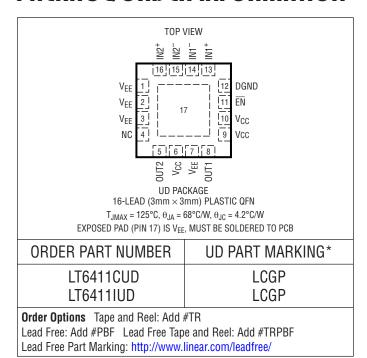

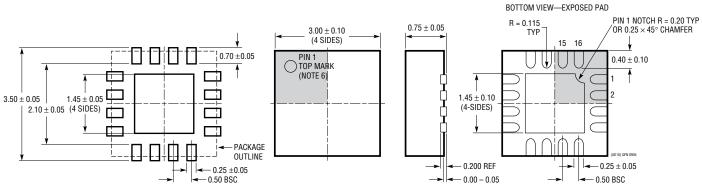

- 3mm × 3mm 16-Pin QFN Package

# **APPLICATIONS**

- Differential ADC Driver

- Single-Ended to Differential Conversion

- Differential Video Line Driver

### DESCRIPTION

The LT®6411 is a dual amplifier with individually selectable gains of +1, +2 and -1. The amplifiers have excellent distortion performance for driving ADCs as well as excellent bandwidth and slew rate for video, data transmission and other high speed applications. Single-ended to differential conversion with a system gain of 2 is particularly straightforward by configuring one amplifier with a gain of +1 and the other amplifier with a gain of -1. The LT6411 can be used on split supplies as large as  $\pm 6$ V and on a single supply as low as 4.5V.

Each amplifier draws only 8mA of quiescent current when enabled. When disabled, the output pins become high impedance and each amplifier draws less than 350µA.

The LT6411 is manufactured on Linear Technology's proprietary, low voltage, complimentary, bipolar process and is available in the ultra-compact,  $3mm \times 3mm$ , 16pin QFN package.

7, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

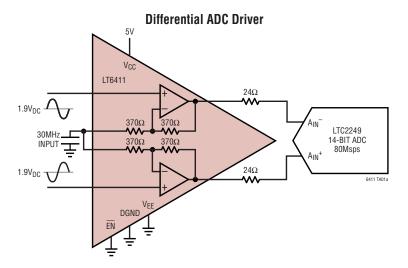

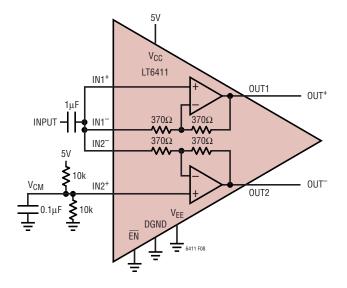

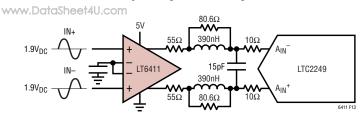

# TYPICAL APPLICATION

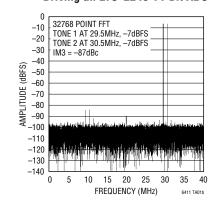

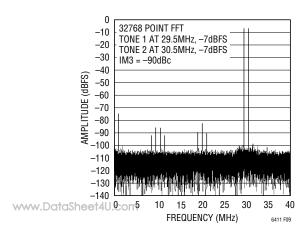

#### 30MHz 2-Tone 32768 Point FFT, LT6411 Driving an LTC®2249 14-Bit ADC

# **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                        |   |

|-----------------------------------------------------------------|---|

| Total Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )12.6\ | / |

| Input Current (Note 2)±10m/                                     | 4 |

| Output Current (Continuous)±70m/                                | 4 |

| EN to DGND Voltage (Note 2)5.5\                                 | V |

| Output Short-Circuit Duration (Note 3) Indefinite               | е |

| Operating Temperature Range (Note 4)40°C to 85°C                | 3 |

| Specified Temperature Range (Note 5)40°C to 85°C                | 3 |

| Storage Temperature Range65°C to 125°C                          | 3 |

| Junction Temperature                                            | 3 |

www.DataSheet4U.com

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*Temperature grade is identified by a label on the shipping container.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C.  $V_S = \pm 5V$ ,  $A_V = 2$ ,  $R_L = 150\Omega$ ,  $C_L = 1.5 pF$ ,  $V_{\overline{EN}} = 0.4 V$ ,  $V_{DGND} = 0 V$ , unless otherwise noted.

| SYMBOL               | PARAMETER                                                              | CONDITIONS                                                 |   | MIN                     | TYP                                        | MAX        | UNITS       |

|----------------------|------------------------------------------------------------------------|------------------------------------------------------------|---|-------------------------|--------------------------------------------|------------|-------------|

| V <sub>OS</sub>      | Input Referred Offset Voltage                                          | $V_{IN} = 0V$ , $V_{OS} = V_{OUT}/2$                       | • |                         | 3                                          | ±10<br>±20 | mV<br>mV    |

| I <sub>IN</sub>      | Input Current                                                          |                                                            | • |                         | -17                                        | ±50        | μА          |

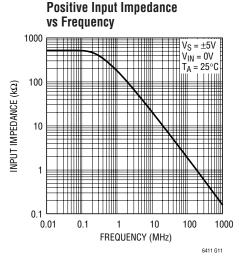

| R <sub>IN</sub>      | Input Resistance                                                       | V <sub>IN</sub> = ±1V                                      | • | 150                     | 500                                        |            | kΩ          |

| C <sub>IN</sub>      | Input Capacitance                                                      | f = 100kHz                                                 |   |                         | 1                                          |            | pF          |

| V <sub>CMR</sub>     | Maximum Input Common Mode Voltage<br>Minimum Input Common Mode Voltage |                                                            |   |                         | V <sub>CC</sub> – 1<br>V <sub>EE</sub> + 1 |            | V           |

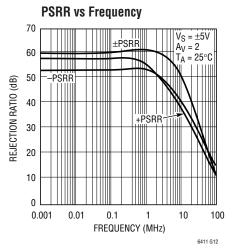

| PSRR                 | Power Supply Rejection Ratio                                           | V <sub>S</sub> (Total) = 4.5V to 12V (Note 6)              | • | 56                      | 62                                         |            | dB          |

| I <sub>PSRR</sub>    | Input Current Power Supply Rejection                                   | V <sub>S</sub> (Total) = 4.5V to 12V (Note 6)              | • |                         | 1                                          | ±4         | μA/V        |

| A <sub>V</sub> ERR   | Gain Error                                                             | $V_{OUT} = \pm 2V$                                         | • |                         | -1.2                                       | ±5         | %           |

| A <sub>V</sub> MATCH | Gain Matching                                                          | $V_{OUT} = \pm 2V$                                         |   |                         | ±1                                         |            | %           |

| V <sub>OUT</sub>     | Maximum Output Voltage Swing                                           | $R_L = 1k$ $R_L = 150\Omega$ $R_L = 150\Omega$             | • | ±3.70<br>±3.25<br>±3.10 | ±3.95<br>±3.6                              |            | V<br>V<br>V |

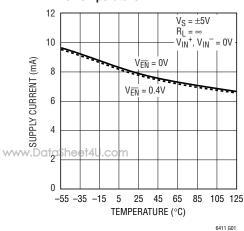

| I <sub>S</sub>       | Supply Current, Per Amplifier                                          |                                                            | • |                         | 8                                          | 11<br>14   | mA<br>mA    |

|                      | Supply Current, Disabled, per Amplifier                                | V <sub>EN</sub> = 4V<br>V <sub>EN</sub> = Open             | • |                         | 22<br>0.5                                  | 350<br>350 | μA<br>μA    |

| I <sub>EN</sub>      | Enable Pin Current                                                     | V <sub>EN</sub> = 0.4V<br>V <sub>EN</sub> = V <sup>+</sup> | • | -200                    | -95<br>0.5                                 | 50         | μA<br>μA    |

|                      | •                                                                      |                                                            |   | •                       |                                            |            | 6411f       |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_S = \pm 5V$ ,  $A_V = 2$ ,  $R_L = 150\Omega$ ,  $C_L = 1.5pF$ ,  $V_{\overline{EN}} = 0.4V$ ,  $V_{DGND} = 0V$ , unless otherwise noted.

| SYMBOL          | PARAMETER                            | CONDITIONS                                                                                          |   | MIN  | TYP        | MAX | UNITS    |

|-----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------|---|------|------------|-----|----------|

| I <sub>SC</sub> | Output Short-Circuit Current         | $R_L = 0\Omega$ , $V_{IN} = \pm 1V$                                                                 | • | ±50  | ±105       |     | mA       |

| SR              | Slew Rate                            | ±1V on ±2V Output Step (Note 9)                                                                     |   | 1700 | 3300       |     | V/µs     |

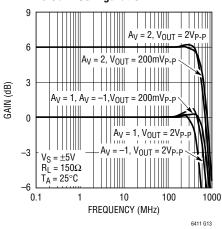

| –3dB BW         | Small-Signal –3dB Bandwidth          | V <sub>OUT</sub> = 200mV <sub>P-P</sub> , Single Ended                                              |   |      | 650        |     | MHz      |

| 0.1dB BW        | Gain Flatness ±0.1dB Bandwidth       | V <sub>OUT</sub> = 200mV <sub>P-P</sub> , Single Ended                                              |   |      | 200        |     | MHz      |

| FPBW            | Full Power Bandwidth 2V Differential | V <sub>OUT</sub> = 2V <sub>P-P</sub> Differential, –3dB                                             |   |      | 600        |     | MHz      |

|                 | Full Power Bandwidth 2V              | V <sub>OUT</sub> = 2V <sub>P-P</sub> (Note 7)                                                       |   | 270  | 525        |     | MHz      |

|                 | Full Power Bandwidth 4V              | V <sub>OUT</sub> = 4V <sub>P-P</sub> (Note 7)                                                       |   |      | 263        |     | MHz      |

| vw.DataShe      | All Hostile Crosstalk                | f = 10MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub><br>f = 100MHz, V <sub>OUT</sub> = 2V <sub>P-P</sub> |   |      | -75<br>-50 |     | dB<br>dB |

| t <sub>s</sub>  | Settling Time                        | 0.1% to V <sub>FINAL</sub> , V <sub>STEP</sub> = 2V                                                 |   |      | 6          |     | ns       |

| $t_r, t_f$      | Small-Signal Rise and Fall Time      | 10% to 90%, V <sub>OUT</sub> = 200mV <sub>P-P</sub>                                                 |   |      | 550        |     | ps       |

| dG              | Differential Gain                    | (Note 8)                                                                                            |   |      | 0.02       |     | %        |

| dP              | Diffierential Phase                  | (Note 8)                                                                                            |   |      | 0.01       |     | Deg      |

The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ ,  $V_{EE} = 0V$ ,  $A_V = 2$ , No  $R_{LOAD}$ ,  $V_{\overline{EN}} = 0.4V$ ,  $V_{DGND} = 0V$ , unless otherwise noted.

| SYMBOL              | PARAMETER                               | CONDITIONS                                                                                               | MIN | TYP        | MAX | UNITS      |

|---------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----|------------|-----|------------|

| Noise/Harr          | monic Performance Input/Output Characte | eristics                                                                                                 |     |            |     |            |

| 1MHz Sign           | al                                      |                                                                                                          |     |            |     |            |

| HD                  | Second/Third Harmonic Distortion        | $2V_{P-P}$ Differential $2V_{P-P}$ Differential, $R_L = 200\Omega$ Differential                          |     | -88<br>-87 |     | dBc<br>dBc |

| IMD3 <sub>1M</sub>  | Third-Order IMD                         | 2V <sub>P-P</sub> Differential Composite, f1 = 0.95MHz,<br>f2 = 1.05MHz                                  |     | -93        |     | dBc        |

|                     |                                         | $2V_{P-P}$ Differential Composite, f1 = 0.95MHz, f2 = 1.05MHz, R <sub>L</sub> = $200\Omega$ Differential |     | -91        |     | dBc        |

| OIP3 <sub>1M</sub>  | Output Third-Order Intercept            | Differential, f1 = 0.95MHz, f2 = 1.05MHz (Note 10)                                                       |     | 49.5       |     | dBm        |

| NF                  | Noise Figure                            | Single Ended                                                                                             |     | 25.1       |     | dB         |

| e <sub>n1M</sub>    | Input Referred Noise Voltage Density    |                                                                                                          |     | 8          |     | nV/√Hz     |

| P1dB                | 1dB Compression Point                   | (Note 10)                                                                                                |     | 19.5       |     | dBm        |

| 10MHz Sig           | nal                                     |                                                                                                          |     |            |     |            |

| HD                  | Second/Third Harmonic Distortion        | $2V_{P-P}$ Differential $2V_{P-P}$ Differential, $R_L = 200\Omega$ Differential                          |     | -85<br>-76 |     | dBc<br>dBc |

| IMD3 <sub>10M</sub> | Third-Order IMD                         | 2V <sub>P-P</sub> Differential Composite, R <sub>L</sub> = 1k,<br>f1 = 9.5MHz, f2 = 10.5MHz              |     | -92        |     | dBc        |

|                     |                                         | $2V_{P-P}$ Differential Composite, f1 = 9.5MHz, f2 = 10.5MHz, R <sub>L</sub> = $200\Omega$ Differential  |     | -89        |     | dBc        |

| OIP3 <sub>10M</sub> | Output Third-Order Intercept            | Differential, f1 = 9.5MHz, f2 = 10.5MHz (Note 10)                                                        |     | 49         |     | dBm        |

| NF                  | Noise Figure                            | Single Ended                                                                                             |     | 24.7       |     | dB         |

| e <sub>n10M</sub>   | Input Referred Noise Voltage Density    |                                                                                                          |     | 7.7        |     | nV/√Hz     |

| P1dB                | 1dB Compression Point                   | (Note 10)                                                                                                |     | 19.5       |     | dBm        |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{CC} = 5V$ , $V_{EE} = 0V$ , $A_V = 2$ , No $R_{LOAD}$ , $V_{\overline{EN}} = 0.4V$ , $V_{DGND} = 0V$ , unless otherwise noted.

| SYMBOL              | PARAMETER                            | CONDITIONS                                                                                               | MIN | TYP             | MAX | UNITS      |

|---------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----------------|-----|------------|

| 30MHz Sigr          | nal                                  |                                                                                                          | '   |                 |     |            |

| HD                  | Second/Third Harmonic Distortion     | $2V_{P-P}$ Differential $2V_{P-P}$ Differential, $R_L = 200\Omega$ Differential                          |     | -77<br>-64      |     | dBc<br>dBc |

| IMD3 <sub>30M</sub> | Third-Order IMD                      | 2V <sub>P-P</sub> Differential Composite, f1 = 29.5MHz,<br>Differential, f2 = 30.5MHz                    |     | -87             |     | dBc        |

|                     |                                      | $2V_{P-P}$ Differential Composite, f1 = 29.5MHz, f2 = 30.5MHz, R <sub>L</sub> = $200\Omega$ Differential |     | <del>-</del> 75 |     | dBc        |

| OIP3 <sub>30M</sub> | Output Third-Order Intercept         | Differential, f1 = 29.5MHz, f2 = 30.5MHz (Note 10)                                                       |     | 46.5            |     | dBm        |

|                     | Noise Figure                         | Single Ended                                                                                             |     | 24.6            |     | dB         |

| e <sub>n30M</sub>   | Input Referred Noise Voltage Density |                                                                                                          |     | 7.6             |     | nV/√Hz     |

| P1dB                | 1dB Compression Point                | (Note 10)                                                                                                |     | 19.5            |     | dBm        |

| 70MHz Sigr          | nal                                  |                                                                                                          |     |                 |     |            |

| HD                  | Second/Third Harmonic Distortion     | $2V_{P-P}$ Differential $2V_{P-P}$ Differential, $R_L = 200\Omega$ Differential                          |     | -63<br>-52      |     | dBc<br>dBc |

| IMD3 <sub>70M</sub> | Third-Order IMD                      | 2V <sub>P-P</sub> Differential Composite, f1 = 69.5MHz,<br>Differential, f2 = 70.5MHz                    |     | -83             |     | dBc        |

|                     |                                      | $2V_{P-P}$ Differential Composite, f1 = 69.5MHz, f2 = 70.5MHz, R <sub>L</sub> = $200\Omega$ Differential |     | -64             |     | dBc        |

| OIP3 <sub>70M</sub> | Output Third-Order Intercept         | Differential, f1 = 69.5MHz, f2 = 70.5MHz (Note 10)                                                       |     | 44.5            |     | dBm        |

| NF                  | Noise Figure                         | Single Ended                                                                                             |     | 24.7            |     | dB         |

| e <sub>n70M</sub>   | Input Referred Noise Voltage Density |                                                                                                          |     | 7.7             |     | nV/√Hz     |

| P1dB                | 1dB Compression Point                | (Note 10)                                                                                                |     | 19.5            |     | dBm        |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** This parameter is guaranteed to meet specified performance through design and characterization. It is not production tested.

**Note 3:** As long as output current and junction temperature are kept below the Absolute Maximum Ratings, no damage to the part will occur. Depending on the supply voltage, a heat sink may be required.

**Note 4:** The LT6411C is guaranteed functional over the operating temperature range of -40°C to 85°C.

**Note 5:** The LT6411C is guaranteed to meet specified performance from 0°C to 70°C. The LT6411C is designed, characterized and expected to meet specified performance from –40°C and 85°C but is not tested or QA sampled at these temperatures. The LT6411I is guaranteed to meet specified performance from –40°C to 85°C.

**Note 6:** The two supply voltage settings for power supply rejection are shifted from the typical  $\pm V_S$  points for ease of testing. The first measurement is taken at  $V_{CC} = 3V$ ,  $V_{EE} = -1.5V$  to provide the required 3V headroom for the enable circuitry to function with EN, DGND and all inputs connected to 0V. The second measurement is taken at  $V_{CC} = 8V$ ,  $V_{EE} = -4V$ .

**Note 7:** Full power bandwidth is calculated from the slew rate: FPBW =  $SR/(\pi \cdot V_{P-P})$

**Note 8:** Differential gain and phase are measured using a Tektronix TSG120YC/NTSC signal generator and a Tektronix 1780R video measurement set. The resolution of this equipment is better than 0.05% and 0.05°. Ten identical amplifier stages were cascaded giving an effective resolution of better than 0.005% and 0.005°.

**Note 9:** Slew rate is 100% production tested on channel 1. Slew rate of channel 2 is guaranteed through design and characterization.

**Note 10:** Since the LT6411 is a feedback amplifier with low output impedance, a resistive load is not required when driving an ADC. Therefore, typical output power is very small. In order to compare the LT6411 with typical  $g_m$  amplifiers that require  $50\Omega$  output loading, the LT6411 output voltage swing driving an ADC is converted to OIP3 and P1dB as if it were driving a  $50\Omega$  load.

# TYPICAL PERFORMANCE CHARACTERISTICS

All measurements are per amplifier with single-ended outputs unless otherwise noted.

# Supply Current per Amplifier vs Temperature

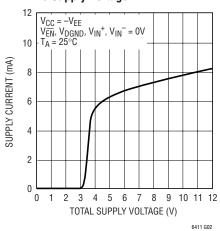

# Supply Current per Ampifier vs Supply Voltage

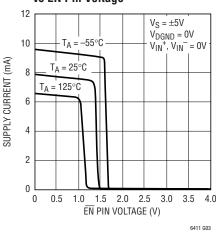

Supply Current per Amplifier vs EN Pin Voltage

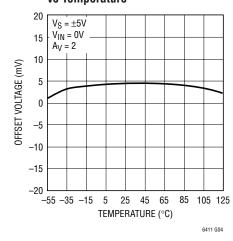

# Output Offset Voltage vs Temperature

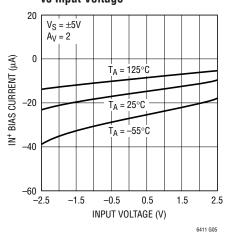

# Positive Input Bias Current vs Input Voltage

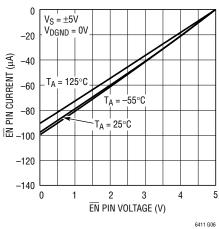

**EN** Pin Current vs **EN** Pin Voltage

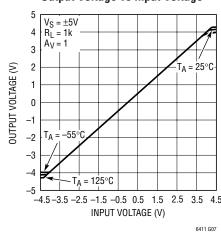

#### **Output Voltage vs Input Voltage**

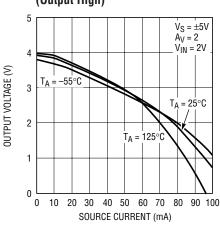

# Output Voltage Swing vs I<sub>LOAD</sub> (Output High)

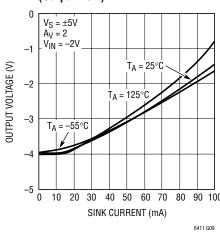

# Output Voltage Swing vs I<sub>LOAD</sub> (Output Low)

# TYPICAL PERFORMANCE CHARACTERISTICS

All measurements are per amplifier with single-ended outputs unless otherwise noted.

###

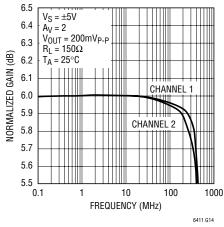

Frequency Response vs Gain Configuration

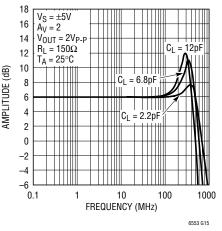

Frequency Response with Capacitive Loads

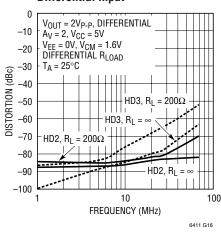

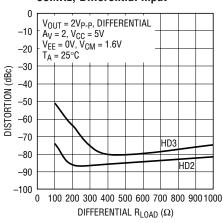

Harmonic Distortion vs Frequency, Differential Input

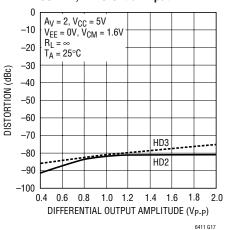

Harmonic Distortion vs Amplitude, 30MHz, Differential Input

Harmonic Distortion vs Load, 30MHz, Differential Input

# TYPICAL PERFORMANCE CHARACTERISTICS

All measurements are per amplifier with single-ended outputs unless otherwise noted.

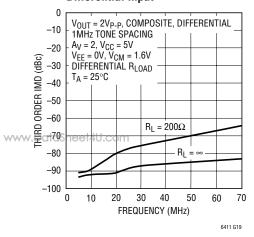

#### Third Order Intermodulation Distortion vs Frequency, Differential Input

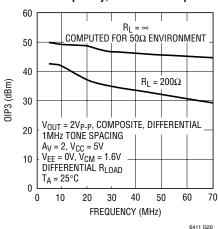

# Output Third Order Intercept vs Frequency, Differential Input

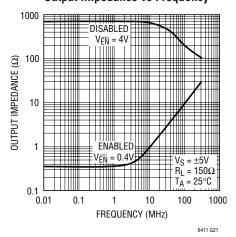

#### **Output Impedance vs Frequency**

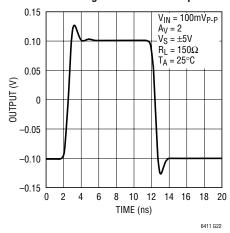

#### **Small-Signal Transient Response**

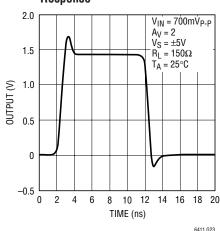

#### Video Amplitude Transient Response

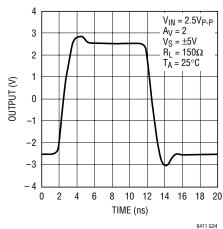

#### **Large-Signal Transient Response**

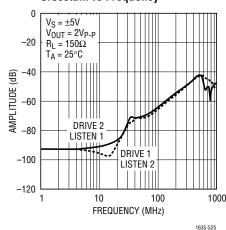

#### Crosstalk vs Frequency

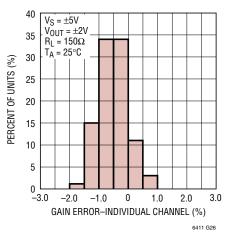

#### Gain Error Distribution

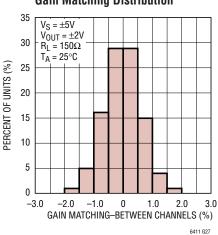

#### **Gain Matching Distribution**

### PIN FUNCTIONS

$V_{EE}$  (Pins 1, 2): Negative Supply Voltage.  $V_{EE}$  pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

$V_{EE}$  (Pins 3, 7): Negative Supply Voltage for Output Stage.  $V_{EE}$  pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

NC (Pin 4): This pin is not internally connected.

**OUT2** (**Pin 5**): Output of Channel 2. The gain between the input and the output of this channel is set by the connection of the channel 2 input pins. See Table 1 in Applications Information for details.

$V_{CC}$  (Pins 6, 9): Positive Supply Voltage for Output Stage.  $V_{CC}$  pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

**OUT1 (Pin 8):** Output of Channel 1. The gain between the input and the output of this channel is set by the connection of the channel 1 input pins. See Table 1 in Applications Information for details.

$V_{CC}$  (Pin 10): Positive Supply Voltage.  $V_{CC}$  pins are not internally connected to each other and must all be connected externally. Proper supply bypassing is necessary for best performance. See the Applications Information section.

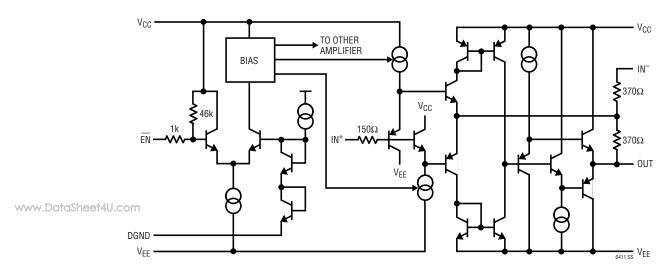

**EN (Pin 11):** Enable Control Pin. An internal pull-up resistor of 46k will turn the part off if the pin is allowed to float and defines the pin's impedance. When the pin is pulled low, the part is enabled.

**DGND (Pin 12):** Digital Ground Reference for Enable Pin. This pin is normally connected to ground.

**IN1+** (Pin 13): Channel 1 Positive Input. This pin has a nominal impedance of  $400k\Omega$  and does not have an internal termination resistor.

**IN1**<sup>-</sup> (**Pin 14**): This pin connects to the internal resistor network of the channel 1 amplifier, connecting by a  $370\Omega$  resistor to the inverting input.

**IN2**<sup>-</sup> (**Pin 15**): This pin connects to the internal resistor network of the channel 2 amplifier, connecting by a  $370\Omega$  resistor to the inverting input.

**IN2+** (Pin 16): Channel 2 Positive Input. This pin has a nominal impedance of  $400k\Omega$  and does not have an internal termination resistor.

**Exposed Pad (Pin 17):** The pad is internally connected to  $V_{EE}$  (Pin 1). If split supplies are used, **do not** tie the pad to ground.

### **Power Supplies**

The LT6411 can be operated on as little as  $\pm 2.25 V$  or a single 4.5V supply and as much as  $\pm 6 V$  or a single 12V supply. Internally, each supply is independent to improve channel isolation. Note that the Exposed Pad is internally connected to  $V_{EE}$  and must not be grounded when using split supplies. **Do not leave any supply pins disconnected or the part may not function correctly!**

#### Enable/Shutdown

The LT6411 has a TTL compatible shutdown mode controlled by the  $\overline{EN}$  pin and referenced to the DGND pin. If the amplifier will be enabled at all times, the  $\overline{EN}$  pin can be connected directly to DGND. If the enable function is desired, either driving the pin above 2V or allowing the internal 46k pull-up resistor to pull the  $\overline{EN}$  pin to the top rail will disable the amplifier. When disabled, the DC output impedance will rise to approximately  $740\Omega$  through the internal feedback and gain resistors (assuming inputs at ground). Supply current into the amplifier in the disabled state will be primarily through  $V_{CC}$  and approximately equal to  $(V_{CC}-V_{\overline{EN}})/46k$ .

It is important that the two following constraints on the DGND pin and the EN pin are always followed:

$$\label{eq:VCC} \begin{split} V_{CC} - V_{DGND} &\geq 3V \\ -0.5V &\leq V_{\overline{EN}} - V_{DGND} \leq 5.5V \end{split}$$

Split supplies of  $\pm 3V$  to  $\pm 5.5V$  will satisfy these requirements with DGND connected to 0V.

In dual supply cases with  $V_{CC}$  less than 3V, DGND should be connected to a potential below ground such as  $V_{EE}$ .

Since the  $\overline{\text{EN}}$  pin is referenced to DGND, it may need to be pulled below ground in those <u>cases</u>. In order to protect the internal enable circuitry, the  $\overline{\text{EN}}$  pin should not be forced more than 0.5V below DGND.

In single supply applications above 5.5V, an additional resistor may be needed from the  $\overline{\text{EN}}$  pin to DGND if the pin is ever allowed to float. For example, on a 12V single supply, a 33k resistor would protect the pin from floating too high while still allowing the internal pull-up resistor to disable the part.

The DGND pin should not be pulled above the  $\overline{\text{EN}}$  pin since doing so will turn on an ESD protection diode. If the  $\overline{\text{EN}}$  pin voltage is forced a diode drop below the DGND pin, current should be limited to 10mA or less.

The enable/disable times of the LT6411 are fast when driven with a logic input. Turn on (from  $50\% \overline{EN}$  input to 50% output) typically occurs in less than 50ns. Turn off is slower, but is less than 300ns.

#### **Gain Selection**

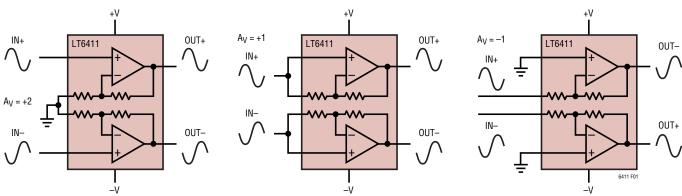

The gain of the internal amplifiers of the LT6411 is configured by connecting the IN<sup>+</sup> and IN<sup>-</sup> pins to the input signal or ground in the combinations shown in Figure 1.

As shown in the Simplified Schematic, the IN<sup>-</sup> pins connect to the internal gain resistor of each amplifier, and therefore, each pin can be configured independently. Floating the IN<sup>-</sup> pins is not recommended as the parasitic capacitance causes an AC gain of 2 at high frequencies, despite a DC gain of +1. Both inputs are connected together in the gain of +1 configuration to avoid this limitation.

Figure 1. LT6411 Configured in Noninverting Gain of 2, Noninverting Gain of 1 and Inverting Gain of 1, All Shown with Dual Supplies

#### **Input Considerations**

The LT6411 input voltage range is from  $V_{EE} + 1V$  to  $V_{CC} - 1V$ . Therefore, on split supplies the LT6411 input range is always as large as or larger than the output swing. On a single positive supply with a gain of +2 and IN $^-$  connected to ground, however, the input range limit of +1V limits the linear output low swing to 2V (1V multiplied by the internal gain of 2).

The inputs can be driven beyond the point at which the coutput clips somlong as input currents are limited to ±10mA. Continuing to drive the input beyond the output limit can result in increased current drive and slightly increased swing, but will also increase supply current and may result in delays in transient response at larger levels of overdrive.

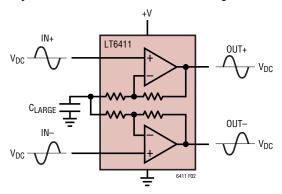

### **DC Biasing Differential Amplifier Applications**

The inputs of the LT6411 must be DC biased within the input common mode voltage range, typically  $V_{EE}$  + 1V to  $V_{CC}$  – 1V. If the inputs are AC coupled or DC biased beyond the input voltage range of a driven A-to-D converter, DC biasing or level shifting will be required. In the basic circuit configurations shown in Figure 1, the DC input common mode voltage and the differential input signal are both multiplied by the amplifier gain. In the gain of +2 configuration, the DC common mode voltage gain can be set to unity by adding a capacitor at the IN $^-$  pins as shown in Figure 2.

If the inputs are AC coupled or the LT6411 is preceded by a highpass filter, the input common mode voltage can be set by resistor dividers as shown in Figure 3. Adding

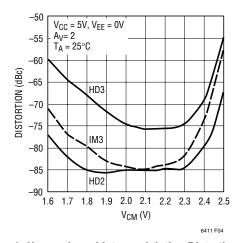

Figure 2. LT6411 Configured with a Differential Gain of 2 and Unity DC Common Mode Gain

the blocking capacitor to the gain setting resistors sets the input and output DC common mode voltages equal. When using the LT6411 to drive an A-to-D converter, the DC common mode voltage level will affect the harmonic distortion of the combined amplifier/ADC system. Figure 4 shows the measured distortion of an LTC2249 ADC when driven by the LT6411 at different common mode voltage levels with the inputs configured as shown in Figure 3. Adjusting the DC bias voltage can optimize the design for the lowest possible distortion.

If the input signals are within the input voltage range and output swing of the LT6411, but outside the input range of an ADC or other circuit the LT6411 is driving,

Figure 3. Using Resistor Dividers to Set the Input Common Mode Voltage When AC Coupling

Figure 4. Harmonic and Intermodulation Distortion of the LT6411 Driving an LTC2249 Versus DC Common Mode Voltage. Harmonic Distortion Measured with a -1dBFS Signal at 30.2MHz. Intermodulation Distortion Measured with Two -7dBFS Tones at 30.2MHz and 29.2MHz

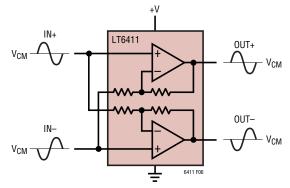

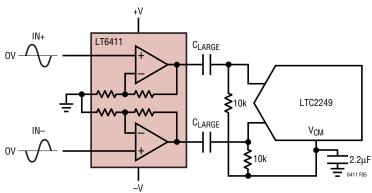

the output signals can be AC coupled and DC biased in a manner similar to what is shown at the inputs in Figure 3. A simpler alternative when using an ADC such as the LTC2249 is to use the ADC's  $V_{CM}$  pin to set the optimal common mode voltage as shown in Figure 5.

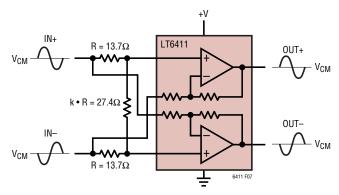

If unity common mode gain and difference mode response to DC is desired, there is another configuration available. Figure 6 shows the LT6411 connected to provide a differential signal gain of +3 with unity common mode gain. For differential signal gain between unity and +3, three resistors can be added to provide attenuation and set the differential input impedance of the stage as illustrated in Figure 7. The general expression for the differential gain is:

$$A_{V(DIFF)} = 1 + \frac{2 \cdot k}{k+2}$$

Scaling factor 'k' is the multiple between the two equal-value series input resistors and the resistor connected between the two positive inputs. The correct value of R for the external resistors can be computed from the desired differential input impedance,  $Z_{IN}$ , as a function of k and the  $370\Omega$  internal gain setting resistors, as described in the equation:

$$R = \frac{Z_{IN} \cdot 370\Omega}{370\Omega(k+2) - Z_{IN}(k+1)}$$

In Figure 7 k = 2 and R = 13.7 $\Omega$ , setting the differential gain to +2 and the differential input impedance to approximately  $50\Omega$ .

Figure 6. LT6411 Configured for a Differential Gain of +3 and Unity Common Mode Gain with Response to DC

Figure 7. LT6411 Configured with a Differential Input Impedance of  $50\Omega$ , a Differential Gain of +2 and Unity Common Mode Gain

Figure 5. Level Shifting the Output Common Mode Voltage of the LT6411 Using the V<sub>CM</sub> Pin of an LTC2249

#### **Layout and Grounding**

It is imperative that care is taken in PCB layout in order to utilize the very high speed and very low crosstalk of the LT6411. Separate power and ground planes are highly recommended and trace lengths should be kept as short as possible. If input or output traces must be run over a distance of several centimeters, they should use a controlled impedance with matching series and shunt resistances to maintain signal fidelity.

Series termination resistors should be placed as close to the output pins as possible to minimize output capacitance. See the Typical Performance Characteristics section for a plot of frequency response with various output capacitors—only 12pF of parasitic output capacitance causes 6dB of peaking in the frequency response!

Low ESL/ESR bypass capacitors should be placed as close to the positive and negative supply pins as possible. One 4700pF ceramic capacitor is recommended for both  $V_{CC}$  and  $V_{EE}$ . Additional 470pF ceramic capacitors with minimal trace length on each supply pin will further improve AC and transient response as well as channel isolation. For high current drive and large-signal transient applications, additional  $1\mu F$  to  $10\mu F$  tantalums should be added on each

supply. The smallest value capacitors should be placed closest to the LT6411 package.

If the undriven input pins are not connected directly to a low impedance ground plane, they must be carefully bypassed to maintain minimal impedance over frequency. Although crosstalk will be very dependent on the board layout, a recommended starting point for bypass capacitors would be 470pF as close as possible to each input pin with one 4700pF capacitor in parallel.

To maintain the LT6411's channel isolation, it is beneficial to shield parallel input and output traces using a ground plane or power supply traces. Vias between topside and backside metal may be required to maintain a low inductance ground near the part where numerous traces converge.

#### **ESD Protection**

The LT6411 has reverse-biased ESD protection diodes on all pins. If any pins are forced a diode drop above the positive supply or a diode drop below the negative supply, large currents may flow through these diodes. If the current is kept below 10mA, no damage to the devices will occur.

# TYPICAL APPLICATIONS

#### Single-Ended to Differential Converter

Because the gains of each channel of the LT6411 can be configured independently, the LT6411 can be used to provide a gain of +2 when amplifying differential signals and when converting single-ended signals to differential. With both channels connected to a single-ended input, one channel configured with a gain of +1 and the other configured with a gain of -1, the output will be a differential version of the input with twice the peak-to-peak (differential) amplitude. Figure 8 shows the proper connections and Figure 9 displays the resulting performance when driving an LTC2249. This configuration can preserve signal amplitude when converting single ended video signals to differential signals when driving double terminated cables. The 10k resistors in Figure 8 set the common mode voltage at the output.

Figure 8. Single-Ended to Differential Converter with Gain of +2 and Common Mode Control

# TYPICAL APPLICATIONS

Figure 9. 2-Tone Response of the LT6411 Configured with Single-Ended Inputs Driving the LTC2249 at 29.5MHz, 30.5MHz

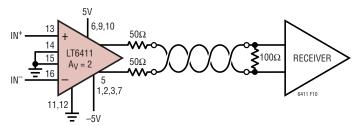

#### **Twisted-Pair Line Driver**

The LT6411 is ideal when used for driving inexpensive unshielded twisted-pair wires as often found in telephone or communications infrastructure. The input can be composite video, or if three parts are used, RGB or similar and can be either single ended or differential. The LT6411 has excellent performance with all formats.

Double termination of the video cable will enhance fidelity and isolate the LT6411 from capacitive loads. Although most twisted-pair cables have a characteristic impedance

Figure 10. Twisted-Pair Driver

of  $100\Omega$ , the cables can be terminated with a smaller series resistance or a larger shunt resistance in order to compensate for attenuation. A typical circuit for a twisted-pair driver is shown in Figure 10.

### **Single Supply Differential ADC Driver**

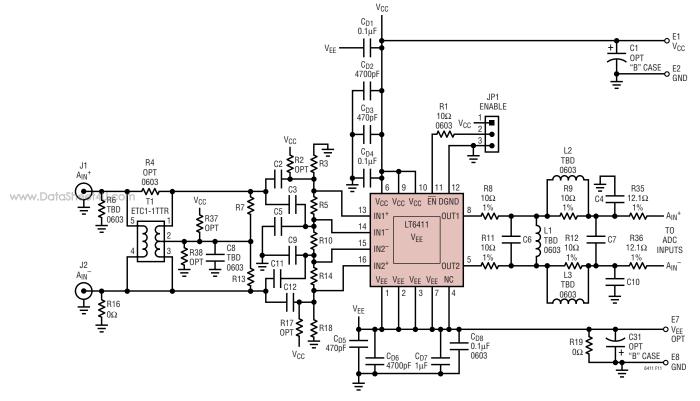

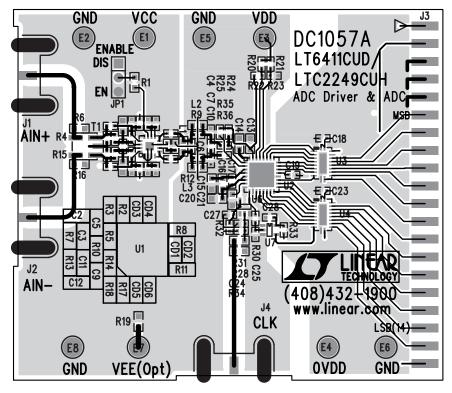

The LT6411 is well suited for driving differential analog to digital converters. The low output impedance of the LT6411 is capable of driving a variety of filters as well as interfacing with the typically high impedance inputs of ADCs. In addition, the LT6411's excellent distortion allows the part to perform with an SFDR below the limits of many high speed ADCs. The DC1057 demo board, shown schematically in Figure 11 and physically in Figure 12, allows implementation and testing of the LT6411 with a variety of different Linear Technology high speed ADCs.

# TYPICAL APPLICATIONS

Figure 11. DC1057 Demo Circuit Schematic

Figure 12. Layout of DC1057 Demo Circuit

# SIMPLIFIED SCHEMATIC

# PACKAGE DESCRIPTION

#### **UD Package** 16-Lead Plastic QFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1691)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- 1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WEED-2)

2. DRAWING NOT TO SCALE

- 2. DIAWNING NOT 10 SOALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

- ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

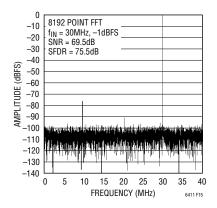

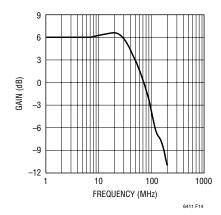

In cases where lowering the noise floor is paramount, adding higher order lowpass or bandpass filtering can significantly increase signal-to-noise ratio. In Figure 13, the LT6411 is shown driving an LTC2249 with a 2nd order lowpass filter that has been carefully chosen to ensure optimal intermodulation distortion. The response is shown in Figure 14. The filter improves the SNR over the unfiltered case by 6dB to 69.5dB. With the filter, the SNR of the ADC and the LT6411 are comparable; better SNR can be achieved by using either a higher resolution ADC

Figure 13. Optimized 30MHz LT6411 Differential ADC Driver

Figure 15. SNR and SFDR of the LT6411 and Filter Driving the LTC2249

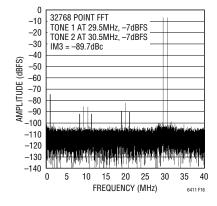

or additional filtering. Figure 15 shows the corresponding SFDR of -75.5dBc with a 30MHz tone. Figure 16 shows the 2-tone response of the LT6411 with 29.5MHz and 30.5MHz inputs. Note that 0dBFS corresponds to a  $2V_{P-P}$  differential signal.

Figure 14. Frequency Response of the LT6411 and Filter

Figure 16. 2-Tone Response of the LT6411 and Filter Driving the LTC2249 at 29.5MHz, 30.5MHz

# RELATED PARTS

| PART NUMBER | DESCRIPTION                                                                                                                  | COMMENTS                                        |

|-------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| LT1993-2    | 800MHz Low Distortion, Low Noise ADC Driver, A <sub>V</sub> = 2                                                              | 3.8nV/√Hz Total Noise, Low Distortion to 100MHz |

| LT1993-4    | 900MHz Low Distortion, Low Noise ADC Driver, A <sub>V</sub> = 4 2.4nV/√Hz Total Noise, Low Distortion to 100MHz              |                                                 |

| LT1993-10   | 700MHz Low Distortion, Low Noise ADC Driver, A <sub>V</sub> = 10 1.9nV/√Hz Total Noise, Low Distortion to 100MHz             |                                                 |

| LT1994      | Low Noise, Low Distortion Fully Differential Amplfier                                                                        | 70MHz Gain Bandwidth Differential In and Out    |

| LT6402-6    | 300MHz Low Distortion, Low Noise ADC Driver, $A_V = 2$ 3.8nV/ $\sqrt{\text{Hz}}$ Input Referred Noise, Low Distortion to 30M |                                                 |

| LT6553      | 53 650MHz Gain of 2 Triple Video Amplifier Triple Amplifier with Fixed Gain                                                  |                                                 |

| LT6554      | 650MHz Gain of 1 Triple Video Amplifier                                                                                      | Triple Amplifier with Fixed Gain                |

WWW Data Sheet 4 U.Com

LILL TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2006