## ACT<sup>™</sup> 1 and ACT 2 Military Field Programmable **Gate Arrays**

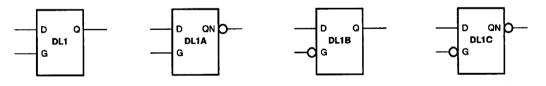

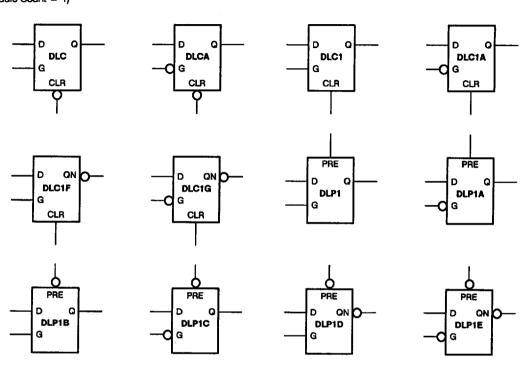

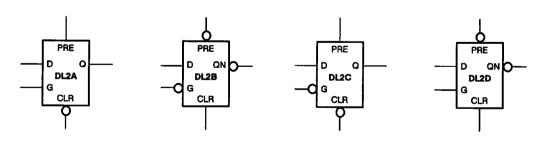

T.46-19-11

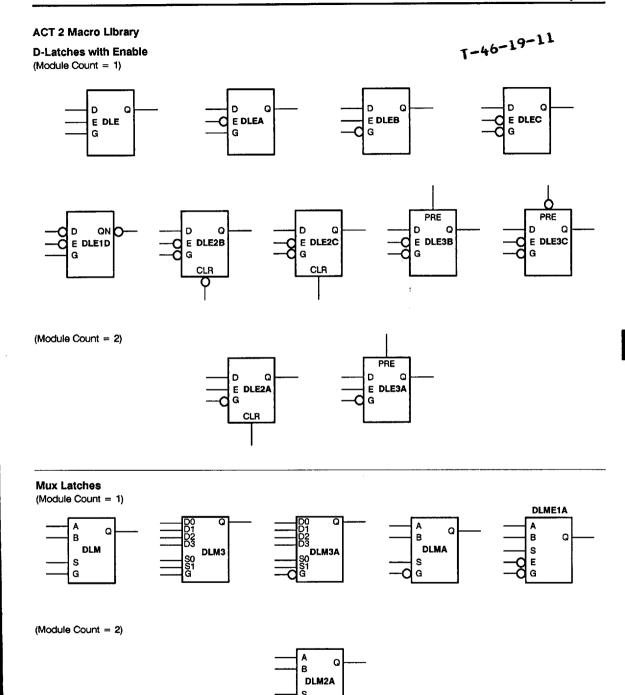

#### **ACT 1 Features**

- Up to 2000 Gate Array Gates (6000 PLD/LCATM equivalent gates)

- Replaces up to 53 TTL Packages

- Replaces up to 17 20-Pin PAL Packages

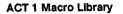

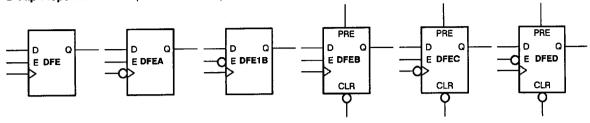

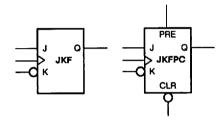

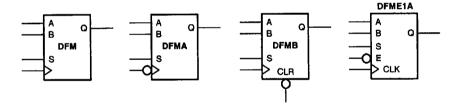

- Design Library with over 250 Macros

- Single Logic Module Architecture

- Up to 547 Logic Modules

- Up to 273 Flip-Flops

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 50 MHz

- Built-In High-Speed Clock Distribution Network

- I/O Drive to 4 mA

- Nonvolatile, User Programmable

- · Logic Fully Tested Prior to Shipment

## **ACT 2 Features**

- Up to 8000 Gate Array Gates (20,000 PLD/LCA<sup>TM</sup> equivalent gates)

- Replace up to 210 TTL Packages

- Replace up to 69 20-Pin PAL Packages

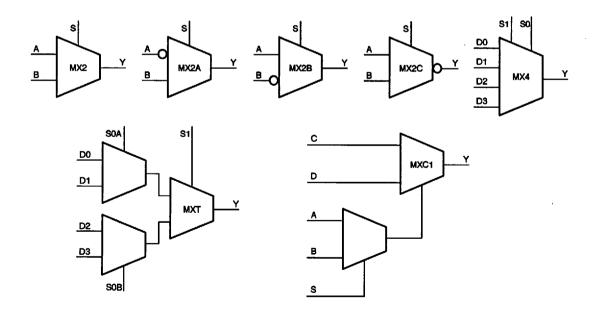

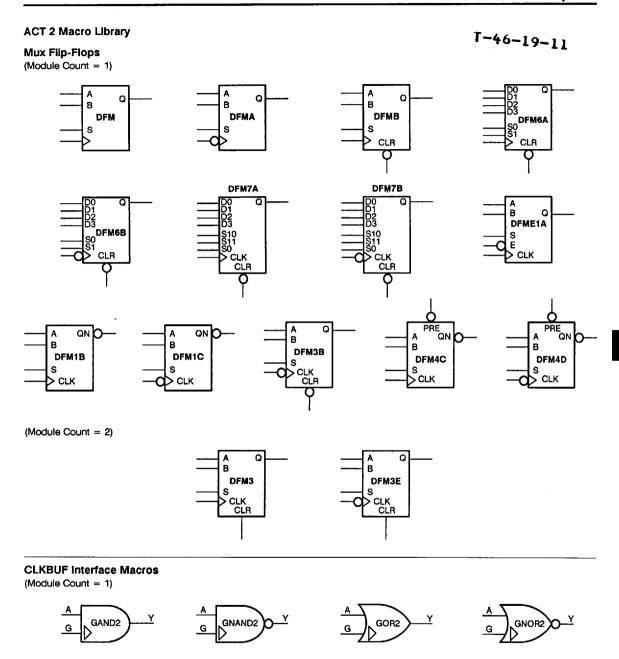

- Design Library with over 250 Macros

- Single-Module Sequential Functions

- Wide-Input Combinatorial Functions

- Up to 1232 Programmable Logic Modules

- Up to 998 Flip-Flops

- 16-Bit Counter Performance to 50 MHz (MIL Temp)

- 16-Bit Accumulator Performance to 25 MHz (MIL Temp)

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 50 MHz

- Two High-Speed, Low-Skew Clock Networks

- I/O Drive to 6 mA

- Nonvolatile, User Programmable

- Logic Fully Tested Prior to Shipment

## **Product Family Profile**

| Family                         | A        | CT 2     |                     | ACT 1               |  |  |

|--------------------------------|----------|----------|---------------------|---------------------|--|--|

| Device                         | A1280    | A1240    | A1020A              | A1010A              |  |  |

| Capacity                       |          |          |                     |                     |  |  |

| Gate Array Equivalent Gates    | 8,000    | 4,000    | 2,000               | 1,200               |  |  |

| PLD/LCA Equivalent Gates       | 20,000   | 10,000   | 6,000               | 3,000               |  |  |

| TTL Equivalent Packages        | 210      | 105      | 53                  | 34                  |  |  |

| 20-Pin PAL Equivalent Packages | 69       | 34       | 17                  | 12                  |  |  |

| Logic Modules                  | 1,232    | 684      | 547                 | 295                 |  |  |

| S-Modules                      | 624      | 348      |                     |                     |  |  |

| C-Modules                      | 608      | 336      |                     |                     |  |  |

| Flip-Flops (maximum)           | 998      | 565      | 273                 | 147                 |  |  |

| Routing Resources              |          |          |                     |                     |  |  |

| Horizontal Tracks/Channel      | 36       | 36       | 22                  | 22                  |  |  |

| Vertical Tracks/Column         | 15       | 15       | 13                  | 13                  |  |  |

| PLICE® Antifuse Elements       | 750,000  | 400,000  |                     |                     |  |  |

| User I/Os (maximum)            | 140      | 104      | 69                  | 57                  |  |  |

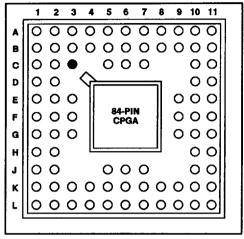

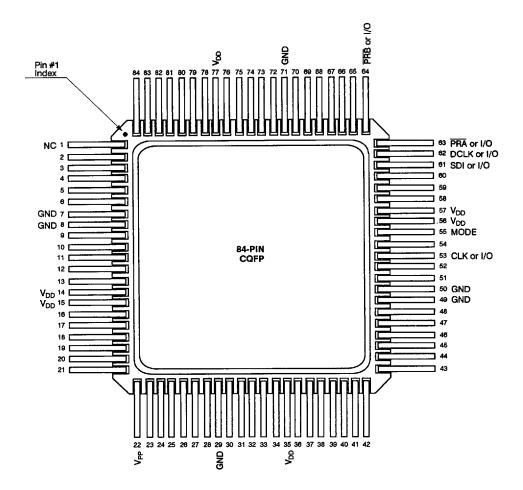

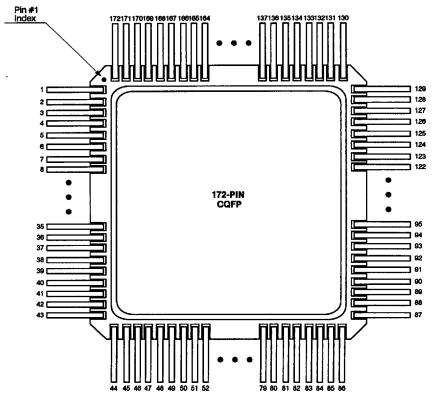

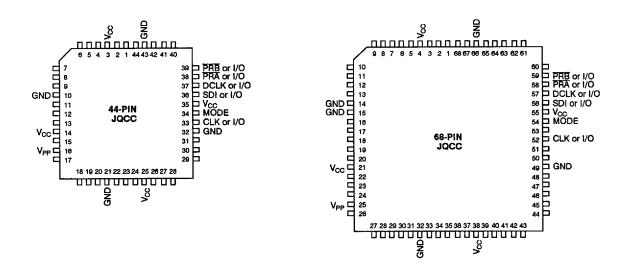

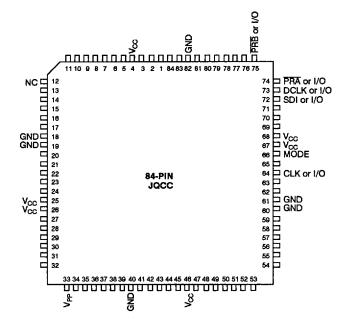

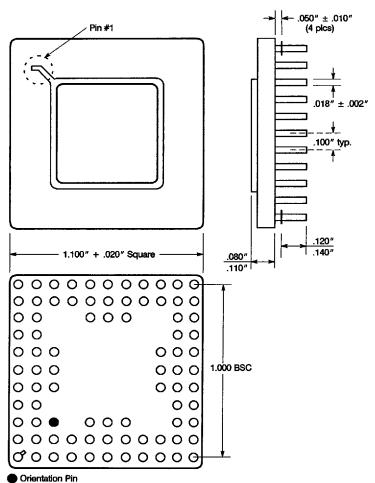

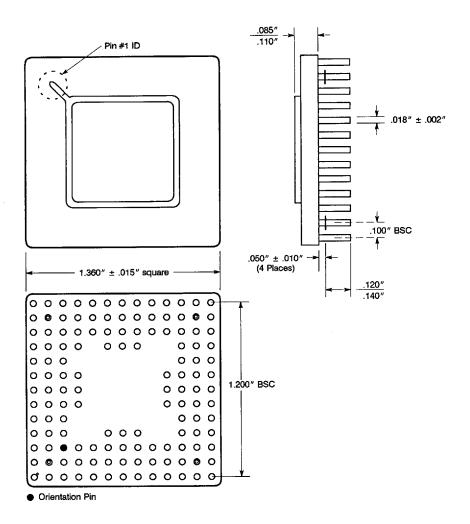

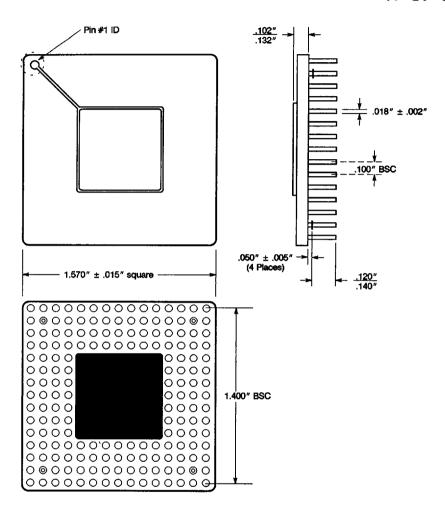

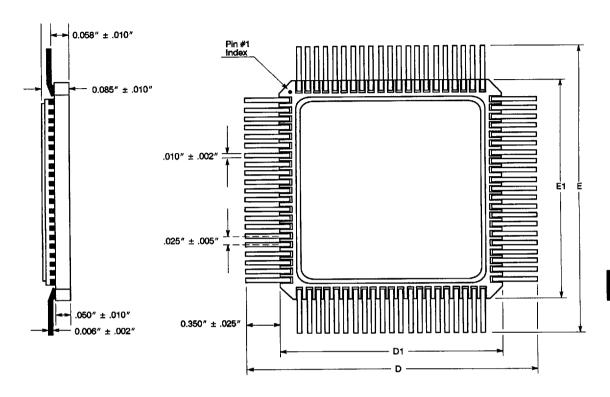

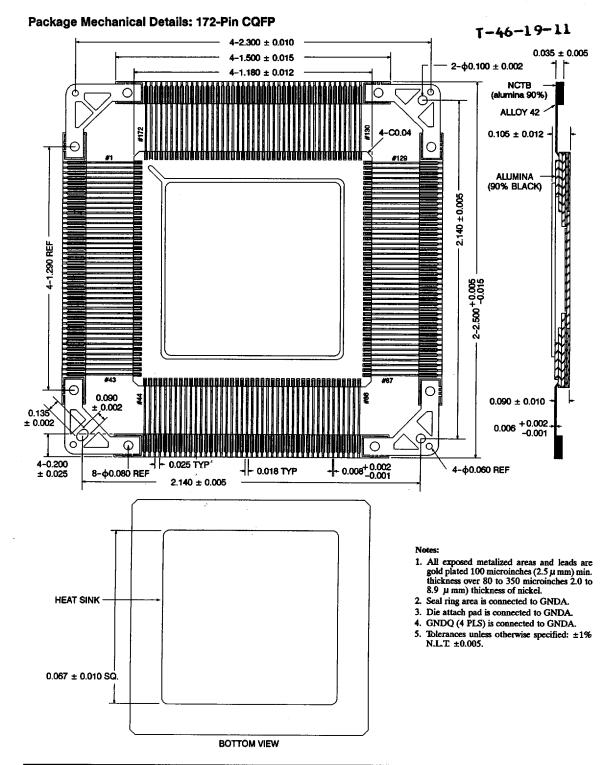

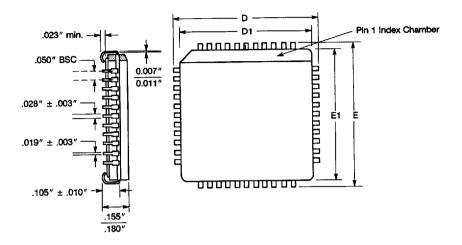

| Packages <sup>1</sup>          | 176 CPGA | 132 CPGA | 84 CPGA             | 84 CPGA             |  |  |

|                                | 172 CQFP |          | 84 CQFP             |                     |  |  |

|                                |          |          | 44/68/84 JQCC       |                     |  |  |

| Performance (MIL Temp)         |          |          |                     | ·*·                 |  |  |

| 16-Bit Counters                | 39 MHz   | 50 MHz   | 39 MHz <sup>2</sup> | 39 MHz <sup>2</sup> |  |  |

| 16-Bit Accumulators            | 23 MHz   | 25 MHz   | 20 MHz <sup>2</sup> | 20 MHz <sup>2</sup> |  |  |

| CMOS Process                   | 1.2 µm   | 1.2 µm   | 1.2 µm              | 1.2 µm              |  |  |

#### Note:

- 1. See product plan on page 1-130 for package availability.

- Performance is based on a -1 speed graded device at worst-case military operating conditions.

## High Reliability, Low Risk Solution

Actel builds the most reliable field programmable gate arrays (FPGAs) in the industry, with overall antifuse reliability ratings of less than 10 Failures-In-Time (FITs), corresponding to a useful life of more than 40 years. Actel FPGAs have been production-proven, with over one million devices shipped and over 130 billion antifuses manufactured. Actel devices are fully tested prior to shipment, with an outgoing defect level of only 122 ppm. (Further reliability data is available in the "Actel Reliability Report.")

#### 100% Tested Product

Device functionality is fully tested before shipment and during device programming. Routing tracks, logic modules, and programming, debug, and test circuits are 100% tested before shipment. Antifuse integrity also is tested before shipment. Programming algorithms are tested when a device is programmed using Actel's Activator 1 or 2® programming stations.

#### **Benefits**

No cost risk — Once you have an Action Logic<sup>TM</sup> System (ALS), Actel's CAE software and programming package, you can produce as many chips as you like for just the cost of the device itself, with no NRE charges to eat up your development budget each time you want to try out a new design.

No time risk — After entering your design, placement and routing is automatic, and programming the device takes only about 5 to 15 minutes for an average design. You save time in the design entry process by using tools that are familiar to you. The Action Logic System software interfaces to popular CAE software such as Mentor Graphics<sup>®</sup>, Valid<sup>TM</sup>, OrCAD<sup>TM</sup>, HP DCS, and Viewlogic<sup>®</sup> and runs on popular platforms such as Apollo<sup>®</sup>, HP, Sun<sup>TM</sup>, and 386/486<sup>TM</sup> PC compatible machines.

No reliability risk — The PLICETM antifuse is a one-time programmable, nonvolatile connection. Since Actel devices are permanently programmed, no downloading from EPROM or SRAM storage is required. Inadvertent erasure is impossible and there is no need to reload the program after power disruptions. Both the PLICE antifuse and the base process are radiation tolerant. Fabrication using a low-power CMOS process means cooler junction temperatures. Actel's non-PLD architecture delivers lower dynamic operating current. Our reliability tests show a very low failure rate of 91 FTIs at 90 °C junction temperature with no degradation in AC performance. Special stress testing at wafer test eliminates infant mortalities prior to packaging.

No security risk — Reverse engineering of programmed Actel devices from optical or electrical data is extremely difficult. Programmed antifuses cannot be identified from a photograph or by using a SEM. The antifuse map cannot be deciphered either electrically or by microprobing. Each device has a silicon signature that identifies its origins, down to the wafer lot and fabrication facility.

## T-46-19-11

No testing risk — Unprogrammed Actel parts are fully tested at the factory. This includes the logic modules, interconnect tracks, and I/Os. AC performance is assured by special speed path tests, and programming circuitry is verified on test antifuses. During the programming process, an algorithm is run to assure that all antifuses are correctly programmed. In addition, Actel's Actionprobe<sup>TM</sup> diagnostic tools allow 100% observability of all internal nodes to check and debug your design.

### **ACT 1 Description**

The ACT 1 family of FPGAs offers a variety of package, speed, and application combinations. Devices are implemented in silicon gate, 1.2-micron two-level metal CMOS, and they employ Actel's PLICE antifuse technology. The unique architecture offers gate array flexibility, high performance, and instant turnaround through user programming. Device utilization is typically 95% of available logic modules.

ACT 1 devices also provide system designers with unique on-chip diagnostic probe capabilities, allowing convenient testing and debugging. Additional features include an on-chip clock driver with a hardwired distribution network. The network provides efficient clock distribution with minimum skew.

The user-definable I/Os are capable of driving at both TTL and CMOS drive levels. Available packages include ceramic J-leaded chip carriers, ceramic quad flatpack, and ceramic pin grid array.

A security fuse may be programmed to disable all further programming and to protect the design from being copied or reverse engineered.

#### **ACT 2 Description**

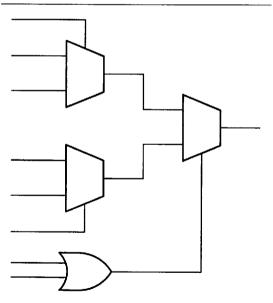

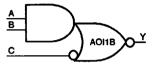

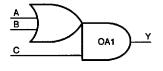

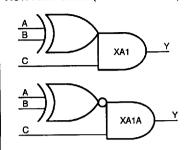

The ACT 2 family represents Actel's second generation of FPGAs. The ACT 2 family presents a two-module architecture consisting of C-Modules and S-Modules. These modules are optimized for both combinatorial and sequential designs (see Figure 1). Based on Actel's patented channeled array architecture, the ACT 2 family provides significant enhancements to gate density and performance while maintaining upward compatibility with the ACT 1 design environment. The devices are implemented in silicon gate, 1.2-µm, two-level metal CMOS, and employ Actel's PLICE antifuse technology. This revolutionary architecture offers gate array design flexibility, high performance, and fast time-to-production through user programming.

The ACT 2 family is supported by the ALS, which offers automatic pin assignment, validation of electrical and design rules, automatic placement and routing, timing analysis, user programming, and debug and diagnostic probe capabilities. The Action Logic System is supported on the following platforms: 386/486 PC, Sun, HP and Apollo workstations. It provides CAE interfaces to the following design environments: Valid, Viewlogic, Mentor Graphics, HP DCS and OrCAD.

**ACT 1 and ACT 2 Military FPGAs**

#### **ACT 1 Architecture**

ACT 1 devices consist of a matrix of logic modules arranged in rows separated by wiring channels. This array is surrounded by a ring of peripheral circuits including I/O buffers, testability circuits, and diagnostic probe circuits providing real-time diagnostic capability. Between rows of logic modules are routing channels containing sets of segmented metal tracks with PLICE antifuses. Each channel has 22 signal tracks. Vertical routing is permitted via 13 vertical tracks per logic module column. The resulting network allows arbitrary and flexible interconnections between logic modules and I/O modules.

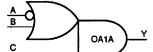

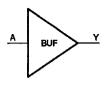

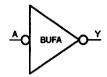

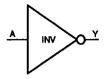

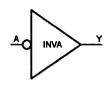

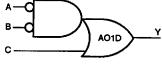

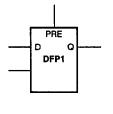

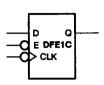

### The ACT 1 Logic Module

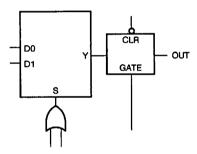

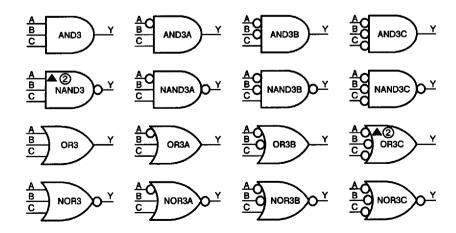

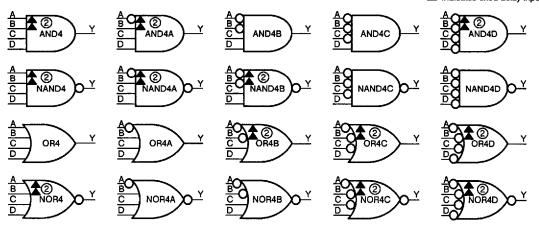

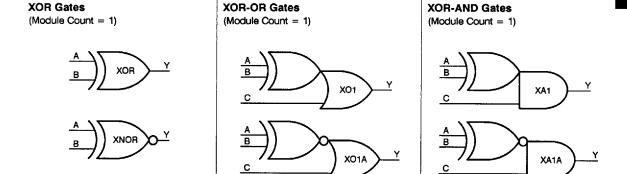

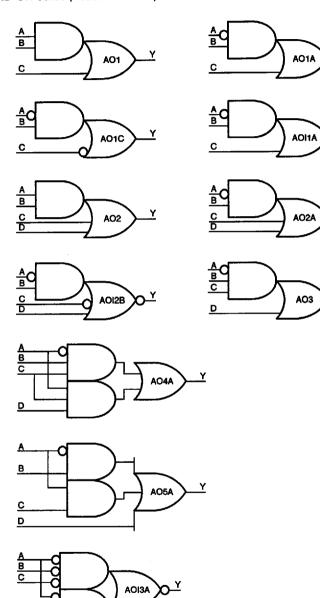

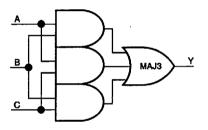

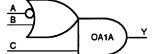

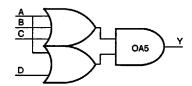

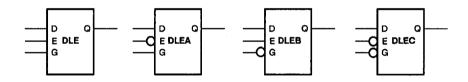

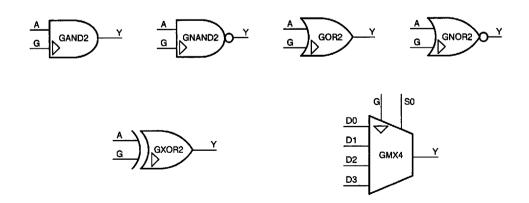

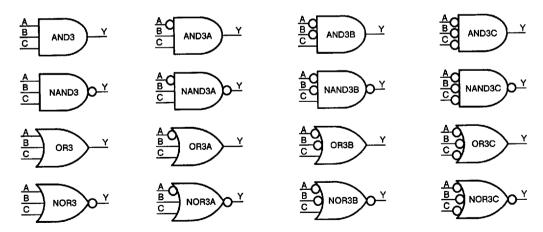

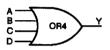

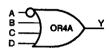

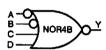

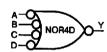

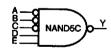

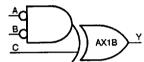

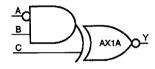

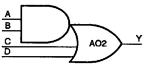

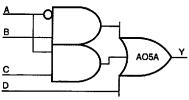

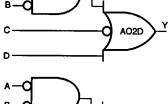

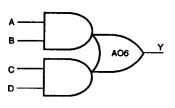

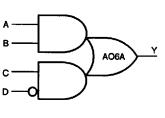

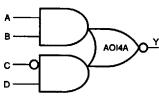

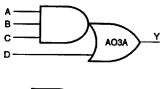

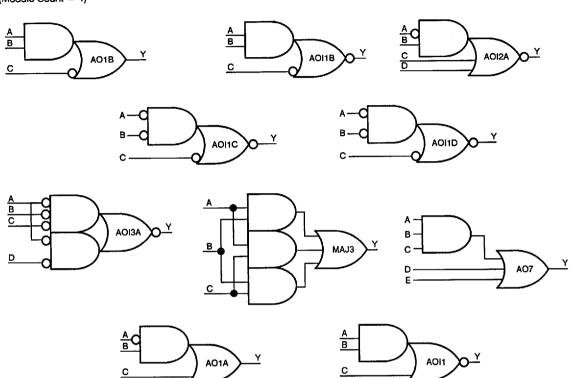

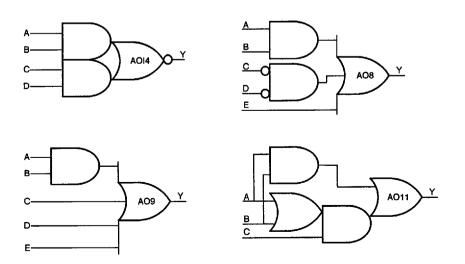

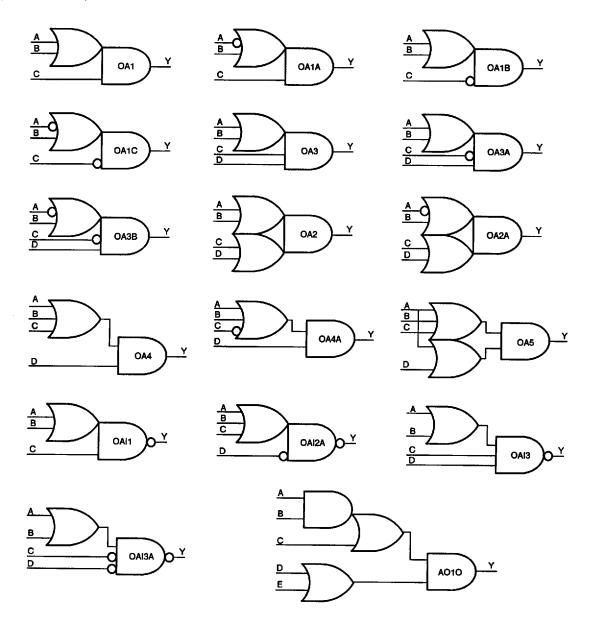

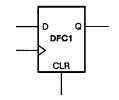

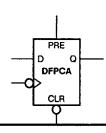

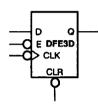

The ACT 1 logic module is an 8-input, one-output logic circuit chosen for the wide range of functions it implements and for its efficient use of interconnect routing resources (Figure 1).

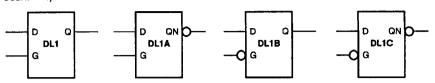

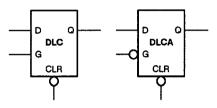

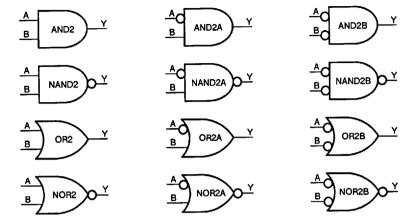

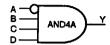

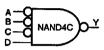

The logic module can implement the four basic logic functions (NAND, AND, OR, and NOR) in gates of two, three, or four inputs. Each function may have many versions, with different combinations of active-low inputs. The logic module can also implement a variety of D-latches, exclusivity function, AND-ORs, and OR-ANDs. No dedicated hardwired latches or flip-flops are required in the array since latches and flip-flops may be constructed from logic modules wherever needed in the application.

Figure 1. ACT 1 Logic Module

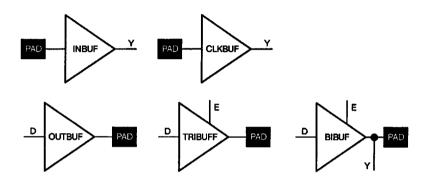

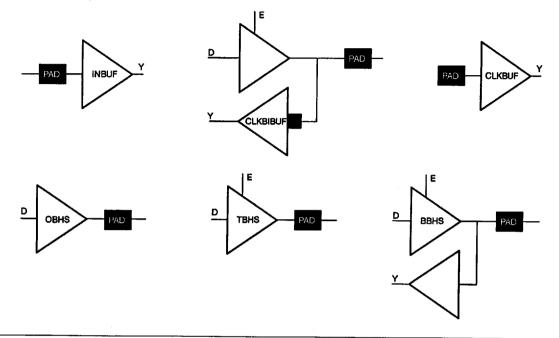

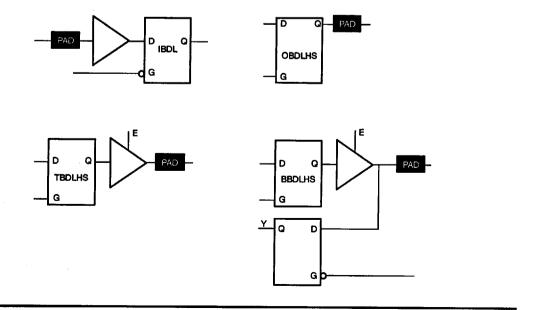

## Programmable I/O Pins

T-46-19-11

Each I/O pin can be configured as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Outputs sink or source 4 mA at TTL levels. See Electrical Specifications for additional I/O buffer specifications.

#### Probe Pin

ACT 1 devices have two independent diagnostic probe pins. These pins allow the user to observe any two internal signals by entering the appropriate net name in the diagnostic software. Signals may be viewed on a logic analyzer using Actel's Actionprobe diagnostic tools. The probe pins can also be used as user-defined I/Os when debugging is finished.

#### **ACT 2 Architecture**

This section of the datasheet is meant to familiarize the user with the architecture of ACT 2 family devices. A generic description of the family will first be presented, followed by a detailed description of the logic blocks, the routing structure, the antifuses, and the special function circuits. Diagrams for the A1280 and A1240 are provided at the end of the datasheet. The additional circuitry required to program and test the devices will not be covered.

## **Array Topology**

The ACT 2 family architecture is composed of five key elements or building blocks: Logic modules, I/O modules, Routing Tracks, Global Clock Networks, and Probe Circuits. The basic structure is similar for all devices in the family, differing only in the number of rows, columns, and I/Os.

Table 1. Array Sizes

| Device | Rows | Columns | Logic | I/O |

|--------|------|---------|-------|-----|

| A1280  | 18   | 82      | 1232  | 140 |

| A1240  | 14   | 62      | 684   | 104 |

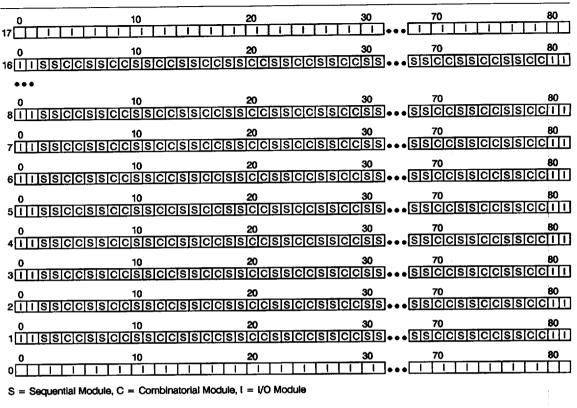

The Logic and I/O modules are arranged in a two-dimensional array (Figure 2). There are three types of modules: Logic, I/O, and Bin. Logic and I/O modules are available as user resources. Bin modules are used during testing and are not available to users.

T-46-19-11

Figure 2. Actel 1280 Simplified Floor Plan

## **Logic Modules**

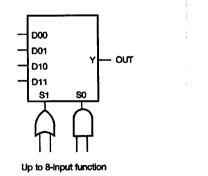

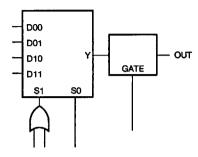

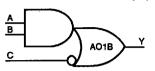

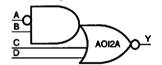

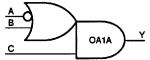

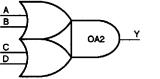

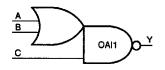

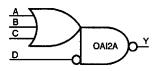

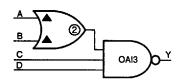

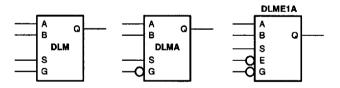

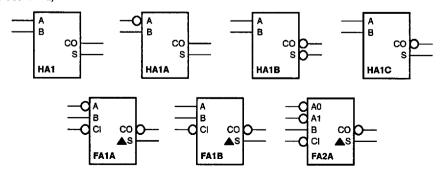

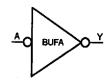

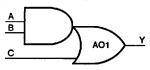

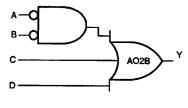

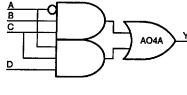

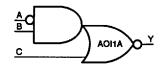

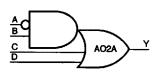

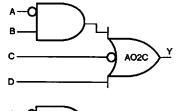

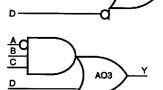

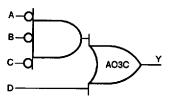

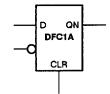

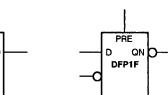

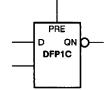

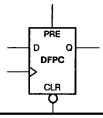

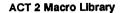

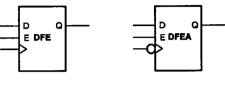

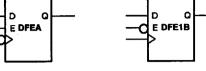

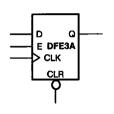

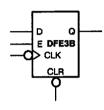

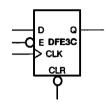

Logic modules are classified into two types: combinatorial C-modules and sequential S-modules (see Figures 3 and 4). The C-module is an enhanced version of the Act 1 family logic module optimized to implement high fan-in combinatorial macros, such as 5-input AND, 5-input OR, etc. The S-module is designed to implement high speed flip-flop functions within a single module. S-modules also include combinatorial logic, which allows an additional level of logic to be implemented without additional propagation delay. C-modules and S-modules are arranged in pairs called module-pairs. Module-pairs are arranged in alternating pairs (shown in Figure 2) and make up the bulk of the array. This arrangement allows the placement software to support two-module macros of four types (CC, CS, SC, and SS). I/O-modules are arranged around the periphery of the array.

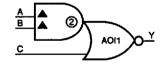

The combinatorial module (shown in Figure 3) implements the following function:

$$Z = !S1 * (D00 * !S0 + D01 * S0) + S1 * (D10 * !S0 + D11 * S0)$$

where:

S0 = A0 \* B0S1 = A1 + B1

Figure 3. C-Module Implementation

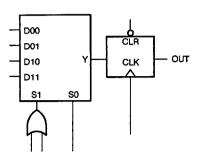

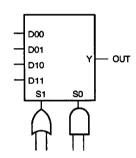

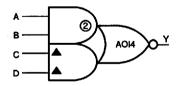

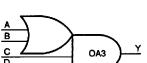

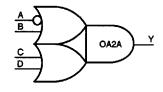

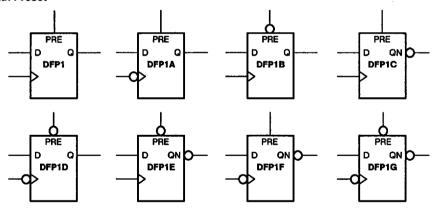

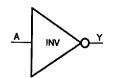

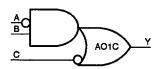

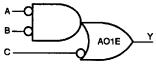

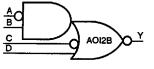

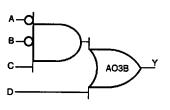

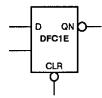

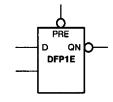

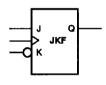

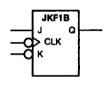

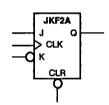

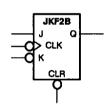

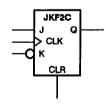

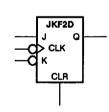

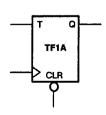

The sequential module implements this same function Z, followed by a sequential block. The sequential block can be configured to implement either a D-type flip-flop or transparent latch. It can also be fully transparent so that S-modules can be used to implement

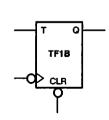

purely combinatorial functions. The function of the sequential module is determined by the macro selection from the design library of hard macros. Allowable S-module implementations are shown in Figure 4. T-46-19-11

Up to 7-input function plus D-type flip-flop with clear

Up to 4-input function plus latch with clear

Up to 7-input function plus latch

Up to 8-input function (same as C-Module)

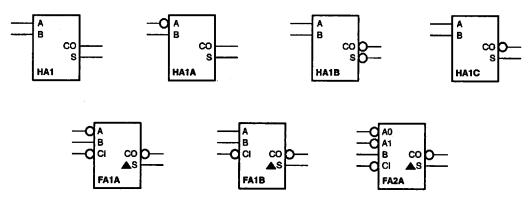

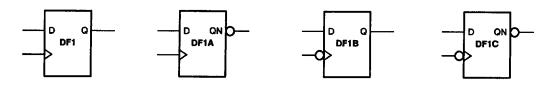

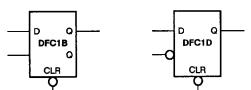

Figure 4. S-Module implementations

#### I/Os

The I/O architecture consists of pad drivers located near the bonding pads and I/O modules located in the array. Top/bottom I/O modules are located in the top and bottom rows respectively. Side I/O modules occupy the leftmost two columns and the rightmost two columns of the array. The function of all I/O modules is identical, but the top/bottom I/O modules have a different routing interface to the array than the side I/O modules. I/Os implement a variety of user functions determined by library macro selection.

## Special Purpose I/Os

Certain I/O pads are temporarily used for programming and testing the device. During normal user operation, these special I/O pads are identical to other I/O pads. The following special I/O pads and their functions are shown in Table 2.

#### Table 2. Special I/O Pads

| SDI    | Serial Data In       |

|--------|----------------------|

| SDIO   | Serial Data Out      |

| BININ  | Binning Circuit In   |

| BINOUT | Binning Circuit Out  |

| DCLK   | Serial Data Clock In |

| PRA    | Probe A Output       |

| PRB    | Probe B Output       |

Two other pads, CLKA and CLKB, also differ from normal I/Os in that they can be used to drive the global clock networks. Power, Ground, and Programming pads are not considered I/O functions. Their function is summarized as follows:

| VCCA, VCCQ, VCCI | Power                 |

|------------------|-----------------------|

| GNDA, GNDQ, GNDI | Circuit Ground        |

| VSV, VKS         | Programming Pads      |

| MODE             | Program/Debug Control |

#### I/O Pads

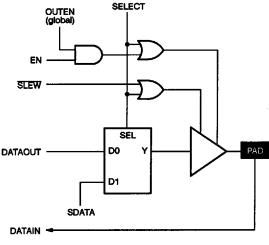

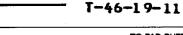

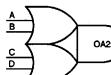

I/O pads are located on the periphery of the die and consist of the bonding pad, the high-drive CMOS drivers, and the TTL level-shifter inputs. Each I/O pad is associated with a specific I/O module. Connections form the I/O pad to the I/O module are made using the signals DATAOUT, DATAIN and EN (shown in Figure 5).

Figure 5. I/O Pad Signals

#### I/O Modules

There are two types of I/O modules: side and top/bottom. The I/O module schematic is shown in Figure 6. In the side I/O modules. there are two inputs supplying the data to be output from the chip: UO1 and UO2. (UO stands for user output). Two are used so that the router can choose to take the signal from either the routing channel above or the routing channel below the I/O module. The top/bottom I/O modules interact with only one channel and therefore have only one UO input.

Figure 6. I/O Module

The EN input enables the tristate output buffer. The global signals INEN and OUTEN (Figure 5) are used to disable the inputs and outputs during certain test modes. Latches are provided in the input and output path. When GOUT is low, the output signal on UO1/UO2 is latched. When it is high, the latch is transparent. The latch can be used as the second stage of a rising-edge flip-flop as described in the Applications note accompanying this data sheet. GIN is the reverse of GOUT. When GIN is high, the input data is latched; when it is low, the input latch becomes transparent.

The output of the module, Y, is used for data being input to the chip. Side I/O modules have a dedicated output segment for Y extending into the routing channels above and below it (similar to logic modules). Side I/O modules may also connect to the array through nondedicated Long Vertical Tracks (LVTs). Top/Bottom I/O modules have no dedicated output segment. Signals coming into the chip from the top or bottom must be routed using F-fuses and LVTs (F-fuses and LVTs are explained in detail in the routing section). As a result, I/O signals connected to I/O modules on either the top or bottom of the array may incur a slight delay penalty (~1nS) over signals connected to I/O modules on the sides.

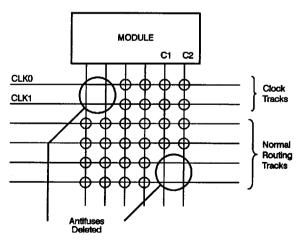

## **Routing Structure**

The ACT 2 architecture uses Vertical and Horizontal routing tracks to interconnect the various Logic and I/O modules. These routing tracks are metal interconnects that may either be of continuous length or broken into pieces called segments. Segments can be joined together at the ends using antifuses to increase their lengths up to the full length of the track.

## **Horizontal Routing**

T-46-19-11

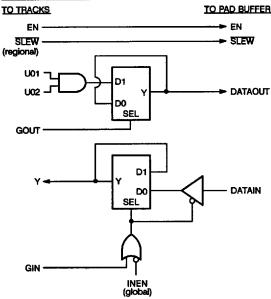

Horizontal channels are located between the rows of modules and are composed of several routing tracks. The horizontal routing tracks within the channel are divided into one or more segments. The minimum horizontal segment length is the width of a module-pair, and the maximum horizontal segment length is the full length of the channel. Any segment that spans more than one-third the row length is considered a long horizontal segment. A typical channel is shown in Figure 7. Nondedicated horizontal routing tracks are used to route signal nets. Dedicated routing tracks are used for the global clock networks and for power and ground tie-off tracks.

Figure 7. Horizontal Routing Tracks and Segments

T-46-19-11

#### **Vertical Routing**

Other tracks run vertically through the modules. Vertical tracks are of three types: input, output, and long. Vertical tracks are also divided into one or more segments. Each segment in an input track is dedicated to the input of a particular module. Each segment in an output track is dedicated to the output of a particular module. Long segments are uncommitted and can be assigned during routing. Each output segment spans four channels (two above and two below), except near the top and bottom of the array where edge effects occur. LVTs contain either one or two segments. An example of vertical routing tracks and segments is shown in Figure 8.

An antifuse is a "normally open" structure as opposed to the normally closed fuse structure used in PROMs or PAL®s. The use of antifuses to implement a Programmable Logic Device results in highly testable structures as well as efficient programming algorithms. The structure is highly testable because there are no pre-existing connections, therefore temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed as well as isolate individual circuit structures to be tested. This can be done both before and after programming. For example, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

#### **Antifuse Structures**

Figure 8. Vertical Routing Tracks and Segments

#### **Antifuse Connections**

Four types of antifuse connections are used in the routing structure of the Act 2 array. (The physical structure of the antifuse is identical in each case, only the usage differs.) The four types are:

| XF | Cross connected antifuse        | Most intersections of horizontal and vertical tracks have an XF that connects the perpendicular tracks.           |

|----|---------------------------------|-------------------------------------------------------------------------------------------------------------------|

| HF | Horizontally connected antifuse | Adjacent segments in the same horizontal track are connected end-to-end by an HF.                                 |

| VF | Vertically connected antifuse   | Some long vertical tracks are divided into two segments. Adjacent long segments are connected end-to-end by a VF. |

| FF | "Fast-Fuse" antifuse            | The FF connects a module output directly to a long vertical track.                                                |

Examples of all four antifuse connections are shown in Figures 7 and 8.

#### **Antifuse Programming**

The ACT 2 family uses the PLICE antifuse developed by Actel. The PLICE element is programmed by placing a high voltage (~20 V) across the element and supplying current (~5 mA) for a short duration (<1mS). In the ACT 2 architecture, most antifuses are programmed to ~500 ohms resistance, except for the F-fuses which are programmed to ~250 ohms. The programming circuits are transparent to the user.

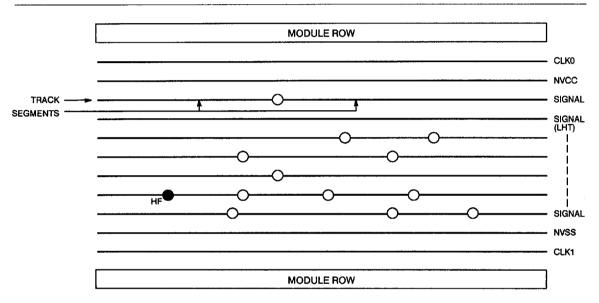

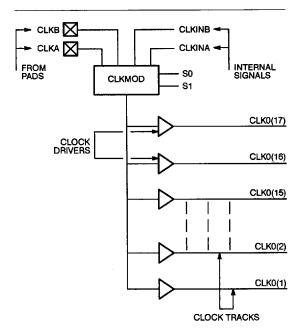

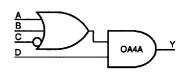

#### **Clock Networks**

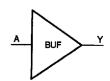

Two low-skew, high fan-out clock distribution networks are provided in the Act 2 architecture (Figure 9). These networks are referred to as CLK0 and CLK1. Each network has a clock module (CLKMOD) that selects the source of the clock signal and may be driven as follows:

- 1. externally from the CLKA pad

- 2. externally from the CLKB pad

- 3. internally from the CLKINA input

- 4. internally from the CLKINB input

The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel.

Figure 9. Clock Networks

The user configures the clock module by selecting one of two clock macros from the macro library. The macro CLKBUF is used to connect one of the two external clock pins to a clock network, and the macro CLKINT is used to connect an internally generate clock signal to a clock network. Since both clock networks are identical, the user does not care whether CLK0 or CLK1 is being used.

The clock input pads may also be used as normal I/Os, by-passing the clock networks.

#### Module Interface

T-46-19-11

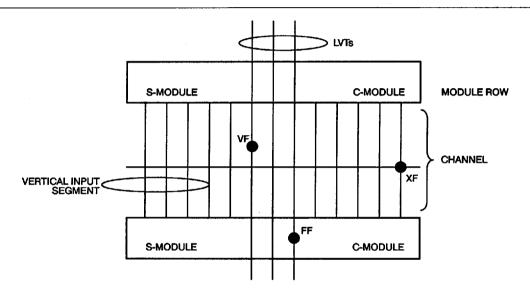

Connections to Logic and I/O modules are made through vertical segments that connect to the module inputs and outputs. These vertical segments lie on vertical tracks that span the entire height of the array.

#### **Module Input Connections**

Vertical tracks span the vertical height of the array. The tracks dedicated to module inputs are segmented by pass transistors in each module row. During normal user operation, the pass transistors are inactive (off), which isolates the inputs of a module from the inputs of the module directly above or below it. During certain test modes, the pass transistors are active (on) to verify the continuity of the metal tracks. Vertical input segments span only one channel. Inputs to the array modules come either from the channel above or the channel below. The logic modules are arranged such that half of the inputs are connected to the channel above and half of the inputs to segments in the channel below (Figure 10).

#### **Module Output Connections**

Module outputs have dedicated output segments. Output segments extend vertically two channels above and two channels below, except at the top or bottom of the array. Output segments twist, as shown in Figure 10, so that only four vertical tracks are required.

#### LVT Connections

Outputs may also connect to nondedicated segments, (LVTs). Each module pair in the array shares three LVTs that span the length of column as shown in Figure 9. Any module in the column pair can connect to one of the LVTs in the column using an FF connection. The FF connection uses antifuses connected directly to the driver stage of the module output, by-passing the isolation transistor. FF antifuses are programmed at a higher current level than HF, VF, or XF antifuses to produce a lower resistance value.

#### **Antifuse Connections**

In general every intersection of a vertical segment and a horizontal segment contains an unprogrammed antifuse (XF-type). One exception is in the case of the clock networks.

Figure 10. Logic Module Routing Interface

## **Clock Connections**

To minimize loading on the clock networks, only a subset of inputs has fuses on the clock tracks. Only a few of the C-module and

S-module inputs can be connected to the clock networks. To further reduce loading on the clock network, only a subset of the horizontal routing tracks can connect to the clock inputs of the S-Module. Both of these are illustrated in Figure 11.

Figure 11.

ACT 1 and ACT 2 Military FPGAs

#### **Programming and Test Circuits**

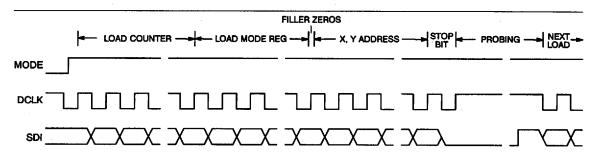

The array of logic and I/O modules is surrounded by test and programming circuits controlled by the external pins: MODE, SDI, and DCLK. The function of these pins is summarized below. When MODE is low (GND), the device is in normal or user mode. When MODE is high (VCC), the device is placed into one of several programming or test states. The SDI pin (when MODE is high) is used to input serial data to the Mode register and various address

registers surrounding the array. Data is clocked into these registers using the DCLK pin. The registers are connected as a long series of shift registers as shown in Figure 12. The Mode register determines the test or programming state of the device. Many of the test modes are used during wafer sort and final test at the factory. Other test modes are used during programming in the Activator 2, and some of the modes are available only after programming. The Actionprobe function is one such function available to users.

T-46-19-11 - SDI MODE REGISTER DCLK ■ MODE Y1<0> Y1 REGISTER Y1<c> Y2 REGISTER Y2<c> Y2<0> છું REGISTER K2 REGISTER MODULE ARRAY OTHER REGISTERS

Figure 12. ACT 2 Shift Register

#### Actionprobe

SDO G

If a device has been successfully programmed and the security fuse has not been programmed, any internal logic or I/O module output can be observed using the Actionprobe circuitry and the PRA and/or PRB pins. The Actionprobe Diagnostic system provides the software and hardware required to perform real-time debugging. The software automatically performs the following functions.

A pattern of "1s" and "0s" is shifted into the device from the SDI pin at each positive edge transition of DCLK. The complete sequence contains 10 bits of counter, 21 bits of Mode Register, n bits of zeros (filler of unused fields, where n depends on the particular device type), R bits of X2, C bits of Y2, R bits of X1, C bits of Y1, and a stop bit ("0" or "1"). After the stop bit has been shifted in, DCLK is left high (see definitions below). X1 and Y1 represent the (X,Y) location in the array for the Actionprobe output, PRA.

T-46-19-11

X2 and Y2 represent the (X,Y) location in the array for the Actionprobe output, PRB. R and C are the row and column size as defined in Table 1. The filler bits, counter pattern, and Mode register pattern are shown in Table 3. Addressing for rows and columns is active high, i.e. unselected rows and columns are "zeros"

and the selected row and column is "high." The timing sequence is shown in Figure 13. The recommended frequency is 10 MHz with 10 nS setup and hold times allowing for SDI and DCLK transitions. The selected module output will be present at the PRA or PRB output approximately 20 nS after the stop-bit transition.

Table 3. Bit Stream Definitions for Actionprobe Diagnostics

| Device | Probe_Mode    | Filler (n) | Counter_Pattern | Mode_Register_Pattern | # of clocks |

|--------|---------------|------------|-----------------|-----------------------|-------------|

| A1280  | Probe A only  | 443        | 0011011111      | 000000110001111100000 | 675         |

| A1280  | Probe B only  | 443        | 0011011111      | 000000101001111100000 | 675         |

| A1280  | Probe A and B | 443        | 0011011111      | 000000111001111100000 | 675         |

| A1240  | Probe A only  | 361        | 1111000001      | 000000110001111100000 | 541         |

| A1240  | Probe B only  | 361        | 1111000001      | 000000101001111100000 | 541         |

| A1240  | Probe A and B | 361        | 1111000001      | 000000111001111100000 | 541         |

| A1225  | Probe A only  | 308        | 1101011010      | 000000110001111100000 | 458         |

| A1225  | Probe B only  | 308        | 1101011010      | 000000101001111100000 | 458         |

| A1225  | Probe A and B | 308        | 1101011010      | 000000111001111100000 | 458         |

For Example: Selecting PRA for A1280 results in the following bit stream:

0011011111 000000110001111100000

(443 zeros)\_X2<0>...X2<17>\_Y2<81>...Y2<0>\_X1<0>...X1<17>\_Y1<0>...X1<17>\_Y1<0>...Y1<81>\_0,

where "\_" is used for clarity only.

Figure 13. Timing Waveforms

**ACT 1 and ACT 2 Military FPGAs**

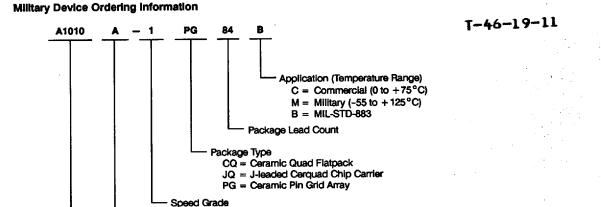

Part Number

A1010A A1020A A1240 -1200 Gates -2000 Gates -4000 Gates

Die Revision

Std = Standard Speed -1 = Standard + 15% Speed

A1280

-8000 Gates

## SMD Drawing Number to Actel Part Number Cross Reference

| SMD Number      | Cage Number | Actel Part Number |

|-----------------|-------------|-------------------|

| 5962-9096401MZX | 0J4Z0       | A1010A-PG84B      |

| 5962-9096501MXX | 0J4Z0       | A1020A-JQ44B      |

| 5962-9096501MYX | 0J4Z0       | A1020A-JQ68B      |

| 5962-9096501MZX | 0J4Z0       | A1020A-JQ84B      |

| 5962-9096501MUX | 0J4Z0       | A1020A-PG84B      |

| 5962-9096501MTX | 0J4Z0       | A1020A-CQ84B      |

\* Speed Grade: -1 = 15% faster than Standard

## **Product Plan**

## T-46-19-11

|                                           | Speed Grade |     |          | cation |    |   |

|-------------------------------------------|-------------|-----|----------|--------|----|---|

|                                           | Std         | -1* | C        | М      | В  | E |

| A1280 Device                              |             |     |          |        |    |   |

| 176-pin Ceramic Pin Grid Array (PG)       | ~           | P   | <u> </u> | v      | v  | _ |

| 172-pin Ceramic Quad Flatpack (CQ)        | ~           | P   | ~        | ~      | M  | • |

| A1240 Device                              |             |     | *****    |        |    |   |

| 132-pin Ceramic Pin Grid Array (PG)       | V           | Р   | V        | V      | u  | _ |

| A1020A Device                             |             |     |          |        |    |   |

| 84-pin Ceramic Pin Grid Array (PG)        | ~           | V   | ~        | v      | V  | _ |

| 84-pin Ceramic Quad Flatpack (CQ)         | ~           | ~   | ~        | -      | M  | ~ |

| 84-pin J-leaded Cerquad Chip Carrier (JQ) | <b>u</b>    | ~   | ~        | M      | in | _ |

| 68-pin J-leaded Cerquad Chip Carrier (JQ) | <b>u</b>    | r   | v        | _      | ~  | _ |

| 44-pin J-leaded Cerquad Chip Carrier (JQ) | <b>u</b>    | ~   | ~        | ~      | ~  | _ |

| A1010A Device                             |             |     |          |        |    |   |

| 84-pin Ceramic Pin Grid Array (PG)        | V           | ~   | <i>ν</i> | ~      | ~  | _ |

Applications:C = Commercial

Availability: u = Available P = Planned

M = Military B = MIL-STD-883C

- = Not Planned

E = Extended Flow

**Device Resources**

|        |         |       |         |         |        | User    | I/Os   |        | -      |        |

|--------|---------|-------|---------|---------|--------|---------|--------|--------|--------|--------|

|        | Logic   |       |         | CPGA    |        | CQ      | FP     |        | JQCC   |        |

| Device | Modules | Gates | 176-pin | 132-pin | 84-pin | 172-pin | 84-pin | 84-pin | 68-pin | 44-pin |

| A1280  | 1232    | 8000  | 140     | -       | _      | 140     | _      | _      | _      | _      |

| A1240  | 684     | 4000  | _       | 104     | _      | _       | _      | _      | _      | _      |

| A1020A | 547     | 2000  | _       | _       | 69     | _       | 69     | 69     | 57     | 34     |

| A1020A | 295     | 1200  | -       | _       | 57     | _       | _      | _      | _      |        |

ACT 1 and ACT 2 Military FPGAs

## Pin Description

#### CLKA Clock A (input)

TTL Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

#### CLKB Clock B (Input)

TTL Clock input for clock distribution networks. The Clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

### DCLK Diagnostic Clock (Input)

TTL Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### GND Ground (Input)

Input LOW supply voltage.

## I/O Input/Output (Input, Output)

I/O pins function as an input, output, three-state, or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/O pins are automatically driven LOW by the ALS software.

#### MODE Mode (Input)

The MODE pin controls the use of multi-function pins (DCLK, PRA, PRB, SDI, SDO). When the MODE pin is HIGH, the special functions are active. When the MODE pin is LOW, the pins function as I/Os.

#### NC No Connection

This pin is not connected to circuitry within the device.

#### PRA Probe A (Output)

The Probe A pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the Probe B pin to allow real-time diagnostic output of any signal path within the device. The Probe A

pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRA is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

## PRB Probe B (Output) T-46-19-11

The Probe B pin is used to output data from any user-defined design node within the device. This independent diagnostic pin is used in conjunction with the Probe A pin to allow real-time diagnostic output of any signal path within the device. The Probe B pin can be used as a user-defined I/O when debugging has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. PRB is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDI Serial Data input (Input)

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDO Serial Data Output (Output)

Serial data output for diagnostic probe. SDO is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### V<sub>CC</sub> Supply Voltage (Input)

Input HIGH supply voltage.

#### V<sub>KS</sub> Programming Voltage (input)

Input supply voltage used for device programming. This pin must be connected to GND during normal operation.

## V<sub>PP</sub> Programming Voltage (Input)

Input supply voltage used for device programming. This pin must be connected to  $V_{\rm CC}$  during normal operation.

## V<sub>SV</sub> Programming Voltage (input)

Input supply voltage used for device programming. This pin must be connected to V<sub>CC</sub> during normal operation.

**Actel Military Product Flow**

T-46-19-11

| Step | Screen                                                                                                                            | 883C—Clasa B<br>883C Method                               | 883C—Class B<br>Requirement | Military<br>Datasheet<br>Requirement |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------|--------------------------------------|

| 1.0  | Internal Visual                                                                                                                   | 2010, Test Condition B                                    | 100%                        | 100%                                 |

| 2.0  | Temperature Cycling                                                                                                               | 1010, Test Condition C                                    | 100%                        | 100%                                 |

| 3.0  | Constant Acceleration                                                                                                             | 2001, Test Condition E<br>(min), Y1, Orientation only     | 100%                        | 100%                                 |

| 4.0  | Seal<br>a. Fine<br>b. Gross                                                                                                       | 1014                                                      | 100%<br>100%                | 100%<br>100%                         |

| 5.0  | Visual Inspection                                                                                                                 |                                                           | 100%                        | 100%                                 |

| 6.0  | Pre Burn-in<br>Electrical Parameters                                                                                              | In accordance with Actel applicable device specifications | 100%                        | N/A                                  |

| 7.0  | Burn-in Test                                                                                                                      | 1015 Condition D<br>160 hours @ 125°C Min.                | 100%                        | N/A                                  |

| 8.0  | Interim (post burn-in)<br>Electrical Parameters                                                                                   | In accordance with Actel applicable device specifications | 100%                        | 100%<br>(as final test)              |

| 9.0  | Percent Defective Allowable                                                                                                       | 5%                                                        | All Lots                    | N/A                                  |

| 10.0 | Final Electrical Test  a. Static Tests (1) 25°C (Subgroup 1, Table I, 5005) (2) -55°C and +125°C. (Subgroups 2, 3, Table I, 5005) | In accordance with Actel applicable device specifications | 100%                        | 100%                                 |

|      | b. Dynamic and Functional Tests (1) 25°C (Subgroup 7, Table I, 5005) (2) -55°C and +125°C. (Subgroups 8A and 8B, Table I, 5005)   |                                                           | 100%                        | 100%                                 |

|      | c. Switching Tests at 25°C<br>(Subgroup 9, Table 1, 5005)                                                                         |                                                           | 100%                        | 100%                                 |

| 11.0 | Gualification or Quality<br>Conformance Inspection Test<br>Sample Selection (Group A)                                             | 5005                                                      | All Lots                    | N/A                                  |

| 12.0 | External Visual                                                                                                                   | 2009                                                      | 100%                        | Actel specification                  |

#### **ACT 1 and ACT 2 Military FPGAs**

T-46-19-11

##

| Actel | Extended Flow <sup>1, 2</sup>                                                                                                                        |                                                          |                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------|

|       | Screen                                                                                                                                               | Method R                                                 | tequirement    |

| 1.    | Wafer Lot Acceptance <sup>3</sup>                                                                                                                    | 5007 with step coverage waiver                           | All Lots       |

| 2.    | Destructive In-Line Bond Pull <sup>4</sup>                                                                                                           | 2011, condition D                                        | Sample         |

| 3.    | Internal Visual                                                                                                                                      | 2010, condition A                                        | 100%           |

| 4.    | Temperature Cycling                                                                                                                                  | 1010, condition C                                        | 100%           |

| 5.    | Constant Acceleration                                                                                                                                | 2001, condition E (min) Y <sub>1</sub> orientation only  | 100%           |

| 6.    | Visual Inspection                                                                                                                                    | 2009                                                     | 100%           |

| 7.    | Particle Impact Noise Detection                                                                                                                      | 2020, condition A                                        | 100%           |

| 8.    | Serialization                                                                                                                                        |                                                          | 100%           |

| 9.    | Pre Burn-in Electrical Parameters                                                                                                                    | In accordance with Actel applicable device specification | 100%           |

| 10.   | Burn-in Test                                                                                                                                         | 1015, 240 hours @ 125°C minimum                          | 100%           |

| 11.   | Interim (Post Burn-In) Electrical Parameters                                                                                                         | In accordance with Actel applicable device specification | 100%           |

| 12.   | Reverse Bias Burn-in                                                                                                                                 | 1015, condition A or C, 72 hours @ 150°C minimum         | 100%           |

| 13.   | Interim (Post Burn-in) Electrical Parameters                                                                                                         | In accordance with Actel applicable device specification | 100%           |

| 14.   | Percent Defective Allowable (PDA) Calculation                                                                                                        | 5%, 3% functional parameters @ 25°C                      | All Lots       |

| 15.   | Final Electrical Test                                                                                                                                | In accordance with Actel applicable device specification | 100%           |

|       | <ul> <li>a. Static Tests</li> <li>(1) 25°C</li> <li>(Subgroup 1, Table 1)</li> <li>(2) -55°C and 125°C</li> <li>(Subgroups 2, 3, Table 1)</li> </ul> | 5005<br>5005                                             | 100%           |

|       | b. Dynamic or Functional Tests (1) 25°C (Subgroup 4 or 7, Table 1) (2) -55°C and 125°C                                                               | 5005<br>5005                                             | 100%           |

|       | (Subgroups 5 and 6, or 8 a and b, Table 1)  c. Switching Tests at 25°C (Subgroup 9, Table 1)                                                         | 5005                                                     | 100%           |

| 16.   | Seal                                                                                                                                                 | 1014                                                     | 100%           |

|       | a. Fine<br>b. Gross                                                                                                                                  |                                                          |                |

| 17.   | Radiographic                                                                                                                                         | 2012, two views                                          | 100%           |

| 18.   | Qualification or Quality Conformance Inspection<br>Test Sample Selection                                                                             | 5005                                                     | Per<br>Group A |

| 19.   | External Visual                                                                                                                                      | 2009                                                     | 100%           |

#### Notes:

- 1. Actel offers the Extended Flow in order to satisfy those customers that require additional screening beyond the requirements of MIL-STD-883C, Class B. Actel is compliant to the requirements of MIL-STD-883C, Paragraph 1.2.1, and MIL-M-38510 Appendix A. Actel is offering this extended flow incorporating the majority of the screening procedures as outlined in Method 5004 of MIL-STD-883C Class S. The exceptions to Method 5004 are as shown in Notes 2-4 below.

- 2. Method 5004 requires 100% Radiation Latch-up testing to Method 1020. Actel will not be performing any radiation testing and this requirement must be waived in its entirety.

- 3. Wafer lot acceptance is performed to Method 5007, however the step coverage requirement as specified in Method 2018 must be waived.

- 4. Method 5004 requires a 100%, Non-Destructive Bond Pull to Method 2023. Actel substitutes a Non-Destructive Bond Pull to Method 2011, condition D on a sample basis only.

## **Absolute Maximum Ratings**

Free air temperature range

| Symbol          | Parameter                            | Limits                       | Units |

|-----------------|--------------------------------------|------------------------------|-------|

| Vcc             | DC Supply Voltage <sup>1, 2, 3</sup> | -0.5 to +7.0                 | Volts |

| Vi              | Input Voltage                        | -0.5 to V <sub>CC</sub> +0.5 | Volts |

| Vo              | Output Voltage                       | -0.5 to V <sub>CC</sub> +0.5 | Volts |

| I <sub>IK</sub> | Input Clamp Current                  | ±20                          | mA    |

| lok             | Output Clamp Current                 | ±20                          | mA    |

| lok             | Continuous Output Current            | ±25                          | mA    |

| TSTG            | Storage Temperature                  | -65 to +150                  | °C    |

Stresses beyond those listed above may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Device should not be operated outside the Recommended Operating Conditions.

- 1. VPP = VCC, except during device programming.

- 2. V<sub>SV</sub> = V<sub>CC</sub>, except during device programming.

- 3. VKS = GEN, except during device programming.

## **Package Thermal Characteristics**

The device junction to case thermal characteristic is  $\theta$  jc, and the junction to ambient air characteristic is  $\theta$ ja. The thermal characteristics for  $\theta$ ja are shown with two different air flow rates.

T-46-19-11

**Recommended Operating Conditions**

| Parameter                         | Commercial | Military    | Units            |

|-----------------------------------|------------|-------------|------------------|

| Temperature<br>Range <sup>1</sup> | 0 to +70   | -55 to +125 | ۰c               |

| Power Supply<br>Tolerance         | ±5         | ±10         | %V <sub>CC</sub> |

#### Note:

1. Ambient temperature (TA) is used for commercial and industrial; case temperature (T<sub>C</sub>) is used for military.

Maximum junction temperature is 150°C.

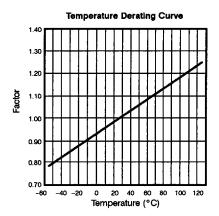

A sample calculation of the maximum power dissipation for a CPGA 176-pin package at military temperature is as follows:

$$\frac{\text{Max. junction temp. (°C) - Max. military temp. (°C)}}{\theta \text{ja (°C/W)}} = \frac{150 \text{°C} - 125 \text{°C}}{20 \text{°C/W}} = 1.2 \text{ W}$$

| Package Type                  | Pin Count | θjο | θja<br>Still air |    | θja<br>300 ft/min. <sup>Unita</sup> |

|-------------------------------|-----------|-----|------------------|----|-------------------------------------|

| Ceramic Pin Grid Array        | 84        | 8   | 33               | 20 | °C/W                                |

|                               | 132       | 5   | 30               | 15 | °C/W                                |

|                               | 176       | 2   | 20               | 8  | °C/W                                |

| Ceramic Quad Flatpack         | 84<br>172 | 5   | 40               | 30 | °C/W                                |

| J-leaded Cerquad Chip Carrier | 44        | 8   | 38               | 30 | °C/W                                |

|                               | 68        | 8   | 35               | 25 | •C/W                                |

|                               | 84        | 8   | 34               | 24 | °C/W                                |

### **ACT 1 Electrical Specifications**

Parameter

#### T-46-19-11 Military Units Max. Min. ٧ ٧ 3.7 0.33 0.40 ٧ 0.8 ٧ -0.3 ٧ 2.0 $V_{CC} + 0.3$

| Input Transition Tim           | ıet <sub>R</sub> , t⊊²              |     | 500  |     | 500  | TR. |

|--------------------------------|-------------------------------------|-----|------|-----|------|-----|

| C <sub>IO</sub> I/O Capacitano | e <sup>2, 3</sup>                   |     | 10   |     | 10   | pl  |

| Standby Current, Ic            |                                     |     | 10   |     | 25   | m   |

| Leakage Current <sup>5</sup>   |                                     | -10 | 10   | -10 | 10   | μ/  |

| Ios Output Short               | (V <sub>O</sub> = V <sub>CC</sub> ) | 20  | 140  | 20  | 140  | m   |

| Circuit Current <sup>6</sup>   | (V <sub>O</sub> = GND)              | -10 | -100 | -10 | -100 | m   |

Commercial

Max.

8.0

$V_{CC} + 0.3$

Min.

3.84

-0.3

2.0

#### Notes:

V<sub>OH</sub>1

Vol

VIL

$V_{IH}$

- 1. Only one output tested at a time.  $V_{CC} = min$ .

- 2. Not tested, for information only.

- 3. Includes worst-case 84-pin PLCC package capacitance.  $V_{OUT} = 0 \text{ V, f} = 1 \text{ MHz.}$

$(I_{OH} = -4 \text{ mA})$

$(I_{OL} = 4 \text{ mA})$

$(I_{OH} = -3.2 \text{ mA})$

- 4. Typical standby current = 3 mA. All outputs unloaded. All inputs = V<sub>CC</sub> or GND.

- 5.  $V_0$ ,  $V_{IN} = V_{CC}$  or GND.

- 6. Only one output tested at a time. Min. at  $V_{CC} = 4.5 \text{ V}$ ; Max. at  $V_{CC} = 5.5 \text{ V}$ .

**ACT 2 Electrical Specifications**

| Parameter                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Co   | Commercial            |      | Allitary              | Unite   |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|-----------------------|---------|

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min. | Max.                  | Min. | Max.                  | _ Units |

|                                                       | (I <sub>OH</sub> = -6 mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.84 |                       |      |                       | V       |

| V <sub>OH</sub> <sup>1</sup> -                        | (I <sub>OH</sub> = -4 mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                       | 3.7  |                       | ٧       |

| V <sub>OL</sub> <sup>1</sup>                          | (I <sub>OL</sub> = 6 mA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 0.33                  |      | 0.40                  |         |

| V <sub>IL</sub>                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -0.3 | 0.8                   | -0.3 | 0.8                   | ٧       |

| V <sub>IH</sub>                                       | - Marie - Mari | 2.0  | V <sub>CC</sub> + 0.3 | 2.0  | V <sub>CC</sub> + 0.3 | ٧       |

| Input Transition Time t <sub>R</sub> , t <sub>F</sub> | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      | 500                   |      | 500                   | ns      |

| C <sub>IO</sub> I/O Capacitance <sup>2, 3</sup>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 10                    |      | 10                    | pF      |

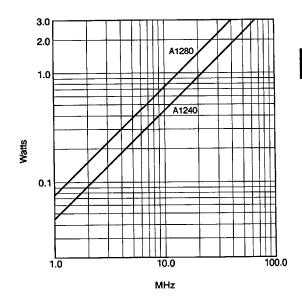

| Standby Current, I <sub>CC</sub> <sup>4</sup>         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | 10                    |      | 25                    | mA      |