### Features

- Compatible with an Embedded ARM7TDMI<sup>™</sup> Processor

- Programmable Baud Rate Generator

- Parity, Framing and Overrun Error Detection

- Line Break Generation and Detection

- Automatic Echo, Local Loopback and Remote Loopback Channel Modes

- Multi-drop Mode: Address Detection and Generation

- Interrupt Generation

- Two Dedicated Peripheral Data Controller Channels Can be Easily Implemented

- 5-, 6-, 7-, 8- and 9-bit Character Length

- Full Scan Testable (up to 98%)

- Can be Directly Connected to the Atmel Implementation of the AMBA<sup>™</sup> Peripheral Bus (APB)

### Description

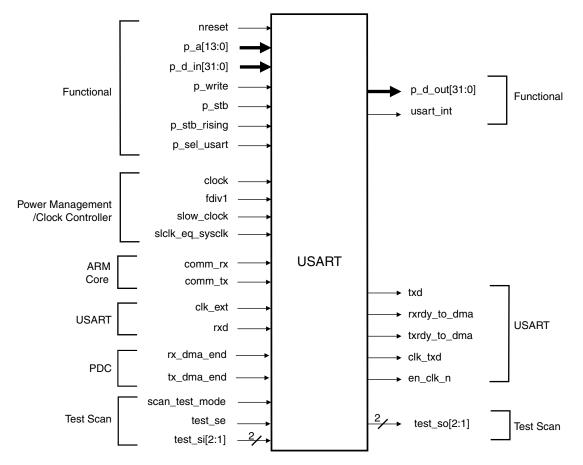

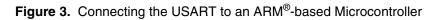

The two-channel, full-duplex USART features parity, framing and overrun error detection. A baud rate generator provides the bit period clock named the Baud Rate Clock to both the receiver and the transmitter. The USART can be programmed to operate in three different test modes: automatic echo, local loopback and remote loopback.

Two dedicated Peripheral Data Controller channels can be easily implemented. One is dedicated to the receiver. The other is dedicated to the transmitter.

The generation of interrupts is controlled in the status register by asserting the corresponding interrupt line.

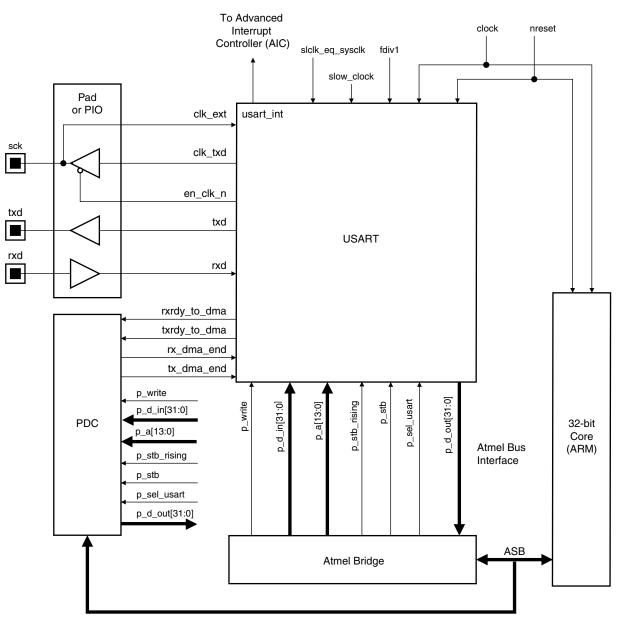

The USART can be used with any 32-bit microcontroller core if the timing diagram shown on page 8 is respected. When using an ARM7TDMI as the core, the Atmel Bridge must be used to provide the correct bus interface to the peripheral.

# 32-bit Embedded ASIC Core Peripheral

# USART

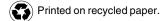

#### Figure 1. USART Symbol

# 2 USART

#### Active Name Function Туре Level Comments Functional nreset Reset System Input Low Resets all the counters and signals Address Bus Input The address takes into account the 2 LSBs p\_a[13:0] [1:0], but the macrocell does not take these bits into account (left unconnected). p\_d\_in[31:0] Input Data Bus Input From host (bridge) p\_d\_out[31:0] **Output Data Bus** Output \_ To host (bridge) Write Enable From host (bridge) p\_write Input High p\_stb Peripheral Strobe Input High From host (bridge) User Interface Clock Signal From host (bridge). Clock for all DFFs p\_stp\_rising Input controlling the configuration registers. Selection of the block High From host (bridge) p\_sel\_usart Input usart\_int Interrupt signal to AIC Output High **Power Management/Clock Controller** clock System Clock Input System clock for the USART output waveforms fdiv1 **USART Clock Enable** System clock (clock) divided Input \_ ARM<sup>®</sup> Core Operation slow\_clock Input ARM<sup>®</sup> Core Operation slclk\_eq\_sysclk Input **ARM®** Core ARM<sup>®</sup> Core Operation Input Must be connected to ARM core. comm rx High ARM<sup>®</sup> Core Operation Input High Must be connected to ARM core. comm\_tx USART From SCK pad clk\_ext Baud rate signal Input \_ Receive serial data pin rxd Input \_ Output txd Transmit serial data pin \_ Output rxrdy\_to\_dma Output signal to DMA channel High Byte available in the Receiver Holding Register (RHR). This signal connects to the PDC<sup>(1)</sup> Output signal to the DMA There are no more characters in the Output High txrdy\_to\_dma channel Transmitter Holding Register (THR). This signal connects to the PDC<sup>(1)</sup> Output of the baud rate To SCK pad clk\_txd Output \_ generator Direction signal for SCK pad Output Active in synchronous mode en\_clk\_n \_ PDC rx\_dma\_end End of receive DMA transfer Input High Generated by PDC<sup>(1)</sup> tx dma end End of transmit DMA transfer Input High Generated by PDC<sup>(1)</sup>

#### Table 1. USART Pin Description

#### Table 1. USART Pin Description

| Name           | Function                                  | Туре      | Active<br>Level | Comments                |

|----------------|-------------------------------------------|-----------|-----------------|-------------------------|

|                |                                           | Test Scar | า               |                         |

| scan_test_mode | Must be set when running the scan vectors | Input     | High            |                         |

| test_se        | Scan test enable                          | Input     | High/Low        | Scan shift/scan capture |

| test_si[2:1]   | Scan test input                           | Input     | High            | Entry of scan chain     |

| test_so[2:1]   | Scan test output                          | Output    | -               | Output of scan chain    |

Note: 1. The Peripheral Data Controller (PDC) is a separate block. Please refer to the corresponding datasheet.

### Scan Test Configuration

The fault coverage is maximum if all non-scan inputs can be controlled and all non-scan outputs can be observed. In order to achieve this, the ATPG vectors must be generated on the entire circuit (top-level), which includes the USART, or all USART I/Os must have a top-level access and ATPG vectors must be applied to these pins.

# USART

4

Figure 2. USART Block Diagram

### Peripheral Data Controller (PDC)

When the dedicated Atmel PDC is used, four additional registers are available in the USART (see page 16). These registers are physically located in the PDC and accessed when selecting the USART. For more details concerning these registers, please refer to the PDC datasheet.

The following pins are exclusively reserved for use with the PDC: rxrdy\_to\_dma, txrdy\_to\_dma, rx\_dma\_end, tx\_dma\_end. If the PDC is not used, rx\_dma\_end and tx\_dma\_end must be tied to zero.

### **Pin Description**

Each USART channel has the following external signals:

| Name | Description                                                                                                                                                                                                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sck  | USART Serial clock can be configured as input or output:<br>sck is configured as input if an external clock is selected (USCLKS = 11)<br>sck is driven as output if the external clock is disabled (USCLKS[1] = 0) and clock output<br>is enabled (CLKO = 1) |

| txd  | Transmit Serial Data is an output                                                                                                                                                                                                                            |

| rxd  | Receive Serial Data is an input                                                                                                                                                                                                                              |

USART

6

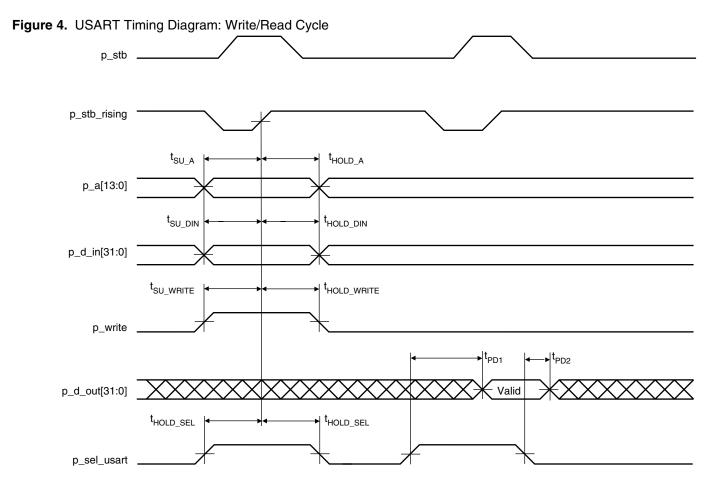

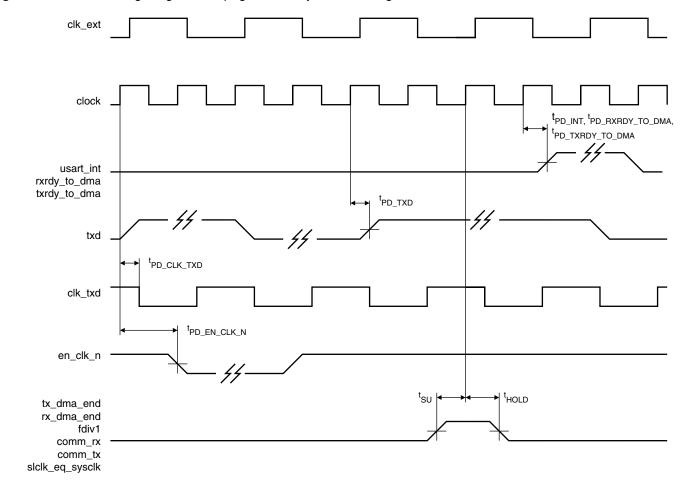

## **Timing Diagrams**

# USART

8

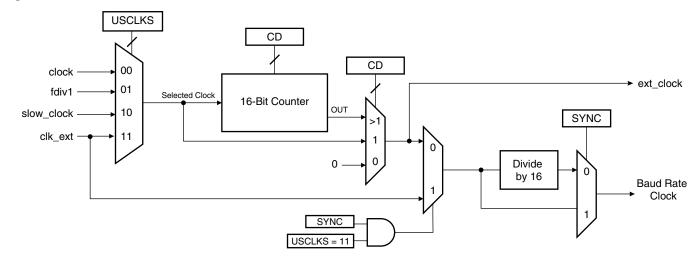

### Baud Rate Generator

The Baud Rate Generator provides the bit period clock named the Baud Rate Clock to both the receiver and the transmitter.

The Baud Rate Generator can select between external and internal clock sources. The external clock source is SCK (clk\_ext) or slow\_clock. The internal clock sources can be either the master clock (clock) or the master clock divided (fdiv1).

Note: In all cases, if an external clock is used, the duration of each of its levels must be longer than the system clock (clock) period. The external clock frequency must be at least 4.5 times lower than the system clock.

When the USART is programmed to operate in asynchronous mode (SYNC = 0 in the Mode Register US\_MR), the selected clock is divided by 16 times the value (CD) written in US\_BRGR (Baud Rate Generator Register). If US\_BRGR is set to 0, the Baud Rate Clock is disabled.

Baud Rate =  $\frac{\text{Selected Clock}}{16 \times \text{CD}}$

When the USART is programmed to operate in synchronous mode (SYNC = 1) and the selected clock is internal (USCLKS[1] = 0 in the Mode Register US\_MR), the Baud Rate Clock is the internal selected clock divided by the value written in US\_BRGR. If US\_BRGR is set to 0, the Baud Rate Clock is disabled.

Baud Rate =

$$\frac{\text{Selected Clock}}{\text{CD}}$$

In synchronous mode with external clock selected (USCLKS = 11), the clock is provided directly by the signal on the SCK pin (clk\_ext). No division is active. The value written in US\_BRGR has no effect.

Figure 6. Baud Rate Generator

#### Receiver

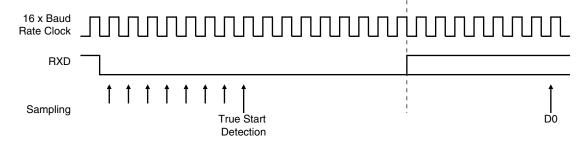

#### Asynchronous Receiver

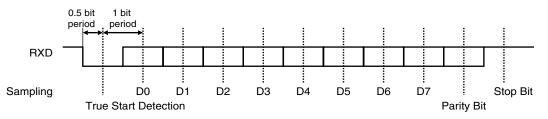

The USART is configured for asynchronous operation when SYNC = 0 (bit 7 of US\_MR). In asynchronous mode, the USART detects the start of a received character by sampling the RXD signal until it detects a valid start bit. A low level (space) on RXD is interpreted as a valid start bit if it is detected for more than 7 cycles of the sampling clock, which is 16 times the baud rate. Hence, a space that is longer than 7/16 of the bit period is detected as a valid start bit. A space which is 7/16 of a bit period or shorter is ignored and the receiver continues to wait for a valid start bit.

When a valid start bit has been detected, the receiver samples the RXD at the theoretical midpoint of each bit. It is assumed that each bit lasts 16 cycles of the sampling clock (1-bit period) so the sampling point is eight cycles (0.5 bit period) after the start of the bit. The first sampling point is therefore 24 cycles (1.5 bit periods) after the falling edge of the start bit was detected. Each subsequent bit is sampled 16 cycles (1-bit period) after the previous one.

#### Figure 7. Asynchronous Mode: Start Bit Detection

#### Figure 8. Asynchronous Mode: Character Reception

Example: 8-bit, parity enabled 1 stop

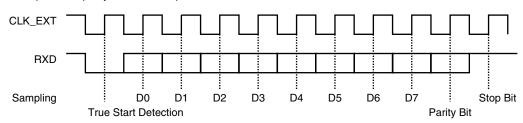

#### Synchronous Receiver

When configured for synchronous operation (SYNC = 1), the receiver samples the RXD signal on each rising edge of the Baud Rate Clock. If a low level is detected, it is considered as a start. Data bits, parity bit and stop bit are sampled and the receiver waits for the next start bit. See the example in Figure 9.

Figure 9. Synchronous Mode: Character Reception

Example: 8-bit, parity enabled 1 stop

**Receiver Ready** When a complete character is received, it is transferred to the US\_RHR and the RXRDY status bit in US\_CSR is set. If US\_RHR has not been read since the last transfer, the OVRE status bit in US\_CSR is set.

**Parity Error** Each time a character is received, the receiver calculates the parity of the received data bits, in accordance with the field PAR in US\_MR. It then compares the result with the received parity bit. If different, the parity error bit PARE in US\_CSR is set.

Framing Error If a character is received with a stop bit at low level and with at least one data bit at high level, a framing error is generated. This sets FRAME in US\_CSR.

**Time-out** This function allows an idle condition on the RXD line to be detected. The maximum delay for which the USART should wait for a new character to arrive while the RXD line is inactive (high level) is programmed in US\_RTOR (Receiver Time-out). When this register is set to 0, no time-out is detected. Otherwise, the receiver waits for a first character and then initializes a counter, which is decremented at each bit period and reloaded at each byte reception. When the counter reaches 0, the TIMEOUT bit in US\_CSR is set. The user can restart the wait for a first character with the STTTO (Start Time-out) bit in US\_CR.

Calculation of time-out duration:

Duration = US\_RTOR Value × 4 × Bit Period

**Generating CLK\_TXD** In synchronous mode, CLK\_TXD is the clock as defined in Figure 9. In asynchronous mode,

$CLK_TXD = 16 \times Baud Rate Clock$

as defined in Figure 7.

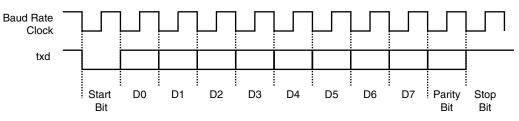

| Transmitter     | The transmitter has the same behavior in both synchronous and asynchronous operating modes. Start bit, data bits, parity bit and stop bits are serially shifted, lowest significant bit first, on the falling edge of the serial clock. See the example in Figure 10.                                                                                                                                    |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | The number of data bits is selected in the CHRL field in US_MR.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                 | The parity bit is set according to the PAR field in US_MR.                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|                 | The number of stop bits is selected in the NBSTOP field in US_MR.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                 | When a character is written to US_THR (Transmit Holding), it is transferred to the Shift Regis-<br>ter as soon as it is empty. When the transfer occurs, the TXRDY bit in US_CSR is set until a<br>new character is written to US_THR. If Transmit Shift Register and US_THR are both empty,<br>the TXEMPTY bit in US_CSR is set.                                                                        |  |  |  |  |

| Time-guard      | The time-guard function allows the transmitter to insert an idle state on the TXD line between two characters. The duration of the idle state is programmed in US_TTGR (Transmitter Time-guard). When this register is set to zero, no time-guard is generated. Otherwise, the transmitter holds a high level on TXD after each transmitted byte during the number of bit periods programmed in US_TTGR: |  |  |  |  |

|                 | Idle State Duration<br>between Two Characters = Time-guard × Bit<br>Value × Period                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Multi-drop Mode | When the field PAR in US_MR equals 11X (binary value), the USART is configured to run in multi-drop mode. In this case, the parity error bit PARE in US_CSR is set when data is detected with a parity bit set to identify an address byte. PARE is cleared with the Reset Status Bits command (RSTSTA) in US_CR. If the parity bit is detected low, identifying a data byte, PARE is not set.           |  |  |  |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

The transmitter sends an address byte (parity bit set) when a Send Address command (SENDA) is written to US\_CR. In this case, the next byte written to US\_THR will be transmitted as an address. After this, any byte transmitted will have the parity bit cleared.

Figure 10. Synchronous and Asynchronous Modes: Character Transmission

Example: 8-bit, parity enabled 1 stop

#### Break

A break condition is a low signal level that has a duration of at least one character (including start/stop bits and parity).

Transmit Break

The transmitter generates a break condition on the TXD line when STTBRK is set in US\_CR (Control Register). In this case, the character present in the Transmit Shift Register is completed before the line is held low.

To cancel a break condition on the TXD line, the STPBRK command in US\_CR must be set. The USART completes a minimum break duration of one character length. The TXD line then returns to high level (idle state) for at least 12 bit periods, or the value of the Time-guard register if it is greater than 12, to ensure that the end of break is correctly detected. Then the transmitter resumes normal operation.

The BREAK is managed like a character:

- The STTBRK and the STPBRK commands are performed only if the transmitter is ready (bit TXRDY = 1 in US\_CSR).

- The STTBRK command blocks the transmitter holding register (bit TXRDY is cleared in US\_CSR) until the break has started.

- A break is started when the Shift Register is empty (any previous character is fully transmitted). US\_CSR.TXEMPTY is cleared. The break blocks the transmitter shift register until it is completed (high level for at least 12 bit periods after the STPBRK command is requested).

In order to avoid unpredictable states:

- STTBRK and STPBRK commands must not be requested at the same time.

- Once an STTBRK command is requested, further STTBRK commands are ignored until the BREAK is ended (high level for at least 12 bit periods).

- All STPBRK commands requested without a previous STTBRK command are ignored.

- A byte written into the Transmit Holding Register while a break is pending but not started (bit TXRDY = 0 in US\_CSR) is ignored.

- It is *not permitted* to write new data in the Transmit Holding Register while a break is in progress (STPBRK has not been requested), even though TXRDY = 1 in US\_CSR.

- A new STTBRK command *must not* be issued until an existing break has ended (TXEMPTY=1 in US\_CSR).

The standard break transmission sequence is:

- 1. Wait for the transmitter ready. (US\_CSR.TXRDY = 1)

- 2. Send the STTBRK command. (Write 0x0200 to US\_CR)

- Wait for the transmitter ready. (bit TXRDY = 1 in US\_CSR)

- 4. Send the STPBRK command. (Write 0x0400 to US\_CR)

The next byte can then be sent:

- Wait for the transmitter ready. (bit TXRDY = 1 in US\_CSR)

- Send the next byte. (Write byte to US\_THR)

Each of these steps can be scheduled by using the interrupt if the bit TXRDY in US\_IMR is set. For character transmission, the USART channel must be enabled before sending a break.

| Receive Break                 | The receiver detects a break condition when all data, parity and stop bits are low. When the low stop bit is detected, the receiver asserts the RXBRK bit in US_CSR. An end of receive break is detected by a high level for at least 2/16 of a bit period in asynchronous operating mode or at least one sample in synchronous operating mode. RXBRK is also asserted when an end-of-break is detected.                                                        |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Both the beginning and the end of a break can be detected by interrupt if the bit US_IMR.RXBRK is set.                                                                                                                                                                                                                                                                                                                                                          |

| Peripheral Data<br>Controller | Each USART channel is closely connected to a corresponding Peripheral Data Controller channel. One is dedicated to the receiver. The other is dedicated to the transmitter.                                                                                                                                                                                                                                                                                     |

| Channels (PDC)                | The PDC channel is programmed using US_TPR (Transmit Pointer) and US_TCR (Transmit Counter) for the transmitter and US_RPR (Receive Pointer) and US_RCR (Receive Counter) for the receiver. The status of the PDC is given in US_CSR by the ENDTX bit for the transmitter and by the ENDRX bit for the receiver.                                                                                                                                                |

|                               | The pointer registers (US_TPR and US_RPR) are used to store the address of the transmit or receive buffers. The counter registers (US_TCR and US_RCR) are used to store the size of these buffers.                                                                                                                                                                                                                                                              |

|                               | The receiver data transfer is triggered by the RXRDY bit and the transmitter data transfer is triggered by TXRDY. When a transfer is performed, the counter is decremented and the pointer is incremented. When the counter reaches 0, the status bit is set (ENDRX for the receiver, ENDTX for the transmitter in US_CSR) and can be programmed to generate an interrupt. While the counter is at zero, the status bit is asserted and transfers are disabled. |

| Interrupt<br>Generation       | Each status bit in US_CSR has a corresponding bit in US_IER (Interrupt Enable) and US_IDR (Interrupt Disable), which controls the generation of interrupts by asserting the USART interrupt line connected to the Advanced Interrupt Controller. US_IMR (Interrupt Mask Register) indicates the status of the corresponding bits.<br>When a bit is set in US_CSR and the same bit is set in US_IMR, the interrupt line is asserted.                             |

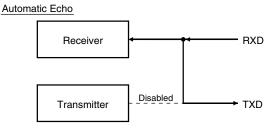

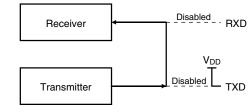

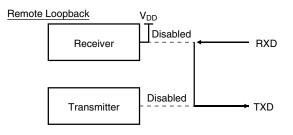

### Channel Test Configurations

The USART can be programmed to operate in three different test modes, using the field CHMODE in US\_MR.

Automatic echo mode allows bit-by-bit retransmission. When a bit is received on the RXD line, it is sent to the TXD line. Programming the transmitter has no effect.

Local loopback mode allows the transmitted characters to be received. TXD and RXD pins are not used and the output of the transmitter is internally connected to the input of the receiver. The RXD pin level has no effect and the TXD pin is held high, as in idle state.

Remote loopback mode directly connects the RXD pin to the TXD pin. The Transmitter and the Receiver are disabled and have no effect. This mode allows bit-by-bit retransmission.

Figure 11. Channel Modes

#### Local Loopback

### **USART User Interface**

#### Table 2. USART Memory Map

| Offset | Register                        | Name    | Access     | Reset State |

|--------|---------------------------------|---------|------------|-------------|

| 0x0000 | Control Register                | US_CR   | Write-only | _           |

| 0x0004 | Mode Register                   | US_MR   | Read/Write | _           |

| 0x0008 | Interrupt Enable Register       | US_IER  | Write-only | _           |

| 0x000C | Interrupt Disable Register      | US_IDR  | Write-only | _           |

| 0x0010 | Interrupt Mask Register         | US_IMR  | Read-only  | 0           |

| 0x0014 | Channel Status Register         | US_CSR  | Read-only  | 0x18        |

| 0x0018 | Receiver Holding Register       | US_RHR  | Read-only  | 0           |

| 0x001C | Transmitter Holding Register    | US_THR  | Write-only | _           |

| 0x0020 | Baud Rate Generator Register    | US_BRGR | Read/Write | 0           |

| 0x0024 | Receiver Time-out Register      | US_RTOR | Read/Write | 0           |

| 0x0028 | Transmitter Time-guard Register | US_TTGR | Read/Write | 0           |

| 0x002C | Reserved                        | _       | _          | _           |

| 0x0030 | Reserved for PDC connection     | _       | _          | _           |

| 0x0034 | Reserved for PDC connection     | _       | _          | _           |

| 0x0038 | Reserved for PDC connection     | -       | _          | _           |

| 0x003C | Reserved for PDC connection     | -       | _          | _           |

Notes: 1. The address takes into account the 2 LSBs [1:0], but the macrocell does not take these bits into account (left unconnected). Therefore loading 0x0001, 0x0002 or 0x0003 or P\_A[13:0] addresses the Control Register. 2. In the following register description, all undefined bits ("–") read "0".

3. If the user selects an address that is not defined in the above table, the value of P\_D\_OUT[31:0] is 0x00000000.

### **USART Control Register**

| Name:<br>Access Type: | US_CR<br>: Write-only       |    |       |       |        |        |        |

|-----------------------|-----------------------------|----|-------|-------|--------|--------|--------|

| 31                    | 30                          | 29 | 28    | 27    | 26     | 25     | 24     |

| _                     | _                           | _  | _     | _     | _      | _      | -      |

| 23                    | 22                          | 21 | 20    | 19    | 18     | 17     | 16     |

| _                     | _                           | _  | _     | _     | _      | _      | -      |

| 15                    | 14                          | 13 | 12    | 11    | 10     | 9      | 8      |

| -                     | _                           | -  | SENDA | STTTO | STPBRK | STTBRK | RSTSTA |

| 7                     | 6                           | 5  | 4     | 3     | 2      | 1      | 0      |

| TXDIS                 | TXDIS TXEN RXDIS RXEN RSTTX |    | RSTTX | RSTRX | _      | _      |        |

#### • RSTRX: Reset Receiver

- 0 = No effect.

- 1 = The receiver logic is reset, disabling the receive function (RXDIS is set internally).

#### • RSTTX: Reset Transmitter

- 0 = No effect.

- 1 = The transmitter logic is reset, disabling the transmit function (TXDIS and STPBRK are set internally).

#### • RXEN: Receiver Enable

- 0 = No effect.

- 1 = The receiver is enabled if RXDIS is 0.

#### • RXDIS: Receiver Disable

- 0 = No effect.

- 1 = The receiver is disabled.

- TXEN: Transmitter Enable

- 0 = No effect.

- 1 = The transmitter is enabled if TXDIS is 0.

#### • TXDIS: Transmitter Disable

- 0 = No effect.

- 1 = The transmitter is disabled.

- RSTSTA: Reset Status Bits

- 0 = No effect.

- 1 = Resets the status bits PARE, FRAME, OVRE and RXBRK in the US\_CSR.

#### • STTBRK: Start Break

0 = No effect.

1 = If break is not being transmitted, start transmission of a break after the characters present in US\_THR and the Transmit Shift Register have been transmitted.

#### • STPBRK: Stop Break

0 = No effect.

1 = If a break is being transmitted, stop transmission of the break after a minimum of one character length and transmit a high level during 12 bit periods.

#### • STTTO: Start Time-out

0 = No effect.

1 = Start waiting for a character before clocking the time-out counter.

#### • SENDA: Send Address

0 = No effect.

1 = In Multi-drop Mode only, the next character written to the US\_THR is sent with the address bit set. USART Mode Register

#### **USART Mode Register**

| Name:        | US_MR      |  |  |

|--------------|------------|--|--|

| Access Type: | Read/Write |  |  |

| 31  | 30          | 29  | 28     | 27 | 26   | 25    | 24   |

|-----|-------------|-----|--------|----|------|-------|------|

| -   | -           | _   | FILTER | -  | —    | -     | -    |

| 23  | 22          | 21  | 20     | 19 | 18   | 17    | 16   |

| _   | _           | -   | —      | _  | CLKO | MODE9 | _    |

| 15  | 14          | 13  | 12     | 11 | 10   | 9     | 8    |

| CHM | 10DE        | NBS | STOP   |    | PAR  |       | SYNC |

| 7   | 6           | 5   | 4      | 3  | 2    | 1     | 0    |

| CH  | CHRL USCLKS |     | _      | _  | _    | _     |      |

#### • USCLKS: Clock Selection (Baud Rate Generator Input Clock)

| USC | LKS | Selected Clock   |

|-----|-----|------------------|

| 0   | 0   | clock            |

| 0   | 1   | fdiv1            |

| 1   | 0   | slow_clock (ARM) |

| 1   | 1   | External (SCK)   |

#### • CHRL: Character Length

Start, stop and parity bits are added to the character length.

| CH | IRL | Character Length |

|----|-----|------------------|

| 0  | 0   | 5 bits           |

| 0  | 1   | 6 bits           |

| 1  | 0   | 7 bits           |

| 1  | 1   | 8 bits           |

#### • SYNC: Synchronous Mode Select

0 = USART operates in Asynchronous Mode.

1 = USART operates in Synchronous Mode.

#### • PAR: Parity Type

|   | PAR |   | Parity Type                |

|---|-----|---|----------------------------|

| 0 | 0   | 0 | Even parity                |

| 0 | 0   | 1 | Odd parity                 |

| 0 | 1   | 0 | Parity forced to 0 (Space) |

| 0 | 1   | 1 | Parity forced to 1 (Mark)  |

| 1 | 0   | х | No parity                  |

| 1 | 1   | х | Multi-drop mode            |

#### • NBSTOP: Number of Stop Bits

The interpretation of the number of stop bits depends on SYNC.

| NBSTOP |   | Asynchronous (SYNC = 0) | Synchronous (SYNC = 1) |

|--------|---|-------------------------|------------------------|

| 0      | 0 | 1 stop bit              | 1 stop bit             |

| 0      | 1 | 1.5 stop bits           | Reserved               |

| 1      | 0 | 2 stop bits             | 2 stop bits            |

| 1      | 1 | Reserved                | Reserved               |

Note: 1.5 or 2 stop bits are reserved for the TX function. The RX function uses only the 1 stop bit (there is no check on the 2 stop bit timeslot if NBSTOP = 10).

#### CHMODE: Channel Mode

| CHM | IODE | Mode Description                                                                   |  |  |  |  |  |

|-----|------|------------------------------------------------------------------------------------|--|--|--|--|--|

| 0   | 0    | Normal Mode<br>The USART Channel operates as an RX/TX USART.                       |  |  |  |  |  |

| 0   | 1    | Automatic Echo<br>Receiver Data Input is connected to the TXD pin.                 |  |  |  |  |  |

| 1   | 0    | Local Loopback<br>Transmitter Output Signal is connected to Receiver Input Signal. |  |  |  |  |  |

| 1   | 1    | Remote Loopback<br>RXD pin is internally connected to TXD pin.                     |  |  |  |  |  |

#### • MODE9: 9-bit Character Length

- 0 = CHRL defines character length.

- 1 = 9-bit character length.

MODE9 has priority on character length.

#### CKLO: Clock Output Select

- 0 = The USART does not drive the SCK pin.

- 1 = The USART drives the SCK pin if USCLKS[1] is 0.

- FILTER: Receive Line Filter

- 0 = The USART does not filter receive line.

1 = The USART filters receive line using a three-sample filter (1/16 bit clock) (2 over 3 majority)

### **USART Interrupt Enable Register**

| Name:        | US_IER     |

|--------------|------------|

| Access Type: | Write-only |

| 31      | 30      | 29   | 28    | 27    | 26    | 25      | 24      |

|---------|---------|------|-------|-------|-------|---------|---------|

| COMM_RX | COMM_TX | _    | _     | -     | _     | _       | -       |

| 23      | 22      | 21   | 20    | 19    | 18    | 17      | 16      |

| _       | _       | -    | _     | _     | _     | _       | _       |

| 15      | 14      | 13   | 12    | 11    | 10    | 9       | 8       |

| -       | -       | -    | _     | -     | -     | TXEMPTY | TIMEOUT |

| 7       | 6       | 5    | 4     | 3     | 2     | 1       | 0       |

| PARE    | FRAME   | OVRE | ENDTX | ENDRX | RXBRK | TXRDY   | RXRDY   |

#### • RXRDY: Enable RXRDY Interrupt

0 = No effect.

1 = Enables RXRDY Interrupt.

#### • TXRDY: Enable TXRDY Interrupt

0 = No effect.

1 = Enables TXRDY Interrupt.

#### • RXBRK: Enable Receiver Break Interrupt

- 0 = No effect.

- 1 = Enables Receiver Break Interrupt.

#### • ENDRX: Enable End of Receive Transfer Interrupt

- 0 = No effect.

- 1 = Enables End of Receive Transfer Interrupt.

#### • ENDTX: Enable End of Transmit Interrupt

- 0 = No effect.

- 1 = Enables End of Transmit Interrupt.

#### • OVRE: Enable Overrun Error Interrupt

- 0 = No effect.

- 1 = Enables Overrun Error Interrupt.

- FRAME: Enable Framing Error Interrupt

- 0 = No effect.

- 1 = Enables Framing Error Interrupt.

**USART**

#### • PARE: Enable Parity Error Interrupt

0 = No effect.

- 1 = Enables Parity Error Interrupt.

- TIMEOUT: Enable Time-out Interrupt

- 0 = No effect.

- 1 = Enables Reception Time-out Interrupt.

- TXEMPTY: Enable TXEMPTY Interrupt

- 0 = No effect.

- 1 = Enables TXEMPTY Interrupt.

- COMM\_TX: Enable COMM\_TX (from ARM) Interrupt

- 0 = No effect.

- 1 = Enables COMM\_TX interrupt.

- COMM\_RX: Enable COMM\_RX (from ARM) Interrupt

0 = No effect.

1 = Enables COMM\_RX interrupt.

### **USART Interrupt Disable Register**

| Name:        | US_IDR     |

|--------------|------------|

| Access Type: | Write-only |

| 31      | 30      | 29   | 28    | 27    | 26    | 25      | 24      |

|---------|---------|------|-------|-------|-------|---------|---------|

| COMM_RX | COMM_TX | -    | -     | —     | _     | -       | -       |

| 23      | 22      | 21   | 20    | 19    | 18    | 17      | 16      |

| _       | -       | -    | _     | _     | -     | -       | -       |

| 15      | 14      | 13   | 12    | 11    | 10    | 9       | 8       |

| _       | -       | Ι    | -     | —     | Ι     | TXEMPTY | TIMEOUT |

| 7       | 6       | 5    | 4     | 3     | 2     | 1       | 0       |

| PARE    | FRAME   | OVRE | ENDTX | ENDRX | RXBRK | TXRDY   | RXRDY   |

#### • RXRDY: Disable RXRDY Interrupt

0 = No effect.

1 = Disables RXRDY Interrupt.

#### • TXRDY: Disable TXRDY Interrupt

0 = No effect.

1 = Disables TXRDY Interrupt.

#### • RXBRK: Disable Receiver Break Interrupt

- 0 = No effect.

- 1 = Disables Receiver Break Interrupt.

#### • ENDRX: Disable End of Receive Transfer Interrupt

- 0 = No effect.

- 1 = Disables End of Receive Transfer Interrupt.

#### • ENDTX: Disable End of Transmit Interrupt

#### 0 = No effect.

1 = Disables End of Transmit Interrupt.

#### • OVRE: Disable Overrun Error Interrupt

0 = No effect.

- 1 = Disables Overrun Error Interrupt.

- FRAME: Disable Framing Error Interrupt

- 0 = No effect.

- 1 = Disables Framing Error Interrupt.

#### • PARE: Disable Parity Error Interrupt

0 = No effect.

- 1 = Disables Parity Error Interrupt.

- TIMEOUT: Disable Time-out Interrupt

- 0 = No effect.

- 1 = Disables Receiver Time-out Interrupt.

- TXEMPTY: Disable TXEMPTY Interrupt

- 0 = No effect.

- 1 = Disables TXEMPTY Interrupt.

- COMM\_TX: Disable COMM\_TX (from ARM) Interrupt

- 0 = No effect.

- 1 = Disables COMM\_TX interrupt.

- COMM\_RX: Disable COMM\_RX (from ARM) Interrupt

0 = No effect.

1 = Disables COMM\_RX interrupt.

### **USART Interrupt Mask Register**

| Name:        | US_IMR    |

|--------------|-----------|

| Access Type: | Read-only |

| 31      | 30      | 29   | 28    | 27    | 26    | 25      | 24      |

|---------|---------|------|-------|-------|-------|---------|---------|

| COMM_RX | COMM_TX | _    | _     | _     | _     | _       | _       |

| 23      | 22      | 21   | 20    | 19    | 18    | 17      | 16      |

| _       | _       | _    | _     | _     | _     | _       | _       |

| 15      | 14      | 13   | 12    | 11    | 10    | 9       | 8       |

| _       | —       | _    | -     | -     | -     | TXEMPTY | TIMEOUT |

| 7       | 6       | 5    | 4     | 3     | 2     | 1       | 0       |

| PARE    | FRAME   | OVRE | ENDTX | ENDRX | RXBRK | TXRDY   | RXRDY   |

#### • RXRDY: Mask RXRDY Interrupt

- 0 = RXRDY Interrupt is disabled.

- 1 = RXRDY Interrupt is enabled.

#### • TXRDY: Mask TXRDY Interrupt

- 0 = TXRDY Interrupt is disabled.

- 1 = TXRDY Interrupt is enabled.

#### • RXBRK: Mask Receiver Break Interrupt

- 0 = Receiver Break Interrupt is disabled.

- 1 = Receiver Break Interrupt is enabled.

#### • ENDRX: Mask End of Receive Transfer Interrupt

- 0 = End of Receive Transfer Interrupt is disabled.

- 1 = End of Receive Transfer Interrupt is enabled.

#### • ENDTX: Mask End of Transmit Interrupt

- 0 = End of Transmit Interrupt is disabled.

- 1 = End of Transmit Interrupt is enabled.

#### • OVRE: Mask Overrun Error Interrupt

- 0 = Overrun Error Interrupt is disabled.

- 1 = Overrun Error Interrupt is enabled.

#### • FRAME: Mask Framing Error Interrupt

- 0 = Framing Error Interrupt is disabled.

- 1 = Framing Error Interrupt is enabled.

**USART**

#### • PARE: Mask Parity Error Interrupt

- 0 = Parity Error Interrupt is disabled.

- 1 = Parity Error Interrupt is enabled.

- TIMEOUT: Mask Time-out Interrupt

- 0 = Receive Time-out Interrupt is disabled.

- 1 = Receive Time-out Interrupt is enabled.

#### • TXEMPTY: Mask TXEMPTY Interrupt

- 0 = TXEMPTY Interrupt is disabled.

- 1 = TXEMPTY Interrupt is enabled.

- COMM\_TX: Mask COMM\_TX (from ARM) Interrupt

- 0 = COMM\_TX interrupt is disabled.

- 1 = COMM\_TX interrupt is enabled.

#### • COMM\_RX: Mask COMM\_RX (from ARM) Interrupt

- 0 = COMM\_RX interrupt is disabled.

- 1 = COMM\_RX interrupt is enabled.

### **USART Channel Status Register**

| Name:        | US_CSR    |

|--------------|-----------|

| Access Type: | Read-only |

| 31      | 30      | 29   | 28    | 27    | 26    | 25      | 24      |

|---------|---------|------|-------|-------|-------|---------|---------|

| COMM_RX | COMM_TX | -    | -     | -     | —     | -       | -       |

| 23      | 22      | 21   | 20    | 19    | 18    | 17      | 16      |

| _       | -       | -    | -     | -     | —     | -       | _       |

| 15      | 14      | 13   | 12    | 11    | 10    | 9       | 8       |

| _       | -       | Ι    | -     | -     | _     | TXEMPTY | TIMEOUT |

| 7       | 6       | 5    | 4     | 3     | 2     | 1       | 0       |

| PARE    | FRAME   | OVRE | ENDTX | ENDRX | RXBRK | TXRDY   | RXRDY   |

#### • RXRDY: Receiver Ready

0 = No complete character has been received since the last read of the US\_RHR or the receiver is disabled. If characters were being received when the receiver was disabled, RXRDY changes to 1 when the receiver is enabled.

1 = At least one complete character has been received and the US\_RHR has not yet been read.

#### • TXRDY: Transmitter Ready

0 = A character is in the US\_THR waiting to be transferred to the Transmit Shift Register, or an STTBRK command has been requested, or the transmitter is disabled. As soon as the transmitter is enabled, TXRDY becomes 1.

1 = There is no character in the US\_THR.

Equal to zero when the USART is disabled or at reset. The Transmitter Enable command (in US\_CR) sets this bit to one if the transmitter was previously disabled.

#### • RXBRK: Break Received/End of Break

0 = No Break Received or End of Break detected since the last Reset Status Bits command in the Control Register.

1 = Break Received or End of Break detected since the last Reset Status Bits command in the Control Register.

#### • ENDRX: End of Receiver Transfer

0 = The End of Transfer signal from the Peripheral Data Controller channel dedicated to the receiver is inactive.

1 = The End of Transfer signal from the Peripheral Data Controller channel dedicated to the receiver is active.

#### • ENDTX: End of Transmitter Transfer

0 = The End of Transfer signal from the Peripheral Data Controller channel dedicated to the transmitter is inactive.

1 = The End of Transfer signal from the Peripheral Data Controller channel dedicated to the transmitter is active.

#### • OVRE: Overrun Error

0 = No byte has been transferred from the Receive Shift Register to the US\_RHR when RxRDY was asserted since the last Reset Status Bits command.

1 = At least one byte has been transferred from the Receive Shift Register to the US\_RHR when RxRDY was asserted since the last Reset Status Bits command.

#### • FRAME: Framing Error

0 = No stop bit has been detected low since the last Reset Status Bits command.

1 = At least one stop bit has been detected low since the last Reset Status Bits command.

#### PARE: Parity Error

1 = At least one parity bit has been detected false (or a parity bit high in multi-drop mode) since the last Reset Status Bits command.

0 = No parity bit has been detected false (or a parity bit high in multi-drop mode) since last Reset Status Bits command.

#### • TIMEOUT: Receiver Time-out

0 = There has not been a time-out since the last Start Time-out command or the Time-out Register is 0.

1 = There has been a time-out since the last Start Time-out command.

#### • TXEMPTY: Transmitter Empty

0 = There are characters in either US\_THR or the Transmit Shift Register, or the transmitter is disabled.

1 = There are no characters in either US\_THR or the Transmit Shift Register. TXEMPTY is 1 after Parity, Stop Bit and Timeguard have been transmitted. TXEMPTY is 1 after stop bit has been sent, or after Time-guard has been sent if US\_TTGR is not 0.

Equal to zero when the USART is disabled or at reset. Transmitter Enable command (in US\_CR) sets this bit to one if the transmitter is disabled.

#### • COMM\_TX: (from ARM)

$0 = COMM_TX$  is at 0.

- 1 = COMM\_TX is at 1.

- COMM\_RX: (from ARM)

- $0 = COMM_RX$  is at 0.

- 1 = COMM\_RX is at 1.

#### **USART Receiver Holding Register** IIS BHB

Name

| Access Type: | Read-only |    |    |    |    |    |    |  |  |  |

|--------------|-----------|----|----|----|----|----|----|--|--|--|

| 31           | 30        | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

| _            | _         | _  | -  | -  | —  | -  | -  |  |  |  |

| 23           | 22        | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

| _            | _         | _  | _  | _  | _  | _  | -  |  |  |  |

| 15           | 14        | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

| _            | _         | _  | -  | _  | —  | _  | -  |  |  |  |

| 7            | 6         | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|              | RXCHR     |    |    |    |    |    |    |  |  |  |

#### • RXCHR: Received Character

Last character received if RXRDY is set. When number of data bits is less than 8 bits, the bits are right-aligned. All non-significant bits read zero.

### **USART Transmitter Holding Register**

| Name:<br>Access Type: | US_THR<br>Write-only |    |     |     |    |    |    |

|-----------------------|----------------------|----|-----|-----|----|----|----|

| 31                    | 30                   | 29 | 28  | 27  | 26 | 25 | 24 |

| _                     | _                    | _  | _   | _   | _  | _  | _  |

| 23                    | 22                   | 21 | 20  | 19  | 18 | 17 | 16 |

| _                     | -                    | -  | -   | -   | -  | -  | _  |

| 15                    | 14                   | 13 | 12  | 11  | 10 | 9  | 8  |

| _                     | -                    | -  | -   | -   | -  | -  | —  |

| 7                     | 6                    | 5  | 4   | 3   | 2  | 1  | 0  |

|                       |                      |    | ТХС | CHR |    |    |    |

#### • TXCHR: Character to be Transmitted

Next character to be transmitted after the current character if TXRDY is not set. When number of data bits is less than 8 bits, the bits are right-aligned.

### **USART Baud Rate Generator Register US\_BRGR**

| Access Type: | Read/Write |    |    |    |    |    |    |  |  |  |

|--------------|------------|----|----|----|----|----|----|--|--|--|

| 31           | 30         | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

| _            | -          | _  | _  | _  | _  | -  | _  |  |  |  |

| 23           | 22         | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

| _            | -          | -  | _  | _  | _  | -  | _  |  |  |  |

| 15           | 14         | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

|              | CD         |    |    |    |    |    |    |  |  |  |

| 7            | 6          | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|              | CD         |    |    |    |    |    |    |  |  |  |

#### • CD: Clock Divisor

Name:

This register has no effect if Synchronous Mode is selected with an external clock.

|                        | CD | Description                                                                                                      |  |  |  |  |

|------------------------|----|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0 Disables Clock       |    |                                                                                                                  |  |  |  |  |

| 1 Clock Divisor Bypass |    |                                                                                                                  |  |  |  |  |

| 2 to 65535             |    | Baud Rate (Asynchronous Mode) = Selected Clock / (16 x CD)<br>Baud Rate (Synchronous Mode) = Selected Clock / CD |  |  |  |  |

Notes: 1. In Synchronous Mode, when either external clock (clk\_ext or fdiv1) is selected, the value programmed must be even to ensure a 50:50 mark:space ratio.

In Synchronous Mode, when the internal clock (clock) is selected, the CD can be even and the duty clock is 50:50.

2. Clock divisor bypass (CD = 1) must not be used when the internal clock (clock) is selected (USCLKS = 0).

### **USART Receiver Time-out Register**

| Name:        | US_RTOR    |  |  |  |

|--------------|------------|--|--|--|

| Access Type: | Read/Write |  |  |  |

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

| _  | -  | _  | -  | _  | -  | -  | _  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| —  | —  | -  | -  | —  | -  | Ι  | _  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| —  | -  | -  | -  | -  | _  | -  | _  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | ТО |    |    |    |    |    |    |

#### • TO: Time-out Value

When a value is written to this register, a Start Time-out command is automatically performed.

Time-out duration = TO x 4 x Bit Period

| то      | Description                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Disables the RX Time-out function.                                                                                                                         |

| 1 - 255 | The Time-out counter is loaded with TO when the Start Time-out command is given or when each new data character is received (after reception has started). |

### **USART Transmitter Time-guard Register**

| Name:        | US_TTGR    |  |  |  |

|--------------|------------|--|--|--|

| Access Type: | Read/Write |  |  |  |

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|----|----|----|----|----|----|----|----|

| -  | -  | -  | -  | -  | _  | _  | -  |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| _  | -  | -  | Ι  | -  | _  |    | _  |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

| _  | -  | Ι  | Ι  | -  | _  | Ι  | —  |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|    | TG |    |    |    |    |    |    |

#### • TG: Time-guard Value

Time-guard duration = TG x Bit Period

| TG      |                                                                                                  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------|--|--|--|

| 0       | Disables the TX Time-guard function.                                                             |  |  |  |

| 1 - 255 | - 255 TXD is inactive high after the transmission of each character for the time-guard duration. |  |  |  |

#### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel SarL Route des Arsenaux 41 Casa Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Atmel Asia, Ltd. Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

Atmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

#### **Atmel Product Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

#### Atmel Grenoble

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-7658-3000 FAX (33) 4-7658-3480

#### Atmel Heilbronn

Theresienstrasse 2 POB 3535 D-74025 Heilbronn, Germany TEL (49) 71 31 67 25 94 FAX (49) 71 31 67 24 23

#### Atmel Nantes

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 0 2 40 18 18 18 FAX (33) 0 2 40 18 19 60

#### Atmel Rousset

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-4253-6000 FAX (33) 4-4253-6001

#### Atmel Smart Card ICs

Scottish Enterprise Technology Park East Kilbride, Scotland G75 0QR TEL (44) 1355-357-000 FAX (44) 1355-242-743

> *e-mail* literature@atmel.com

> Web Site http://www.atmel.com

© Atmel Corporation 2001.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel® is the registered trademark of Atmel.

ARM<sup>®</sup>, Thumb<sup>®</sup> and ARM Powered<sup>®</sup> are the registered trademarks of ARM Ltd.; ARM7TDMI<sup>™</sup> and AMBA<sup>™</sup> are trademarks of ARM Ltd. Other terms and product names in this document may be trademarks of others.