STEL-2060C/CR Data Sheet

# STEL-2060C/CR

## 45 Mbps Viterbi Decoder

www.DataSheet4U.cor

www.DataSheet4U.com

## **FEATURES**

- **45 Mbps Operating Rate**

- Constraint Length K = 7 G<sub>1</sub> = 171<sub>8</sub> G<sub>2</sub> = 133<sub>8</sub>

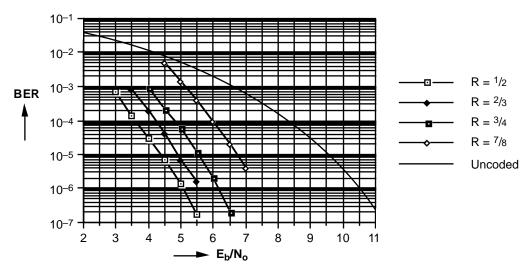

- Multiple Rates: Rate <sup>1</sup>/<sub>2</sub> as well as Punctured codes at Rates <sup>2</sup>/<sub>3</sub> through <sup>7</sup>/<sub>8</sub>

- Internal Depuncturing Capability at Rates <sup>2</sup>/<sub>3</sub>, <sup>3</sup>/<sub>4</sub> and <sup>7</sup>/<sub>8</sub>

- Multiple Devices can be Multiplexed to Give Higher Data Rates

- Optimized Interface to Operate with BPSK and QPSK Demodulators

- Auto Node Sync Capability

- Differential Decoder

- "Invert G2" Descrambler

- Internal BER Monitor and BER Measurement Circuit

- **5.2 dB Coding Gain** @10<sup>-5</sup> BER (R = <sup>1</sup>/<sub>2</sub>)

- 100-pin PQFP Package

- 0.5 Micron CMOS Technology

## FUNCTIONAL DESCRIPTION

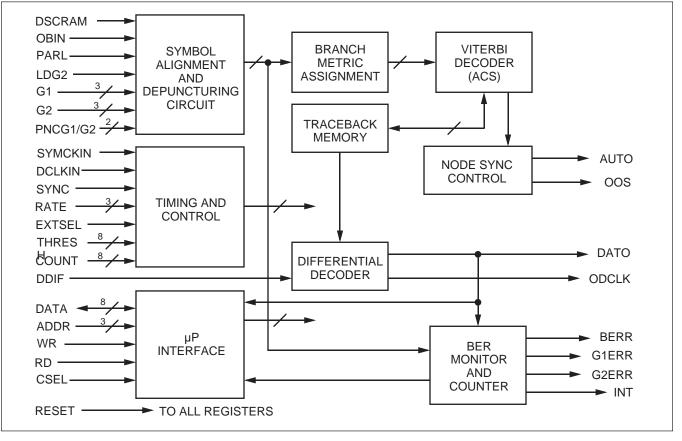

Convolutional encoding and Viterbi decoding are used to provide forward error correction (FEC) which improves digital communication performance over a noisy link. The STEL-2060C is a specialized product designed to perform this specific communications related function. At the encoder a stream of symbols is created which introduces a high degree of redundancy. This enables accurate decoding of the information despite a high symbol error rate resulting from an impaired communications link.

The STEL-2060C contains a K = 7 Viterbi Decoder. The data inputs can be in offset binary or offset signed-magnitude formats, with 3-bit soft decision. Auto node sync is provided for applications where symbol uncertainty can occur. Rate  $\frac{2}{3}, \frac{3}{4}, \frac{4}{5}, \frac{5}{6}, \frac{6}{7}$  and  $\frac{7}{8}$  punctured signals can be decoded, as well as non-punctured, Rate 1/2, signals. The polynomials and puncturing patterns used are industry standards. Depuncturing logic is incorporated into the decoder to provide automatic depuncturing of received data at rates 2/3, 3/4 and 7/8 when the puncturing patterns supported by the device are used. A BER monitor is also provided in the device, along with a circuit for computing the mean value of the BER over an extended period. These circuits operate with punctured codes as well as unpunctured. The STEL-2060C incorporates a descrambler for signals scrambled with the "Invert G2" algorithm. (With this method the G2 symbols are logically inverted at the encoder. This provides a very effective level of scrambling for the purpose of avoiding long strings of ones or zeroes in the transmitted signal using BPSK modulation.)

## **BLOCK DIAGRAM**

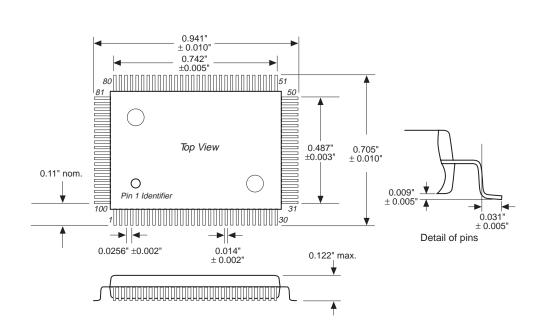

## PIN CONFIGURATION

Package: 100-pin HQFP Thermal coefficient,  $\theta_{ja} = 30^{\circ} \text{ C/W}$

Notes: (1) Tolerances on pin spacing are not cumulative

- (2) Dimensions shown are at seating plane

- (3) I.C. denotes Internal Connection. This pin *must* be left unconnected. Do not use for vias.

- (4) N.C. denotes No Connection. These pins can be used for vias.

#### **PIN CONNECTIONS**

| 3 N.C. 23 PNCG1                          |                      | 63 INT             | $83 \text{ THR}_2$   |

|------------------------------------------|----------------------|--------------------|----------------------|

| 4 $G1_0$ 24 PNCG2                        | 44 READ              | 64 N.C.            | 84 THR <sub>3</sub>  |

| 5 $G1_1$ 25 DSCRAM                       | 45 V <sub>SS</sub>   | 65 V <sub>SS</sub> | 85 THR <sub>4</sub>  |

| 6 G1 <sub>2</sub> 26 SYNC                | 46 ADDR <sub>2</sub> | 66 ODCLK           | 86 THR <sub>5</sub>  |

| 7 G2 <sub>0</sub> 27 LDG2                | 47 $ADDR_1$          | 67 N.C.            | 87 THR <sub>6</sub>  |

| 8 G2 <sub>1</sub> 28 N.C.                | 48 $ADDR_0$          | 68 V <sub>SS</sub> | 88 THR <sub>7</sub>  |

| 9 G2 <sub>2</sub> 29 N.C.                | 49 WRITE             | 69 DATO            | 89 EXTSEL            |

| 10 N.C. 30 V <sub>DD</sub>               | 50 CSEL              | 70 N.C.            | 90 V <sub>SS</sub>   |

| 11 OBIN 31 V <sub>DD</sub>               | 51 V <sub>DD</sub>   | 71 OOS             | 91 V <sub>SS</sub>   |

| 12 N.C. 32 COUNT <sub>0</sub>            | 52 V <sub>DD</sub>   | 72 AUTO            | 92 V <sub>SS</sub>   |

| 13 $V_{SS}$ 33 COUNT <sub>1</sub>        | 53 N.C.              | 73 N.C.            | 93 V <sub>DD</sub>   |

| 14 SYMCKIN 34 COUNT <sub>2</sub>         | 54 DATA <sub>7</sub> | 74 I.C.            | 94 V <sub>SS</sub>   |

| 15 N.C. 35 COUNT <sub>3</sub>            | 55 DATA <sub>6</sub> | 75 N.C.            | 95 DDIF              |

| 16 V <sub>SS</sub> 36 COUNT <sub>4</sub> | 56 DATA <sub>5</sub> | 76 BERR            | 96 V <sub>SS</sub>   |

| 17 DCLKIN 37 COUNT <sub>5</sub>          | 57 DATA <sub>4</sub> | 77 G1ERR           | 97 RATE <sub>2</sub> |

| 18 N.C. 38 COUNT <sub>6</sub>            | 58 DATA <sub>3</sub> | 78 G2ERR           | 98 $RATE_1$          |

| 19 V <sub>SS</sub> 39 COUNT <sub>7</sub> | 59 DATA <sub>2</sub> | 79 V <sub>DD</sub> | 99 $RATE_0$          |

| 20 RESET 40 V <sub>DD</sub>              | $60 \text{ DATA}_1$  | 80 V <sub>DD</sub> | 100 V <sub>DD</sub>  |

### **INPUT SIGNALS**

#### RESET

**Reset**. A logic low on this asynchronous input will completely reset all registers in the decoder to an initial condition within 20 nsec. Normal operation will commence after **RESET** goes high. This will not affect the values stored in the decision path memory but will reset the node sync state to the initial condition.

#### DCLKIN

Decoder **clock in**put. It is the reference clock for all internal synchronous functions in the decoder when operating in the Internal Puncturing mode. It should nominally be a square wave with a maximum frequency of 45 MHz, corresponding to a decoded data rate of 45 Mbps. When operating at Rate <sup>1</sup>/2 and in the External Puncturing mode this clock will be generated internally from **SYMCKIN**, and **DCLKIN** should be connected to ground.

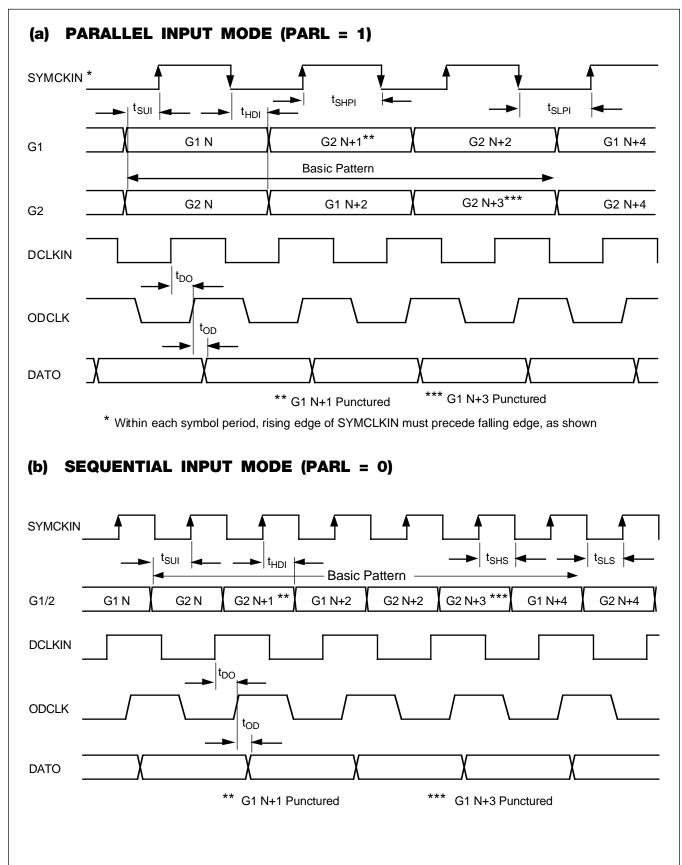

#### SYMCKIN

**Sym**bol **c**lock **in**put. This is the reference clock for all internal synchronous functions in the symbol alignment and depuncturing circuits. It should nominally be a square wave with a maximum frequency of 90 MHz. Its frequency should be equal to  $f_{DCLKIN}/2R$  in the parallel input mode (**PARL** = 1) and equal to  $f_{DCLKIN}/R$  in the sequential input mode (**PARL** = 0), where R is the decoding rate when using internal depuncturing. Please refer to the section on Punctured Mode Operation for more detailed information.

#### G1<sub>2-0</sub>, G2<sub>2-0</sub>

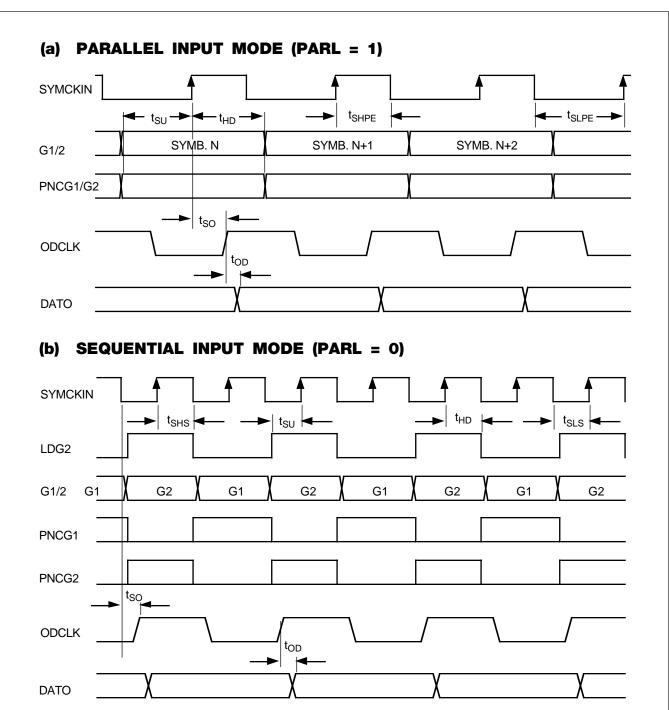

The G1<sub>2-0</sub> and G2<sub>2-0</sub> signals are the 3-bit soft decision input symbols to the decoder. They are presented to the decoder either sequentially or in parallel depending on the states of the PARL and RATE<sub>2-0</sub> inputs. In the parallel mode (PARL = 1) the symbols are clocked into the device on the rising edges of SYMCKIN when RATE<sub>2-0</sub> = 0 (Rate <sup>1</sup>/<sub>2</sub> and External Depuncturing) and on both edges of SYMCKIN when RATE<sub>2-0</sub>  $\neq 0$  (Internal Depuncturing). In the sequential mode (PARL = 0) in which th G2<sub>2-0</sub> inputs are not used, both the G1 and G2 symbols are loaded via the G1<sub>2-0</sub> pins. The G1 symbols are then latched in on the rising edges of SYMCKIN when LDG2 is low and the G2 symbols are latched in on the rising edges of SYMCKIN when LDG2 is high.

#### LDG2

When this signal is high during a rising edge of **SYMCKIN** the symbol loaded into the  $G1_{2-0}$  pins will be G2. This function is only active when **PARL** is set low (sequential input mode) and **RATE**<sub>2-0</sub> is set to 000 (Rate <sup>1</sup>/<sub>2</sub> operation or External Puncturing mode). If auto node sync is used, the **LDG2** signal can be derived by dividing the **SYMCKIN** signal by two. The auto node sync will then compensate for the phase ambiguity.

#### PARL

When this signal is high, the input symbols are accepted in **parallel** by the chip, using the  $G1_{2\cdot 0}$  pins for the G1 symbols and the  $G2_{2\cdot 0}$  pins for the G2 symbols. When it is set low, the

inputs are accepted sequentially, using the **G1**<sub>2-0</sub> pins for both symbols. The sequential input is most suited for BPSK data, and the parallel input is most suited for QPSK data. The auto node sync sequence will operate on the assumption that the signal is BPSK modulated when **PARL** is set low and QPSK modulated when it is set high. Setting **PARL** low adds two cycles of **ODCLK** to the pipeline delay.

#### OBIN

The STEL-2060CCC can accept the soft-decision input data in either offset binary or offset signed-magnitude formats. When the **OBIN** input is set high, the format expected will be offset binary; when it is set low it will be offset signedmagnitude. The meanings of the 3-bit values for these two codes is shown in the following table:

| <b>OBIN</b> = 1 | OBIN = 0 | Value             |

|-----------------|----------|-------------------|

| 111             | 111      | Most confident +  |

| 110             | 110      | (Data = 1)        |

| 101             | 101      |                   |

| 100             | 100      | Least confident + |

| 011             | 000      | Least confident – |

| 010             | 001      |                   |

| 001             | 010      | (Data = 0)        |

| 000             | 011      | Most confident –  |

|                 |          |                   |

When using the STEL-2060CCC with hard-decision data, the symbols should be loaded into the **G1**<sub>2</sub> and **G2**<sub>2</sub> pins. The other symbol inputs should be set to a logic high level and **OBIN** should be set low.

#### RATE<sub>2-0</sub>

These signals select the decoding rate for unpunctured operation (Rate  $^{1}/_{2}$ ) and internally supported depuncturing patterns (Rates  $^{2}/_{3}$ ,  $^{3}/_{4}$  and  $^{7}/_{8}$ ). These patterns are shown in the following table, where a 0 in the pattern indicates a punctured symbol:

| RATE <sub>2-0</sub> | Rate            | Pattern                    |

|---------------------|-----------------|----------------------------|

| 0 0 0               | $\frac{1}{2}$   | N.A.                       |

| 001                 | <sup>2</sup> /3 | G1: 10                     |

|                     |                 | G2: 11                     |

| 100                 | <sup>3</sup> /4 | G1: 101<br>G2: 110         |

| 010                 | 7/8             | G1: 1000101<br>G2: 1111010 |

Other puncturing patterns can be implemented externally using the **PNCG1** and **PNCG2** inputs.

#### DDIF

When this input is set high, it causes the data out of the Viterbi **d**ecoder to be **dif**ferentially decoded. This adds one cycle of **ODCLK** to the pipeline delay.

#### DSCRAM

When this input is set high, it causes the G2 symbols to be inverted before they enter the Viterbi decoder, thereby reversing the effect of the G2 inversion if an "Invert G2" scrambler is implemented at the encoder.

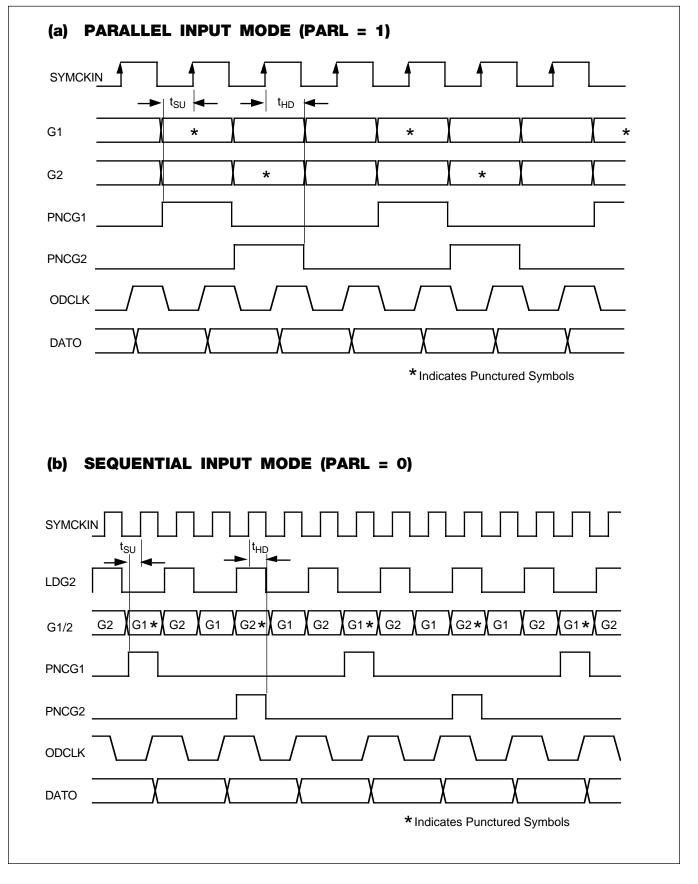

#### PNCG1, PNCG2

The PNCG1 and PNCG2 signals are used to control the STEL-2060CCC when operating in punctured modes not supported by the internal puncturing logic. In normal operation (Rate 1/2 and when using internal puncturing) these pins should be set low. In the external depuncturing mode, the PNCG1 signal must be set high to indicate that the G1 symbol is punctured and the PNCG2 signal must be set high to indicate that the G2 symbol is punctured. A symbol will be depunctured when the PNCG1 or PNCG2 signals are high during the rising edge of SYMCKIN which latches the corresponding symbol in to the decoder. **RATE**<sub>2-0</sub> should be set to 000 when operating in external depuncturing mode. Zero value metrics will be substituted internally for the actual metrics corresponding to the signals present on the G1<sub>2-0</sub> and G2<sub>2-0</sub> pins at that time. Internal depuncturing can be selected by the use of the **RATE** inputs.

#### SYNC

When the **SYNC** input is set high during the rising edge of **SYMCKIN** the internal symbol synchronization will be changed. When auto node sync is not desired this pin should be set low. It should be connected to the **AUTO** output to use the auto node sync capability of the STEL-2060CCC. The state of this circuit will always be set to normal after a reset.

#### COUNT<sub>7-0</sub>

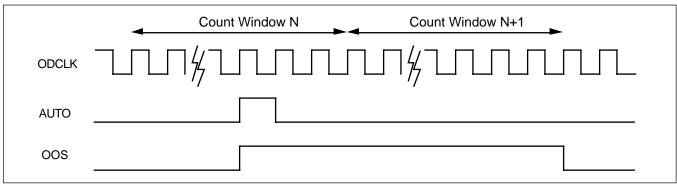

The 8-bit **COUNT**<sub>7-0</sub> input defines the period (number of bits) used in the node synchronization circuit when **EXTSEL** is set high. The 8-bit number N is used to set up a period of (256N + 256) bits internally, where N is the value of **COUNT**<sub>7-0</sub>. An out-of-sync condition is declared (i.e., the output pin **OOS** is set high and **AUTO** pulses high) if the renormalization count exceeds the threshold value during a period of this number of bits.

#### **THR**<sub>7-0</sub>

The 8-bit THR<sub>7-0</sub> input defines the threshold for node synchronization when EXTSEL is set high. The 8-bit number N is used to set up a threshold value of (8N + 6) internally, where N is the value of THR<sub>7-0</sub>. An out-of-sync condition is declared (i.e., the output pin OOS is set high and AUTO pulses high) if the renormalization count exceeds this threshold value.

#### EXTSEL

When the **EXTSEL** input is set high, the **COUNT**<sub>7-0</sub> and **THR**<sub>7-0</sub> information is derived from the **COUNT**<sub>7-0</sub> and **THR**<sub>7-0</sub> input pins. When it is set low, this information is derived from the data written into addresses 0 and 1.

## **OUTPUT SIGNALS**

#### ODCLK

Output data clock. All outputs change on the rising edge of this clock. The falling edge of **ODCLK** can be used as a strobe for **DATO** output, which is guaranteed to be valid on this edge.

#### DATO

Decoded data output. This is the output of the Viterbi decoder. This signal changes on the rising edges of ODCLK. In Rate  $^{1}/_{2}$  operation there will be a pipeline delay of 526 cycles of ODCLK from the G1<sub>2-0</sub>/G2<sub>2-0</sub> inputs to the DATO output when DDIF is set low and PARL is set high. Setting DDIF high adds one cycle to this value and setting PARL low adds two cycles.

#### **00**S

This output pin serves as a flag for the out-of-sync condition. When it goes high it signifies that the renormalization count in the internal node sync circuit has exceeded the threshold value set by the  $\rm THR_{7-0}$  signal, declaring an out-of-sync condition. It will remain high until this condition ceases to exist. i.e., until the next time the threshold is not exceeded during a complete count period.

#### AUTO

This is the feedback signal from the internal node sync correction circuit. It will pulse high for one cycle of **DCLKIN** each time the renormalization count in the internal node sync circuit has exceeded the threshold value set by the **THR**<sub>7-0</sub> signal and the out-of-sync condition is declared. It should be connected to the **SYNC** input when using the internal node sync facility.

#### BERR

The **B**it **Err**or output indicates that an error has been detected in either the G1 or G2 symbols corresponding to the current output bit.

#### G1ERR

The **G1 Err**or output indicates that an error has been detected in the G1 symbol corresponding to the current output bit.

#### **G2ERR**

The **G2 Err**or output indicates that an error has been detected in the G2 symbol corresponding to the current output bit. **Note:** The **BERR**, **G1ERR** and **G2ERR** signals are in NRZ format, i.e., the signals will not return to zero between two

consecutive errors. To generate pulsed outputs, the signals can be gated with the **ODCLK** signal.

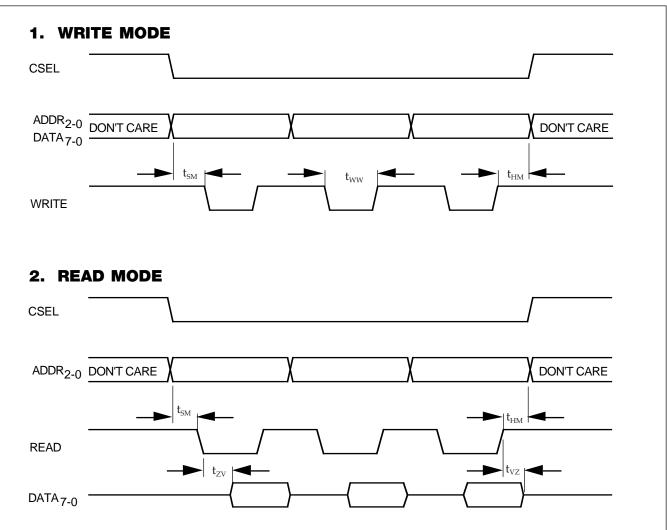

#### **MICROPROCESSOR INTERFACE**

#### DATA7-0

All I/O and control functions can be accessed via the  $DATA_{7-0}$  bus with the associated control signals. The STEL-2060CCC is used as a memory or I/O mapped peripheral to the host processor.

#### ADDR<sub>2-0</sub>

The 3-bit address bus is used to access the various I/O functions, as shown in the Memory Map table, below. Note that some addresses contain both Read and Write registers. These read and write mode registers are separate and contain different data.

#### WRITE

The **Write** input is used to write data to the microprocessor data bus. It is active low and is normally connected to the write line of the host processor.

#### READ

The **Read** input is used to read data from the microprocessor data bus. It is active low and is normally connected to the read line of the host processor.

#### CSEL

The **Chip Select** input can be used to selectively enable the microprocessor data bus. It is active low.

#### INT

The **Int**errupt output indicates when the Period Counter in the BER Monitor has completed a count period, and that a new value of **BERCT** is ready to be read from addresses  $0_H$  and  $1_{H'}$  when **INT** will go high for one symbol period.

## **INPUT (WRITE) FUNCTIONS**

#### COUNT<sub>7-0</sub>

The 8-bit **COUNT**<sub>7-0</sub> data defines the period (i.e., the number of bits) used in the node synchronization circuit. The 8-bit number N is used to set up a period of (256N + 256) internally, where N is the value of **COUNT**<sub>7-0</sub>. If the renormalization count exceeds the threshold value during a period of this number of bits then an out-of-sync condition is declared (i.e., the output pin **OOS** is set high and **AUTO** pulses high). Reset value  $00_{\rm H}$ .

#### **THR**<sub>7-0</sub>

The 8-bit  $\text{THR}_{7-0}$  data defines the threshold for node synchronization when **EXTSEL** is set low. The function is identical to that of the  $\text{THR}_{7-0}$  input signal. Reset value  $00_{\text{H}}$ .

#### BPER<sub>23-0</sub>

The 24-bit **B**ER **Per**iod data is used to set the period (number of data bits) over which the mean BER is measured by the BER Monitor. The period used is 1000 times the value of **BPER**<sub>23-0</sub>. Reset value FFFFFF<sub>H</sub>.

**Note:** The BER Count function incorporated in the STEL-2060CCC uses a counter to count the number of thousands of bits received. When the value of this counter is **equal** to the value written into  $\text{BPER}_{23-0}$  the number of errors counted is dumped into the  $\text{BERCT}_{15-0}$  output register and can be read from read addresses  $0-1_{\text{H}}$ . Simultaneously, both the error and bit counters are reset and the process is restarted, and an interrupt (INT) is generated to indicate that the new value is ready to be read.

Since the default (reset) value of the BPER<sub>23-0</sub> register is FF FF  $FF_H$  a potential problem occurs if the desired value is not written into this register before the value of the counter has already incremented past this value. If this is not done the equality will not be detected until after the counter overflows and increments to the desired value once again. Even at the maximum rate of 45 Mbps this will take over 6 minutes and, at a more modest data rate, such as 1 Mbps, it will take over  $4^{1}/2$  hours! In any case, the user can easily be misled into believing that the circuit is not operating correctly since the interrupts will not be generated as expected. It is therefore imperative that the BPER<sub>23-0</sub> value be written into the STEL-2060CCC as soon as possible after a reset to ensure that this condition does not take place. The maximum time allowable is just less than the desired interrupt period itself, since the counter begins counting right after the reset is released.

e.g., if the desired interrupt period is one second, the BPER<sub>23-0</sub> value must be written within one second of the reset. At a data rate of 1 Mbps the period would correspond to  $10^6$  bits and the correct BPER<sub>23-0</sub> value would be  $10^3$ , or 00 03 E8<sub>H</sub>.

If, for some reason, it is not possible to do this, a dummy value should first be written into the STEL-2060CCC. This should be large enough so that, at the time of writing, the bit counter will not have exceeded the dummy value. In this way the first interrupt will be generated within a reasonable period of time and the dummy value can then be overwritten with the desired value. Again, care must be taken to ensure that the BPER<sub>23-0</sub> value written is greater than the instantaneous counter value, otherwise the same problem will occur.

e.g., in the above example, if it is not possible to write the BPER<sub>23-0</sub> value until 5 seconds after the reset, then a dummy BPER<sub>23-0</sub> value corresponding to >5 seconds, e.g., 6 seconds, or 00 17 70<sub>H</sub> should first be written. The desired value of 00 03 E8<sub>H</sub> must then be written within one second of an interrupt generated by the STEL-2060CCC, thereby ensuring that the counter has not exceeded the new value at that time.

## **OUTPUT (READ) FUNCTIONS**

#### BERCT<sub>15-0</sub>

The 16-bit **B**it **E**rror **C**ount data represents the mean Bit Error Rate over the period determined by the BER Period data **BPER**<sub>23-0</sub>. The actual BER is given by:

$$BER = \frac{8 \times BERCT_{15-0}}{1000 \times BPER_{23-0}}$$

The value will be updated each time the period counter completes its count. Completion is indicated by the **INT** output going high for one clock cycle. If the accumulator overflows during a measurement period its output will be caused to saturate at a value of  $FFF_H$ .

## MICROPROCESSOR INTERFACE MEMORY MAP

#### WRITE MODE REGISTERS

| ADDR <sub>2-0</sub> | DATA <sub>7</sub>  | DATA <sub>6</sub>  | DATA <sub>5</sub>  | DATA <sub>4</sub>  | DATA <sub>3</sub>  | DATA <sub>2</sub>  | DATA <sub>1</sub>  | DATA <sub>0</sub>  |

|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| 0                   | COUNT <sub>7</sub> | COUNT <sub>6</sub> | COUNT <sub>5</sub> | COUNT <sub>4</sub> | COUNT <sub>3</sub> | COUNT <sub>2</sub> | COUNT <sub>1</sub> | COUNT <sub>0</sub> |

| 1                   | THR <sub>7</sub>   | THR <sub>6</sub>   | THR <sub>5</sub>   | THR <sub>4</sub>   | THR <sub>3</sub>   | THR <sub>2</sub>   | THR <sub>1</sub>   | THR <sub>0</sub>   |

| 2                   |                    |                    |                    |                    |                    |                    |                    |                    |

| 3                   | BPER <sub>7</sub>  | BPER <sub>6</sub>  | BPER <sub>5</sub>  | BPER <sub>4</sub>  | BPER <sub>3</sub>  | BPER <sub>2</sub>  | BPER <sub>1</sub>  | BPER <sub>0</sub>  |

| 4                   | BPER <sub>15</sub> | BPER <sub>14</sub> | BPER <sub>13</sub> | BPER <sub>12</sub> | BPER <sub>11</sub> | BPER <sub>10</sub> | BPER <sub>9</sub>  | BPER <sub>8</sub>  |

| 5                   | BPER <sub>23</sub> | BPER <sub>22</sub> | BPER <sub>21</sub> | BPER <sub>20</sub> | BPER <sub>19</sub> | BPER <sub>18</sub> | BPER <sub>17</sub> | BPER <sub>16</sub> |

#### **READ MODE REGISTERS**

| ADDR <sub>2-0</sub> | DATA <sub>7</sub>   | DATA <sub>6</sub>   | DATA <sub>5</sub>   | DATA <sub>4</sub>   | DATA <sub>3</sub>   | DATA <sub>2</sub>   | DATA <sub>1</sub>  | DATA <sub>0</sub>  |

|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--------------------|--------------------|

| 0                   | BERCT <sub>7</sub>  | BERCT <sub>6</sub>  | BERCT <sub>5</sub>  | BERCT <sub>4</sub>  | BERCT <sub>3</sub>  | BERCT <sub>2</sub>  | BERCT <sub>1</sub> | BERCT <sub>0</sub> |

| 1                   | BERCT <sub>15</sub> | BERCT <sub>14</sub> | BERCT <sub>13</sub> | BERCT <sub>12</sub> | BERCT <sub>11</sub> | BERCT <sub>10</sub> | BERCT <sub>9</sub> | BERCT <sub>8</sub> |

## PUNCTURED MODE OPERATION

#### **CONCEPT OF PUNCTURING**

In punctured codes some of the symbols generated by the convolutional encoder are deleted, or punctured, from the transmitted sequence. For example, in a rate 1/2(unpunctured) sequence, four symbols are transmitted for every two data bits. If one symbol out of every group of four was punctured from the sequence then only three symbols would be transmitted for every two data bits. This would result in a rate  $^{2}/_{3}$  code. The coding gain is significantly less than that for unpunctured operation, but this is the trade-off for the reduced bandwidth required to transmit the information. The STEL-2060CC decoder is designed to operate with punctured codes as well as rate  $^{1}$ /2 code. Two methods are provided for depuncturing the symbols. The external method can be used for all rates and patterns up to rate 7/8 by indicating which symbols were punctured at the encoder (and then reinserted prior to decoding) with the PNCG1 and PNCG2 signals. When one of these signals is set high the input data at the corresponding symbol input is ignored, and the internally generated metric for the symbol pair (G1 and G2) assigns a zero weight to the punctured symbol in the pair. This is done because the Viterbi decoder has no way of knowing what the punctured symbol should have been. The recommended puncturing sequences for the various (N-1)/N rates of punctured operation are shown in the tables. The portions shown in boldface are the basic sequences, which are then repeated. The use of the **PNCG1** and **PNCG2** signals for rate  $^{3}/_{4}$  is shown in the External Puncturing timing diagrams. The sequence for rate  $^{3}/_{4}$  is G1 G2 P G2 G1 P, and the punctured symbols are marked with asterisks in the timing diagrams.

#### **USING INTERNAL DEPUNCTURING**

The internal depuncturing method supports Rates <sup>2</sup>/3, <sup>3</sup>/4 and 7/8 using the puncturing sequences specified in the tables, and the node sync process will automatically find the correct places to reinsert the punctured symbols. The puncturing sequences used for the rates supported are shown in the tables, along with the speeds of the two input clocks, SYMCKIN and DCLKIN. The portions shown in boldface are the basic sequences, which are then repeated. The symbol sequence for rate 2/3 is shown in the Internal Puncturing timing diagrams. The sequence is G1 G2 P G2; only G1 symbols are punctured in this particular sequence. The SYMCKIN and DCLKIN clocks are used to clock in the symbols and to clock out the data bits. The speeds of these two clocks vary according to the modes and rate in use. When operating in the External Depuncturing modes the DCLKIN signal is not used and the SYMCKIN speed will be equal to the data rate (D) in the parallel mode (PARL = 1) and be equal to twice the data rate (2D) in the sequential mode (**PARL** = 0). In the Internal Depuncturing modes, however, DCLKIN is used and the speed of SYMCKIN will be as shown in the tables.

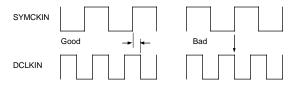

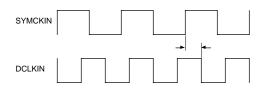

The depuncturing circuit in the STEL-2060CC takes symbols synchronized to the SYMCKIN signal and depunctures them, i.e., inserts dummy symbols into the signal stream at the appropriate positions. To do this the circuit handles the symbols as a group of up to four pairs, depending on the code rate. This circuit operates at the SYMCKIN rate and, at this point, the group of depunctured symbols is transferred into another set of registers clocked with DCLKIN. There is an internal timing requirement that the falling edge of DCLKIN must follow the rising edge of SYMCKIN by a minimum of 8 nsec. at this instant, otherwise the handover will not occur correctly. This occurs once every 4 cycles of DCLKIN at rate  $^{7}/_{8}$ , every 2 cycles at rate  $^{3}/_{4}$  and every 3 cycles at rate  $^{2}/_{3}$ , the number of cycles of SYMCKIN depending on whether the parallel or sequential input mode is used, as well as the code rate. Two examples of clock phasing for rate  $^{3}/_{4}$  parallel operation are shown below.

In the first example the falling edges of DCLKIN never coincide with the rising edges of SYMCKIN. Thus the timing violation will never occur provided that the delay from the non-coincident rising edges of SYMCKIN to the following falling edge of DCLKIN (shown by the arrows) exceeds 8 nsec. In the second case the falling edge of DCLKIN coincides with the rising edge of SYMCKIN once every two cycles of DCLKIN, resulting in a 50% probability that this may be the point at which the handover occurs, creating the problem discussed above.

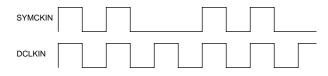

There are several ways to satisfy the timing requirement, depending on the code rate. One effective way which works at all rates is to generate SYMCKIN from DCLKIN by puncturing the clock to reduce its frequency while keeping all the edges synchronized; this will require the use of a small FIFO to buffer the input symbols to cope with the punctured clock. The rate <sup>3</sup>/4 timing is shown below as an example.

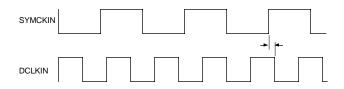

For rate <sup>3</sup>/4 operation it is possible to generate the two clocks with a mutual phase relationship that can exclude the timing violation, as was shown in the first figure. As previously stated, provided the two clocks can be generated as shown in the first example, where only the **rising** edges of DCLKIN coincide with the edges of SYMCKIN, the timing violation will never occur provided that the delay from the non-coincident rising edges of SYMCKIN to the following falling edge of DCLKIN (shown by the arrows) exceeds 8 nsec. In the example shown this will be true at data rates up to 30 Mbps. Care must be taken to ensure that jitter between the clocks is kept low enough to avoid the timing violation, as shown below.

Here, the timing is such that the falling edges of DCLKIN only coincide with falling edges of SYMCKIN, never with rising edges. In this case the timing violation never occurs at any speed, since the non-coincident falling edges of DCLKIN will trail the rising edges of SYMCKIN by approximately 8 nsec. at a speed of 45 Mbps. Again, the same caveat regarding jitter must be observed. However, the symbol signal setup and hold requirements, shown in page 11 of the data sheet make it necessary for SYMCKIN to have a minimum low time of 12 nsec. to satisfy these requirements, so that it is not possible for this signal to be a square wave above 40 MHz for this reason. Since the method for eliminating the clock timing violation presented here relies on the use of square waves (50% mark-space ratio), it cannot be used above 40 MHz because of the setup and hold time requirements.

Again, a similar condition exists for rate  $^{7}/_{8}$  operation, as shown below.

However, in this case the timing violation will begin to occur at speeds over 15 Mbps, so that this method of solving the timing problem is less useful for rate  $^{7}/8$  operation.

Note that for sequential mode operation (PARL = 0) the frequency of the SYMCKIN signal will be doubled in every case. This presents a problem with the synchronized clock method presented here since it will not be possible to generate the necessary waveforms with the correct mutual phasing guaranteed because of the phase ambiguity of the SYMCKIN signal itself relative to the internal handover process. In this case it will be necessary to use either the punctured clock approach or the synchronized reset approach.

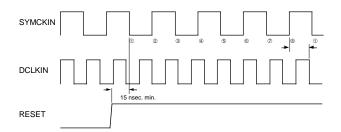

The third method, which, while having the disadvantage that it is susceptible to loss of sync from disturbances, is easier to implement than clock puncturing and provides a lot more margin than simple clock phase synchronization. It consists of a synchronized reset generator used in conjunction with clock phase synchronization. This is shown below for rate  $^{7}/8$ .

This ensures that the STEL-2060CC starts up during the optimum phase of the SYMCKIN/DCLKIN repetition cycle, i.e., the phase with the maximum separation between the rising edge of SYMCKIN and the next falling edge of DCLKIN;

the decoder will then continue to operate correctly provided that nothing occurs to upset this cycle. This method exploits the fact that not all falling edges of DCLKIN have a timing sensitivity relative to the rising edges of SYMCKIN, as was discussed earlier. For example, in rate <sup>7</sup>/8 operation only every fourth falling edge of DCLKIN is critical, starting with the fourth one after the reset is released. By timing the rising edge of the reset at a point in the cycle where there is good separation between the rising edge of SYMCKIN and the following falling edge of DCLKIN the same situation will occur again every four cycles of DCLKIN, which is precisely where the timing sensitivity occurs, as shown in the figure. This method ensures good timing margins for stable operation at all data rates up to 40 Mbps, this limit again being set by the symbol setup and hold time requirements and need to use square waves for the clocks.

## **ELECTRICAL CHARACTERISTICS**

## ABSOLUTE MAXIMUM RATINGS

**Warning:** Stresses greater than those shown below may cause permanent damage to the device. Exposure of the device to these conditions for extended periods may also affect device reliability.

| Symbol                | Parameter                                                | Range                 | Units |

|-----------------------|----------------------------------------------------------|-----------------------|-------|

| T <sub>stg</sub>      | Storage Temperature                                      | -65 to +150           | °C    |

| T <sub>a</sub>        | Operating Temperature (Ambient)                          | -40 to +85            | °C    |

| V <sub>DDmax</sub>    | Max. voltage between $V_{\text{DD}}$ and $V_{\text{SS}}$ | +7 to -0.7            | volts |

| V <sub>I/O(max)</sub> | Max. voltage on any input or output pin                  | V <sub>DD</sub> + 0.3 | volts |

| V <sub>I/O(min)</sub> | Min. voltage on any input or output pin                  | $V_{SS} - 0.3$        | volts |

## RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter                       | Range       | Units |

|-----------------|---------------------------------|-------------|-------|

| V <sub>DD</sub> | Supply Voltage                  | $+5\pm10\%$ | volts |

| T <sub>a</sub>  | Operating Temperature (Ambient) | 0 to +70    | °C    |

#### **D.C. CHARACTERISTICS** (Operating Conditions: $V_{DD} = 5.0 \pm 5\%$ volts, $T_a = 0^{\circ}$ to 70° C)

| Symbol               | Parameter                      | Min. | Тур. | Max. | Units   | Conditions                     |

|----------------------|--------------------------------|------|------|------|---------|--------------------------------|

| I <sub>DD(Q)</sub>   | Supply Current, Quiescent      |      |      | 1.0  | mA      | Static, no clock               |

| I <sub>DD</sub>      | Supply Current, Operational    |      | 8    |      | mA/Mbps | @ 45 Mbps (f <sub>DATA</sub> ) |

| V <sub>IH(min)</sub> | Min. High Level Input Voltage  | 2.0  |      |      | volts   | Guaranteed Logic '1'           |

| V <sub>IL(max)</sub> | Max. Low Level Input Voltage   |      |      | 0.8  | volts   | Guaranteed Logic '0'           |

| V <sub>OH(min)</sub> | Min. High Level Output Voltage | 2.4  |      |      | volts   | $I_{O} = -4.0 \text{ mA}$      |

| V <sub>OL(max)</sub> | Max. Low Level Output Voltage  |      |      | 0.4  | volts   | $I_0 = +4.0 \text{ mA}$        |

| I <sub>IH(max)</sub> | Max. High Level Input Current  |      |      | 10   | μΑ      | $V_{IN} = +5.0 \text{ volts}$  |

| I <sub>IL(max)</sub> | Max. Low Level Input Current   |      |      | -10  | μΑ      | $V_{IN} = 0$ volts             |

## TIMING. RATE <sup>1</sup>/<sub>2</sub> AND EXTERNAL DEPUNCTURING

## **A.C. CHARACTERISTICS** (Operating Conditions: $V_{DD} = 5.0 \pm 5\%$ volts, $T_a = 0^{\circ}$ to 70° C)

| Symbol                                | Parameter                                                                           | Min. | Max. | Units  | Conditions                                                 |

|---------------------------------------|-------------------------------------------------------------------------------------|------|------|--------|------------------------------------------------------------|

| f <sub>DAT</sub>                      | Data speed, Parallel input mode ( <b>PARL</b> = 1),                                 |      | 45   | Mbps   | <b>PARL</b> = 1 and $\mathbf{i}$                           |

|                                       | all rates when <b>not</b> using Internal Depuncturing                               |      |      |        | $\mathbf{RATE}_{\mathbf{2-0}} = 0 \qquad \mathbf{\int}$    |

| f <sub>DAT</sub>                      | Data speed, Sequential input mode (PARL = 0), Rate $^{1}/_{2}$                      |      | 45   | Mbps   | $\mathbf{PARL} = 0 \text{ or }$                            |

|                                       | and all rates and modes when using Internal Depuncturing                            |      |      |        | $\mathbf{RATE}_{\mathbf{2-0}} \neq 0 \qquad \mathbf{\int}$ |

| t <sub>SU</sub>                       | G1, G2, PNCG1 or PCNG2, LDG2 to SYMCKIN Setup                                       | 3    |      | nsecs. | $\mathbf{PARL} = 0 \text{ or }$                            |

| t <sub>HD</sub>                       | G1, G2, PNCG1 or PCNG2, LDG2 to SYMCKIN Hold                                        | 5    |      | nsecs. | $\mathbf{RATE}_{\mathbf{2-0}} = 0 \qquad \mathbf{\int}$    |

| t <sub>SUI</sub>                      | G1, G2, PNCG1 or PCNG2, LDG2 to SYMCKIN Setup                                       | 6    |      | nsecs. | <b>PARL</b> = 1 and $\mathbf{i}$                           |

| t <sub>HDI</sub>                      | G1, G2, PNCG1 or PCNG2, LDG2 to SYMCKIN Hold                                        | 6    |      | nsecs. | $\mathbf{RATE}_{\mathbf{2-0}} \neq 0 \qquad \int$          |

| t <sub>SHPE</sub> , t <sub>SLPE</sub> | SYMCKIN Pulse width (high or low), Parallel input mode,                             | 10   |      | nsecs. | <b>PARL</b> = $1$ and                                      |

|                                       | all rates when <b>not</b> using Internal Depuncturing                               |      |      |        | $\mathbf{RATE}_{\mathbf{2-0}} = 0  \mathbf{\mathbf{5}}$    |

| t <sub>SHPI</sub> , t <sub>SLPI</sub> | SYMCKIN Pulse width (high or low), Parallel input mode,                             | 12   |      | nsecs. | <b>PARL</b> = $1$ and                                      |

|                                       | all rates when using Internal Depuncturing                                          |      |      |        | $\mathbf{RATE}_{\mathbf{2-0}} \neq 0 \qquad \mathbf{5}$    |

| t <sub>SHS,</sub> t <sub>SLS</sub>    | SYMCKIN Pulse width (high or low), Serial input mode                                | 6    |      | nsecs. | $\mathbf{PARL} = 0$                                        |

| t <sub>SO</sub>                       | <b>SYMCKIN</b> to <b>ODCLK</b> stable delay ( $RATE_{2-0} = 000$ )                  | 3    | 8    | nsecs. |                                                            |

| t <sub>DO</sub>                       | <b>DCLKIN</b> to <b>ODCLK</b> stable delay ( <b>RATE</b> <sub>2-0</sub> $\neq$ 000) | 3    | 8    | nsecs. | Load = 15  pF                                              |

| t <sub>OD</sub>                       | ODCLK to output stable delay, all other outputs                                     | 1    | 3    | nsecs. | $Load = 15 \ pF$                                           |

## PUNCTURED SYMBOL SEQUENCES

#### 1. RATE 1/2 AND EXTERNAL DEPUNCTURING - SEQUENTIAL INPUTS (PARL = 0)

| Rate            |                 | Symbol sequence (suffix is symbol number in sequence, all at G1 <sub>2-0</sub> input) |                 |                 |                       |                 |                |                                         |                 |                 |                 |                 |                 |                 | SYMCKIN | DCLKIN |

|-----------------|-----------------|---------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------|-----------------|----------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------|--------|

| 1/2             | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | G1 <sub>2</sub> | G2 <sub>2</sub> | G1 <sub>3</sub>       | G2 <sub>3</sub> | (No            | (Not Punctured)                         |                 |                 |                 |                 |                 |                 | 2 D     | 0      |

| 2/3             | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | G1 <sub>3</sub>       | G2 <sub>3</sub> | $P_4$          | $P_4$ $G2_4$ $G1_5$ $G2_5$ $P_6$ $G2_6$ |                 |                 |                 |                 |                 | 2 D             | 0       |        |

| <sup>3</sup> /4 | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | G1 <sub>3</sub>       | P <sub>3</sub>  | $G1_4$         | $G2_4$                                  | $P_5$           | G2 <sub>5</sub> | G1 <sub>6</sub> | $P_6$           | G1 <sub>7</sub> | G2 <sub>7</sub> | 2 D     | 0      |

| 4/5             | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | <b>P</b> <sub>3</sub> | G2 <sub>3</sub> | $\mathbf{P}_4$ | G2 <sub>4</sub>                         | $G1_5$          | G2 <sub>5</sub> | $P_6$           | $P_6$           | G2 <sub>7</sub> | $P_7$           | 2 D     | 0      |

| <sup>5</sup> /6 | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | G1 <sub>3</sub>       | P <sub>3</sub>  | $\mathbf{P}_4$ | G2 <sub>4</sub>                         | G1 <sub>5</sub> | $P_5$           | G1 <sub>6</sub> | G2 <sub>6</sub> | $P_7$           | G2 <sub>7</sub> | 2 D     | 0      |

| 6/7             | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | <b>P</b> <sub>3</sub> | G2 <sub>3</sub> | G14            | $\mathbf{P}_4$                          | $P_5$           | G2 <sub>5</sub> | G1 <sub>6</sub> | P <sub>6</sub>  | G1 <sub>7</sub> | G2 <sub>7</sub> | 2 D     | 0      |

| 7/8             | G1 <sub>1</sub> | G2 <sub>1</sub>                                                                       | $P_2$           | G2 <sub>2</sub> | <b>P</b> <sub>3</sub> | G2 <sub>3</sub> | $\mathbf{P}_4$ | G24                                     | G1 <sub>5</sub> | $P_5$           | P <sub>6</sub>  | G2 <sub>6</sub> | G1 <sub>7</sub> | $P_7$           | 2 D     | 0      |

#### 2. RATE 1/2 AND EXTERNAL DEPUNCTURING - PARALLEL INPUTS (PARL = 1)

| Rate | Input                                  |                                    | Sym                                | ıbol sequ                          | uence (s                           | uffix is s                         | symbol r                           | number                             | in seque                           | ence)                              | -                                                | SYMCKIN | DCLKIN |

|------|----------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|--------------------------------------------------|---------|--------|

| 1/2  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | G1 <sub>2</sub><br>G2 <sub>2</sub> | G1 <sub>3</sub><br>G2 <sub>3</sub> | G1 <sub>4</sub><br>G2 <sub>4</sub> | G1 <sub>5</sub><br>G2 <sub>5</sub> | G1 <sub>6</sub><br>G2 <sub>6</sub> | (No                                | t Punctu                           | red)                               |                                                  | D       | 0      |

| 2/3  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | P <sub>2</sub><br>G2 <sub>2</sub>  | G1 <sub>3</sub><br>G2 <sub>3</sub> | P <sub>4</sub><br>G2 <sub>4</sub>  | G1 <sub>5</sub><br>G2 <sub>5</sub> | P <sub>6</sub><br>G2 <sub>6</sub>  | G1 <sub>7</sub><br>G2 <sub>7</sub> | P <sub>8</sub><br>G2 <sub>8</sub>  | G1 <sub>9</sub><br>G2 <sub>9</sub> | $\begin{array}{c} P_{10} \\ G2_{10} \end{array}$ | D       | 0      |

| 3/4  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | P <sub>2</sub><br>G2 <sub>2</sub>  | G1 <sub>3</sub><br>P <sub>3</sub>  | G1 <sub>4</sub><br>G2 <sub>4</sub> | P <sub>5</sub><br>G2 <sub>5</sub>  | G1 <sub>6</sub><br>P <sub>6</sub>  | G1 <sub>7</sub><br>G2 <sub>7</sub> | P <sub>8</sub><br>G2 <sub>8</sub>  | G19<br>P9                          | $\begin{array}{c} G1_{10}\\ G2_{10} \end{array}$ | D       | 0      |

| 4/5  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | P <sub>2</sub><br>G2 <sub>2</sub>  | P <sub>3</sub><br>G2 <sub>3</sub>  | P <sub>4</sub><br>G2 <sub>4</sub>  | G1 <sub>5</sub><br>G2 <sub>5</sub> | P <sub>6</sub><br>G2 <sub>6</sub>  | P <sub>7</sub><br>G2 <sub>7</sub>  | P <sub>8</sub><br>G2 <sub>8</sub>  | G1 <sub>9</sub><br>G2 <sub>9</sub> | $\begin{array}{c} P_{10} \\ G2_{10} \end{array}$ | D       | 0      |

| 5/6  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | P <sub>2</sub><br>G2 <sub>2</sub>  | G1 <sub>3</sub><br>P <sub>3</sub>  | P <sub>4</sub><br>G2 <sub>4</sub>  | G1 <sub>5</sub><br>P <sub>5</sub>  | G1 <sub>6</sub><br>G2 <sub>6</sub> | P <sub>7</sub><br>G2 <sub>7</sub>  | G1 <sub>8</sub><br>P <sub>8</sub>  | P9<br>G29                          | $\begin{array}{c} G1_{10} \\ P_{10} \end{array}$ | D       | 0      |

| 6/7  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub> | P <sub>2</sub><br>G2 <sub>2</sub>  | P <sub>3</sub><br>G2 <sub>3</sub>  | G1 <sub>4</sub><br>P <sub>4</sub>  | P <sub>5</sub><br>G2 <sub>5</sub>  | G1 <sub>6</sub><br>P <sub>6</sub>  | G1 <sub>7</sub><br>G1 <sub>7</sub> | P <sub>8</sub><br>G2 <sub>8</sub>  | P9<br>P9                           | $\begin{array}{c} G1_{10}\\ G2_{10} \end{array}$ | D       | 0      |

| 7/8  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> |                                    | P <sub>2</sub><br>G2 <sub>2</sub>  | P <sub>3</sub><br>G2 <sub>3</sub>  | P <sub>4</sub><br>G2 <sub>4</sub>  | G1 <sub>5</sub><br>P <sub>5</sub>  | P <sub>6</sub><br>G2 <sub>6</sub>  | G1 <sub>7</sub><br>P <sub>7</sub>  | G1 <sub>8</sub><br>G2 <sub>8</sub> | P9<br>G29                          | $\begin{array}{c} P_{10} \\ G2_{10} \end{array}$ | D       | 0      |

#### 3. INTERNAL DEPUNCTURING - SEQUENTIAL INPUTS (PARL = 0)

| Rate            |                                                                                                                                                                                   | Symbol sequence (suffix is symbol number in sequence, all at <b>G1<sub>2-0</sub></b> input) |                 |                 |                 |                 |                 |                 |                 |                 |                 |                  |                   | DCLKIN |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-------------------|--------|

| 1/2             | $\mathbf{G1}_{1}  \mathbf{G2}_{1}  \mathbf{G1}_{2}  \mathbf{G2}_{2}  \mathbf{G1}_{3}  \mathbf{G2}_{3}  \mathbf{G1}_{4}  \mathbf{G2}_{4}  \mathbf{G1}_{5}  \text{(Not Punctured)}$ |                                                                                             |                 |                 |                 |                 |                 |                 | 2 D             | 0               |                 |                  |                   |        |

| <sup>2</sup> /3 | G1 <sub>1</sub>                                                                                                                                                                   | G2 <sub>1</sub>                                                                             | G2 <sub>2</sub> | G1 <sub>3</sub> | G2 <sub>3</sub> | $G2_4$          | G1 <sub>5</sub> | G2 <sub>5</sub> | G2 <sub>6</sub> | G17             | G2 <sub>7</sub> | G2 <sub>8</sub>  | <sup>3</sup> /2 D | D      |

| 3/4             | G1 <sub>1</sub>                                                                                                                                                                   | G2 <sub>1</sub>                                                                             | G2 <sub>2</sub> | G1 <sub>3</sub> | $G1_4$          | $G2_4$          | G2 <sub>5</sub> | G1 <sub>6</sub> | G17             | G2 <sub>7</sub> | G2 <sub>8</sub> | G19              | <sup>4</sup> /3 D | D      |

| 7/8             | G1 <sub>1</sub>                                                                                                                                                                   | G2 <sub>1</sub>                                                                             | G2 <sub>2</sub> | G2 <sub>3</sub> | G2 <sub>4</sub> | G1 <sub>5</sub> | G2 <sub>6</sub> | G1 <sub>7</sub> | G1 <sub>8</sub> | G2 <sub>8</sub> | G2 <sub>9</sub> | G2 <sub>10</sub> | <sup>8</sup> /7 D | D      |

4. INTERNAL DEPUNCTURING - PARALLEL INPUTS (PARL = 1)

| Rate | Input                                  | Symbol sequence (suffix is symbol number in sequence) |                                    |                                    |                                    |                                    |                                     | SYMCKIN                              | DCLKIN                               |                                      |                                                   |                   |   |

|------|----------------------------------------|-------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------------------|-------------------|---|

| 1/2  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub>                    | G1 <sub>2</sub><br>G2 <sub>2</sub> | G1 <sub>3</sub><br>G2 <sub>3</sub> | G1 <sub>4</sub><br>G2 <sub>4</sub> | G1 <sub>5</sub><br>G2 <sub>5</sub> | G1 <sub>6</sub><br>G2 <sub>6</sub>  | G1 <sub>7</sub><br>G2 <sub>7</sub>   | (No                                  | t Punctu                             | ured)                                             | D                 | 0 |

| 2/3  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub>                    | G2 <sub>2</sub><br>G1 <sub>3</sub> | G2 <sub>3</sub><br>G2 <sub>4</sub> | G1 <sub>5</sub><br>G2 <sub>5</sub> | G2 <sub>6</sub><br>G1 <sub>7</sub> | G2 <sub>7</sub><br>G2 <sub>8</sub>  | G1 <sub>9</sub><br>G2 <sub>9</sub>   | G2 <sub>10</sub><br>G1 <sub>11</sub> | G2 <sub>11</sub><br>G2 <sub>12</sub> |                                                   | <sup>3</sup> /4 D | D |

| 3/4  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub>                    | G2 <sub>2</sub><br>G1 <sub>3</sub> | G1 <sub>4</sub><br>G2 <sub>4</sub> | G2 <sub>5</sub><br>G1 <sub>6</sub> | G1 <sub>7</sub><br>G2 <sub>7</sub> | G2 <sub>8</sub><br>G1 <sub>9</sub>  | G1 <sub>10</sub><br>G2 <sub>10</sub> | G2 <sub>11</sub><br>G1 <sub>12</sub> | G1 <sub>13</sub><br>G2 <sub>13</sub> | $\begin{array}{c} G2_{14} \\ G1_{15} \end{array}$ | <sup>2</sup> /3 D | D |

| 7/8  | G1 <sub>2-0</sub><br>G2 <sub>2-0</sub> | G1 <sub>1</sub><br>G2 <sub>1</sub>                    | G2 <sub>2</sub><br>G2 <sub>3</sub> | G2 <sub>4</sub><br>G1 <sub>5</sub> | G2 <sub>6</sub><br>G1 <sub>7</sub> | G1 <sub>8</sub><br>G2 <sub>8</sub> | G2 <sub>9</sub><br>G2 <sub>10</sub> | G2 <sub>11</sub><br>G1 <sub>12</sub> | G1 <sub>13</sub><br>G2 <sub>14</sub> | G1 <sub>15</sub><br>G2 <sub>15</sub> | G2 <sub>16</sub><br>G1 <sub>17</sub>              | <sup>4</sup> /7 D | D |

## INTERNAL DEPUNCTURING TIMING. RATE <sup>2</sup>/<sub>3</sub> SHOWN

**STEL-2060C**

## MICROPROCESSOR INTERFACE TIMING

## A.C. CHARACTERISTICS

(Operating Conditions:  $V_{DD}$  = 5.0 ±5% volts,  $T_a$  = 0° to 70° C)

| Symbol          | Parameter                                                               | Min. | Max. | Units  |

|-----------------|-------------------------------------------------------------------------|------|------|--------|

| t <sub>SM</sub> | CSEL, ADDR <sub>2-0</sub> or DATA <sub>7-0</sub> to WRITE or READ Setup | 10   |      | nsecs. |

| t <sub>HM</sub> | CSEL, ADDR <sub>2-0</sub> or DATA <sub>7-0</sub> to WRITE or READ Hold  | 5    |      | nsecs. |

| t <sub>ww</sub> | WRITE Pulse width                                                       | 5    |      | nsecs. |

| t <sub>ZV</sub> | READ (low) to DATA <sub>7-0</sub> Valid                                 |      | 10   | nsecs. |

| t <sub>vz</sub> | <b>READ</b> (high) to <b>DATA</b> <sub>7-0</sub> High-Impedance         |      | 10   | nsecs. |

## NODE SYNCHRONIZATION

In a communication system using Viterbi decoding the decoder will only operate correctly when the symbols G1 and G2 are loaded into the decoder in the correct order. Identifying which symbol is G1 and which one is G2 is referred to as node synchronization. The STEL-2060C contains a circuit designed to carry out the node synchronization function automatically. It uses the internally generated metrics of the received sequence to do this. These constantly changing parameters are periodically renormalized to keep them within bounds. If renormalization occurs too frequently it is a good indication that the system is not converging, most likely due to lack of node synchronization. The renormalization rate at which the system will decide to change the node sync is determined by the threshold parameter. This is an 8-bit number which is set by the THR<sub>7-0</sub> inputs. When the renormalization count exceeds this value, the OOS output will go high and the AUTO output will pulse high for one clock cycle, as shown during Count Window N in the timing diagram below. The counter is reset after a number of bits determined by the number set by the COUNT<sub>7-0</sub> inputs, so that the threshold must be exceeded somewhere in that period for resynchronization to take place. OOS will be reset if the counter then counts through an entire window and the threshold is not exceeded, as shown during Count Window N + 1 in the timing diagram below. The most suitable threshold setting will depend on the value of  $E_{\rm b}/N_0$ , the coding rate, and the signal level at the G1 and G2 inputs. For full scale inputs, i.e., the peak signal values almost saturate the digital inputs, suitable starting values for the threshold will be 1% for Rate  $^{1}/_{2}$ , 0.5% for Rates  $^{2}/_{3}$  to  $^{6}$ /7, and 0.1% for Rate  $^{7}$ /8. e.g., for Rate  $^{1}$ /2, if the number of bits over which the measure is made is set to 512  $(COUNT_{7-0} = 01_{H})$  the threshold should be set to 5. Setting **THR**<sub>7-0</sub> = 0 gives a value of 6, which is adequately close. More reliable results will be obtained by counting over a longer period to improve the averaging process, but this increases the time taken to make a decision and hence to acquire node sync. Thus, starting with a low count period and then increasing it (and adjusting the threshold accordingly to maintain a value of 1%) when **OOS** goes low will result in a faster acquisition of correct node sync with a lower probability of accidental loss of node sync once correct sync has been achieved. To use the internal node sync the AUTO output must be connected to the SYNC input. The synchronization sequence depends on the setting of the PARL input. When PARL is set low it is assumed that the data was modulated using BPSK, and when it is set high it is assumed that the data was modulated using QPSK. The appropriate synchronization sequences will be invoked, as shown in the node sync sequence tables. Note that the pipeline delay through the device will be affected by the node sync state. If multiple devices are used in parallel to achieve higher data rates, it is necessary for the all devices to have the same node sync state to equalize their pipeline delays. It will be necessary to reset the devices together to achieve this state

When internal depuncturing is used, additional node sync states exist because of the uncertainty of the current symbol position in the puncture sequence. In this case the node sync circuit will also search through the sequence by adding delays in the depuncturing process to precess through the sequence. In the sequential input mode (PARL = 0) this is simply an extension of the node sync process, since the alternate state is achieved by delaying the symbols. In the parallel input mode, however, this is different from the "invert G2 and swap" process, and in this sync sequence "invert G2 and swap" precedes the delay addition, so that the system goes through both the initial and alternate states for each delay addition tried. This is shown for the Rate  $^2$ /3 case. In each case the symbols are read into the depuncturing circuit in groups of three (in the BPSK mode) or six (in the QPSK mode) and attempts are made to reinsert the punctured symbol in all of the possible insertion positions. The positions of the punctured symbols in the sequences are shown by the asterisks (\*). The resulting groups of four or eight symbols are then decoded in pairs, resulting in two decoded bits in the BPSK mode and four bits in the QPSK mode. For higher rates the sequences will be extensions of this procedure.

When external depuncturing is used, the determination of which symbols were punctured, and need to be reinserted into the symbol sequence, is part of the node sync process. This is because the acquisition of correct node sync cannot be completed until the punctured symbols are reinserted correctly. The **AUTO** and **OOS** outputs of the STEL-2060C can be used as indicators of the operation of the internal node sync process; **OOS** will remain high as long as node sync has not been achieved and **AUTO** will pulse each time a new node sync state is being tried. Since there are only two possible internal node sync states, alternate pulses on the **AUTO** output can be used as an indication that the depuncturing is incorrect and a new depuncturing sequence should be tried externally.

## NODE SYNC TIMING

## NODE SYNC SEQUENCES 1. RATE 1/2

| PARL | Input | Initial State                   | Alternate State   |  |  |

|------|-------|---------------------------------|-------------------|--|--|

| 0    | G1    | G1 <sub>n</sub> G2 <sub>n</sub> | $G2_n$ $G1_{n+1}$ |  |  |

|      | G2    | N.A.                            | N.A.              |  |  |

| 1    | G1    | G1 <sub>n</sub>                 | $\overline{G2_n}$ |  |  |

|      | G2    | G2 <sub>n</sub>                 | G1 <sub>n</sub>   |  |  |

## 2. RATE $^{2}/_{3}$ , PARL = 0 (BPSK MODE)

| Input | Initial State                     | Alternate States                                                             |                                                                                  |  |  |  |

|-------|-----------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

|       |                                   | 1                                                                            | 2                                                                                |  |  |  |

| G1    | $G1_n G2_n^* G2_{n+1}$ (No delay) | G2 <sup>*</sup> G2 <sup>n+1</sup> G1 <sup>n+2</sup><br>(One symbol<br>delay) | G2 <sub>n+1</sub> G1 <sub>n+2</sub> G2 <sub>n+2</sub> *<br>(Two symbol<br>delay) |  |  |  |

## 3. RATE $^{2}/_{3}$ , PARL = 1 (QPSK MODE)

| Input | Initial State                | Alternate States                                                |                                     |                                                                                  |                                     |                                                                                        |  |  |

|-------|------------------------------|-----------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------|--|--|

|       |                              | 1                                                               | 2                                   | 3                                                                                | 4                                   | 5                                                                                      |  |  |

| G1    | $G1_n G2_{n+1} G2_{n+2}^*$   | $G2_{n}^{*} G1_{n+2} G2_{n+3}$                                  | $G2_n^* G1_{n+2} G2_{n+3}$          | $G2_{n+1}G2_{n+2}^*G1_{n+4}$                                                     | $*G2_{n+1} G2_{n+2} *G1_{n+4}$      | $G1_{n+2} G2_{n+3} G2_{n+4}^{*}$                                                       |  |  |

| G2    | $G2_{n}^{*}G1_{n+2}G2_{n+3}$ | $\overline{G1_n}$ $\overline{G2_{n+1}}$ $\overline{G2_{n+2}}^*$ | $G2_{n+1}G2_{n+2}^*G1_{n+4}$        | $\overline{\text{G2}_n}^* \overline{\text{G1}_{n+2}} \overline{\text{G2}_{n+3}}$ | $G1_{n+2}$ $G2_{n+3}$ $G2_{n+4}$    | $\overline{\text{G2}_{n+1}} \ \overline{\text{G2}_{n+2}}^* \overline{\text{G1}_{n+4}}$ |  |  |

|       | (No Invert/Swap<br>No delay) | (Invert/Swap<br>No delay)                                       | (No Invert/Swap<br>One symb. delay) |                                                                                  | (No Invert/Swap<br>Two symb. delay) |                                                                                        |  |  |

## **BER PERFORMANCE**

The coding gain obtained by the use of Convolutional coding and Viterbi decoding is extremely dependent on many parameters. Not surprisingly, the code rate is a primary factor, but so are the bit error rate (BER) and amplitude of the input signal. The BER affects the coding gain because the error correction capability of the Viterbi decoder is dependent on the statistics of the errors, specifically the clustering of errors. As the BER of the input signal increases, so does the clustering, causing a reduction in the error correcting capability of the device, along with the coding gain. The signal amplitude is important because of the weighting given to the signal amplitude as an indication of the likelihood of an error in a given symbol pair. Consequently it is important to maintain the signal amplitude at an optimum level in order to maximize the performance. The performance curves shown above were measured using a digital link simulator with the signal level set at one half of full scale; i.e., the signal amplitude without noise ranged from 101 to 001 in signed magnitude format, or 101 to 010 in offset binary format. The coding gain under these conditions is about 0.2 dB less than that under optimum signal level conditions. The performance of the STEL-2060C is shown here for unpunctured operation (Rate 1/2) as well as punctured operation at the rates for which internal depuncturing is supported (Rates 2/3, 3/4 and 7/8). The error rate for uncoded data is shown for comparison.

## **APPLICATION INFORMATION**

The STEL-2060C can be used in a variety of different environments. One example of a system using a convolutional encoder with the STEL-2060C Viterbi decoder is illustrated here. The STEL-2060C cannot be used as a common decoder in multi-channel applications because of the memory incorporated on the chip which is dedicated to a single channel.

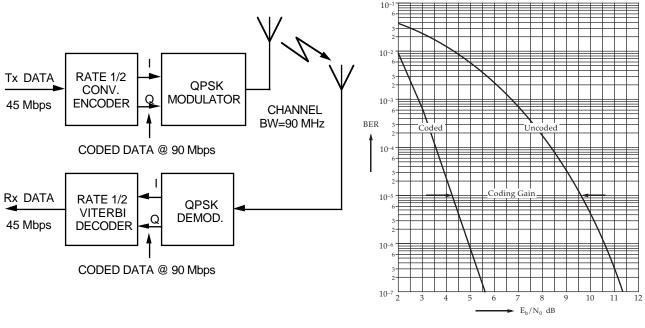

The system modulates a data stream of rate 45 Mbps using binary PSK (BPSK) or quaternary PSK (QPSK). To be able to use convolutional coding, the system must either have available the additional bandwidth needed to transmit symbols at a higher rate or must be able to make use of higher levels of modulation. e.g., by changing from BPSK to QPSK modulation, the data can be encoded at Rate  $^{1}/_{2}$  without requiring any additional bandwidth. The performance improvement that can be expected is shown in the graph below.

The STEL-2060C is designed to accept symbols synchronously. **SYMCKIN** is supplied by the user to clock in the symbols. The maximum data rate is 45 Mbps, using a **SYMCKIN** frequency of 45 MHz (when **PARL** is set high) or 90 MHz (when **PARL** is set low) at rate <sup>1</sup>/<sub>2</sub>, corresponding to 90 MSymbols per sec.

**QPSK Communication System Using Convolutional** Encoding and Viterbi Decoding. Rate = 1/2

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied

Intel may make changes to specifications and product descriptions at any time, without notice. warranty, relating to sale and/or use of Intel® products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

#### For Further Information Call or Write

#### INTEL CORPORATION

Cable Network Operation 350 E. Plumeria Drive, San Jose, CA 95134 Customer Service Telephone: (408) 545-9700 Technical Support Telephone: (408) 545-9799 FAX: (408) 545-9888