# **FEATURES**

- **20 MBPS OPERATING DATA RATE**

- 5.4 dB CODING GAIN @10<sup>-5</sup> BER (K=7)

- MULTIPLE DEVICES CAN BE MULTIPLEXED TO GIVE UNLIMITED DATA RATES

- OPTIMIZED INTERFACE TO OPERATE WITH BPSK, QPSK, AND OQPSK DEMODULATORS

- OPERATES IN BURST AND CONTINUOUS MODES, WITH INTEGRAL TAIL-OFF

- **AUTO NODE SYNC CAPABILITY**

- **DUAL CONTRAINT LENGTHS:**

$K=6 (G_1 = 73_8, G_2 = 61_8) AND K=7 (G_1 = 171_8, G_2 = 133_8)$

**MULTIPLE RATES:**

$R = \frac{1}{2}, \frac{2}{3}, \frac{3}{4}, \frac{7}{8}$

\* Punctured codes

INTERNAL PUNCTURING CAPABILITY

## **FUNCTIONAL DESCRIPTION**

Convolutional Encoding and Viterbi Decoding are used to provide forward error correction (FEC) which improves digital communication performance over a noisy link. In satellite communication systems where transmitter power is limited, FEC techniques can reduce the required transmission power. The STEL-2020 is a specialized product designed to perform this specific communications related function.

The encoder creates a stream of symbols which are transmitted at twice the information rate. This encoding introduces a high degree of redundancy which enables accurate decoding of the information despite a high symbol error rate resulting from a noisy link.

The STEL-2020 contains a convolutional encoder and Viterbi decoder (including differential, as well as direct encoding/decoding) capable of fully independent (full duplex) operation, with completely independent data clocks. At the decoder the symbol input format can be either serial, i.e., sequential symbols, (for BPSK applications) or parallel (for QPSK and OQPSK applications). The data inputs can be in offset binary or offset signed magnitude formats, with 4-bit soft decision. Auto node sync is provided for (2,1) codes, and provision for external metric assignment is also available. The unique architecture allows the device to operate with a constraint length of either 6 or 7, and punctured codes at Rates. 2/3, 3/4, and 7/8 can be encoded and decoded as well as continuous, Rate 1/2, data. The polynomials used are industry standards.

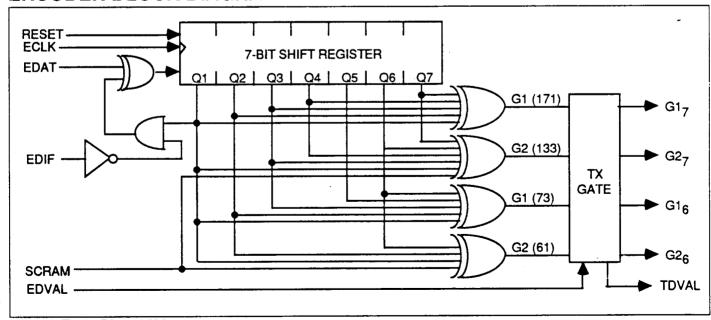

# **ENCODER BLOCK DIAGRAM**

# **PIN CONFIGURATION**

| 1 N        | P                                           | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | 0.129°                  | 129" max.    129" max.   0.135" ±0.01 (0.018" ±0.002" dia   Standoffs: 0.07" high, 0.047" dia.   on 4 corner pins. |                                    |          |                         |  |  |  |  |  |

|------------|---------------------------------------------|---------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|-------------------------|--|--|--|--|--|

| į.         | E   0 0 0<br>D   0 0 0<br>C   0 0 0 0 0 0 0 |                                       | <b>)</b>                | Package: 132 pin Ceramic PGA                                                                                       |                                    |          |                         |  |  |  |  |  |

|            | 1 2 3 4 5 6 7 8  1.415° (r square)          | 9 10 11 12131                         |                         | Note: Tolerances on pin spacing are not cumulative.                                                                |                                    |          |                         |  |  |  |  |  |

| .1         | AUTO                                        | C6                                    | V <sub>ss</sub>         | H1                                                                                                                 | G <sub>2-0</sub>                   | M10      | V <sub>DD</sub>         |  |  |  |  |  |

| .2         | THR <sub>6</sub>                            | C7                                    | V <sub>DD</sub>         | H2                                                                                                                 | V <sub>ss</sub>                    | M11      | I.C.                    |  |  |  |  |  |

| .3         | THR₄                                        | C8                                    | NSO <sub>6</sub>        | H3                                                                                                                 | CLK                                | M12      | $V_{ss}$                |  |  |  |  |  |

| 4          | THR <sub>2</sub>                            | C9                                    | V <sub>ss</sub>         | H12                                                                                                                | V <sub>ss</sub>                    | M13      | V <sub>ss</sub>         |  |  |  |  |  |

| .5         | THR,                                        | C10                                   | SYNC                    | H13                                                                                                                | V <sub>DD</sub>                    | M14      | V <sub>ss</sub>         |  |  |  |  |  |

| 6          | NSO <sub>7</sub>                            | C11                                   | N.C.                    | H14                                                                                                                | V <sub>DD</sub>                    | N1       | V <sub>SS</sub>         |  |  |  |  |  |

| 7          | V <sub>DD</sub>                             | C12                                   | V <sub>SS</sub>         | J1                                                                                                                 | G <sub>2-1</sub>                   | N2       | XBR,                    |  |  |  |  |  |

| 8          | NSO <sub>4</sub>                            | C13                                   | RESET                   | J2                                                                                                                 | G <sub>2-2</sub>                   | N3       | XBR₅                    |  |  |  |  |  |

| 9          | NSO <sub>3</sub>                            | C14                                   | ODVAL                   | J3                                                                                                                 | G <sub>2-3</sub>                   | N4       | V <sub>ss</sub>         |  |  |  |  |  |

| 10         | NSO <sub>1</sub>                            | D1                                    | SCRAM                   | J12                                                                                                                | V <sub>ss</sub>                    | N5       | XBR₀<br>TBD             |  |  |  |  |  |

| 11         | V <sub>ss</sub>                             | D2                                    | SEQ                     | J13                                                                                                                | V <sub>ss</sub>                    | N6<br>N7 |                         |  |  |  |  |  |

| .12<br>.13 | V <sub>DO</sub><br>N.C.                     | D3                                    | BIN                     | J14<br>K1                                                                                                          | V <sub>ss</sub> .                  | 'N8      | V <sub>ss</sub><br>ECLK |  |  |  |  |  |

| 14         |                                             | D12<br>D13                            | V <sub>ss</sub><br>DATO | K2                                                                                                                 | V <sub>DD</sub>                    | N9       | TDVAL                   |  |  |  |  |  |

| 31         | V <sub>DD</sub><br>QPSYNC                   | D13                                   | DIFO                    | K3                                                                                                                 | XBR <sub>11</sub>                  | N10      | G <sub>2-7</sub>        |  |  |  |  |  |

| 2          | BPSYNC                                      | E1                                    | RDVAL                   | K12                                                                                                                | V <sub>ss</sub>                    | N11      | G <sub>2-6</sub>        |  |  |  |  |  |

| 3          | THR,                                        | E2                                    | PNCG,                   | K13                                                                                                                | Vss<br>V                           | N12      | ر<br>I.C.               |  |  |  |  |  |

| 4          | THR <sub>5</sub>                            | E3                                    | PNCG,                   | K14                                                                                                                | V <sub>ss</sub><br>V <sub>ss</sub> | N13      | V <sub>00</sub> _       |  |  |  |  |  |

| 5          | THR <sub>3</sub>                            | E12                                   | V <sub>ss</sub>         | L1                                                                                                                 | XBR <sub>15</sub>                  | N14      | V <sub>ss</sub>         |  |  |  |  |  |

| 6          | THR <sub>0</sub>                            | E13                                   | DIFVAL                  | L2                                                                                                                 | XBR <sub>12</sub>                  | P1       | XBR <sub>8</sub>        |  |  |  |  |  |

| 7          | V <sub>DD</sub>                             | E14                                   | V <sub>ss</sub>         | L3                                                                                                                 | XBR <sub>9</sub>                   | P2       | XBR <sub>6</sub>        |  |  |  |  |  |

| 8          | NSO <sub>5</sub>                            | F1                                    | G <sub>1-1</sub>        | L12                                                                                                                | V <sub>ss</sub>                    | P3       | XBR <sub>3</sub>        |  |  |  |  |  |

| 9          | NSO <sub>2</sub>                            | F2                                    | G <sub>1-0</sub>        | L13                                                                                                                | V <sub>DD</sub>                    | P4       | XBR <sub>2</sub>        |  |  |  |  |  |

| 10         | NSO <sub>0</sub>                            | F3                                    | V <sub>DD</sub>         | L14                                                                                                                | V <sub>ee</sub>                    | P5       | XSEĹ                    |  |  |  |  |  |

| 11         | KEQ7                                        | F12                                   | UČLK                    | M1                                                                                                                 | XBR <sub>13</sub>                  | P6       | $V_{DD}$                |  |  |  |  |  |

| 12         | I.C.                                        | F13                                   | GCLK                    | M2                                                                                                                 | XBR <sub>10</sub>                  | P7       | V <sub>ss</sub>         |  |  |  |  |  |

| 13         | V <sub>ss</sub>                             | F14                                   | $V_{ss}$                | М3                                                                                                                 | V <sub>DD</sub>                    | P8       | EĎAT                    |  |  |  |  |  |

| 14         | V <sub>DD</sub>                             | G1                                    | G <sub>1.2</sub>        | M4                                                                                                                 | XBR₄                               | P9       | EDVAL                   |  |  |  |  |  |

| 1          | V <sub>ss</sub>                             | G2                                    | G.,                     | M5                                                                                                                 | XBR,                               | P10      | $V_{ss}$                |  |  |  |  |  |

| 2          | V <sub>ss</sub><br>OQSYNC                   | G3                                    | V <sub>DO</sub>         | M6                                                                                                                 | V                                  | P11      | G <sub>1.7</sub>        |  |  |  |  |  |

| 3          | V <sub>DO</sub>                             | G12                                   | V <sub>DD</sub>         | M7                                                                                                                 | V <sub>DD</sub>                    | P12      | G <sub>1-6</sub>        |  |  |  |  |  |

| 4          | oös                                         | G13                                   | V <sub>DD</sub>         | M8                                                                                                                 | v <sub>DD</sub>                    | P13      | V <sub>ss</sub>         |  |  |  |  |  |

| 5          | V <sub>DD</sub>                             | G14                                   | V <sub>ss</sub>         | М9                                                                                                                 | EDIF                               | P14      | V <sub>ss</sub>         |  |  |  |  |  |

**STEL-2020**

# **ENCODER OPERATION**

The convolutional coder is functionally independent from the decoder. A single data bit is clocked into the 7-bit shift register on the rising edge of **ECLK**. There are four symbols generated for each data bit, two from K=6 polynomials and two from K=7 polynomials. Only two of these will normally be used at any one time, depending on which constraint length is being used. The four symbols are brought out on separate pins.

# INPUT SIGNALS

#### RESET

Asynchronous master **Reset**. A logic low on this pin will completely reset all internal registers of the chip to an initial condition within 100 nanoseconds. This function is common to the encoder and decoder sections of the device

#### **ECLK**

The transmit clock is the encoder system clock. The maximum ECLK frequency is 20 MHz. There is no minimum frequency.

#### **EDAT**

The encoder input data is connected to this input. The data is clocked in on the rising edge of the ECLK signal.

#### **EDVAL**

The encoder data valid signal is used to identify a group of transmitted bits within the same burst. This signal should be set low at the beginning of a new burst and set high at the end of the burst. The first data bit of the burst will be clocked in on the first rising edge of ECLK after EDVAL goes low. In continuous mode of operation this pin should be held low at all times.

#### **EDIF**

When the EDIF signal is set high it enables the differential encoder circuit. When it is set low this circuit will be disabled, and normal, non-differential data will be loaded into the convolutional encoder.

#### **SCRAM**

When this input is set high it causes the encoded data to be scrambled by inverting the G2 symbols after encoding. This guarantees that there will be a minimum of 1 transition in every 14 symbols in the transmitted symbol stream for Rate ½ encoding when the input data to the encoder contains no transitions. The G2 symbols will also be inverted before decoding when SCRAM is set high. When the SCRAM signal is set low this function will be inhibited.

# **OUTPUT SIGNALS**

G1, G2,

The  $G1_6$  and  $G2_6$  signals are the two encoded symbols generated with the K=6 polynomials,  $G1=73_8$  and  $G2=61_6$ .

G1,, G2,

The G1, and G2, signals are the two encoded symbols generated with the K=7 polynomials, G1=171<sub>8</sub> and G2=133<sub>a</sub>.

#### **TDVAL**

This signal signifies when transmitted data (the output symbols) is valid. When it is low the symbols are valid, and when it is high they are invalid. Invalid data is generated at the end of a burst, when the signals remaining in the shift register are being flushed out.

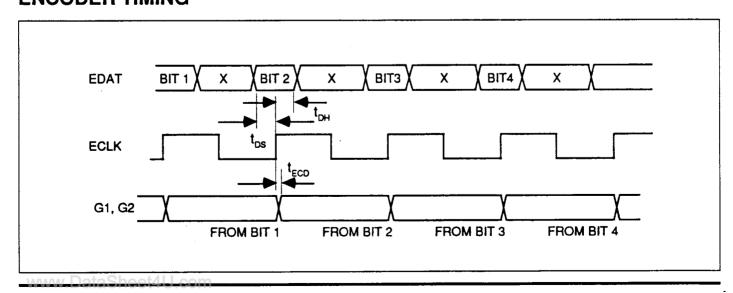

# **ENCODER TIMING**

# **ELECTRICAL CHARACTERISTICS**

# **ABSOLUTE MAXIMUM RATINGS**

Note: Stresses greater than those shown below may cause permanent damage to the device. Exposure of the device to these conditions for extended periods may also affect device reliability.

| Symbol                | Parameter                                  | Range                | Units                |

|-----------------------|--------------------------------------------|----------------------|----------------------|

| T <sub>sig</sub>      | Storage Temperature                        | -65 to +150          | °C                   |

| Ta                    | Operating Temperature                      | ∫–40 to +85          | °C (Plastic package) |

| _                     |                                            | \_55 to +125         | °C (Ceramic package) |

| V <sub>CCmax</sub>    | Max. voltage between $V_{cc}$ and $V_{dd}$ | +7 to -0.7           | volts                |

| V <sub>I/O(max)</sub> | Max. voltage on any input or output pin    | V <sub>00</sub> +0.7 | volts                |

| V <sub>I/O(min)</sub> | Min. voltage on any input or output pin    | V <sub>ss</sub> –0.7 | volts                |

# RECOMMENDED OPERATING CONDITIONS

| Symbol          | Parameter                       | Range                   | Units                                     |

|-----------------|---------------------------------|-------------------------|-------------------------------------------|

| V <sub>DD</sub> | Supply Voltage                  | +5 ± 10%                | volts                                     |

| T <sub>a</sub>  | Operating Temperature (Ambient) | 0 to +70<br>-55 to +125 | °C (Plastic package) °C (Ceramic package) |

# **D.C. CHARACTERISTICS** (Operating Conditions: $V_{DD}$ =5.0 ±5% volts, $T_a$ =0° to 70°C)

| Symbol               | Parameter                      | Min. | Тур. | Max. | Units  | . Conditions                  |

|----------------------|--------------------------------|------|------|------|--------|-------------------------------|

| l <sub>DD(Q)</sub>   | Supply Current, Quiescent      |      |      | 1.0  | mA     | Static, no clock              |

| I <sub>DD</sub>      | Supply Current, Operational    |      |      | 8.0  | mA/MHz | @ 20 MHz                      |

| V <sub>IH(min)</sub> | Min. High Level Input Voltage  | 2.0  | ļ    |      | volts  | Guaranteed Logic '1'          |

| V <sub>IL(max)</sub> | Max. Low Level Input Voltage   |      |      | 0.8  | volts  | Guaranteed Logic '0'          |

| V <sub>OH(min)</sub> | Min. High Level Output Voltage | 2.4  |      |      | volts  | $I_0 = -4.0 \text{ mA}$       |

| V <sub>OL(max)</sub> | Max. Low Level Output Voltage  |      |      | 0.4  | volts  | $l_0 = +4.0 \text{ mA}$       |

| I <sub>IH(max)</sub> | Max. High Level Input Current  |      |      | 10   | μА     | $V_{iN} = +5.0 \text{ volts}$ |

| I <sub>IL(max)</sub> | Max. Low Level Input Current   |      |      | -10  | μА     | V <sub>IN</sub> = 0 volts     |

# **ENCODER A.C. CHARACTERISTICS** (Operating Conditions: $V_{DD}$ =5.0 volts, $V_{SS}$ =0 volts, $V_{a}$ =25°C)

| Symbol            | Parameter                                                                                     | Min. | Max. | Units |

|-------------------|-----------------------------------------------------------------------------------------------|------|------|-------|

| t <sub>os</sub>   | EDAT to ECLK setup                                                                            | 10   |      | nsec. |

| t <sub>on</sub>   | EDAT to ECLK hold                                                                             | 5    |      | nsec. |

| t <sub>ECD</sub>  | ECLK to G1 <sub>8</sub> , G1 <sub>7</sub> , G2 <sub>6</sub> , or G2 <sub>7</sub> stable delay |      | 5    | nsec. |

| f <sub>ECLK</sub> | ECLK frequency                                                                                |      | 20   | MHz   |

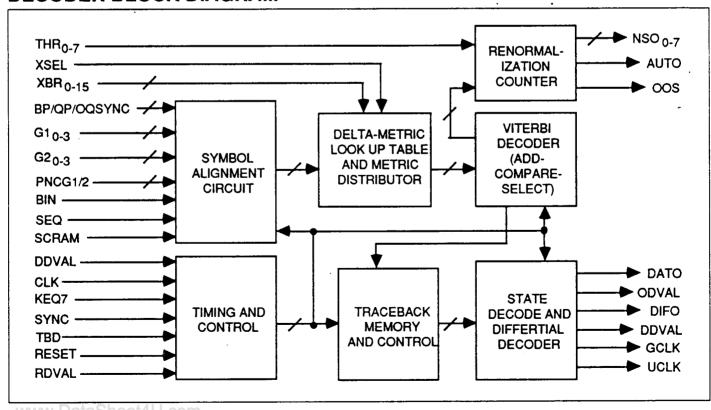

## **DECODER OPERATION**

The decoder section of the STEL-2020 implements the Viterbi algorithm for decoding convolutionally encoded data. It incorporates many unique features which enhance its capabilities and flexibility. The incoming symbols can be accepted either sequentially, as would be the case in a BPSK system, or in parallel, as would be the case in a QPSK system. In addition, a special circuit takes care of symbol alignment in an offset QPSK (OQPSK) system. The signals can be in either offset binary or two's complement codes. In both cases the codes are offset from zero by half a bit, giving the same number of allowable states in both the positive and negative directions. When the encoder uses the scramble function to invert the G2 symbols these will automatically be re-inverted before being decoded.

The Viterbi decoder itself uses the add/compare/select

algorithm to determine the most likely value for each bit from the received symbols. Five-bit arithmetic is used to maximize the performance with the four-bit softdecision data inputs. The decoder contains many user controlled features which enhance its performance in different environments. The depth of the trace-back used can be set to the long mode (70 to 140 states) for optimum performance in the punctured modes (R=2/3, <sup>3</sup>/<sub>4</sub>, <sup>7</sup>/<sub>8</sub>), or to the short mode (38-76 states) in normal mode (R=1/2). (The penalty for using the longer traceback length is the additional delay in decoding the data.) A data valid input also enhances burst mode operation by automatically setting the device into the end-of-burst mode at the correct point in time. A builtin counter estimates the probability of incorrect node synchronization from the error rate. A user selectable feedback loop allows the node synchronization to be corrected automatically.

# **DECODER BLOCK DIAGRAM**

# INPUT SIGNALS

#### RESET

Asynchronous master **Reset**. Alogic low on this pin will completely reset all internal registers of the chip to an initial condition within 100 nanoseconds. This function is common to the encoder and decoder sections of the device.

#### KEQ7

The **KEQ7** signal selects the constraint length of the decoder. When it is high, K=7, and when it is low, K=6.

#### CLK

System clock to the decoder. It is the reference clock for all internal synchronous functions. It should nominally be a square wave at the same frequency as the data, with a maximum frequency of 20 MHz.

#### RDVAL

The Receive data valid signal is used to identify a group of symbols associated with the same burst. This signal should be set low at the beginning of a new burst and set high at the end of the burst. The first data bit of the burst will be clocked in on the first rising edge of CLK after RDVAL goes low. When RDVAL is high it should remain high for at least 1 cycle of CLK. In continuous mode of operation, RDVAL should be set low at all times.

G1<sub>03</sub>, G2<sub>03</sub>

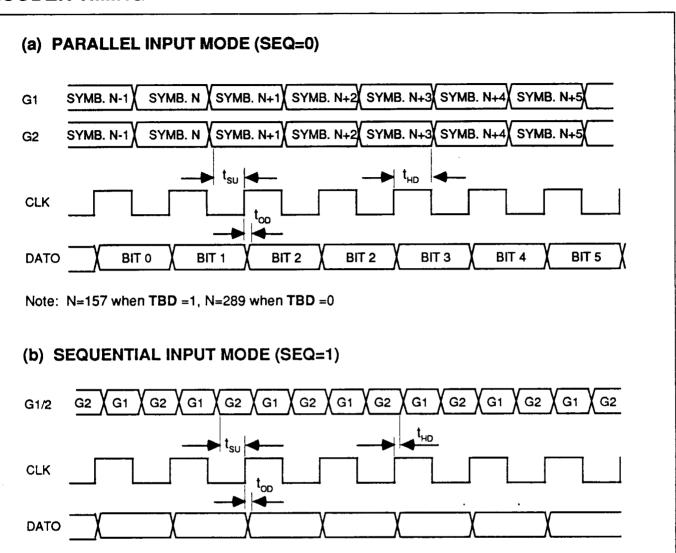

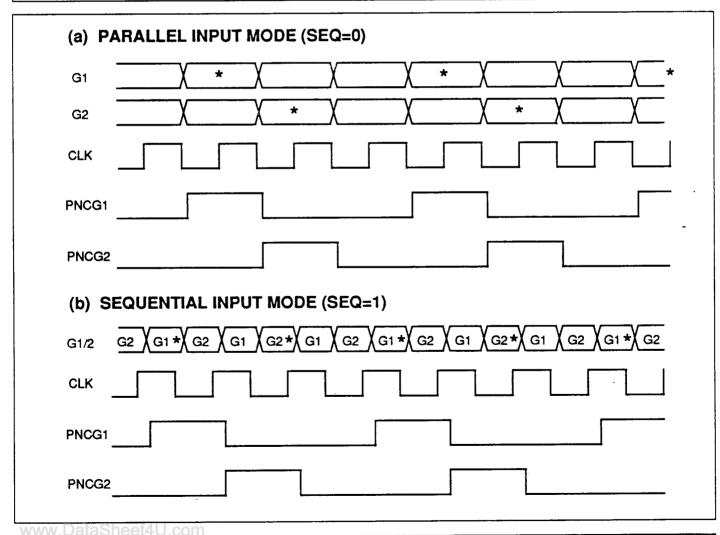

The G1<sub>0.3</sub> and G2<sub>0.3</sub> signals are the 4-bit soft decision input symbols to the decoder. They are presented to the decoder either sequentially or in parallel depending on the state of the SEQ signal. In the parallel mode (SEQ = 0) the symbols are clocked into the device on the rising edge of the CLK. In the sequential mode (SEQ =1) the G2<sub>0.3</sub> inputs are not used, both the G1 and G2 symbols are loaded via the G1<sub>0.3</sub> pins. The G2 symbols are then latched in on the rising edge of CLK and the G1 symbols are latched in on the falling edge.

## SEQ

When this signal is high, the input symbols are accepted **seq**uentially by the chip, using the  $G1_{0.3}$  pins for both symbols. When it is set low the inputs are accepted in parallel, using the  $G1_{0.3}$  pins for the G1 symbols and the  $G2_{0.3}$  pins for the G2 symbols. The sequential input is most suited for BPSK data and the parallel input is most suited for QPSK data.

#### RIN

The STEL-2020 can accept the soft-decision input data in either offset binary or offset 2's complement

formats. When the **BIN** signal is set high the format expected will be offset **bin**ary, and when it is set low it will be offset two's complement. The meanings of the 4-bit values for these two codes is shown in the table.

| Offset 2's Comp. | Offset Binary | Value             |

|------------------|---------------|-------------------|

| 0111             | 1111          | Most confident +  |

| 0110             | 1110          |                   |

| 0101             | 1101          |                   |

| 0100             | 1100          |                   |

| 0011             | 1011          |                   |

| 0010             | 1010          |                   |

| 0001             | 1001          |                   |

| 0000             | 1000          | Least confident + |

| 1111             | 0111          | Least confident - |

| 1110             | 0110          |                   |

| 1101             | 0101          |                   |

| 1100             | 0100          |                   |

| 1011             | 0011          |                   |

| 1010             | 0010          |                   |

| 1001             | 0001          |                   |

| 1000             | 0000          | Most confident -  |

#### **SCRAM**

When this input is set high it causes the encoded data to be scrambled by inverting the G2 symbols after encoding. This guarantees that there will be a minimum of 1 transition in every 14 symbols when the input data to the encoder contains no transitions. The G2 symbols will also be inverted before decoding. When the SCRAM signal is set low, this function will be inhibited. This function is common to the encoder and decoder sections of the device.

#### PNCG1, PNCG2

The PNCG1 and PNCG2 signals are used to control the STEL-2020 when operating in punctured mode. In normal (Rate=1/2) operation these pins should be set low. In punctured mode the PNCG1 signal must be set high to indicate that the G1 symbol is punctured and the PNCG2 signal must be set high to indicate that the G2 symbol is punctured. A symbol will be punctured when the PNCG1 or PNCG2 signals are high during the rising edge of CLK and alternating least-confident ones and zeroes will be substituted for the actual data present on the G1<sub>0-3</sub> or G2<sub>0-3</sub> pins at that time.

#### TBC

This signal selects the Trace-Back Depth used in the decoding process. When it is set low the traceback

depth will be 70 to 140 states, and when it is set high the traceback depth will be 38 to 76 states. The longer traceback depth gives better performance, especially in the punctured modes; the shorter traceback depth gives a shorter latency.

#### SYNC

When the SYNC input is set high, the node sync circuit will be enabled, and when it is set low, the node sync circuit will be disabled. When it is enabled the node sync circuit will examine the renormalization count. If this count is greater than the threshold (defined by the user via the 8 input pins THR) for every 256 bit period, then out-of-sync condition is declared (OOS output signal is set high). The renormalization count for every 256 bit period is available at the 8 output pins NSO<sub>0-7</sub>. This signal can be used externally to correct the node sync. Automatic internal node sync is achieved by connecting the AUTO output to BPSYNC, QPSYNC, or OQSYNC, depending on the mode of operation.

#### BPSYNC, QPSYNC, and OQSYNC

The BPSYNC, QPSYNC, and OQSYNC signals are used to correct the node sync in the Viterbi decoder. The BPSYNC input should be used when the device is being used with BPSK data, the QPSYNC input should be used with QPSK data, and the OQSYNC input should be used with Offset QPSK (OQPSK) data. When these inputs are set low, no change will be made to the symbols, and when they are set high, the G1 and G2 symbols will be interchanged internally in the manner appropriate to the mode of operation. The appropriate input should be connected to the AUTO output to use the internal node sync circuit.

# THR<sub>0-7</sub>

This 8-bit input signal defines the threshold for node synchronization. If the renormalization count is greater than this threshold value then out-of-sync condition is declared (i.e., the output pin OOS is switched to High).

# XBR<sub>0-15</sub>

If the user wishes to use adaptive metrics, or metrics other than the ones stored internally, different branch metrics can be loaded via these 16 pins. XSEL must be set high to enable this function.

#### **XSEL**

When this input is set high, external branch metrics will be used. It is set low for normal operation.

## **OUTPUT SIGNALS**

#### **GCLK**

Gated output data clock. The rising edge of GCLK can be used as a strobe for DATO output, which is guaranteed to be valid on this edge. When ODVAL is High, GCLK is disabled and stays Low.

#### **UCLK**

Ungated output clock. Same as GCLK except that this output clock is not gated by ODVAL.

#### DATO

Decoded data output. This is the output of the Viterbi decoder. The output data bits are delayed by 161 clock cycles relative to the corresponding input symbols, G1<sub>0.3</sub> and G2<sub>0.3</sub>, when operating in the short trace-back depth mode (TBD=1), and 289 clock cycles when operating in the long trace-back depth mode (TBD=0).

#### **ODVAL**

Output Data Valid. This is a replica of RDVAL input, delayed by the same number of clock cycles as the decoded data bits. When ODVAL is low the output data DATO is valid. When it is high DATO is invalid.

#### **DIFO**

Differential decoded data output. This is the output of the Viterbi decoder after passing through the differential decoder. The DIFO output is delayed by one clock cycle relative to the DATO signal.

#### **DIFVAL**

Differential output data valid. When DIFVAL is low DIFO is valid. When it is high DIFO is invalid.

# NSO<sub>0-7</sub>

These are the 8 output bits of renormalization count for every 256-bit period.

## oos

This output pin serves as a flag for the out-of-sync condition. When it goes high it signifies that the renormalization count in the internal node sync circuit has exceeded the threshold value set by the THR<sub>0-7</sub> signal.

#### **AUTO**

The AUTO output is the feedback signal from the internal node sync correction circuit. It will toggle each time the OOS output goes high. It should be connected to BPSYNC, QPSYNC, or OQSYNC, depending on the mode of operation, when the internal node sync facility is used.

# **DECODER TIMING**

# **DECODER A.C. CHARACTERISTICS**

(Operating Conditions:  $V_{DD}$ =5.0  $\pm$  5% volts,  $V_{SS}$ =0 volts,  $T_a$ =0° to 70°C)

| Symbol            | Parameter                | Min. | Max. | Units  | Conditions              |

|-------------------|--------------------------|------|------|--------|-------------------------|

| f <sub>CLK</sub>  | CLK Frequency            |      | 20   | MHz    |                         |

| f <sub>CLK</sub>  | CLK Frequency            |      | 16   | MHz    | @ 125° C (ceramic only) |

| t <sub>su</sub> , | G1 or G2 to CLK setup    | 10   |      | nsecs. |                         |

| t <sub>HD</sub>   | G1 or G2 to CLK hold     | 5    |      | nsecs. |                         |

| top               | CLK to DATO stable delay |      | 5    | nsecs. |                         |

|                   |                          |      |      |        |                         |

# PUNCTURED MODE OPERATION

In punctured codes some of the symbols generated by the convolutional encoder are deleted, or punctured, from the transmitted sequence. For example, in an unpunctured Rate ½ sequence, four bits would be transmitted for every two data bits. If every fourth bit was punctured from the sequence then only three bits would be transmitted for every two data bits. This would result in a Rate ½ code. The STEL-2020 is designed to operate in punctured mode as well as normal, Rate ½, mode. This is easily accomplished by means of the PNCG1 and PNCG2 signals, which delete the symbol which would normally have been loaded into the device at the time when either of these signals is set high. The punctured symbols are replaced by alternating least confident ones and

zeroes, to avoid the introduction of a bias. The Viterbi algorithm treats the least confident symbols as if they were badly corrupted signals, and zero weight is given to them in the computations relative to the other symbols. The coding gain is significantly less than that for unpunctured operation, but this is the trade-off for the reduced bandwidth required to transmit the symbols. The puncturing sequences for the various (N-1)/N rates of punctured operation are shown in the table. The sequence shown in boldface is the basic sequence, which is then repeated. The use of the PNCG1 and PNCG2 signals is shown below for Rate <sup>3</sup>/<sub>4</sub>. The sequence is G1 G2 P G2 G1 P. The punctured symbols are marked with asterisks.

| Rate            | Symbol sequence |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-----------------|-----------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| <sup>2</sup> /3 | G1              | G2 | G1 | P  | G1 | G2 | G1 | Р  | G1 | G2 | G1 | Р  | G1 | G1 | G2 | G1 | Ρ  | G1 |

| 3/4             | G1              | G2 | P  | G2 | G1 | P  | G1 | G2 | Р  | G2 | G1 | Р  | G1 | G1 | G2 | Р  | G2 | G1 |

| <sup>7</sup> /8 | G1              | G2 | P  | G2 | P  | G2 | P  | G2 | G1 | P  | P  | G2 | G1 | P  | G1 | G2 | Р  | G2 |

# NODE SYNCHRONIZATION

In a communication system using Viterbi decoding the decoder will only operate correctly when the symbols G1 and G2 are loaded into the decoder in the correct order. Identifying which symbol is which is referred to as node synchronization. The STEL-2020 contains a circuit designed to carry out the node synchronization function automatically. It uses the internally generated metrics of the received sequence to do this. These parameters are constantly changing and are periodically renormalized to keep them within bounds. If renormalization is required too frequently it is a good indication that the system is not converging, and the most likely reason is lack of node synchronization. The internal node sync circuit will be enabled if the SYNC input is set high. The renormalization rate at which the system will decide to change the node sync is determined by the threshold parameter. This is an 8bit number which is set by the the THR inputs. When the renormalization count exceeds this value, the OOS output will go high and the AUTO output will toggle. The counter is reset every 256 clock cycles, so that the threshold must be exceeded somewhere in the 256 cycle period for resynchronization to take place. To use the internal node sync the AUTO output must be connected to BPSYNC when the data is being entered sequentially, as in a BPSK system. When the data is being entered in parallel from a QPSK system the AUTO output must be connected to QPSYNC, unless the system is supplying OQPSK data, in which case the OQSYNC pin should be used instead of QPSYNC. When this is done the symbol alignment circuit will correct the node synchronization problem. This is different for each of the three modes.

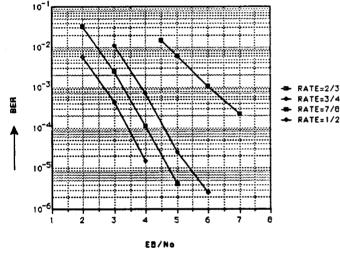

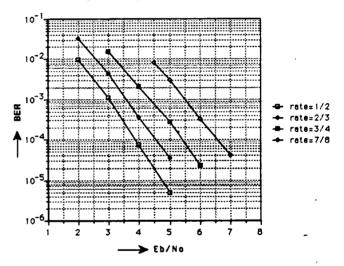

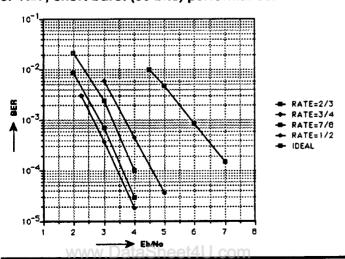

## PERFORMANCE

#### 1. K=7, long burst performance.

### 2. K=6, long burst performance.

#### 3. K=7, short burst (56 bits) performance.

# APPLICATION INFORMATION

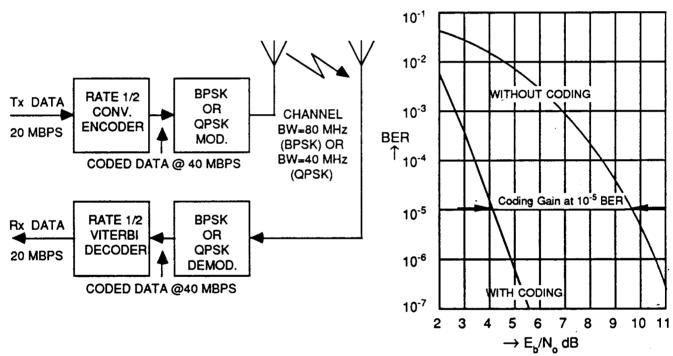

The STEL-2020 can be used in a variety of different environments. One example is shown below. An example of a system using the convolutional coder and Viterbi decoder is illustrated here. The system modulates a data stream of rate 20 Mbps using binary PSK (BPSK) or quaternary PSK (QPSK). To be able to use convolutional coding/decoding, the system must have available the additional bandwidth needed to transmit symbols at twice the data rate (for rate ½ encoding) or make use of two parallel channels (QPSK) to transmit two streams of symbols at the data

rate. The performance improvement that can be expected is shown in the graph below.

The convolutional encoder is functionally independent from the decoder. A single data bit is clocked into the 7 bit shift register on the rising edge of ECLK. The decoder portion of the STEL-2020 is designed to accept symbols synchronously. CLK is supplied by the user to clock in the symbols. The maximum data rate is 20 Mbps, using a clock frequency of 20 MHz. This corresponds to 40 MSymbols per second at Rate ½ with BPSK.

BPSK COMMUNICATION SYSTEM USING CONVOLUTIONAL ENCODING AND VITERBI DECODING. RATE = 1/2

# FOR FURTHER INFORMATION CALL OR WRITE STANFORD TELECOMMUNICATIONS

**ASIC & Custom Products Group**

Direct dial: (408) 980-5684 or Operator assist: (408) 748-1010

Fax: (408) 980-1066 Telex: (910) 339-9531

2421 Mission College Blvd. • Santa Clara, CA 95054-1298

© 1989, 1990 Stanford Telecommunications, Inc. 3/90