## LAN9313/LAN9313i

# Three Port 10/100 Managed Ethernet Switch with MII

## PRODUCT FEATURES

Datasheet

#### **Highlights**

- High performance and full featured 3 port switch with VLAN, QoS packet prioritization, Rate Limiting, IGMP monitoring and management functions

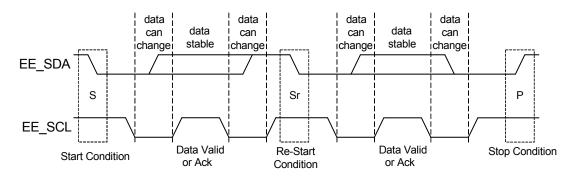

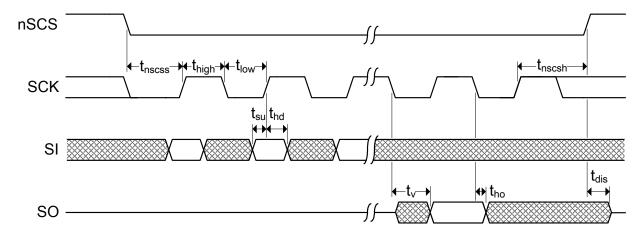

- Serial management via SPI/I<sup>2</sup>C or SMI

- Unique Virtual PHY feature simplifies software development by mimicking the multiple switch ports as a single port PHY

- Integrated IEEE 1588 Hardware Time Stamp Unit

#### **Target Applications**

- Cable, satellite, and IP set-top boxes

- Digital televisions

- Digital video recorders

- VoIP/Video phone systems

- Home gateways

- Test/Measurement equipment

- Industrial automation systems

#### **Key Benefits**

- Ethernet Switch Fabric

- 32K buffer RAM

- 1K entry forwarding table

- Port based IEEE 802.1Q VLAN support (16 groups)

- Programmable IEEE 802.1Q tag insertion/removal

- IEEE 802.1d spanning tree protocol support

- QoS/CoS Packet prioritization

- 4 dynamic QoS queues per port

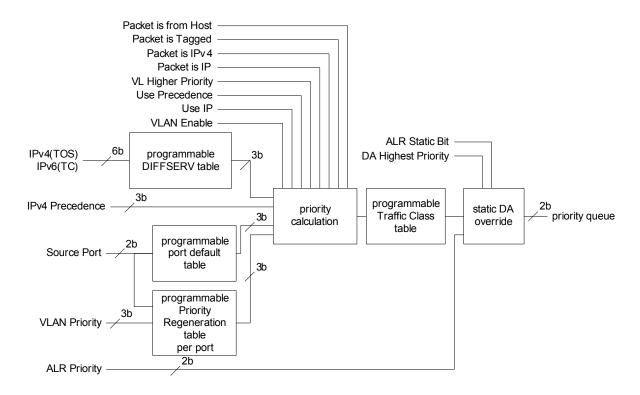

- Input priority determined by VLAN tag, DA lookup, TOS, DIFFSERV or port default value

- Programmable class of service map based on input priority

- Remapping of 802.1Q priority field on per port basis

- Programmable rate limiting at the ingress/egress ports with random early discard, per port / priority

- IGMP v1/v2/v3 monitoring for Multicast packet filtering

- Programmable filter by MAC address

#### Switch Management

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic on any ports or port pairs

- Fully compliant statistics (MIB) gathering counters

- Control registers configurable on-the-fly

#### Ports

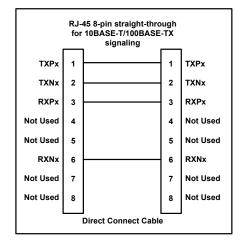

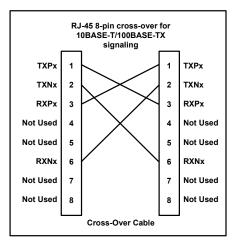

- 2 internal 10/100 PHYs with HP Auto-MDIX support

- 1 MII PHY mode or MAC mode

- Fully compliant with IEEE 802.3 standards

- 10BASE-T and 100BASE-TX support

- Full and half duplex support

- Full duplex flow control

- Backpressure (forced collision) half duplex flow control

- Automatic flow control based on programmable levels

- Automatic 32-bit CRC generation and checking

- 2K Jumbo packet support

- Programmable interframe gap, flow control pause value

- Full transmit/receive statistics

- Auto-negotiation

- Automatic MDI/MDI-X

- Loop-back mode

#### Serial Management

- SPI/I<sup>2</sup>C (slave) access to all internal registers

- MIIM (MDIO) access to PHY related registers

- SMI (extended MIIM) access to all internal registers

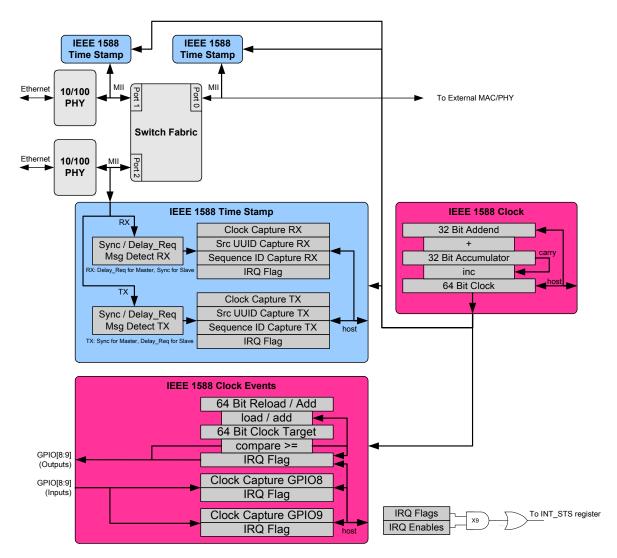

#### ■ IEEE 1588 Hardware Time Stamp Unit

- Global 64-bit tunable clock

- Master or slave mode per port

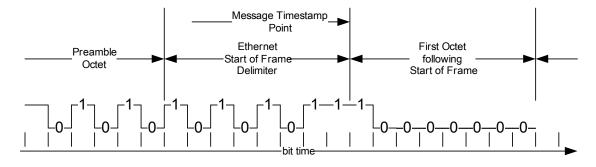

- Time stamp on TX or RX of Sync and Delay\_req packets per port, Timestamp on GPIO

- 64-bit timer comparator event generation (GPIO or IRQ)

#### Other Features

- General Purpose Timer

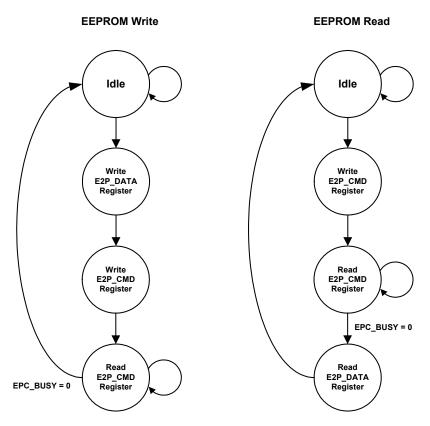

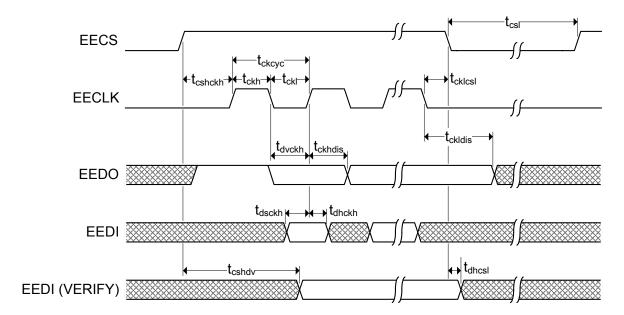

- Serial EEPROM interface (I<sup>2</sup>C master or Microwire<sup>TM</sup> master) for non-managed configuration

- Programmable GPIOs/LEDs

- Single 3.3V power supply

- Available in Commercial & Industrial Temp. Ranges

#### **Order Numbers:**

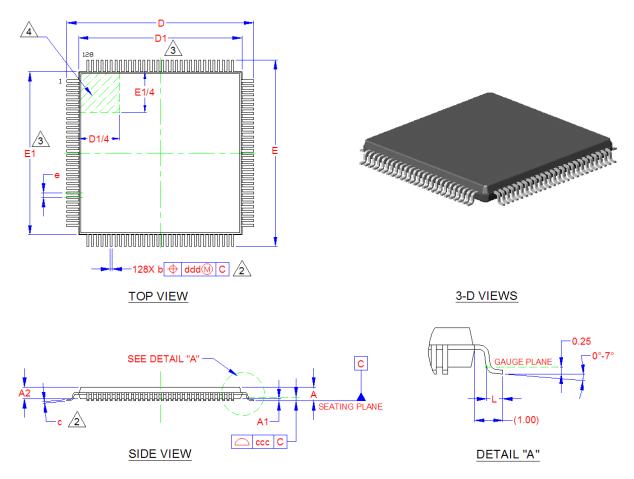

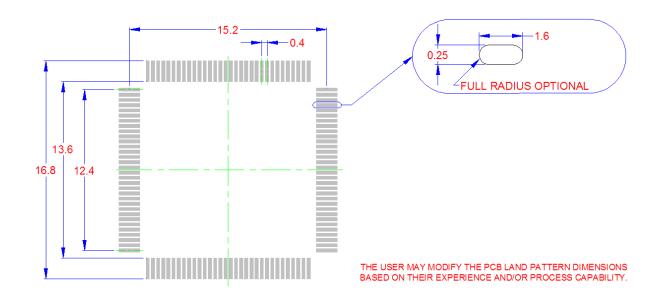

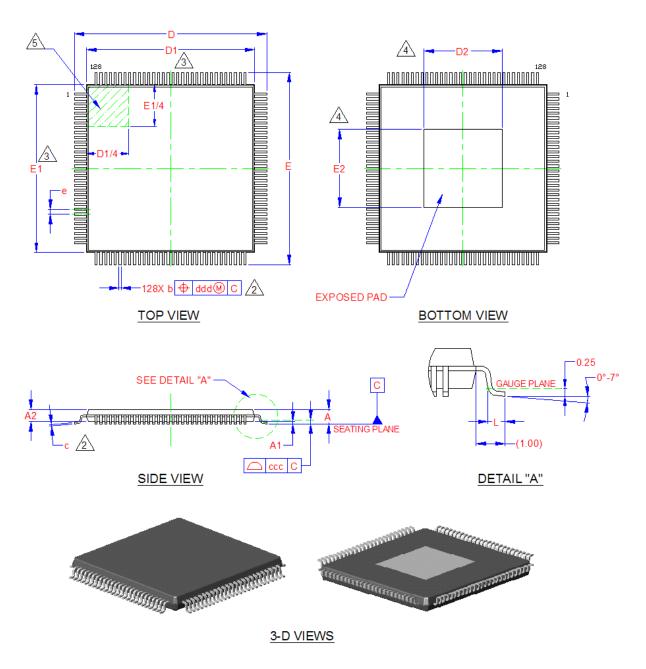

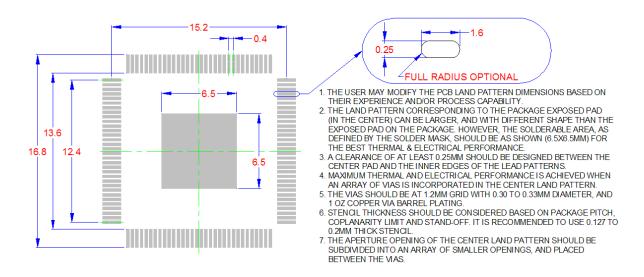

LAN9313-NU For 128-Pin, VTQFP Lead-Free RoHS Compliant Package (0 TO 70°C Temp Range)

LAN9313-NZW For 128-Pin, XVTQFP Lead-Free RoHS Compliant Package (0 TO 70°C Temp Range)

LAN9313i-NZW For 128-Pin, XVTQFP Lead-Free RoHS Compliant Package (-40 TO 85°C Temp Range)

This product meets the halogen maximum concentration values per IEC61249-2-21 For RoHS compliance and environmental information, please visit www.smsc.com/rohs

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2010 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **Table of Contents**

| Chap<br>1.1<br>1.2    | General Terms                                 | 14 |

|-----------------------|-----------------------------------------------|----|

| 1.3                   | Register Nomenclature                         | 17 |

| Chan                  | oter 2 Introduction                           | 10 |

|                       | Operated Description                          | 10 |

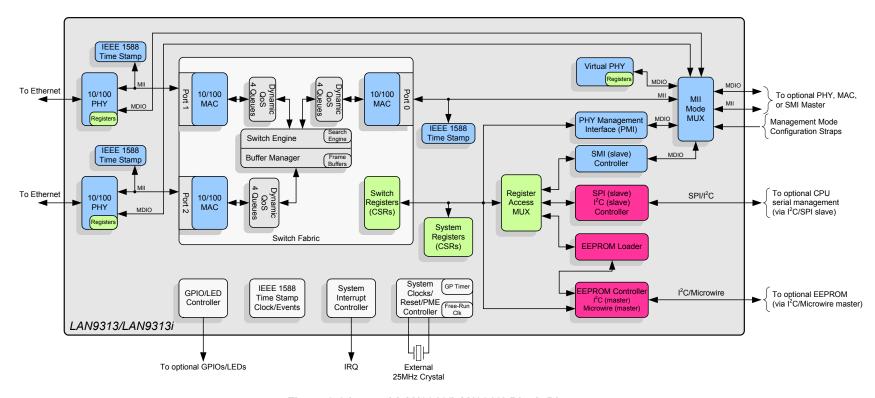

| 2.1                   | General Description                           |    |

| 2.2                   | Block Diagram                                 |    |

| 2.2.1                 | System Clocks/Reset/PME Controller            |    |

|                       | System Interrupt Controller                   |    |

| 2.2.3                 | Switch Fabric                                 |    |

| 2.2.4                 | Ethernet PHYs                                 |    |

| 2.2.5                 | PHY Management Interface (PMI)                |    |

| 2.2.6                 | SPI/I2C Slave Controller                      |    |

| 2.2.7                 | SMI Slave Controller                          |    |

| 2.2.8                 | EEPROM Controller/Loader                      |    |

| 2.2.9                 | 1588 Time Stamp                               |    |

| 2.2.10                |                                               |    |

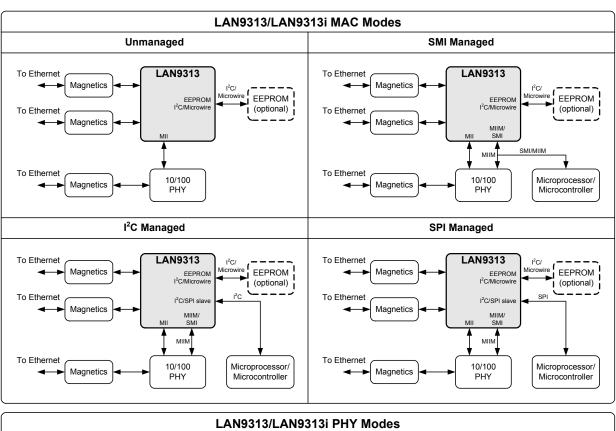

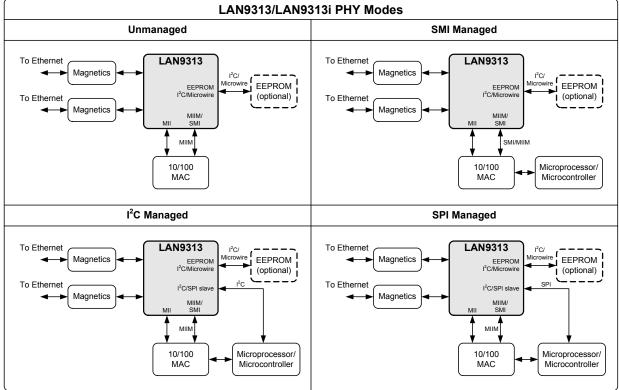

| 2.3                   | Modes of Operation                            |    |

| 2.3.1                 | MAC Mode                                      |    |

| 2.3.2                 | PHY Mode                                      |    |

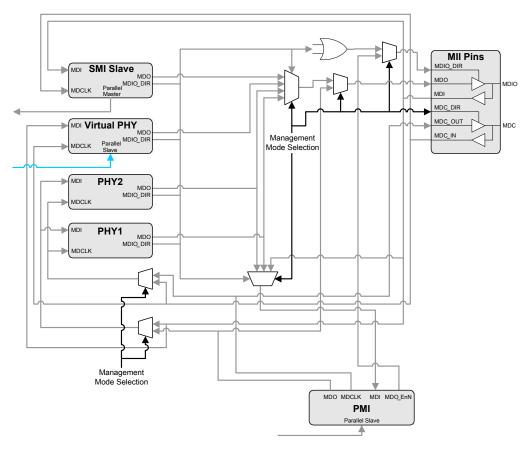

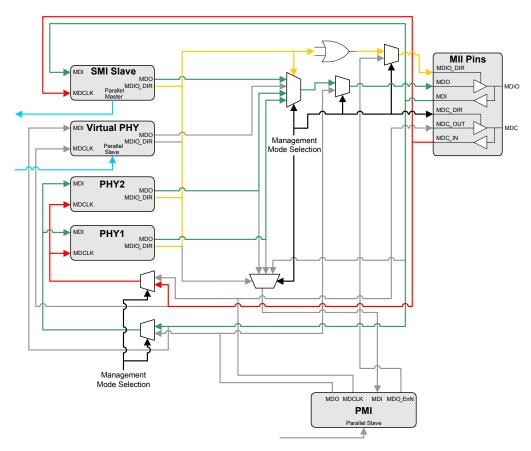

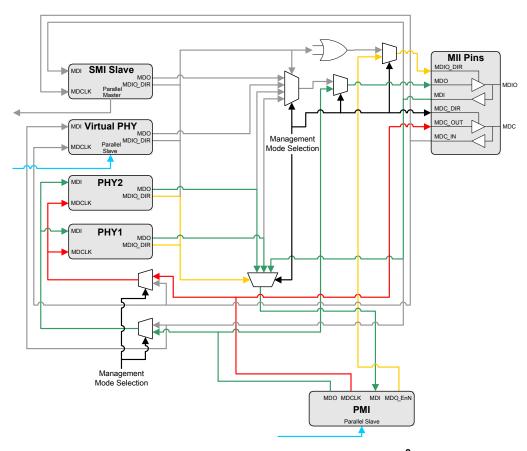

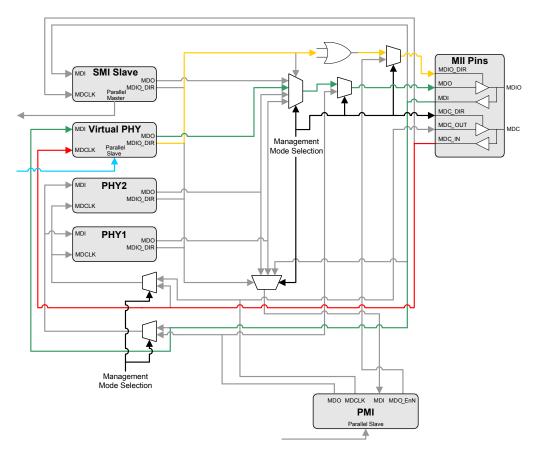

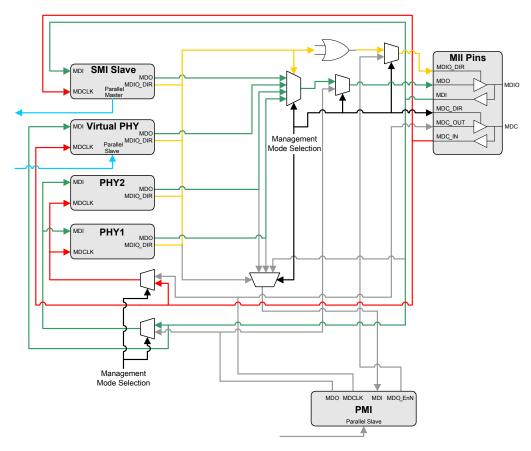

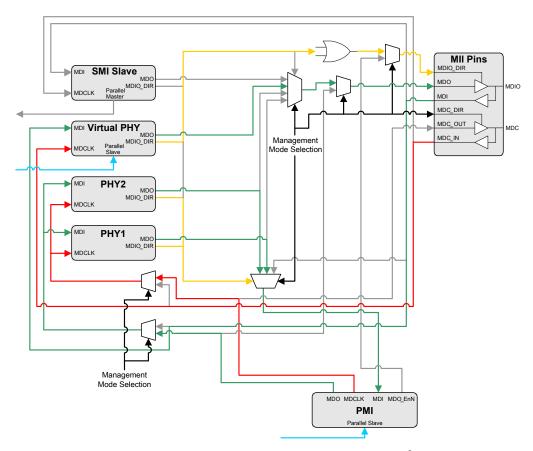

| 2.3.3                 | Management Modes                              | 23 |

| CI                    |                                               | 24 |

|                       | oter 3 Pin Description and Configuration      |    |

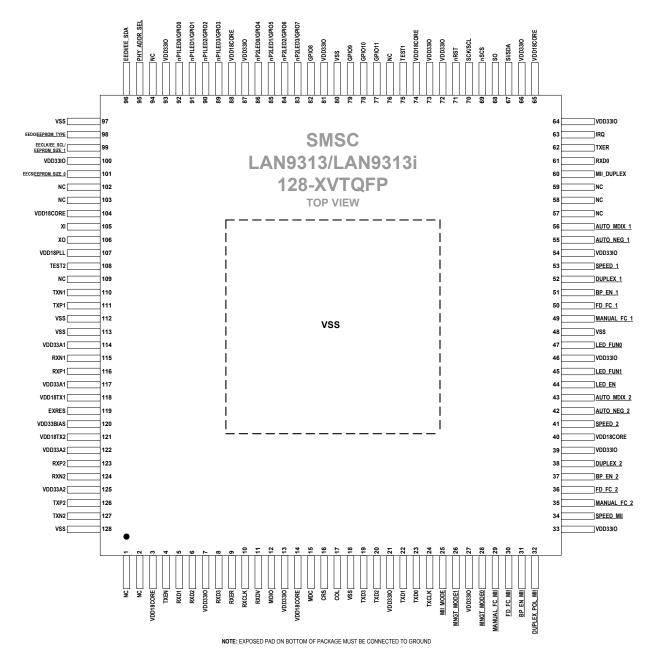

| 3.1                   | Pin Diagrams                                  |    |

| 3.1.1                 | 128-VTQFP Pin Diagram                         |    |

| 3.1.2                 | 128-XVTQFP Pin Diagram                        |    |

| 3.2                   | Pin Descriptions                              | 28 |

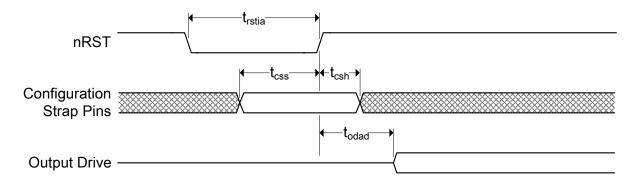

| Chap                  | oter 4 Clocking, Resets, and Power Management | 11 |

| _                     | Clocks                                        | 41 |

| 4.1<br>4.2            |                                               |    |

| 4.2<br>4.2.1          | Resets                                        |    |

| <b>4.∠.</b> I 4.2.1.1 | Chip-Level Resets Power-On Reset (POR)        |    |

| 4.2.1.1               | nRST Pin Reset                                |    |

| 4.2.2                 | Multi-Module Resets                           | 43 |

| 4.2.2.1               | Digital Reset (DIGITAL_RST)                   |    |

| 4.2.3                 | Single-Module Resets                          |    |

| 4.2.3.1<br>4.2.3.2    | Port 2 PHY ResetPort 1 PHY Reset              |    |

| 4.2.3.3               | Virtual PHY Reset                             |    |

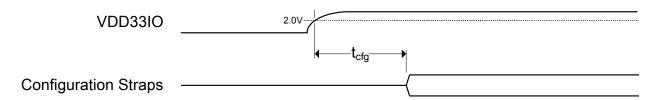

| 4.2.4                 | Configuration Straps                          |    |

| 4.2.4.1<br>4.2.4.2    | Soft-StrapsHard-Straps                        |    |

| 4.3                   | Power Management                              |    |

| 4.3.1                 | Port 1 & 2 PHY Power Management               | 51 |

|                       | <u> </u>                                      |    |

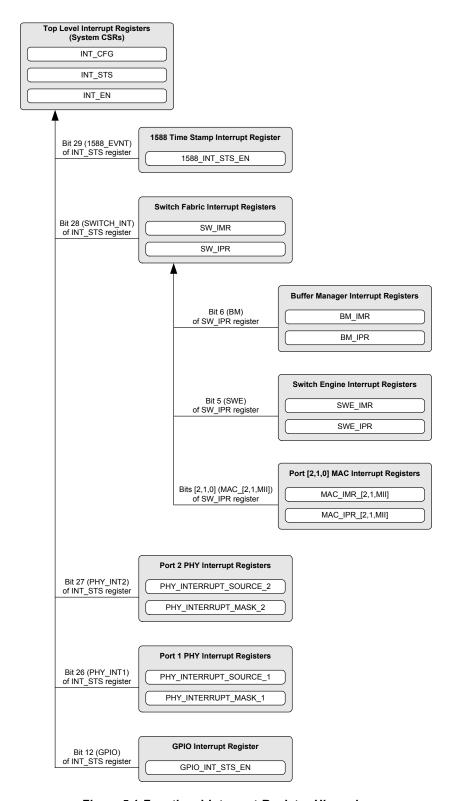

| Chap                  | oter 5 System Interrupts                      | 52 |

| 5.1                   | Functional Overview                           | 52 |

| 5.2                   | Interrupt Sources                             | 52 |

| 5.2.1                 | 1588 Time Stamp Interrupts                    | 54 |

| 5.2.2                 | Switch Fabric Interrupts                      |    |

| 5.2.3                 | Ethernet PHY Interrupts                       |    |

| 5.2.4                 | GPIO Interrupts                               | 55 |

| 5.2.5<br>5.2.6            | General Purpose Timer Interrupt                    | 55<br>56 |

|---------------------------|----------------------------------------------------|----------|

| 5.2.7                     | Device Ready Interrupt.                            |          |

| 0.2.1                     | Dovido Roday intorrupti                            | _        |

| Chap                      | ter 6 Switch Fabric                                | 57       |

| 6.1                       | Functional Overview                                |          |

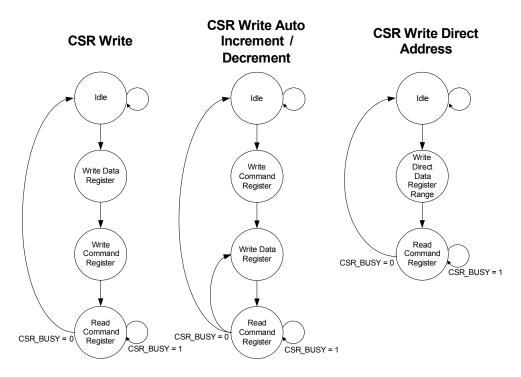

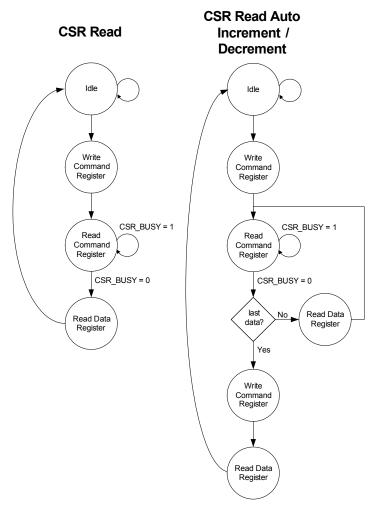

| 6.2                       | Switch Fabric CSRs                                 |          |

| 6.2.1                     | Switch Fabric CSR Writes                           |          |

| 6.2.2                     | Switch Fabric CSR Reads                            |          |

| 6.2.3                     | Flow Control Enable Logic                          |          |

| 6.3                       | 10/100 Ethernet MACs                               |          |

| 6.3.1                     | Receive MAC                                        |          |

| 6.3.1.1                   | Receive Counters                                   |          |

| 6.3.2                     | Transmit MAC                                       |          |

| 6.3.2.1                   | Transmit Counters                                  |          |

| 6.4                       | Switch Engine (SWE)                                |          |

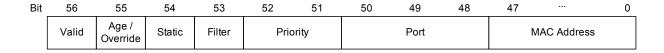

| 6.4.1                     | MAC Address Lookup Table                           |          |

| 6.4.1.1<br>6.4.1.2        | Learning/Aging/MigrationStatic Entries             |          |

| 6.4.1.3                   | Multicast Pruning                                  | 66       |

| 6.4.1.4<br>6.4.1.5        | Address FilteringSpanning Tree Port State Override |          |

| 6.4.1.6                   | MAC Destination Address Lookup Priority            | 66       |

| 6.4.1.7<br><b>6.4.2</b>   | Host Access Forwarding Rules                       |          |

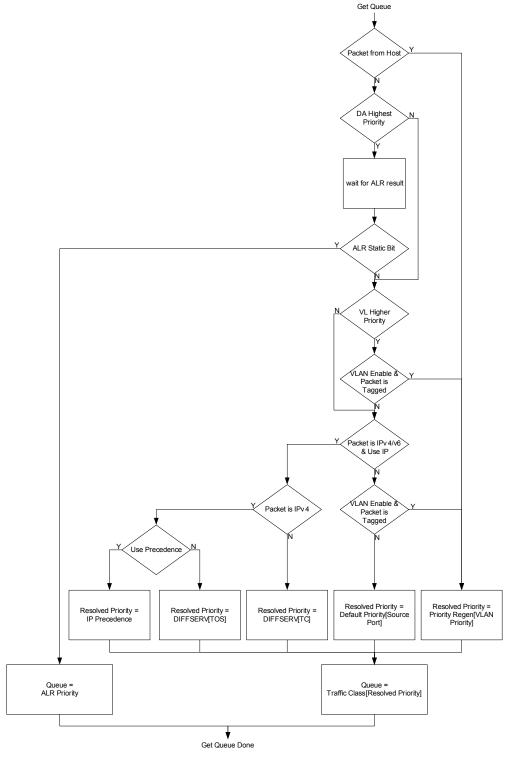

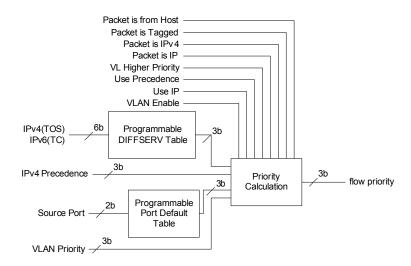

| 6.4.3                     | Transmit Priority Queue Selection                  |          |

| 6.4.3.1                   | Port Default Priority                              |          |

| 6.4.3.2                   | IP Precedence Based Priority                       | 71       |

| 6.4.3.3<br>6.4.3.4        | DIFFSERV Based PriorityVLAN Priority               |          |

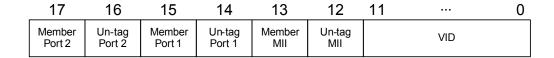

| 6.4.4                     | VLAN Support                                       |          |

| 6.4.5                     | Spanning Tree Support                              |          |

| 6.4.6                     | Ingress Flow Metering and Coloring                 |          |

| 6.4.6.1                   | Ingress Flow Calculation                           | 74       |

| 6.4.7                     | Broadcast Storm Control                            | 76       |

| 6.4.8                     | IPv4 IGMP Support                                  | 76       |

| 6.4.9                     | Port Mirroring                                     |          |

| 6.4.10                    | Host CPU Port Special Tagging                      | 77       |

| 6.4.10.1                  | Packets from the Host CPU                          | 77       |

| 6.4.10.2<br><b>6.4.11</b> | Packets to the Host CPU                            |          |

| 6.5                       | Buffer Manager (BM)                                |          |

| 6.5.1                     |                                                    |          |

| 6.5.1.1                   | Buffer Limits and Flow Control Levels              |          |

| 6.5.2                     | Random Early Discard (RED)                         |          |

| 6.5.3                     | Transmit Queues                                    | 79       |

| 6.5.4                     | Transmit Priority Queue Servicing                  | 79       |

| 6.5.5                     | Egress Rate Limiting (Leaky Bucket)                |          |

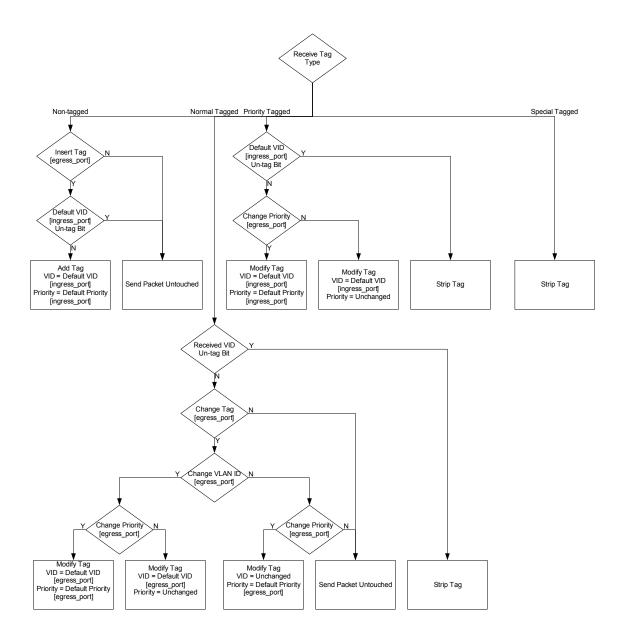

| 6.5.6                     | Adding, Removing, and Changing VLAN Tags           |          |

| 6.5.7                     | Counters                                           |          |

| 6.6                       | Switch Fabric Interrupts                           |          |

|                           |                                                    | _        |

| Chan                      | ter 7 Ethernet PHYs                                | 84       |

| 7.1                       | Functional Overview                                |          |

| 7.1.1<br>7.1.1            | PHY Addressing                                     |          |

| 7.1.1                     | Port 1 & 2 PHYs                                    |          |

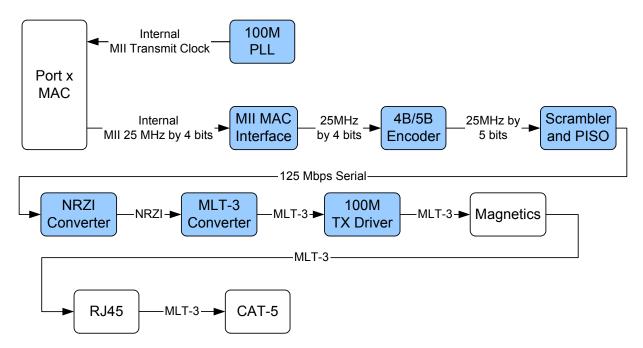

| 7.2.1                     | 100BASE-TX Transmit                                |          |

| 7.2.1.1                   | MII MAC Interface                                  |          |

| 7.2.1.2                   | 4B/5B Encoder                                      | 86       |

| 7.2.1.3<br>7.2.1.4        | Scrambler and PISO                                 |          |

| 7.2.1.5                   | 100M Transmit Driver                               |          |

| 7.2.1.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100M Phase Lock Loop (PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

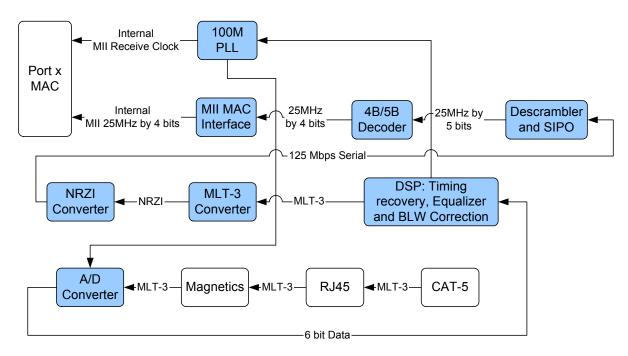

| 7.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 100BASE-TX Receive                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |

| 7.2.2.1<br>7.2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A/D Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |

| 7.2.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | NRZI and MLT-3 Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90                                          |

| 7.2.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Descrambler and SIPO                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| 7.2.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5B/4B Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                             |

| 7.2.2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Receiver Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |

| 7.2.2.7<br><b>7.2.3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MII MAC Interface                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10BASE-T Transmit                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| 7.2.3.1<br>7.2.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MII MAC Interface  10M TX Driver and PLL                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |

| 7.2.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10BASE-T Receive.                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |

| 7.2.4.1<br>7.2.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Filter and Squelch                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |

| 7.2.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MII MAC Interface                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| 7.2.4.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Jabber Detection                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |

| 7.2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PHY Auto-negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92                                          |

| 7.2.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PHY Pause Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94                                          |

| 7.2.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parallel Detection                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                             |

| 7.2.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Restarting Auto-Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

| 7.2.5.4<br>7.2.5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Disabling Auto-Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |

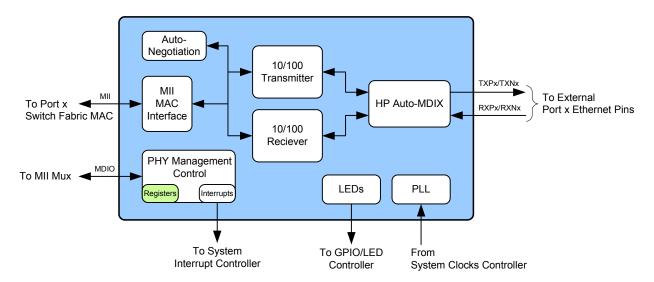

| 7.2.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HP Auto-MDIX                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                             |