#### **Features**

- DAVIC/DVB®/ETS300.429/ITU-T J.83 Annex A, C Fully Compliant

- Direct IF Sampling (No Second IF Down Conversion Required) or Baseband Input

- Internal DC Offset Compensation

- 1024, 512, 256, 128, 64, 32, 16 QAM and QPSK Demodulation

- Roll-off Factor Adapted to Raised-cosine Filtered Signal (0.11 to 0.4)

- Fully Digital Timing Recovery

- Variable Symbol Rate Recovery

- Anti-aliasing Continuously Variable Digital Filtering with Symbol Rate Adaptive Bandwidth (1 to 18.75M baud at the Same Sampling Frequency)

- Fully Digital Carrier Recovery (Coherent or Differential for QPSK)

- Robust Equalizer Acquisition

- Selectable Transversal or Decision Feedback Equalizer

- Dual Phase/Frequency Offset Recovery up to 12% of the Symbol Rate with No Degradation

- MPEG2 Frame Synchronization

- Reed-Solomon Decoder (204, 188, 8)

- De-interleaving (I = 12 and I = 17)

- Energy Dispersal Descrambling

- I<sup>2</sup>C Interface Switch for Separate Bi-directional I<sup>2</sup>C Bus-to-Tuner to Avoid Phase Noise Problems Due to I<sup>2</sup>

- Integrated Clock Reference for Tuner, Especially Designed for NIU in CAN

- Two AGCs: Analog and Digital Gains

- Three Program Identifier (PID) Filtering

- IRQ Interrupt Request Generation to Simplify Monitoring

- Bit Error Rate and Packet Error Rate Monitoring

- Signal-to-noise Ratio Estimation, Residual Phase Noise Estimation

- Automatic Spectrum Inversion

- JTAG Support

- 0.35 micron CMOS Technology, 3.3V Operation

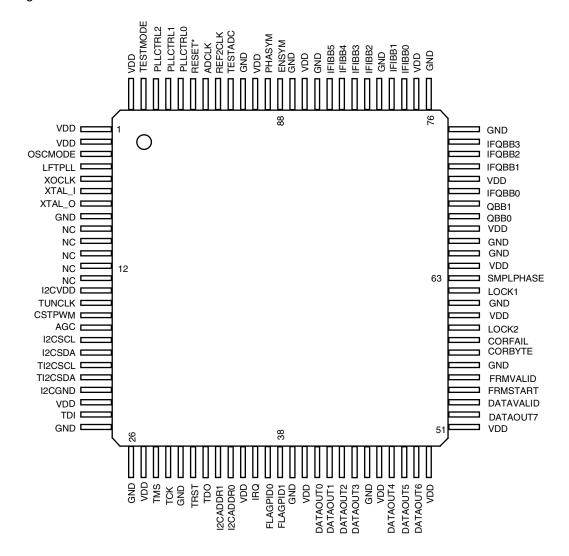

- 100-lead TQFP Package

# **Description**

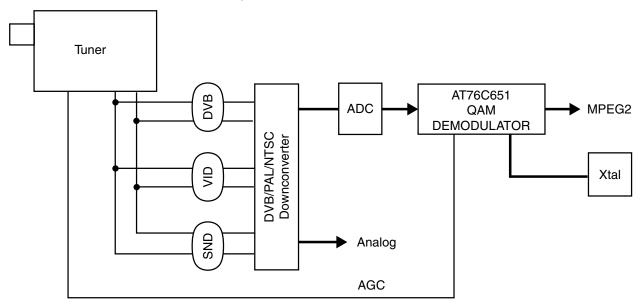

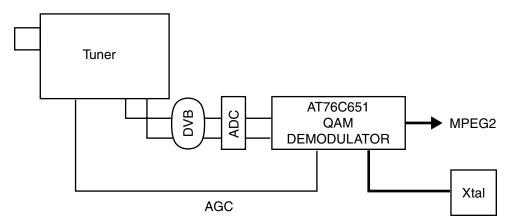

The AT76C651 is a DVB-compliant Quadrature Amplitude Modulation (QAM) demodulation circuit, which can be used in DVB and other applications using Quadrature Phase Shift Keying (QPSK) or QAM transmission systems. The signal, after output from tuner and adjacent channels rejection filter, is externally sampled at IF frequency.

The signal is converted to digital format by an analog-to-digital converter and goes through several processing steps required for demodulation: automatic gain control, baseband down conversion, timing recovery with anti-aliasing filtering, square root raised-cosine receive filtering, carrier recovery and digital gain control and equalization (linear and decision feedback dual structure). The output from demodulation then goes through forward error decoding: DVB/DAVIC de-mapping, frame synchronization, de-interleaving, Reed-Solomon decoding and spectrum de-randomization. The output before decoding may also be output directly for use with post-processing devices in applications other than DVB.

An additional block situated in the back-end may be used to filter out programmable PIDs, which provides additional flexibility in interactive solutions or DVB data-broad-cast PC receive cards. It is especially designed for modem implementations with a 24-bit mask on one PID (medium access control) and can be used for return channel implementation.

# Digital Reception/ Transmission IC Integrated DVBcompliant QAM Demodulator

AT76C651

Rev. 1293C-06/00

Figure 1. Symbol of the AT76C651 QAM Demodulator

Table 1. Signal Description

| Signal Name | Function                                                                       | Number of I/Os | Pull-up   | Voltage          | Direction |

|-------------|--------------------------------------------------------------------------------|----------------|-----------|------------------|-----------|

| I2CADDR     | I <sup>2</sup> C circuit address selection                                     | 2              | No        | $V_{DD3}$        | I         |

| I2CSDA      | SDA line of I <sup>2</sup> C                                                   | 1              | R = 15 kΩ | $V_{DD5}$        | I/O       |

| I2CSCL      | SCL line of I <sup>2</sup> C                                                   | 1              | No        | V <sub>DD5</sub> | I         |

| TI2CSDA     | I <sup>2</sup> C bus data line SDA to/from tuner through bi-directional switch | 1              | R = 15 kΩ | V <sub>DD5</sub> | I/O       |

| TI2CSCL     | I <sup>2</sup> C bus clock SCL to tuner through switch                         | 1              | No        | $V_{DD5}$        | 0         |

| IFIBB       | IF 6 MSBs or I-baseband digital input                                          | 6              | No        | V <sub>DD3</sub> | I         |

| IFQBB       | IF 4 LSBs or Q-baseband digital input 4 MSBs                                   | 4              | No        | V <sub>DD3</sub> | I         |

| QBB         | Q-baseband digital input (2 LSBs)                                              | 2              | No        | $V_{DD3}$        | I         |

| PLLCTRL     | PLL division/bypass control                                                    | 3              | No        | V <sub>DD3</sub> | I         |

| XOCLK       | Crystal oscillator input                                                       | 1              | No        | V <sub>DD3</sub> | I         |

| XTAL_I      | Crystal input                                                                  | 1              | No        | $V_{DD3}$        | I         |

| XTAL_O      | Crystal output                                                                 | 1              | No        | $V_{DD3}$        | 0         |

| OSCMODE     | Oscillator input mode (0 for crystal, 1 for XO)                                | 1              | No        | V <sub>DD3</sub> | I         |

| LFTPLL      | Low pass filter input to PLL                                                   | 1              | No        | $V_{DD3}$        | Α         |

| TESTADC     | A/D test pin (must be connected to VDD3 in standard operation)                 | 1              | No        | $V_{DD3}$        | I         |

| ADCLK       | Sampling clock for external A/D converter                                      | 1              | No        | V <sub>DD3</sub> | 0         |

| SMPLPHASE   | External A/D sampling phase                                                    | 1              | No        | $V_{DD3}$        | I         |

| TDI         | JTAG                                                                           | 1              | No        | $V_{DD3}$        | I         |

| TDO         | JTAG                                                                           | 1              | No        | V <sub>DD3</sub> | 0         |

| TMS         | JTAG                                                                           | 1              | No        | V <sub>DD3</sub> | I         |

| TCK         | JTAG                                                                           | 1              | No        | $V_{DD3}$        | I         |

| TRST        | JTAG                                                                           | 1              | No        | V <sub>DD3</sub> | I         |

| DATAOUT     | MPEG2-TS parallel byte <0:7> or serial bit stream output <0>                   | 8              | No        | $V_{DD3}$        | 0         |

| CORFAIL     | RS packets not corrected                                                       | 1              | No        | $V_{DD3}$        | 0         |

| CORBYTE     | Corrected byte indicator                                                       | 1              | No        | V <sub>DD3</sub> | 0         |

| DATAVALID   | MPEG2-TS byte or bit output enable active at level 0 or on both edges          | 1              | No        | $V_{DD3}$        | 0         |

| FRMSTART    | Start of MPEG2-TS frame                                                        | 1              | No        | V <sub>DD3</sub> | 0         |

| FRMVALID    | Valid MPEG2-TS frame control in parallel mode output                           | 1              | No        | $V_{DD3}$        | 0         |

| FLAGPID     | PID filtering indicator                                                        | 2              | No        | V <sub>DD3</sub> | 0         |

| IRQ         | Interrupt request                                                              | 1              | No        | V <sub>DD3</sub> | 0         |

| LOCK1       | Maskable lock signal 1                                                         | 1              | No        | $V_{DD3}$        | 0         |

| LOCK2       | Maskable lock signal 2                                                         | 1              | No        | $V_{DD3}$        | 0         |

| CSTPWM      | Configurable value output with PWM                                             | 1              | No        | V <sub>DD5</sub> | 0         |

| AGC         | Analog automatic gain control PWM                                              | 1              | No        | $V_{DD5}$        | 0         |

| TUNCLK      | 4 MHz reference oscillator output to tuner                                     | 1              | No        | $V_{DD5}$        | 0         |

| REF2CLK     | Half digital clock                                                             | 1              | No        | $V_{DD3}$        | 0         |

| PHASYM      | Test output signal                                                             | 1              | No        | V <sub>DD3</sub> | 0         |

| ENSYM       | Test output signal                                                             | 1              | No        | V <sub>DD3</sub> | 0         |

Table 1. Signal Description (Continued)

| Signal Name | Function                      | Number of I/Os | Pull-up | Voltage          | Direction |

|-------------|-------------------------------|----------------|---------|------------------|-----------|

| GND         | Ground                        |                |         |                  | GND       |

| I2CGND      | I <sup>2</sup> C ground       |                |         |                  | GND       |

| VDD         | +3.3V supply                  |                |         | V <sub>DD3</sub> | PWR       |

| I2CVDD      | I <sup>2</sup> C power supply |                |         | V <sub>DD5</sub> | PWR       |

| TESTMODE    | Test pin                      | 1              | No      | V <sub>DD3</sub> | I/O       |

| RESET       | Hard reset of circuit         | 1              | No      | V <sub>DD3</sub> | 1         |

Figure 2. Block Diagram of the AT76C651

## **Functional Description**

The following sections describe the main functions of all blocks included in the AT76C651 QAM demodulation IC.

#### Interface to A/D Converter (ADC)

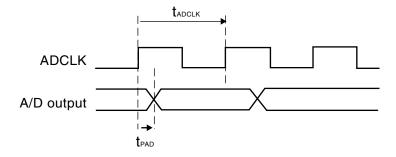

A 10-bit external A/D converter must be connected to the AT76C651 in case of a signal in IF frequency. The sampling clock of the ADC must be taken on pin ADCLK of the chip. The digital outputs of the external ADC must connect input IFIBB5 to IFIBB0 and input IFQBB3 to IFQBB0 (MSB to LSB). The pin SAMPLEPHASE can be used to select the phase of the internal resampling clock, depending on the external ADC propagation delay (see "Timing Waveforms" on page 35).

In case of a signal in baseband, two external 6-bit ADCs must be used. The sampling clock of the ADCs must be taken on pin ADCLK of the chip. The digital outputs of the ADCs must connect input IFIBB5 to IFIBB0 for I input and input IFQBB3 to IFQBB0 and QBB1 to QBB0 for Q input (MSB to LSB). SAMPLEPHASE should be connected as decribed in the previous paragraph.

The sampling clock frequency (on ADCLK) is equal to the input frequency if the PLL is used (either with a crystal or a crystal oscillator XO) or half the crystal frequency if the PLL is bypassed (see "Oscillator and Phase Locked Loop" on page 7). Two examples: If a 28 MHz crystal is used, the sampling frequency is 28 MHz; if a 60 MHz XO is used, the sampling frequency is 30 MHz.

#### DC Offset Control

An internal DC-offset compensation is done on the I and Q baseband signals in order to compensate potential offsets created by A/D converters.

# Direct Digital Synthesizer (DDS) – Coarse Tuning

An IF to baseband conversion from  $F_O$  is then performed. The frequency  $F_O$  is configurable, which reduces the constraint on the relation between the SAW filter center frequency and the chip oscillator. The frequency of the DDS is further adjusted by the carrier frequency recovery in order to adjust exactly the received spectrum to the receive filter.

# "Analog" Automatic Gain Control (AGC1)

The signal level at the ADC input is adjusted through a first AGC loop. The power estimation block estimates the signal level at the output of the ADC, compares it to a given level and generates a Pulse Width Modulation (PWM) signal,

which controls the analog gain. The PWM output generates a very stable control. Since power estimation is done by digital loop control, only the output is given in PWM format for simpler implementation on board (only an RC filter with about 1kHz cut-off bandwidth is required), whose frequency is  $f_{PWM} = f_{REF}/2$ . The power estimation is made over the entire signal sampled by the ADC, thus including the adjacent channels and the target signal. This ensures that no analog saturation can happen due to the AGC feedback.

Also, the power estimation of the analog gain control can be used in conjunction with the AGC2 level (which indicates the power of the QAM signal only) in order to compute the power of adjacent channels. This may be used to adjust the takeover point (TOP) of external amplifiers when several amplifiers are required on the board (typically in the tuner and after the SAW filter). Note that an I<sup>2</sup>C-controllable PWM is available for this purpose.

#### **Digital Timing Recovery**

The baseband conversion output is then fed to the timing recovery block. This block integrates a digital timing loop, which estimates the best resampling time. This information is provided to a time-continuous filter, which interpolates the baseband signal and produces QAM symbols at the recovered symbol rate.

The interpolating filter's main property is its continuously autoadaptive bandwidth, which allows the demodulator to recover a wide range of symbol rate  $1/T_{\rm S}$ , with the same perfomance, and avoids signal aliasing during resampling operation.

# **Square Root Raised-cosine Nyquist Receive** Filter (SRRC)

The SRRC filter, with roll-off factor allowing demodulation of raised-cosine transmitted signals from 0.11 to 0.4, receives the signal from the timing recovery output and ensures an out-of-band rejection higher than 43 dB. This significant rejection increases the back-off margin of the receiver against adjacent channels.

## **Digital Automatic Gain Control (AGC2)**

The internal digital AGC performs a fine adjustment of the signal level at the equalizer input. This AGC only takes into account the QAM signal itself, since adjacent channels have been filtered out by the SRRC, and thus compensates digitally the analog AGC, which may have reduced the input power due to adjacent channels.

#### **Equalizer**

The equalizer is based on algorithms that provide blind and robust acquisition. The equalizer compensates for the different impairments encountered on the network. Two equalizer structures can be selected: transversal (powerful for long echoes) or decision feedback (powerful for strong short echoes).

The equalizer central tap position is configurable. This allows an optimal compensation for post and pre-cursor echoes. The equalizer comprises 32 taps, which represents a length of about 6.2 microseconds at 5M bauds. This allows a large compensation for echoes with significant delays, and a total compensation for significant (small attenuation) short echoes.

#### **Carrier Recovery – Fine Tuning**

The carrier recovery block allows the acquisition and tracking of a frequency offset as high as 12% of the symbol rate, even for low signal-to-noise ratios. The phase comparator algorithm provides a high-phase noise tolerance, which reduces the tuner cost. The frequency offset recovered by the chip can be monitored through the I<sup>2</sup>C interface. This information can be used to readjust the tuner frequency in order to reduce the analog filtering degradation on the signal and thus improves the bit error rate. This information is also provided automatically to the DDS in order to recover the frequency with complete accuracy before receive filtering.

#### Differential Demodulation for QPSK

A differential demodulation can be used in strongly distorted environment in the case of differentially encoded QPSK demodulation. This mode provides a stronger robustness against phase noise but reduces the performance of the receiver by 3 dB, as shown in theory. I<sup>2</sup>C register QAMSEL must be configured to set this mode.

#### **Phase and Additive Noise Estimation**

Phase noise and additive noise estimations are performed. This information can be used to select the best carrier loop bandwidth giving the best trade-off between phase noise and additive noise. The phase noise can come from the tuner and/or the LNB in MMDS application. This feature can also be used to remotely monitor the various problems encountered by an STB or cable modem at the user installation.

# Symbol Detection and DVB/DAVIC Demapping

The output is fed to the symbol threshold detector, then to the differential decoder and finally to the DVB or DAVIC demapper, which produces the recovered bit stream sent to the Forward Error Correction (FEC).

#### Frame Synchronization

The first function performed by the FEC is the frame synchronization. The bit stream is decomposed into packets of 204 bytes at the output, starting with a frame synchronization word.

#### **De-interleaving**

The packets are then de-interleaved. Two depths can be selected for the interleaver: 12 (DVB/DAVIC) and 17. The depth 17 increases the robustness of the system against impulse noise but assumes the signal has been interleaved with the same value as the modulator.

#### **Reed-Solomon Decoder**

The de-interleaved output is sent to the Reed-Solomon (RS) input, which performs a correction of a maximum of eight errors (bytes) per packet. The RS also provides other information regarding the uncorrected packets and the position of the corrected bytes in the packet, if there are any.

#### Spectrum Descrambler

After RS decoding, the packets are descrambled for energy dispersal removal.

#### **PID Filtering**

A Program Identifier (PID) filtering can be performed on the MPEG2 Transport Stream (TS) before feeding the packets to the output. Three PIDs can be selected at the same time. This block outputs an enable signal on the packet stream that goes to the component interfaced with the QAM demodulator. This provides an interesting feature for onboard PC implementations, where either data or video and audio are processed directly by the PC processor. A mask is provided for one of the PIDs, offering a filter on the overall MPEG-TS packet header.

Note that one of the PIDs can be selected, so that a special enable output can be used to filter out all MPEG-TS packets containing MAC messages (for in-band return channel implementations of the DVB-RC specification). This stream contains all the control information for the return channel, and is required by other components used for the return channel.

## **Interrupt Request (IRQ)**

An interrupt request can be generated by the AT76C651 device when configurable events occur. This is controlled by the I<sup>2</sup>C registers IRQMASK and OUTPUTCFG.

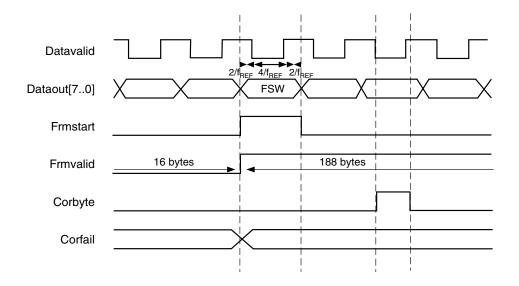

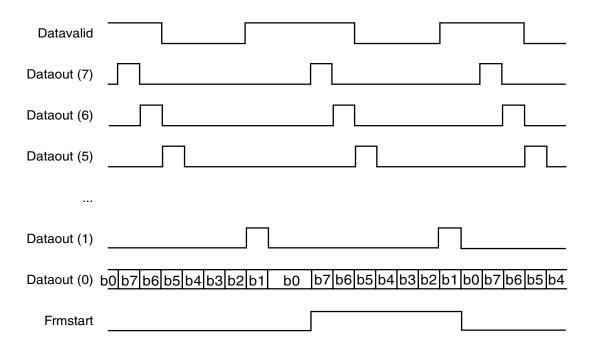

## **MPEG2-TS Output Interface**

The output of the FEC is made up of MPEG2 Transport Stream (TS) packets. The output can be either parallel or serial on DATAOUT. The data is present on either edge or low state of the DATAVALID pin in output mode. In serial output mode DATAOUT (7) to DATAOUT (1) are individually valid, with each bit output in serial mode (see "Timing Waveforms" on page 35).

#### **Oscillator and Phase Locked Loop**

The fully digital clock and carrier recovery eliminates the need to implement external VCOs and VCXOs and thus reduces the total function cost. Only a simple crystal oscillator is needed by the chip to perform all the demodulation functions with variable symbol rate.

Two configurations are possible:

A crystal can be connected to the XTAL\_I and XTAL\_O pins of the chip with frequency:

25 MHz

$$\leq f_{XTAL} \leq$$

30 MHz

Values may depend on crystal characteristics.

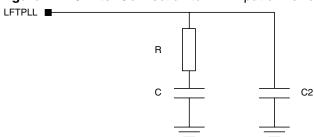

See Figure 3, where R = 12 kOhms and C = 20 pF.

Figure 3.

2. A crystal oscillator (XO) can be connected directly to the XOCLK input pin, with frequency:

$$f_{XTAL} \le 80 \text{ MHz}$$

In case of a crystal, the OSCMODE pin is connected to GND. In case of an XO, it must be connected to  $V_{\text{DD}}$ .

The crystal must be first order, serial resonance and have a load capacitance of 10 pF.

The internal oscillator of the chip provides a direct, jitterfree clock used to sample the input signal of external ADC. This clock is available on the output pin ADCLK.

The internal reference clock of the chip is generated by using an internal PLL and its frequency is given by:

$$f_{REF} = \frac{n}{2} f_{XTAL}$$

with  $n = 2, 4, 5, 6, 7$

The frequency  $f_{REF}$  is the maximum output bit rate supported by the device and must be less than 80 MHz (see "Symbol Rate" on page 13). The value n is configured by the PLLCTRL2, PLLCTRL1 and PLLCTRL0 input pins, as shown in Table 2.

Table 2.

|       | PLLCTRL2 | PLLCTRL1 | PLLCTRL0 |

|-------|----------|----------|----------|

| n = 2 | 1        | 0        | 0        |

| n = 4 | 0        | 0        | 0        |

| n = 5 | 0        | 0        | 1        |

| n = 6 | 0        | 1        | 0        |

| n = 7 | 0        | 1        | 1        |

Note: Other cases for test only.

The value n = 2 allows to input directly the reference clock at frequency  $f_{REF}$  (bypass the PLL).

The PLL pin LFTPLL must be connected to an RC filter as shown in Figure 4. Values of resistance and capacitors should be R =  $25\Omega$ , C = 100 nF, and C2 = 20 nF.

Figure 4. RC Filter Connection to PLL Input of Device

A separate TUNCLK output pin provides a fraction of the crystal frequency given by:

$$f_{TUNCLK} = \frac{1}{p} f_{XTAL}$$

with  $p = 2, 4, 8$

which can be used as a reference for the tuner oscillator or any other reference frequency on the board. The value p is configured by the I<sup>2</sup>C register, OUTPUTCFG (page 23).

#### **JTAG**

A JTAG controller compatible with IEEE Std. 1149.1 is provided in the device. The pin TRST must be connected to a pull-down on the board in order to have it connected to GND during functional operation of the chip. The JTAG provides a boundary scan chain on the pinout of the chip. The following instructions are available:

- BYPASS: The chip remains in functional mode and a single BYPASS register is connected between TDI and TDO. The bit code of this instruction is 11.

- SAMPLE/PRELOAD: The chip remains in functional mode and the boundary-scan register is connected between TDI and TDO. The bit code of this instruction is 01.

- EXTEST:The chip is in external boundary-test mode and the boundary-scan register is connected between TDI and TDO. The bit code of this instruction is 00.

- IDCODE: The chip is in functional mode and the device identification register is connected between TDI and TDO. The bit code of this instruction is 10.

The device identification register is 32 bits long and contains the value 0x00280B8F.

#### Special I/O Description

Special I/Os that are not described elsewhere in this specification are described in this section.

- OSCMODE: When set to 1, a crystal oscillator is used.

When set to 0, a crystal is used.

- TEST: Three test pins are available on the chip for testing.

- 1. TESTMODE: Input test pin, connected to GND

- 2. PHASYM: Output test pin, not connected

- 3. ENSYM: Output test pin, not connected

- · REF2CLK: Clock output test pin, not connected

#### I<sup>2</sup>C Control

The chip is controlled entirely via an  $I^2C$  interface. The chip address can be modified by connecting the I2CADDR pins to GND or  $V_{DD3}$  to select the two LSBs of the address. The chip address is:

| ( | ) | 0 | 0 | 1 | 1 | ADDI2C(1) | ADDI2C(0) |

|---|---|---|---|---|---|-----------|-----------|

|---|---|---|---|---|---|-----------|-----------|

#### I<sup>2</sup>C Write Mode

Registers can be written using a standard  $I^2C$  bus with clock SCL and data SDA as described by "The  $I^2C$ -bus and how to use it", Philips Semiconductors (April 1995). The protocol used to write into  $I^2C$  registers is described by the frame shown below.

| S            | chip address          | 0 (Write) | Α       | register address | Α                                      | data 1 | Α     | •••       | data n                                                           | Α | Р |

|--------------|-----------------------|-----------|---------|------------------|----------------------------------------|--------|-------|-----------|------------------------------------------------------------------|---|---|

| <b>A</b> = . | Start Acknowledge bit |           | to chip |                  | data 1 is written<br>data 2 is written |        | •     |           |                                                                  |   |   |

| <b>)</b> = ( | Stop                  |           |         | from chip        | •<br>It                                |        | sible | to config | nddress + (n - 1)<br>gure several succe<br>from first Start to S |   |   |

#### I<sup>2</sup>C Read Mode

Register values can be read from the chip by transmitting the following frames on the I<sup>2</sup>C bus.

| S | chip address | 0 (Write) | Α | register addre | ss | Α | S | chip | p address | 1 (Read) | Α | da | ata X1 | Α |  |

|---|--------------|-----------|---|----------------|----|---|---|------|-----------|----------|---|----|--------|---|--|

|   |              |           |   |                |    |   |   |      |           |          |   |    |        |   |  |

|   |              |           |   |                |    |   |   |      |           |          |   |    |        |   |  |

- data X1 is read from register address

- data X2 is read from register address + 1

- ..

- data Xn is read from register address + (n 1)

It is therefore possible to read from several successive registers with a single I<sup>2</sup>C frame (from first Start to Stop). Note that multiple byte registers must be read MSB/low address first. All LSBs of the complete data are memorized only at the time when MSBs are read and do not change during readings of LSBs.

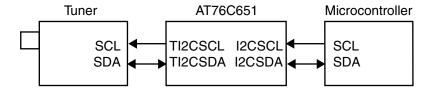

#### Switch for Tuner I<sup>2</sup>C Bus

In order to avoid phase noise created by the  $I^2C$  bus on the tuner, an active bi-directional switch provides a separate  $I^2C$  bus for tuner configuration.

For this purpose, the  $I^2C$  bus to the tuner must be connected to the AT76C651 TI2CSCL and TI2CSDA pins (see Figure 1). The  $I^2C$  register called TUNI2CADD (see  $I^2C$  registers table) must be configured with the  $I^2C$  address of the tuner. The switch between the normal  $I^2C$  bus and the tuner  $I^2C$  bus can be enabled or disabled using the LSB of TUNI2CADD.

When disabled, TI2CSCL/TI2CSDA lines are isolated from I2CSCL/SI2CDA.

When enabled, the switch copies I2CSDA to/from TI2CSDA when data is transmitted to/from the tuner. The switch should be enabled by the microcontroller only when the tuner is being configured.

Figure 5. I<sup>2</sup>C Connection between AT76C651, Tuner and Microcontroller

## **Automatic Configuration**

In order to configure the chip, the following actions are required:

- · Hard reset of chip

- Configure registers SYMRATE (symbol rate), QAMSEL (QAM modulation type) and BBFREQ (IF frequency)

- Write value 0x01 into SETAUTOCFG in order to automatically configure all other registers

- · Optionally modify some register values, if required

- Write value 0x01 into RESTART in order to restart the chip with the new values

The automatic configuration of all registers as a function of the QAM modulation, symbol rate and IF frequency offers a very simple use of the chip with a basic software driver.

**Table 3.** I<sup>2</sup>C Registers List

| Address         | R/W          | Name & Function | Meaning                                                                       |

|-----------------|--------------|-----------------|-------------------------------------------------------------------------------|

| General         |              | <u>'</u>        |                                                                               |

| 0x00 to 0x02    | W/R          | SYMRATE         | Symbol rate                                                                   |

| 0x03            | W/R          | QAMSEL          | QAM selection (and mapping type, DVB and others)                              |

| 0x04 - 05       | W/R          | BBFREQ          | IF input frequency                                                            |

| 0x06            | W            | SETAUTOCFG      | Sets automatic configuration of all parameters (see Note)                     |

| 0x07            | W            | RESTART         | Restart chip without modifying configuration parameters                       |

| 0x08*           | W/R          | OUTPUTCFG       | Select MPEG2 or other internal signals for test output                        |

| 0x09*           | W/R          | MASKLOCK1       | Mask for lock 1 signal output                                                 |

| 0x0A*           | W/R          | MASKLOCK2       | Mask for lock 2 signal output                                                 |

| 0x0B*           | W/R          | IRQMASK         | Events mask for interrupt request generation                                  |

| 0x0C*           | W/R          | TUNI2CADD       | Tuner I <sup>2</sup> C address for use of specific tuner I <sup>2</sup> C bus |

| 0x0E - 0x0F     | R            | CHIPID          | Chip ID and version                                                           |

| Baseband Conv   | ersion and A | GC1             |                                                                               |

| 0x13*           | W/R          | AGC1NMIN        | Minimum value authorized for AGC value                                        |

| 0x14*           | W/R          | AGC1NMAX        | Maximum value authorized for AGC value                                        |

| 0x15*           | W/R          | BBCFG           | General configuration of baseband block                                       |

| 0x17*           | W/R          | CSTPWM          | Constant value for PWM output                                                 |

| 0x19            | R            | BBTOPCNT        | A/D saturation rate over 16384 successive samples                             |

| Timing Recover  | у            | <u>'</u>        |                                                                               |

| 0x23 - 0x24*    | W/R          | TIMLOOPCFG      | Configuration of initial loop parameters                                      |

| 0x29            | R            | TIMLOOPMONIT    | Variable loop bandwidth value                                                 |

| Carrier Recover | у            |                 |                                                                               |

| 0x31*           | W/R          | CARALPHAACQ     | Alpha parameter of loop bandwidth during acquisition phase of carrier         |

| 0x32*           | W/R          | CARBETAACQ      | Beta parameter of loop bandwidth during acquisition phase of carrier          |

| 0x33*           | W/R          | CARALPHATRACK   | Alpha parameter of loop bandwidth during tracking phase of carrier            |

| 0x34*           | W/R          | CARBETATRACK    | Beta parameter of loop bandwidth during tracking phase of carrier             |

| 0x39 - 0x3B     | R            | CARCONST        | Constellation points after carrier recovery                                   |

| AGC2            |              |                 |                                                                               |

| 0x42*           | W/R          | AGC2CFG         | AGC2 configuration                                                            |

| 0x43 - 0x44*    | W/R          | AGC2INIT        | AGC2 initial value                                                            |

| Equalizer       |              |                 |                                                                               |

| 0x51*           | W/R          | EQUCFG          | Equalizer configuration                                                       |

| 0x52*           | W/R          | EQUCENTRAL      | Central tap configuration                                                     |

| 0x53*           | W/R          | EQUTAPTORD      | Coefficient to monitor                                                        |

|                 |              |                 | ·                                                                             |

Table 3. I<sup>2</sup>C Registers List (Continued)

| Address        | R/W   | Name & Function | Meaning                                                     |

|----------------|-------|-----------------|-------------------------------------------------------------|

| 0x54 - 0x55    | R     | EQUTAPREAL      | Real part of selected tap                                   |

| 0x56 - 0x57    | R     | EQUTAPIMAG      | Imaginary part of selected tap                              |

| FEC            |       |                 |                                                             |

| 0x60*          | W/R   | FECIQINV        | I/Q invert mode                                             |

| 0x61*          | W/R   | FECFLEN         | Frame length                                                |

| 0x62*          | W/R   | FECFSW          | Frame synchronization word                                  |

| 0x63*          | W/R   | FECDILVILEN     | Number of branches in interleaver                           |

| 0x64*          | W/R   | FECDILVMLEN     | Memory step size of interleaver                             |

| 0x65*          | W/R   | FECDINH         | FEC inhibitions configuration                               |

| PID Filtering  |       |                 |                                                             |

| 0x70 - 0x71*   | W/R   | PID1            | First PID filter                                            |

| 0x72 - 0x73*   | W/R   | PID2            | Second PID filter                                           |

| 0x74 - 0x76*   | W/R   | PID3            | Third MPEG-TS header filter                                 |

| 0x77 - 0x79*   | W/R   | PIDMSK3         | Mask for third MPEG-TS header filter                        |

| General Monito | oring |                 |                                                             |

| 0x80           | R     | LOCK            | Lock status of AGC1, AGC2, TIMING, CARRIER, EQUALIZER, FEC  |

| 0x81 - 0x83    | R     | BER1            | Bit error rate estimate                                     |

| 0x84           | R     | BER2            | Bit error rate estimate based on frame synchronization word |

| 0x85           | R     | NPERR           | Number of uncorrectable frames                              |

| 0x86 - 0x88    | R     | TIMFREQOFF      | Symbol rate frequency offset with respect to SYMRATE        |

| 0x89 - 0x8A    | R     | DDSFREQOFFSET   | Frequency offset recovered by DDS                           |

| 0x8B - 0x8C    | R     | CARFREQOFFSET   | Residual frequency offset (normalized to symbol rate)       |

| 0x8D - 0x8E    | R     | PHASENOISE      | Phase noise estimation                                      |

| 0x8F - 0x90    | R     | ADDITIVENOISE   | Additive noise estimation                                   |

| 0x91           | R     | AGC1LEVEL       | AGC1 current value (external)                               |

| 0x92 - 0x93    | R     | AGC2LEVEL       | AGC2 current value (internal)                               |

|                |       |                 |                                                             |

Note: All parameters identified by \* are automatically configured when writing 0x01 into SETAUTOCFG register.

# **Performance Specification**

#### Modulation

Supports QPSK and 16, 32, 64, 128, 256, 512, 1024 QAM.

#### **Roll-off Factor**

Greater than 0.11.

#### Symbol Rate

Up to  $f_{REF}/8$  (9.36M baud for  $f_{REF}=75$  MHz,  $f_{XTAL}=30$  MHz) with IF or baseband input, 32-taps equalizer.

Up to  $f_{XTAL}/(2(1 + \alpha))$  (13M baud for  $f_{REF}$  = 30 MHz,  $\alpha$  = 0.15) with IF input, 16-taps equalizer.

Up to  $f_{REF}/4$  (18.75M baud for  $f_{REF} = 75$  MHz,  $f_{XTAL} = 30$  MHz) with baseband input, 16-taps equalizer.

Note however, that the standard MPEG2-TS frame recovery and forward error correction part of the chip can only be used when bitrate  $\leq$  f<sub>REF</sub>. It is possible to use the constellation mode in the opposite case in order to use the demodulation part of the chip only and receive the symbols at the output. (See OUTPUTCFG register I²C to configure this operating mode.)

Table 4.

| Bandwidth | f <sub>XTAL</sub> = f <sub>ADCLK</sub> | DDS freq        | n (CTRLPLL) | f <sub>REF</sub> | Dsym_max           |

|-----------|----------------------------------------|-----------------|-------------|------------------|--------------------|

| 6 MHz     | 25 MHz                                 | 2x25-44 = 6 MHz | 4           | 50 MHz           | 50/8 = 6.25 Mbd    |

| 8 MHz     | 28.9 MHz                               | 36-28.9 = 7 MHz | 4           | 57.8 MHz         | 57.8/8 = 7.225 Mbd |

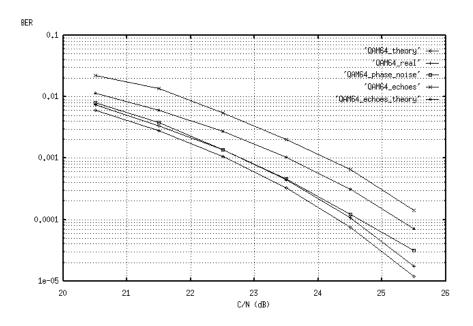

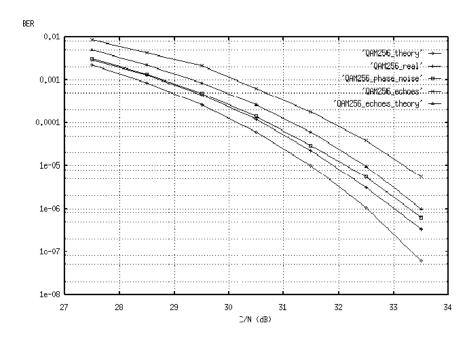

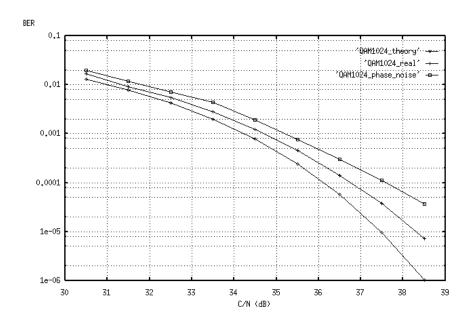

#### **Bit Error Rate**

Figures in the section "Bit Error Rate Measurements (Uncoded)" on page 20 indicate Bit Error Rate (BER) as a function of carrier-to-noise ratio (C/N) for different QAM modulations schemes. Theoretical curves are given to indicate how much degradation is observed with the real performance of the chip.

Table 5 indicates the degradation from theory (implementation margin) for uncoded QAM at BER =  $10^{-4}$ .

Table 5.

| Modulation Scheme | C/N Degradation at BER = 10 <sup>-4</sup> |

|-------------------|-------------------------------------------|

| QPSK              | 0.1 dB                                    |

| QAM-16            | 0.2 dB                                    |

| QAM-32            | 0.2 dB                                    |

| QAM-64            | 0.2 dB                                    |

| QAM-128           | 0.3 dB                                    |

| QAM-256           | 0.4 dB                                    |

| QAM-512           | 0.5 dB                                    |

| QAM-1024          | 0.7 dB                                    |

#### **Echo Cancellation**

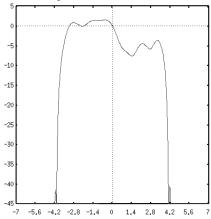

Table 6 indicates the additional degradation between use of a theoretical equalizer and the real chip equalizer, for uncoded QAM at BER =  $10^{-4}$ , when the channel has the transfer response shown in Figure 6.

Table 6.

| Modulation Scheme | C/N Degradation at BER = 10 <sup>-4</sup> |

|-------------------|-------------------------------------------|

| QPSK              | 0.3 dB                                    |

| QAM-16            | 0.3 dB                                    |

| QAM-32            | 0.3 dB                                    |

| QAM-64            | 0.3 dB                                    |

| QAM-128           | 0.3 dB                                    |

| QAM-256           | 0.3 dB                                    |

| QAM-512           | 0.3 dB                                    |

| QAM-1024          | 0.4 dB                                    |

Figure 6. Received Spectrum Used to Measure Degradation with Echoes

#### **Phase Noise Tolerance**

Table 7 indicates the additional degradation when a phase noise of -80 dBc at 10 kHz is present after the tuner, for uncoded QAM at BER =  $10^{-4}$ .

Table 7.

| Modulation Scheme | C/N Degradation at BER = 10 <sup>-4</sup> |

|-------------------|-------------------------------------------|

| QPSK              | 0.1 dB                                    |

| QAM-16            | 0.1 dB                                    |

| QAM-32            | 0.1 dB                                    |

| QAM-64            | 0.1 dB                                    |

| QAM-128           | 0.1 dB                                    |

| QAM-256           | 0.1 dB                                    |

| QAM-512           | 0.3 dB                                    |

| QAM-1024          | 0.9 dB                                    |

#### **AM Hum Tolerance**

Input amplitude variation of 20% peak-to-peak can be supported by the demodulation at frequencies 100 - 120 Hz.

#### **Locking Time**

- 5 to 10 ms, when no echoes are present

- 20 ms typical when echoes are present (see Figure 6)

#### **Carrier Offset**

Up to 12% of the symbol rate: ± 1 MHz at 8M baud.

## **Timing Offset**

Up to 4000 ppm of the symbol rate (± 30 kHz at 8M baud).

# **Electrical Characteristics**

Table 8. Electrical Specification – Recommended Operating Conditions

| Symbol          | Parameter                                  | Conditions                     | Min       | Тур | Max | Unit |  |

|-----------------|--------------------------------------------|--------------------------------|-----------|-----|-----|------|--|

| $V_{DD5}$       | I2CVDD, I <sup>2</sup> C DC supply voltage | I <sup>2</sup> C and AGC1 I/Os | $V_{DD3}$ | 5   | 5.5 | V    |  |

| $V_{DD3}$       | VDD, DC supply voltage                     | Core and standard I/Os         | 3.0       | 3.3 | 3.6 | ٧    |  |

| V <sub>SS</sub> | GND, I2CGND                                |                                |           | 0   |     | ٧    |  |

| TEMP            | Operating free air temperature range       | Commercial                     | 0         |     | +70 | °C   |  |

Table 9. Absolute Maximum Ratings – Before Damage

| Symbol           | Parameter                            | Conditions             | Min  | Max                             | Unit |

|------------------|--------------------------------------|------------------------|------|---------------------------------|------|

| V <sub>DD3</sub> | DC supply voltage                    | Core and standard I/Os | -0.3 | 4.6                             | V    |

| V <sub>I</sub>   | DC input voltage, 3.3V I/Os          |                        | -0.3 | V <sub>DD3</sub> + 0.3, 4.6 max | V    |

|                  | DC input voltage, 5V I/Os            |                        | -0.3 | V <sub>DD5</sub> + 0.3, 5.5 max | V    |

| Vo               | DC output voltage, 3.3V I/Os         |                        | -0.3 | V <sub>DD3</sub> + 0.3, 4.6 max | V    |

|                  | DC output voltage, 5V I/Os           |                        | -0.3 | V <sub>DD5</sub> + 0.3, 5.5 max | V    |

| TEMP             | Operating free air temperature range | Commercial             | 0    | +70                             | °C   |

Table 10. DC Characteristics for Pins Using VDD3 – CMOS Technology

| Symbol          | Parameter                 | Conditions                    | VDD              | Min                     | Max                     | Unit |

|-----------------|---------------------------|-------------------------------|------------------|-------------------------|-------------------------|------|

| TEMP            | Temperature               |                               |                  | 0                       | +70                     | °C   |

| V <sub>IL</sub> | Low-level input voltage   | Guaranteed input low voltage  | 3.0 to 3.6       | -0.3                    | 0.3 x V <sub>DD3</sub>  | V    |

| V <sub>IH</sub> | High-level input voltage  | Guaranteed input high voltage | 3.0 to 3.6       | +0.7 x V <sub>DD3</sub> | V <sub>DD3</sub> + 0.1V | V    |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>OL</sub> = 0.3mA       | 3.0              |                         | V <sub>SS</sub> + 0.1V  | V    |

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = 0.3mA       | 3.0              | V <sub>DD3</sub> - 0.1  |                         | V    |

| Cı              | Input capacitance         |                               | V <sub>DD3</sub> |                         | 6 (typ)                 | pF   |

Table 11. DC Characteristics for Pins Using VDD5

| Symbol          | Parameter                 | Conditions                    | Min                    | Max                    | Unit |

|-----------------|---------------------------|-------------------------------|------------------------|------------------------|------|

| V <sub>IL</sub> | Low-level input voltage   | Guaranteed input low voltage  | -0.3                   | +0.8                   | V    |

| V <sub>IH</sub> | High-level input voltage  | Guaranteed input high voltage | 2.0                    | V <sub>DD5</sub> + 0.3 | V    |

| V <sub>OL</sub> | Low-level output voltage  | $I_{OL} = 2mA$                |                        | 0.4                    | V    |

| V <sub>OH</sub> | High-level output voltage | I <sub>OH</sub> = 2mA         | V <sub>DD5</sub> - 0.4 |                        | V    |

# **Schematic Diagrams**

Figure 7. Standard Use of AT76C651 in Set Top Box Front End

Figure 8. Simplified Use of AT76C651 when No Analog TV Demodulation Required

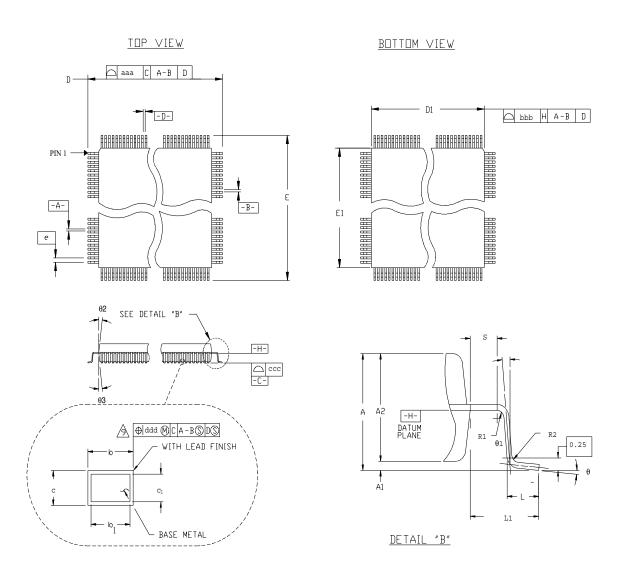

#### **Packaging Information**

100-lead TQFP package.

Commercial temperatures: 0 to 70°C.

Thermal resistance of the package: 40°C/W.

Figure 9. Package Outline

Note: The I/Os located between pins I2CVDD (14) and I2CGND (22) must use  $V_{DD5}$  voltage. All other I/Os must use  $V_{DD3}$  voltage.

Figure 10. 100-lead TQFP Package

Table 12. Lead Count Dimensions (mm)

| Pin   | D/E  | D1/E1 | b    |      |      | b1   |     |      |       |      |      |

|-------|------|-------|------|------|------|------|-----|------|-------|------|------|

| Count | BSC  | BSC   | Min  | Nom  | Max  | Min  | Nom | Max  | e BSC | ccc  | ddd  |

| 100   | 16.0 | 14.0  | 0.17 | 0.22 | 0.27 | 0.17 | 0.2 | 0.23 | 0.50  | 0.10 | 0.06 |

Table 13. Common Dimensions (mm)

| Symbol        | Min                             | Nom      | Max  |  |  |  |  |  |

|---------------|---------------------------------|----------|------|--|--|--|--|--|

| С             | 0.09                            |          | 0.2  |  |  |  |  |  |

| c1            | 0.09                            |          | 0.16 |  |  |  |  |  |

| L             | 0.45                            | 0.6      | 0.75 |  |  |  |  |  |

| L1            |                                 | 1.00 REF |      |  |  |  |  |  |

| R2            | 0.08                            |          | 0.2  |  |  |  |  |  |

| R1            | 0.08                            |          |      |  |  |  |  |  |

| S             | 0.2                             |          |      |  |  |  |  |  |

| q             | 0°                              | 3.5°     | 7°   |  |  |  |  |  |

| θ1            | 0°                              |          |      |  |  |  |  |  |

| θ2            | 11°                             | 12°      | 13°  |  |  |  |  |  |

| θ3            | 11°                             | 12°      | 13°  |  |  |  |  |  |

| Α             |                                 |          | 1.6  |  |  |  |  |  |

| A1            | 0.05                            |          | 0.15 |  |  |  |  |  |

| A2            | 1.35                            | 1.4      | 1.45 |  |  |  |  |  |

| Tolerances of | Tolerances of Form and Position |          |      |  |  |  |  |  |

| aaa           |                                 | 0.2      |      |  |  |  |  |  |

| bbb           |                                 | 0.2      |      |  |  |  |  |  |

# **Bit Error Rate Measurements (Uncoded)**

Figure 11. QAM-64

**Figure 12.** QAM-256

Figure 13. QAM-1024

# **Configuration and Monitoring Registers**

## Description

The AT76C651 device is controlled by an I<sup>2</sup>C interface. Most internal registers are in read/write mode (configuration registers). However, monitoring registers are in readonly mode. Note also that two special registers are write-only: SETAUTOCFG and RESTART. In most applications, very few of these registers need to be configured since the SETAUTOCFG can be used. Some registers are not described in this document. They are used internally and should not be written with a different value after SETAUTOCFG; otherwise performance degradation may result. This means that no other address than the ones specified in this document should be used in I<sup>2</sup>C write mode. Also, reserved bits in a register should always be written with the value 0.

#### **General Registers**

#### SYMRATE: 0x00 to 0x02 (read/write)

Transmission symbol rate,  $f_{SYMBOL}$ , registers give the initial symbol rate of the timing recovery algorithm. A maximum offset of 4000 ppm between the actual symbol rate and this value can be tolerated by the device. The internally compensated frequency offset can be monitored in the register TIMFREQOFF.

The symbol rate is given as a fraction of the REFCLK frequency. The value must be given with a mantissa (21 bits) and an exponent (3 bits).

|      | b7 | b6              | b5 | b4     | b3      | b2    | b1       | b0   |  |  |

|------|----|-----------------|----|--------|---------|-------|----------|------|--|--|

| 0x00 |    |                 |    | manti  | ssa (20 | ):13) |          |      |  |  |

| 0x01 |    | mantissa (12:5) |    |        |         |       |          |      |  |  |

| 0x02 |    |                 | ma | ntissa | (4:0)   | ехро  | onent (2 | 2:0) |  |  |

To compute these values, the following equations can be used:

$$f_{REF} = \left(\frac{f_{XTAL}}{2}\right)pllctrl$$

with  $pllctrl = 2,4,5,6,7$

$$exponent = 10 + floor \left( log_2 \left( \frac{f_{symbol}}{f_{REF}} \right) \right)$$

$$mantissa = \left(\frac{f_{symbol}}{f_{REF}}\right) 2^{30 - exponent}$$

#### Example:

For a 30 MHz crystal and pllctrl = 5,  $f_{REF} = 75 \text{ MHz}$

A symbol rate of 5M bauds gives:

exponent = 6 (0x6)

mantissa = 1 118 481(0 x 11 11 11)

So the register value is 0x 88 88 8E.

A symbol rate of 6.875M bauds gives:

exponent = 6 (0x6)

mantissa = 1 537 911(0 x 17 77 77)

So the register value is 0 x BB BB BE (default value).

#### QAMSEL: 0x03 (read/write)

Specifies the used modulation scheme. This register indicates the number of QAM levels and other parameters such as the used mapping type (DVB or others), whether coherent demodulation or differential demodulation is used for QPSK, and whether intermediate frequency (IF) or baseband (BB) input is used.

|      | b7         | b6         | b5 | b4   | b3 | b2  | b1   | b0 |

|------|------------|------------|----|------|----|-----|------|----|

| 0x03 | ifor<br>bb | dem<br>typ | ma | ptyp |    | qan | ntyp |    |

- iforbb: 0 for IF input signal, 1 for BB input signal

- demtyp: 0 for coherent demodulation, 1 for differential demodulation (in QPSK only)

- maptyp: 00 for DVB mapping, 10 for DAVIC mapping, other values reserved

- qamtyp: Number of bits to specify a QAM symbol.

Example:

2 for QPSK, 4 for QAM-16, 5 for QAM-32,

6 for QAM-64, 7 for QAM-128, 8 for QAM-256,

9 for QAM-512, 10 for QAM-1024 (0, 1, 3, and greater or equal to 11 are reserved values.)

#### BBFREQ: 0x04 to 0x05 (read/write)

Intermediate frequency to baseband-down conversion frequency registers indicate the initial frequency used to down-convert the signal from IF to BB. The value is between 0 and  $f_{ADCLK}/2$ , where  $f_{ADCLK}$  is the sampling frequency of the ADC. A maximum offset between the actual IF and this value of 12% of the symbol rate can be tolerated by this device. This offset can be monitored in the DDS-FREQOFFSET and CARFREQOFFSET registers.

|      | b7             | b6 | b5 | b4 | b3 | b2 | b1 | b0 |  |  |

|------|----------------|----|----|----|----|----|----|----|--|--|

| 0x04 | bbfreq1 (15:8) |    |    |    |    |    |    |    |  |  |

| 0x05 | bbfreq0 (7:0)  |    |    |    |    |    |    |    |  |  |

The frequency is computed by:

$$f_{IF} = \frac{bbfreq1 \times 256 + bbfreq0}{65536} \times f_{ADCLK}$$

#### Example:

For a 30 MHz crystal and a signal at IF frequency  $f_{IF} = 6$  MHz, bbfreq1 = 51 (0x33) and bbfreq0 = 51 (0x33).

Note also that subsampling can be used with this device. This means that the IF can be greater than the sampling frequency of the signal. For example, it is possible to have a sampling frequency  $f_{ADCLK}=30$  MHz, and the IF at  $f_{\rm IF}=36$  MHz. In that case, an image of the spectrum after sampling is present at  $f_{\rm IF2}=36$ - 30=6 MHz, thus the content of BBFREQ should correspond to  $f_{\rm IF2}$ .

#### **SETAUTOCFG: 0x06 (write-only)**

The automatic configuration address, when written with the value 0x01, automatically updates all registers of the device except for SYMRATE, QAMSEL and BBFREQ, which remain the same. All values are derived from these non-modified registers, thus offering a very straightforward configuration of the entire device without necessarily understanding the meaning of all other parameters. However, if necessary, it is possible to modify some register values after having used SETAUTOCFG.

In order to optimize the performance of the IC, the following values must be written into the IC after SETAUTOCFG has been performed.

| Register | Value |

|----------|-------|

| 0x10     | 0x06  |

| 0x11     | 0x10  |

| 0x15     | 0x28  |

| 0x20     | 0x09  |

| 0x24     | 0x90  |

#### **RESTART: 0x07 (write-only)**

This address, when written with the value 0x01, restarts the device without modifying the content of I<sup>2</sup>C registers. All recovery loops (AGC, timing, carrier) and the equalizer restart from their initial value. This should always be done after a SETAUTOCFG or any reconfiguration of I<sup>2</sup>C registers.

#### OUTPUTCFG: 0x08 (read/write)

The data output configuration register configures the output format on pins DATAOUT7 to DATAOUT0 of the device.

|      | b7   | b6   | b5  | b4   | b3         | b2         | b1 | b0  |

|------|------|------|-----|------|------------|------------|----|-----|

| 80x0 | rese | rved | tur | ndiv | irq<br>pol | outputmode |    | ode |

tundiv specifies the frequency of the clock signal output on TUNCLK pin. The frequency of this clock is given by:

$$f_{TUNCLK} = \frac{1}{p} f_{XTAL}$$

with  $p = 2^{TUNDIV + 1}$

So p can take the values: 2, 4 or 8. When tundiv = 3, there is no output on TUNCLK pin in order to reduce power consumption if not needed.

outputmode can take the following binary values:

000: MPEG2-TS parallel (DVB common interface)

001: MPEG2-TS serial

010: Constellation before decision

011: I output after AGC1 and baseband conversion

100: I output after timing recovery

101: I output after A/D sampling

irgpol configures the polarity of the IRQ output pin:

0: IRQ is in high impedance or has value 0 when interruptions occur (see IRQMASK register).

1: IRQ is in high impedance or has value 1 when interruptions occur (see IRQMASK register).

#### Example:

0x0 configures MPEG2-TS parallel output with IRQ going low when interruptions occur. The default value after SET-AUTOCFG is 0x30.

#### MASKLOCK1: 0x09 (read/write)

This register specifies the lock signals that must be monitored on the LOCK1 output pin. If all internal lock signals configured by this mask go high, then LOCK1 goes high.

|      | b7  | b6  | b5  | b4  | b3       | b2       | b1  | b0  |

|------|-----|-----|-----|-----|----------|----------|-----|-----|

| 0x09 | fec | car | equ | tim | agc<br>2 | agc<br>1 | adc | pll |

- · fec: Mask on forward error correction lock signal

- · car: Mask on carrier recovery loop lock signal

- · equ: Mask on equalizer lock signal

- · tim: Mask on symbol rate recovery lock signal

- · agc2: Mask on digital agc lock signal

- · agc1: Mask on analog agc lock signal

- adc: Mask on analog agc level lock signal

- pll: Mask on Phase Locked Loop (PLL) lock signal SETAUTOCFG configures MASKLOCK1 at value 0x80, corresponding to the FEC lock signal only.

#### MASKLOCK2: 0x0A (read/write)

This register specifies the lock signals that must be monitored on the LOCK2 output pin. If all internal lock signals configured by this mask go high, then LOCK2 goes high.

|      |     |     |     | b4  |          |          |     | b0  |

|------|-----|-----|-----|-----|----------|----------|-----|-----|

| 0x0A | fec | car | equ | tim | agc<br>2 | agc<br>1 | adc | pll |

SETAUTOCFG configures MASKLOCK2 at value 0x70, corresponding to the lock signals of the carrier recovery, the equalizer and the timing recovery, which is the full demodulator.

#### IRQMASK: 0x0B (read/write)

Mask for IRQ output pin. This register specifies the mask on events that should activate the IRQ pin. IRQ goes to the value specified by irqpol (see OUTPUTCFG configuration) when any of the events specified by the mask described below occur and goes back to high impedance when any I<sup>2</sup>C register is written by the microcontroller.

|      |            |          | b5         |          |     |            |      |       |

|------|------------|----------|------------|----------|-----|------------|------|-------|

| 0x0A | unlck<br>1 | lck<br>1 | unlck<br>2 | lck<br>2 | sat | frm<br>Ist | time | e_win |

- unlck1: IRQ when LOCK1 signal goes from 1 to 0

- lck1: IRQ when LOCK1 signal goes from 0 to 1

- unlck2: IRQ when LOCK2 signal goes from 1 to 0

- lck2: IRQ when LOCK2 signal goes from 0 to 1

- sat: IRQ when signal input loss (AGC saturation)

- frmlst: IRQ when frame was lost

- time\_win: Periodic generation of IRQ

00: IRQ not activated by time delay

01: IRQ activated every 2048 frames

10: IRQ activated every 16384 frames

11: IRQ activated every 108 bits

SETAUTOCFG configures the mask on UNLOCK1.

#### TUNI2CADD: 0x0C (read/write)

I<sup>2</sup>C address of tuner when connected to I<sup>2</sup>C bus of device (pins TI2CSCL and TI2CSDA). For more details on the tuner I<sup>2</sup>C switch principle, see "I<sup>2</sup>C Read Mode" on page 9.

|      | b7 | b6 | b5   | b4                    | b3     | b2 | b1 | b0 |

|------|----|----|------|-----------------------|--------|----|----|----|

| 0x0C |    |    | Tune | r I <sup>2</sup> C ac | ddress |    |    | EN |

EN enables the switch when set to 1.

Note: EN should be set to 1 when tuner is configured. Then EN must be set back to 0.

#### CHIPID: 0x0E to 0x0F (read)

Gives information about chip number and version. Value is 0x6510 (AT76C651, version A).

|      | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |  |

|------|----|----|----|----|----|----|----|----|--|

| 0x0E | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  |  |

| 0x0F | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |  |

#### **Baseband Conversion and AGC1**

#### AGC1NMIN: 0x13 (read/write)

Specifies the minimum (or maximum) amplification value of AGC1 given by the PWM output pin, which is between 0 and 255 when BBCFG(4) = 0 or BBCFG(4) = 1. For more details about the BBCFG register, see the description below. This value can be used to saturate amplification in case of non-linearities of the amplifier at extreme values.

|      | b7 | b6 | b5 | b4    | b3   | b2 | b1 | b0 |

|------|----|----|----|-------|------|----|----|----|

| 0x13 |    |    |    | agc1r | nmin |    |    |    |

Example:

0x00 (for maximum amplifying range)

#### AGC1NMAX: 0x14 (read/write)

Specifies the maximum (or minimum) amplification value of AGC1 given by the PWM output pin, which is between 0 and 255 when BBCFG(4) = 0 or BBCFG(4) = 1. For more details about the BBCFG register, see the description below. This value can be used to saturate amplification in case of non-linearities of the amplifier at extreme values.

|      | b7 | b6 | b5 | b4    | b3   | b2 | b1 | b0 |

|------|----|----|----|-------|------|----|----|----|

| 0x14 |    |    |    | agc1r | nmax |    |    |    |

Example:

0xFF (for maximum amplifying range)

#### BBCFG: 0x15 (read/write)

General control of IF to BB conversion. This register controls several parameters of the AGC1 control loop, internal DC-offset compensation and AGC output format.

|      | b7  | b6  | b5        | b4        | b3         | b2  | b1         | b0  |

|------|-----|-----|-----------|-----------|------------|-----|------------|-----|

| 0x15 | res | res | dc<br>con | sgn<br>am | adc<br>con | res | pwm<br>con | res |

- res: Reserved (must be configured with 0 when writing register)

- dccon: DC-offset control. If set to 0, the internal DC-offset compensation is ON. If set to 1, the internal DC-offset control is OFF. The DC-offset should be ON when the input signal is in BB.

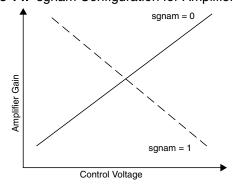

- sgnam: Sign of the amplifier control command (see Figure 14)

Figure 14. sgnam Configuration for Amplifier Gain Control

adccon: Specifies whether ADCLEVEL must be automatically adapted in the presence of adjacent channels or if it must keep its initial value defined by register AGC1INITADC. Automatic adaptation is configured by 0; no adaptation is configured by 1. pwmcon: Specifies output format for AGC and CSTPWM pins. If set to 0, the AGC control is output in PWM format on AGC pin, and a completely configurable value (see CSTPWM register) is output in PWM format on CSTPWM pin. If set to 1, the AGC control is output in differential format on AGC and CSTPWM pins. In this case, differential integration must be performed in the analog domain.

In case of a PWM output, the AGC pin should be connected to an RC filter with a cut-off frequency of maximum 1 kHz.

Example:

$$R = 1.5 \text{ k}\Omega$$

,  $C = 1 \mu\text{F}$

Note: The PWM output pin can be power supplied by 5V through the I2CVDD power supply. This assumes  $I^2C$

bus functions at 5V.

#### CSTPWM: 0x17 (read/write)

Specifies a configurable value between 0 and 255, which is given in PWM format on CSTPWM pin in case BBCFG(1) = 0. The CSTPWM pin should be connected to an RC filter with a cut-off frequency of maximum 1 kHz.

Example:

$$R = 1.5 \text{ k}\Omega$$

,  $C = 1 \mu\text{F}$

This voltage output can be used to control any other device on the board, like other amplifier gain control, variable capacitor, etc.

Note: This pin can output 5V since it is power-supplied by the I2CVDD power supply (this assumes I<sup>2</sup>C bus functions at 5V).

|      | b7 | b6 | b5 | b4    | b3 | b2 | b1 | b0 |

|------|----|----|----|-------|----|----|----|----|

| 0x17 |    |    |    | cstpw | /m |    |    |    |

Example:

cstpwm = 0x7F (2.5V in case 5V is connected to I2CVDD)

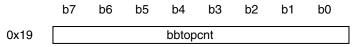

#### BBTOPCNT: 0x19 (read)

This monitoring register indicates the number of A/D saturations over 16384 successive samples. This register can take values between 0 and 255. 255 indicates that more than 255 A/D saturations have occurred during the last 16384 samples.

When the demodulator is working properly, this value should indicate 0x00.

## **Timing Recovery**

#### TIMLOOPCFG: 0x23 to 0x24 (read/write)

These two registers configure the loop bandwidth of the timing recovery loop.

|      | b7 | b6       | b5    | b4 | b3         | b2   | b1   | b0 |  |

|------|----|----------|-------|----|------------|------|------|----|--|

| 0x23 |    | blmax_   | _mexp |    | blmin_mexp |      |      |    |  |

| 0x24 | l  | oltrack_ | _mexp |    |            | rese | rved |    |  |

#### Example:

0x7F for register 0x23 and 0x9 for register 0x24

The three parameters blmax\_mexp, blmin\_mexp and bltrack\_mexp are 4-bit unsigned numbers that must follow the conditions:

- 7 ≤ blmax\_mexp ≤ blmin\_mexp ≤ 15

- 7 ≤ bltrack\_mexp ≤ 15

They are related to the bandwidth blmax, blmin and bltrack by the formula:

$$blx = 2^{-Blx\_mexp}$$

blmax is the maximal and initial bandwidth value used with a robust (Gardner type) comparator. blmin is the minimal bandwidth value that can be taken by the loop bandwidth with the same comparator. When blmax > blmin, the loop can automatically decrease when the lock indicator is positive or increase when this signal detects that the timing recovery system is out of lock. This variable bandwidth allows fast convergence, large timing frequency lock-in range in initial acquisitio1

n phase and low timing jitter when the system is locked.

bltrack is the fixed value of the bandwidth used with decision base comparator. Typical values corresponding to the example above are:

$blmax = 2^{-7} \Rightarrow blmax mexp = 7$

blmin =  $2^{-15} \Rightarrow$  blmin mexp = 15

$bltrack = 2^{-9} \Rightarrow bltrack\_mexp = 9$

#### TIMLOOPMONIT: 0x29 (read)

This monitoring register indicates the value of the automatically variable loop bandwidth.

|      | b7 | b6   | b5   | b4 | b3 | b2   | b1   | b0 |

|------|----|------|------|----|----|------|------|----|

| 0x29 |    | Bl_n | пехр |    |    | rese | rved |    |

Bandwidth Bl, which is given by formula:

$$Bl = 2^{-Bl\_mexp}$$

BI\_mexp is an unsigned value, taking values from blmax\_mexp to blmin\_mexp (see TIMLOOPCFG).

When timing is well recovered, BI is equal to blmin.

#### **Carrier Recovery**

#### CARALPHAACQ/CARBETAACQ: 0x31/0x32 (read/write)

These two registers select the carrier loop bandwidth during acquisition phase. Through those 2 bytes one can control the bandwidth and the damping factor  $(\xi)$  of the loop filter.

|      | b7 | b6 | b5 | b4     | b3    | b2 | b1 | b0 |

|------|----|----|----|--------|-------|----|----|----|

| 0x31 |    |    |    | caralp | haacq |    |    |    |

| 0x32 |    |    |    | carbe  | taacq |    |    |    |

Table 14 depicts some typical values for CARALPHAACQ and CARBETAACQ.

Table 14.

| B <sub>I</sub> f <sub>symbol</sub> | یح  | CARALPHAACQ | CARBETAACQ |

|------------------------------------|-----|-------------|------------|

| 0.005                              | 0.7 | 0xAE        | 0x9C       |

| 0.005                              | 1.0 | 0x98        | 0x98       |

| 0.005                              | 2.0 | 0x9A        | 0xBC       |

| 0.005                              | 4.0 | 0x9A        | 0xDD       |

| 0.010                              | 0.7 | 0x9E        | 0x7C       |

| 0.010                              | 1.0 | 0x88        | 0x78       |

| 0.010                              | 2.0 | A8x0        | 0x9C       |

| 0.010                              | 4.0 | A8x0        | 0xBD       |

| 0.030                              | 0.7 | 0x7A        | 0x4D       |

| 0.030                              | 1.0 | 0x7C        | 0x49       |

| 0.030                              | 2.0 | 0x7E        | 0x6D       |

| 0.030                              | 4.0 | 0x7F        | 0x8E       |

In automatic configuration, these parameters correspond to BI  $f_{symbol} = 0.03$  and  $\xi = 1.0$ .

# CARALPHATRACK/CARBETATRACK: 0x33/0x34 (read/write)

These two registers select the carrier loop bandwidth during tracking phase (after acquisition). The same table as given for (0x31/0x32) configures these parameters. The switch between tracking phase and acquisition phase takes place when agc2, equalizer and carrier are locked.

|      | b7            | b6 | b5 | b4     | b3     | b2 | b1 | b0 |  |

|------|---------------|----|----|--------|--------|----|----|----|--|

| 0x33 | caralphatrack |    |    |        |        |    |    |    |  |

| 0x34 |               |    |    | carbet | atrack |    |    |    |  |

In automatic configuration, these parameters correspond to BI  $f_{\text{symbol}} = 0.03$  and  $\xi = 4.0.$

#### CARCONST: 0x39/0x3A/0x3B (read)

|      | b7       | b6   | b5   | b4   | b3   | b2  | b1    | b0 |  |

|------|----------|------|------|------|------|-----|-------|----|--|

| 0x39 |          |      |      | l (1 | 1:4) |     |       |    |  |

| 0x3A | Q (11:4) |      |      |      |      |     |       |    |  |

| 0x3B |          | I (3 | 3:0) |      |      | Q ( | (3:0) |    |  |

The constellation points after gain adjustment, timing recovery, equalization and carrier recovery can be collected without breaking down the demodulation and the channel decoding. The two components (I, Q), with 12-bit precision, are collected in three bytes:

- Byte 1 (0x39): 8 MSB of I

- Byte 2 (0x3A): 8 MSB of Q

- Byte 3 (0x3B): The 4 MSB of byte 3 are equal to the 4 LSB of I and the 4 LSB of byte 3 are equal to the 4 LSB of Q.

Byte 1 should be collected first. When the address of this byte is detected by the AT76C651, then a constellation point (I: 12 bits, Q: 12 bits) is memorized and only the 8 MSBs of I are sent as data on the I<sup>2</sup>C bus. Byte 2 and byte 3 can be collected later; their content does not change unless byte 1 is collected again.

#### AGC2

#### AGC2CFG: 0x42 (read/write)

|      | b7 | b6 | b5 | b4    | b3 | b2 | b1    | b0 |

|------|----|----|----|-------|----|----|-------|----|

| 0x42 | re | S  |    | oopbw | 1  | I  | oopbw | 2  |

Two operating modes exist for agc2: boost mode and normal mode. After a reset or a soft clear, the agc2 is in boost mode and unlocked. During this phase, equalizer and carrier are inhibited. The switch from boost mode to normal mode happens when agc2 locks. The agc2 loop bandwidth can be controlled through loopbw2 during boost mode and by loopbw1 during normal mode. In both cases the loop bandwidth is proportional to loopbw.

Table 15 gives the value of AGC2CFG for the different QAM in automatic configuration.

Table 15.

| QAM      | AGC2CFG |

|----------|---------|

| QPSK     | 0x34    |

| QAM-16   | 0x35    |

| QAM-32   | 0x35    |

| QAM-64   | 0x34    |

| QAM-128  | 0x33    |

| QAM-256  | 0x32    |

| QAM-512  | 0x31    |

| QAM-1024 | 0x30    |

#### AGC2INIT: 0x43 and 0x44 (read/write)

These registers configure the initial agc2 gain.

|      | b7              | b6       | b5    | b4 | b3 | b2     | b1    | b0 |  |  |

|------|-----------------|----------|-------|----|----|--------|-------|----|--|--|

| 0x43 | mantissa (10:3) |          |       |    |    |        |       |    |  |  |

| 0x44 | ma              | ntissa ( | (2:0) |    | ex | ponent | (4:0) |    |  |  |

AGC2INIT is coded in a floating format with a mantissa coded with 11 unsigned bits and an exponent coded with 5 signed bits, defined as follows:

$$exponent = floor(\log_2(agc2gain))$$

$$mantissa = floor(agc2gain \times 2^{-exponent} \times 1024)$$

Exponent must be in the range -6 to 13, and mantissa takes its value in the range 1024 to 2047.

#### Equalizer

#### EQUCFG: 0x51 (read/write)

This register controls the equalizer operating mode.

|      | b7  | b6  | b5  | b4   | b3             | b2 | b1   | b0 |

|------|-----|-----|-----|------|----------------|----|------|----|

| 0x51 | inh | fre | len | stru | structure step |    | step |    |

- inh: When set to 1, this parameter inhibits the equalizer; all equalizer taps are set to 0 except central tap, which is equal to 1 (in complex format). In standard configuration it is set to 0.

- fre: When set to 1 it freezes the equalizer taps adaptation. The equalizer behaves as a complex FIR (finite impulse response). In standard configuration it is set to 0.

- len: The equalizer has 32 taps when this parameter is set to 1 and only 16 taps when set to 0. The first mode can be selected only if the ratio between f<sub>ref</sub> and f<sub>symbol</sub> is higher or equal to 8(f<sub>ref</sub>/f<sub>symbol</sub> ≥ 8). In standard configuration it is set to 1.

- structure: Two equalizer structures are implemented in the AT76C651: LE (linear equalizer) and DFE (decision feedback equalizer). When b5 = 1, only LE structure can be selected. In DFE mode two substructures, depending on the position of the central tap, can be configured. Table 16 shows the different possibilities.

- step: This parameter controls the step used to adapt the equalizer taps. The higher the step, the higher the adaptation step.

Table 16.

| b4b3 | Structure                                      |

|------|------------------------------------------------|

| 00   | LE                                             |

| 10   | LE                                             |

| 01   | DFE with central tap position between 0 and 7  |

| 11   | DFE with central tap position between 8 and 15 |

#### **EQUCENTRAL:** 0x52 (read/write)

|      | b7  | b6 | b5  | b4 | b3     | b2       | b1      | b0 |  |

|------|-----|----|-----|----|--------|----------|---------|----|--|

| 0x52 | res | ad | apt |    | centra | al tap p | osition |    |  |

central tap position: EQUCENTRAL (4:0) gives the position of the equalizer central tap. This position should be set between 0 and 31 when EQUCFG(5)=1 and between 0 and 15 when EQUCFG(5)=0. In standard configuration this parameter is set to 7.

• adapt: The central tap adaptation mode can be selected between the configurations shown in Table 17:

Table 17.

| b6b5 | Real Part  | Imag Part  |

|------|------------|------------|

| 00   | adapted    | adapted    |

| 01   | adapted    | fixed to 0 |

| 10   | fixed to 1 | adapted    |

| 11   | fixed to 1 | fixed to 0 |

In standard configuration it is set to 11.

#### EQUTAPRORD: 0x53 (read/write)

|      | b7 | b6     | b5 | b4 | b3      | b2     | b1     | b0 |

|------|----|--------|----|----|---------|--------|--------|----|

| 0x53 | r  | eserve | d  |    | equaliz | er tap | ositio | n  |

This parameter selects the position of the equalizer tap that we want to collect (see "EQUTAPREAL: 0x54/0x55 (read) and EQUTAPIMAG: 0x56/0x57 (read)"). The number of taps that can be read depends of the equalizer length (see "EQUCFG: 0x51 (read/write)").

# EQUTAPREAL: 0x54/0x55 (read) and EQUTAPIMAG: 0x56/0x57 (read)

|          | b7                | b6 | b5 | b4      | b3      | b2 | b1 | b0 |  |  |

|----------|-------------------|----|----|---------|---------|----|----|----|--|--|

| 0x54 MSB |                   |    | е  | qutapre | al (15: | 8) |    |    |  |  |

| 0x55 LSB | equtapreal (7:0)  |    |    |         |         |    |    |    |  |  |

| 0x56 MSB | equtapimag (15:8) |    |    |         |         |    |    |    |  |  |

| 0x57 LSB |                   |    | e  | qutapin | nag (7: | 0) |    |    |  |  |

After selecting the equalizer tap to read (see "EQUTAP-RORD: 0x53 (read/write)"), the real part and the imaginary part of the tap are collected in four bytes. The first byte to read must be 0x54. When the AT76C651 detects this address, it memorizes the equalizer tap value (4 bytes) and sends the 8 MSBs of the real part as read data. The three other bytes can be collected later. The value of the tap is equal to:

$$(real + j imag) = \frac{((signed)(EQUTAPREAL)) + (j signed(EQUTAPIMAG))}{16384}$$

#### **FEC**

#### FECIQINV: 0x60 (read/write)

Configuration of I and Q inversion. This register indicates if the I and Q channel must be swapped before de-mapping. An automatic mode is also provided.

|      | b7 | b6 | b5     | b4 | b3    | b2   | b1   | b0 |

|------|----|----|--------|----|-------|------|------|----|

| 0x60 |    | l  | eserve |    | iqinv | iqin | vcmd |    |

- iqinv is a read-only single bit that indicates if I and Q channel are swapped (in manual mode it is equal to b0).

- iqinvcmd is composed of two bits (read/write): the msb (b1) controls the use of the automatic mode (= 0) or the manual mode (= 1); the lsb (b0) is used in manual mode to swap I and Q channel.

Note: The automatic mode uses the frame structure to choose the right configuration. If the frame is not recovered, iqinv can change at any time.

#### FECFLEN: 0x61 (read/write)

Frame length configuration. The size of frame can be configured.

|      | b7 | b6 | b5 | b4  | b3 | b2 | b1 | b0 |

|------|----|----|----|-----|----|----|----|----|

| 0x61 |    |    |    | fle | en |    |    |    |