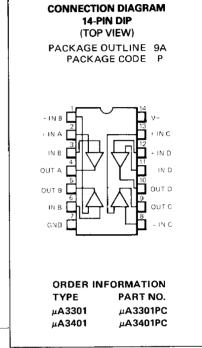

# μA3301 · μA3401

# **QUAD SINGLE-SUPPLY AMPLIFIERS**

FAIRCHILD INTEGRATED CIRCUITS

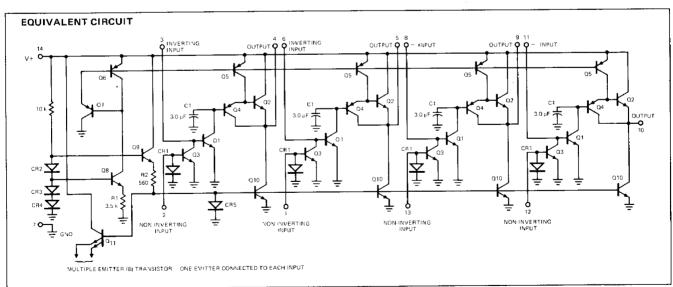

**GENERAL DESCRIPTION** – The  $\mu$ A3301/ $\mu$ A3401 are monolithic Quad Amplifiers consisting of four independent, dual input, internally compensated amplifiers. They are constructed using the Fairchild Planar\* epitaxial process. They were designed specifically to operate from a single power supply voltage and to provide a large output voltage swing. The non-inverting input function is achieved by using a current mirror. Applications for the  $\mu$ A3301/ $\mu$ A3401 are ac amplifiers, FC active filters, low frequency triangle, squarewave and pulse waveform generation circuits, tachometers and low speed, high voltage digital logic gates.

- SINGLE SUPPLY OPERATION +4.0 Vdc to +28 Vdc

- INTERNALLY COMPENSATED

- WIDE UNITY GAIN BANDWIDTH 5.0 MHz

- LOW INPUT BIAS CURRENT 50 nA TYPICAL

- HIGH OPEN LOOP GAIN 1000 V/V MINIMUM

#### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage

µA3301

µA3401

Non-Inverting Input Current

Sink Current

Source Current

Internal Power Dissipation (Note 1)

Operating Temperature Range

µA3301

µA3401

Storage Temperature Range

Pin Temperature (Soldering, 10 s)

+28 V +18 V 5.0 mA 50 mA 50 mA 670 mW -40°C to +85°C 0°C to +70°C -55°C to +125°C

<sup>\*</sup>Planar is a patented Fairchild process.

# FAIRCHILD • $\mu$ A3301 • $\mu$ A3401

# μA3301

# $\textbf{ELECTRICAL CHARACTERISTICS: V}_S = +15 \text{ Vdc, R}_L = 5.0 \text{ k}\Omega, \text{ T}_A = +25^{\circ}\text{C, each amplifier, unless otherwise noted.}$

| CHARACTERISTICS                                                     | CONDITION                                             | MIN  | TYP  | MAX  | UNITS              |

|---------------------------------------------------------------------|-------------------------------------------------------|------|------|------|--------------------|

| Open Loop Voltage Gain (Note 2)                                     | Inverting Input                                       | 1000 | 2000 |      | V/V                |

| Input Bias Current (Note 3)                                         | R <sub>L</sub> = ∞, Inverting Input                   |      | 50   | 300  | nA                 |

| Input Resistance                                                    |                                                       | 0.1  | 1.0  |      | MΩ                 |

| Current Mirror Gain (Note 4)                                        | (I <sub>Mirror</sub> = 200 μAdc)                      | 0.80 | 0.98 | 1.16 | A/A                |

| Output Current                                                      |                                                       |      |      |      |                    |

| Source                                                              | V <sub>OH</sub> = 0.4 Vdc                             | 3.0  | 10   |      | mA                 |

|                                                                     | V <sub>OH</sub> = 9.0 Vdc                             |      | 7.0  |      | mA                 |

| Sink (Note 5)                                                       | V <sub>OL</sub> = 0.4 Vdc                             | 0.5  | 0.87 |      | mA                 |

| Output Voltage (Note 6)                                             |                                                       |      |      |      |                    |

| HIGH                                                                |                                                       | 13.5 | 14.2 |      | V                  |

| LOW                                                                 |                                                       |      | 0.03 | 0,1  | V                  |

| Slew Rate                                                           | $C_{L} = 100 \text{ pF}, R_{L} = 5.0 \text{ k}\Omega$ |      | 0.6  |      | V/μs               |

| Unity Gain Bandwidth (Note 7)                                       |                                                       |      | 5.0  |      | MHz                |

| Phase Margin (Note 7)                                               |                                                       |      | 70   |      | Degrees            |

| Quiescent Power Supply Current (Note 8)                             |                                                       |      | ĺ .  |      |                    |

| Non-Inverting Inputs Open                                           | Total for Four Amplifiers                             |      | 6.9  | 10   | mA                 |

| Non-Inverting Inputs Grounded                                       | Total for Four Amplifiers                             |      | 7.8  | 14   | mA                 |

| Power Supply Rejection (Note 9)                                     | (f = 100 Hz)                                          |      | .75  |      | dB                 |

| Channel Separation                                                  | (f = 1.0 kHz)                                         |      | 85   |      | dB                 |

| The following specifications apply for −40°C <t<sub>A &lt;+</t<sub> | 85°C.                                                 |      |      |      |                    |

| Open Loop Voltage Gain (R <sub>L</sub> = 10 kΩ)                     | Inverting Input                                       |      | 1600 |      | V/V                |

| Input Bias Current                                                  | R <sub>L</sub> = ∞                                    |      |      | 500  | nA                 |

| Output Voltage (Note 10) Undistorted Output Swing                   |                                                       | 10   | 13.5 |      | V <sub>pk-pk</sub> |

# μΑ3401

# $\textbf{ELECTRICAL CHARACTERISTICS: V}_S = +15 \text{ Vdc, R}_L = 5.0 \text{ k}\Omega, T_A = +25 ^{\circ}\text{C, each amplifier, unless otherwise noted.}$

| CHARACTERISTICS                                                                       | CONDITION                              | MIN  | TYP  | MAX | UNITS              |

|---------------------------------------------------------------------------------------|----------------------------------------|------|------|-----|--------------------|

| Open Loop Voltage Gain (Note 2)                                                       | Inverting Input                        | 1000 | 2000 |     | V/V                |

| Input Bias Current (Note 3)                                                           | R <sub>L</sub> = ∞, Inverting Input    |      | 50   | 300 | nΑ                 |

| Input Resistance                                                                      |                                        | 0.1  | 1.0  |     | MΩ                 |

| Output Current                                                                        |                                        |      |      |     |                    |

| Source                                                                                |                                        | 5.0  | 10   |     | mA                 |

| Sink (Note 5)                                                                         |                                        | 0.5  | 1.0  |     | mΑ                 |

| Output Voltage (Note 6)                                                               |                                        |      |      |     |                    |

| HIGH                                                                                  |                                        | 13.5 | 14.2 |     | V                  |

| LOW                                                                                   |                                        |      | 0.03 | 0.1 | V                  |

| Slew Rate                                                                             | $C_L$ = 100 pF, $R_L$ = 5.0 k $\Omega$ |      | 0.6  |     | V/µs               |

| Unity Gain Bandwidth (Note 7)                                                         |                                        |      | 5.0  |     | MHz                |

| Phase Margin (Note 7)                                                                 |                                        |      | 70   |     | Degrees            |

| Quiescent Power Supply Current (Note 8)                                               |                                        |      |      |     |                    |

| Non-Inverting Inputs Open                                                             | Total for Four Amplifiers              |      | 6.9  | 10  | mA                 |

| Non-Inverting Inputs Grounded                                                         | Total for Four Amplifiers              |      | 7.8  | 14  | mA                 |

| Power Supply Rejection (Note 9)                                                       | (f = 100 Hz)                           |      | 75   |     | dB                 |

| Channel Separation                                                                    | (f = 1.0 kHz)                          |      | 85   |     | dB                 |

| The following specifications apply for $0^{\circ}$ C $\leq$ T <sub>A</sub> $\leq$ 70° | C.                                     |      |      |     |                    |

| Open Loop Voltage Gain (R <sub>L</sub> = 10 kΩ)                                       | Inverting Input                        | 800  |      |     | V/V                |

| Input Bias Current                                                                    | R <sub>L</sub> = ∞                     |      |      | 500 | nA                 |

| Output Voltage (Note 10) Undistorted Output Swing                                     |                                        | 10   | 13.5 |     | V <sub>pk-pk</sub> |

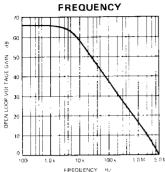

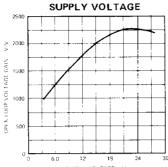

#### **TYPICAL PERFORMANCE CURVES**

# OPEN LOOP VOLTAGE GAIN AS A FUNCTION OF

# OPEN LOOP VOLTAGE GAIN AS A FUNCTION OF

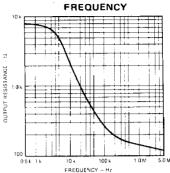

**OUTPUT RESISTANCE** AS A FUNCTION OF

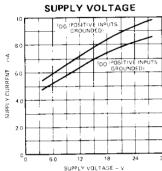

# SUPPLY CURRENT AS A FUNCTION OF

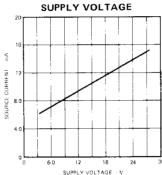

# LINEAR SOURCE CURRENT AS A FUNCTION OF

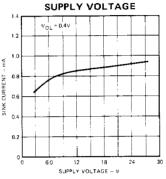

LINEAR SINK CURRENT AS A FUNCTION OF

#### NOTES:

- Rating applies to  $T_A$  up to  $70^{\circ}$ C. Above  $T_A = 70^{\circ}$ C, derate linearly at 8.3 mW/ $^{\circ}$ C.

Open loop voltage gain is defined as the voltage gain from the inverting input to the output.

Input bias current can be defined only for the inverting input. The non-inverting input is not a true "differential input" as with a conventional IC operational amplifier. As such this input does not have a requirement for input bias current.

- Current mirror gain is defined as the current demanded at the inverting input divided by the current into the non-inverting input.

- Sink current is specified for linear operation, When the device is used as a gate or a comparator (non-linear operation), the sink capability of the device is approximately 5.0 milliamperes.

- When used as a non-inverting amplifier, the minimum output voltage is the VBE of the inverting input transistor. 6.

- when used as a non-inverting amplitier, the minimum duplet votige is in a VBE of the inverting input to the output.

Bandwidth and phase margin are defined with respect to the voltage gain from the inverting input to the output.

The quiescent current will increase approximately 0.3 mA for each non-inverting input which is grounded. Leaving the non-inverting input 8.

- open causes the apparent input bias current to increase slightly (100 nA) at high temperatures.

Power supply rejection is specified at closed loop unity gain, and therefore indicates the supply rejection of both the biasing circuitry and

- the feedback amplifier.

Peak-to-peak restrictions are due to the variations of the quiescent dc output voltage in the standard configuration as shown in the 10. peak-to-peak output voltage test circuit.

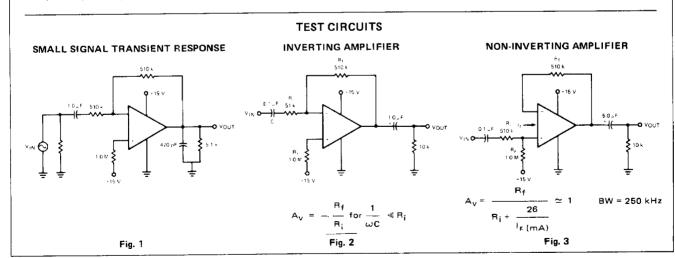

# TEST CIRCUITS (Cont'd)

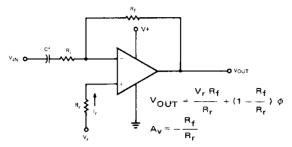

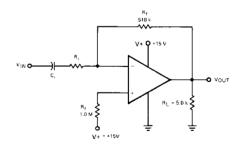

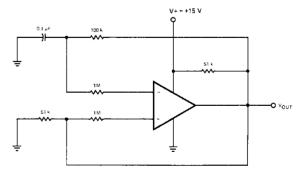

# INVERTING AMPLIFIER WITH ARBITRARY REFERENCE

\*Select for low frequency response.

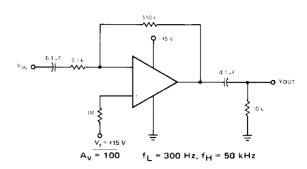

# INVERTING AMPLIFIER WITH $A_v = 100 \text{ AND } V_r = V_{+}$

Fig. 5

Fig. 4

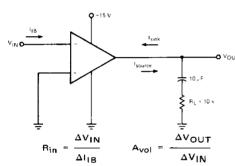

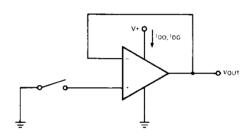

# OPEN LOOP GAIN AND INPUT RESISTANCE (INPUT BIAS CURRENT, OUTPUT CURRENT)

Amplifier must be biased by  $\boldsymbol{V}_{\mbox{\footnotesize{IN}}}$  in the linear operating region

Fig. 6

#### QUIESCENT POWER SUPPLY CURRENT

${\rm I}_{DO}$  is total supply current with noninverting input open,  ${\rm I}_{DG}$  is total supply current with noninverting input grounded.

Fig. 7

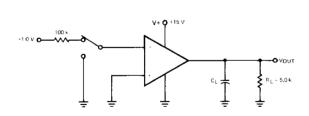

# OUTPUT VOLTAGE SWING

$\rm V_{OL}$  measured with inverting input biased as shown.  $\rm V_{OH}$  measured with inverting input grounded,

# PEAK-TO-PEAK OUTPUT VOLTAGE

$V_{OUT} \simeq V + \frac{R_f}{R_r} \simeq \frac{V +}{2}$  for  $R_r \simeq 2 R_f$

Fig. 9

Fig. 8

1 | • ---

# 5

#### NORMAL DESIGN PROCEDURE

#### Output Q-Point Biasing

A number of techniques may be devised to bias the quiescent output voltage to an acceptable level. However, in terms of loop gain considerations it is usually desirable to use the non-inverting input to effect the biasing as shown in Figures 2 and 3. The high impedance of the collector of the non-inverting "current mirror" transistor helps to achieve the maximum loop gain for any particular configuration. It is desirable that the non-inverting input current be in the  $5.0 \, \mu A$  to  $100 \, \mu A$  range.

#### V+ Reference Voltage (Figures 2 and 3)

The non-inverting input is normally returned to the V+ voltage (which should be well filtered) through a resistor,  $R_r$ , allowing the input current,  $I_r$ , to be within the range of 5.0  $\mu$ A to 100  $\mu$ A. Choosing the feedback resistor,  $R_f$ , to be equal to 1/2  $R_r$  will now bias the amplifier output dc level to approximately:

This allows for maximum dynamic range of the output voltage.

#### Reference Voltage Other Than V+ (Figure 4)

The biasing resistor  $R_r$  may be returned to a voltage  $(V_r)$  other than V+. By setting  $R_f = R_r$ , (still keeping  $I_r$  between 5.0  $\mu A$  and 100  $\mu A$ ) the output dc level will be equal to  $V_r$ . Neglecting error terms, the expression for determining  $V_{Odc}$  is:

$$V_{OUT} = \frac{(V_r) (R_f)}{R_r} + \left(1 - \frac{R_f}{R_r}\right) \phi$$

where  $\phi$  is the V<sub>BE</sub> drop of the input transistors (approximately 0.7 V @ +25°C).

The error terms not appearing in the above equation can cause the dc operating point to vary up to 20% from the expected value. Error terms are minimized by setting the input current within the range of  $5.0 \, \mu A$  to  $100 \, \mu A$ .

#### Gain Determination - Inverting Amplifier

The amplifier is normally used in the inverting mode. The input may be capacitively coupled to avoid upsetting the dc bias and the output is normally capacitively coupled to eliminate the dc voltage across the load. Note that when the output is capacitively coupled to the load, the value of I<sub>sink</sub> becomes a limitation with respect to the load driving capabilities of the device. The limitation is less severe if the device is direct coupled. In this configuration, the ac gain is determined by the ratio of R<sub>f</sub> to R<sub>i</sub>, in the same manner as for a conventional operational amplifier:

$$A_v = -\frac{R_f}{R_i}$$

The lower corner frequency is determined by the coupling capacitors to the input and load resistors. The upper corner frequency will usually be determined by the amplifier internal compensation. The amplifier unity gain bandwidth is typically 5.0 MHz and with the gain roll-off at 20 dB per decade, bandwidth will typically be 500 kHz with 20 dB of closed loop gain or 50 kHz with 40 dB of closed loop gain. The exception to this occurs at low gains where the input resistor selected is large. The pole formed by the amplifier input capacitance, stray capacitance and the input resistor may occur before the closed loop gain intercepts the open loop response curve. The inverting input capacity is typically 3.0 pF.

#### Non-Inverting Amplifier

Although recommended as an inverting amplifier, the 3301/3401 may be used in the non-inverting mode (Figure 3). The amplifier gain in this configuration is subject to the same error terms that affects the output Q point biasing so the gain may deviate as much as  $\pm 20\%$  from that expected. In addition, the resistance of the input diode must be included in the value of the input resistor. This resistance is approximately:

$$\frac{26}{1}$$

$\Omega$

where Ir is input current in mA. The non-inverting gain expression is given by:

$$A_V = \frac{R_f}{R_i + \frac{26}{I_r (mA)}} \pm 20\%.$$

The bandwidth of the non-inverting configuration for a given  $R_f$  value is essentially independent of the gain chosen. For  $R_f$  = 510 k $\Omega$  the bandwidth will be in excess of 200 kHz for non-inverting gains of 1, 10, or 100. This is a result of the loop gain remaining constant for these gains since the input resistor is effectively isolated from the feedback loop.

# FAIRCHILD • $\mu$ A3301 • $\mu$ A3401

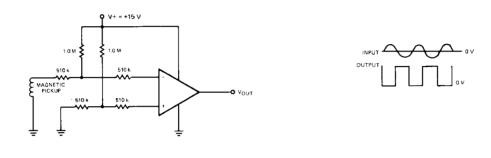

#### **TYPICAL APPLICATIONS** TACHOMETER CIRCUIT V+ = +12V MAGNETIC PICKUP HYSTERISIS AMPLIFIER MONOSTABLE MULTIVIBRATOR PULSE AVERAGING ₹ 13D 本6.10 100 k MAGNETIC } C1 4.7 k 0.01 μF POWER SUPPLY о оптрит NONREGULATED 0.01 µF 10 k $V_{pk-pk} = \frac{\{V_{OUT} | 0.6\} \cdot A_1 \cdot t}{P200}$ HYSTERISIS VOLTAGE FOR SWITCHING $v_H = \frac{A_1 R_2}{R_1} (v_S - 16)$ TIMING INTERVAL 1 ≈ 0.7 R1C1

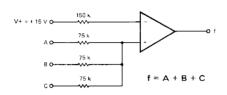

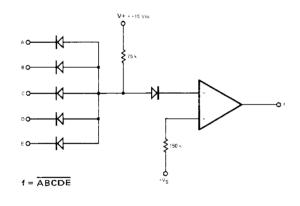

#### LOGIC OR GATE

### LOGIC NAND GATE (Large Fan In)

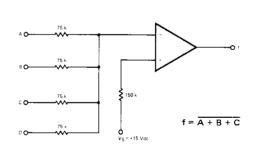

### LOGIC NOR GATE

#### R-S FLIP-FLOP

# STABLE MULTIVIBRATOR

#

### ZERO CROSSING DETECTOR

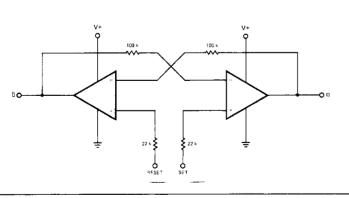

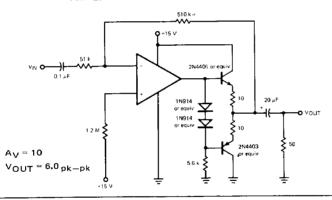

#### AMPLIFIER AND DRIVER FOR 50 $\Omega$ LINE

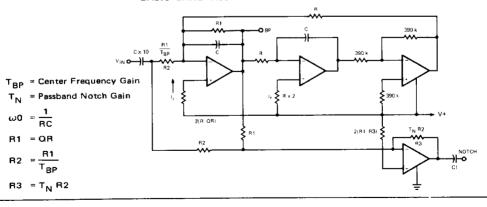

### BASIC BANDPASS AND NOTCH FILTER

| | <del>- ---</del>--