N-MOS VCS, ThinPak<sup>™</sup>

### Description

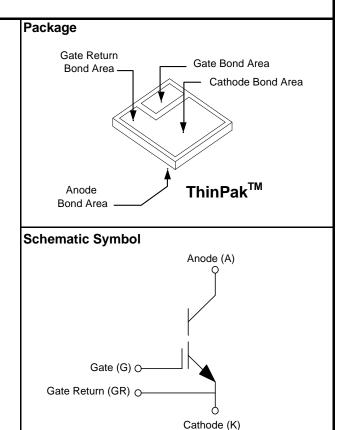

This voltage controlled Solidtron (VCS) discharge switch utilizes an n-type MOS-Controlled Thyristor mounted on a ThinPakTM, ceramic "chip-scale" hybrid.

The VCS features the high peak current capability and low Onstate voltage drop common to SCR thyristors combined with extremely high dl/dt capability. This semiconductor is intended for the control of high power circuits with the use of very small amounts of input energy and is ideally suited for capacitor discharge applications.

The ThinPak<sup>TM</sup> Package is a perforated, metalized ceramic substrate attached to the silicon using 302°C solder. An epoxy underfill is applied to protect the high voltage termination from debris. All exterior metal surfaces are tinned with 63pb/37sn solder providing the user with a circuit ready part. It's small size and low profile make it extremely attractive to high dl/dt applications where stray series inductance must be kept to a minimum.

#### Features

- 1400V Peak Off-State Voltage

- 32A Continuous Rating

- 4kA Surge Current Capability

- >100kA/uSec dl/dt Capability

- <100nSec Turn-On Delay</p>

- Low On-State Voltage

- MOS Gated Control

- Low Inductance Package

#### Absolute Maximum Ratings

|                                                                        | SYMBOL                          | VALUE | UNITS   |

|------------------------------------------------------------------------|---------------------------------|-------|---------|

| Peak Off-State Voltage                                                 | V <sub>DRM</sub>                | 1400  | V       |

| Peak Reverse Voltage                                                   | V <sub>RRM</sub>                | -5    | V       |

| Off-State Rate of Change of Voltage Immunity                           | dv/dt                           | 5000  | V/uSec  |

| Continuous Anode Current at 110°C                                      | I <sub>A110</sub>               | 32    | А       |

| Repetitive Peak Anode Current (Pulse Width=1uSec)                      | I <sub>ASM</sub>                | 4000  | А       |

| Rate of Change of Current                                              | dl/dt                           | 150   | kA/uSec |

| Continuous Gate-Cathode Voltage                                        | V <sub>GKS</sub>                | +/-20 | V       |

| Peak Gate-Cathode Voltage                                              | V <sub>GKM</sub>                | +/-25 | V       |

| Minimum Negative Gate-Cathode Voltage Required for Garanteed Off-State | $V_{\text{GK}(\text{OFF-MIN})}$ | -5    | V       |

| Maximum Junction Temperature                                           | T <sub>JM</sub>                 | 150   | °C      |

| Maximum Soldering Temperature (Installation)                           | 260                             | °C    |         |

This SILICON POWER product is protected by one or more of the following U.S. Patents:

| 5,521,436 | 5,446,316 | 5,105,536 | 5,209,390 | 4,958,211 | 5,206,186 | 4,857,983 | 5,082,795 | 4,644,637 |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 5,585,310 | 5,557,656 | 5,777,346 | 5,139,972 | 5,111,268 | 5,757,036 | 4,888,627 | 4,980,741 | 4,374,389 |

| 5,248,901 | 5,564,226 | 5,446,316 | 5,103,290 | 5,260,590 | 5,777,346 | 4,912,541 | 4,941,026 | 4,750,666 |

| 5,366,932 | 5,517,058 | 5,577,656 | 5,028,987 | 5,350,935 | 5,995,349 | 5,424,563 | 4,927,772 | 4,429,011 |

| 5,497,013 | 4,814,283 | 5,473,193 | 5,304,847 | 5,640,300 | 4,801,985 | 5,399,892 | 4,739,387 | 5,293,070 |

| 5,532,635 | 5,135,890 | 5,166,773 | 5,569,957 | 5,184,206 | 4,476,671 | 5,468,668 | 4,648,174 |           |

www.DataSheet4U.com

N-MOS VCS, ThinPak<sup>™</sup>

| Performance Characteristics T <sub>J</sub> =25°C unless otherwise specified |                      |                                                         |                                                  |      | Measurements |      |         |  |

|-----------------------------------------------------------------------------|----------------------|---------------------------------------------------------|--------------------------------------------------|------|--------------|------|---------|--|

| Parameters                                                                  | Symbol               | Test Conditions                                         |                                                  | Min. | Тур.         | Max. | Units   |  |

| Anode to Cathode Breakdown Voltage                                          | V <sub>(BR)</sub>    | V <sub>GK</sub> =-5, I <sub>A</sub> =1mA                |                                                  | 1400 |              |      | V       |  |

| Anode-Cathode Off-State Current                                             | i <sub>D</sub>       | V <sub>GE</sub> =-5V, V <sub>AK</sub> =1200V            | -5V, V <sub>AK</sub> =1200V T <sub>C</sub> =25°C |      | <10          | 100  | uA      |  |

|                                                                             |                      |                                                         | T <sub>C</sub> =150°C                            |      | 250          | 1000 | uA      |  |

| Gate-Cathode Turn-On Threshold Voltage                                      | V <sub>GK(TH)</sub>  | V <sub>AK</sub> =V <sub>GK</sub> , I <sub>AK</sub> =1mA |                                                  |      | 0.7          |      | V       |  |

| Gate-Cathode Leakage Current                                                | I <sub>GK(lkg)</sub> | V <sub>GK</sub> =+/-20V                                 |                                                  |      |              | 500  | nA      |  |

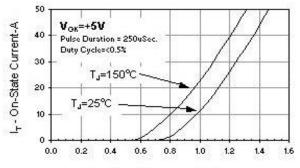

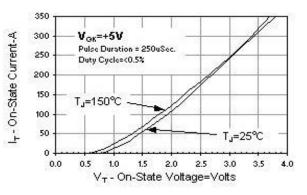

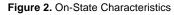

| Anode-Cathode On-State Voltage                                              | V <sub>T</sub>       | I <sub>T</sub> =32A, V <sub>GK</sub> =+5V               | T <sub>C</sub> =25°C                             |      | 1.5          | 2.0  | V       |  |

|                                                                             |                      | (See Figures 1,2 & 3)                                   | T <sub>c</sub> =150°C                            |      | 1.3          | 1.5  | V       |  |

| Input Capacitance                                                           | C <sub>ISS</sub>     |                                                         |                                                  |      | 6            |      | nF      |  |

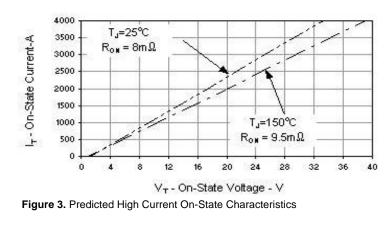

| Turn-on Delay Time                                                          | t <sub>D(ON)</sub>   | 0.2uF Capacitor Discharge                               |                                                  |      | 50           | 100  | nS      |  |

| Rate of Change of Current                                                   | dl/dt                | $T_J=25^{\circ}C$ , $V_{GK}=-5V$ to $+5V$               |                                                  |      | 75           |      | kA/uSec |  |

| Peak Anode Current                                                          | I <sub>P</sub>       | $V_{AK}$ =800V, RG=4.7 $\Omega$                         |                                                  |      | 3500         |      | А       |  |

| Discharge Event Energy                                                      | E <sub>DIS</sub>     | L <sub>S</sub> = 7nH (See Figures 4,5 & 6)              |                                                  |      | 32           |      | mJ      |  |

| Turn-on Delay Time                                                          | t <sub>D(ON)</sub>   | 0.2uF Capacitor Discharge                               |                                                  |      | 50           | 100  | nS      |  |

| Rate of Change of Current                                                   | dl/dt                | $T_J=150^{\circ}C$ , $V_{GK}=-5V$ to $+5V$              |                                                  |      | 110          |      | kA/uSec |  |

| Peak Anode Current                                                          | I <sub>P</sub>       | V <sub>AK</sub> =1200V, RG=4.7Ω                         |                                                  | 4000 |              |      | А       |  |

| Discharge Event Energy                                                      | E <sub>DIS</sub>     | L <sub>S</sub> = 7nH (See Figures 4,5 & 6)              |                                                  |      | 70           |      | mJ      |  |

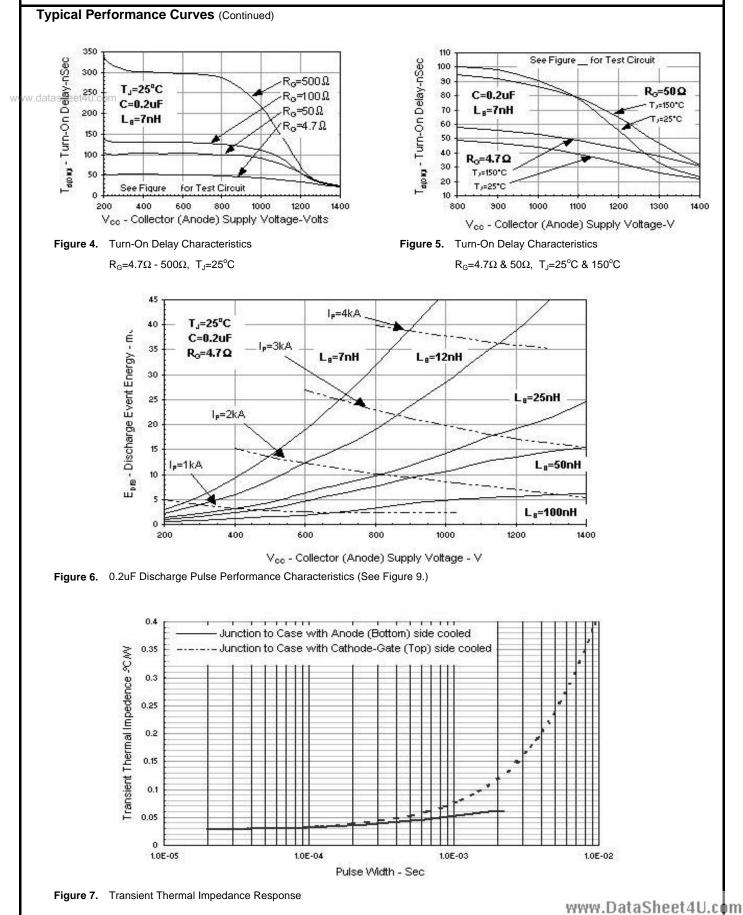

| Junction to Case Thermal Resistance                                         | $R_{	ext{	heta}JC}$  | Anode (bottom) side cooled (Note 1.)                    |                                                  |      | 0.08         |      | °C/W    |  |

| Junction to Case Thermal Resistance                                         | $R_{\theta JC}$      | Cathode-Gate (top) side cooled (Note 2.)                |                                                  |      | 1.5          |      | °C/W    |  |

Notes:

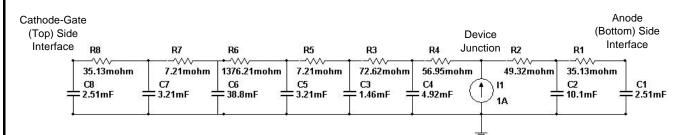

1. Case Exterior Assumed to be 0.002" of 63sn/37pb solder applied directly to Anode. (See Figure 7.)

2. Case Exterior Assummed to be 0.002" of 63sn/37pb solder applied directly to cathode bond area of thinPak. (See Figure 7.)

### Typical Performance Curves (unless otherwise specified)

Figure 1. On-State Characteristics

www.DataSheet4U.com

N-MOS VCS, ThinPak<sup>™</sup>

N-MOS VCS, ThinPak<sup>™</sup>

N-MOS VCS, ThinPak<sup>™</sup>

### **Application Notes**

A1. Junction Temperature Calculation

The figure below shows a lump model of the thermal properties of the size 4 thinPak packaged VCS, from the 2-mil solder w.datashon,the top of the lid on the left to the 2-mil solder on the bottom of the device on the right. By adding the user's lump model of the rest of the thermal system the user can calculate the junction and case temperature rise under any operating condition.

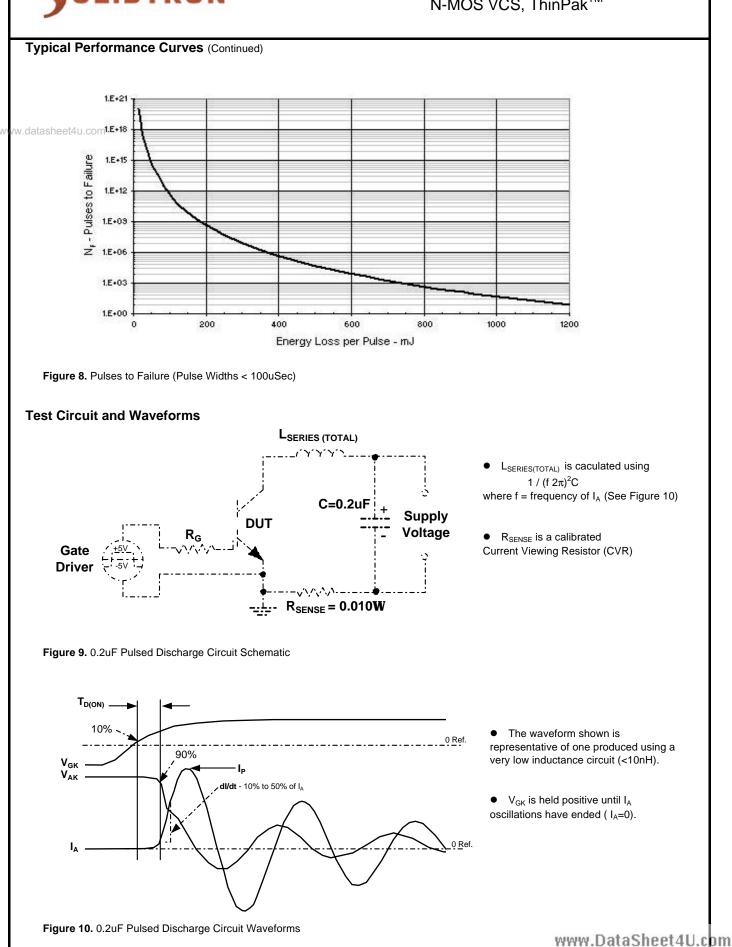

A2. Calculation of Pulses to Failure for Intermediate/Long Pulse Widths

The user may calculate the Number of Pulses to failure (N<sub>F</sub>) for long to intermediate pulse widths (not covered in the typical performance curve section) by applying the junction temperature rise (dT), calculated as described in A1, to the formula  $N_F$ =(300/dT)9.

A3. Use of Gate Return Bond Area.

The MCT was designed for high di/dt applications. An independent cathode connection or "Gate Return Bond Area" was provided to minimize the effects of rapidly changing Anode-Cathode current on the Gate control voltage, (V=L\*di/dt). It is therefore, critcal that the user utilize the Gate Return Bond Area as the point at which the gate driver reference (return) is attached to the VCS device.

### **Packaging and Handling**

1. All metal surfaces are tinned using 63pb/37sn solder.

2. Installation reflow temperature should not exceed 260°C or internal package degradation may result.

3. Package may be cooled from either top or bottom (See Figures 7 & A1 Application Notes.)

4. As with all MOS gated devices, proper handling procedures must be observed to prevent electrostatic discharge which may result in permanent damage to the gate of the device

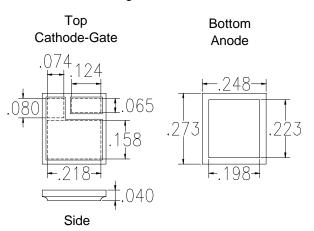

#### Package Dimensions