# LS5019 P-CHANNEL JFET

# Linear Systems replaces discontinued Siliconix 2N5019 The LS5019 is a single P-Channel JFET switch

This p-channel analog switch is designed to provide low on-resistance and fast switching.

The SOT-23 package provides ease of manufacturing, and a lower cost assembly option.

(See Packaging Information).

#### LS5019 Benefits:

- Low Insertion Loss

- No offset or error voltage generated by closed switch

- Purely resistive

#### LS5019 Applications:

- **Analog Switches**

- Commutators

- Choppers

| FEATURES                                     |                        |  |  |

|----------------------------------------------|------------------------|--|--|

| DIRECT REPLACEMENT FOR SILICONIX 2N5019      |                        |  |  |

| ZERO OFFSET VOLTAGE                          |                        |  |  |

| LOW ON RESISTANCE $r_{DS(on)} \le 150\Omega$ |                        |  |  |

| ABSOLUTE MAXIMUM RATINGS                     |                        |  |  |

| @ 25°C (unless otherwise noted)              |                        |  |  |

| Maximum Temperatures                         |                        |  |  |

| Storage Temperature                          | -55°C to +200°C        |  |  |

| Operating Junction Temperature               | -55°C to +200°C        |  |  |

| Maximum Power Dissipation                    | <                      |  |  |

| Continuous Power Dissipation                 | 500mW                  |  |  |

| MAXIMUM CURRENT                              |                        |  |  |

| Gate Current (Note 1)                        | I <sub>G</sub> = -50mA |  |  |

| MAXIMUM VOLTAGES                             |                        |  |  |

| Gate to Drain Voltage                        | V <sub>GDS</sub> = 30V |  |  |

| Gate to Source Voltage                       | V <sub>GSS</sub> = 30V |  |  |

### LS5019 ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted)

| SYMBOL              | CHARACTERISTIC                                      | MIN | TYP. | MAX               | UNITS | CONDITIONS                       |

|---------------------|-----------------------------------------------------|-----|------|-------------------|-------|----------------------------------|

| $BV_{GSS}$          | Gate to Source Breakdown Voltage                    | 30  |      |                   |       | $I_{G} = 1\mu A$ , $V_{DS} = 0V$ |

| $V_{GS(off)}$       | Gate to Source Cutoff Voltage                       |     |      | 5                 | V     | $V_{DS} = -15V, I_{D} = -1\mu A$ |

| $V_{DS(on)}$        | Drain to Source On Voltage                          |     |      | -0.5              |       | $V_{GS} = 0V$ , $I_D = -3mA$     |

| I <sub>DSS</sub>    | Drain to Source Saturation Current (Note 2)         | -5  |      |                   | mA    | $V_{DS} = -20V, V_{GS} = 0V$     |

| I <sub>GSS</sub>    | Gate Reverse Current                                |     |      | 2                 | _nA   | $V_{GS} = 15V, V_{DS} = 0V$      |

| I <sub>D(off)</sub> | Drain Cutoff Current                                |     |      | -10               |       | $V_{DS} = -15V, V_{GS} = 12V$    |

|                     | ' 4 0 7                                             |     |      | -10               | μA    | $V_{DS} = -15V, V_{GS} = 7V$     |

| I <sub>DGO</sub>    | D <mark>ra</mark> in Re <mark>v</mark> erse Current |     |      | -2                | nA    | $V_{DG} = -15V, I_{S} = 0A$      |

| r <sub>DS(on)</sub> | Drain to Source On Resistance                       |     |      | 1 <mark>50</mark> | Ω     | $I_D = -1mA$ , $V_{GS} = 0V$     |

## LS5019 DYNAMIC ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted)

| Į | SYMBOL              | CHARACTERISTIC                | MIN | TYP. | MAX | UNITS | CONDITIONS                                   |

|---|---------------------|-------------------------------|-----|------|-----|-------|----------------------------------------------|

|   | r <sub>DS(on)</sub> | Drain to Source On Resistance | -   |      | 150 | Ω     | $I_D = 0A$ , $V_{GS} = 0V$ , $f = 1kHz$      |

| ĺ | $C_{iss}$           | Input Capacitance             | -   |      | 45  | pF    | $V_{DS} = -15V$ , $V_{GS} = 0V$ , $f = 1MHz$ |

| Ī | $C_{rss}$           | Reverse Transfer Capacitance  |     |      | 10  |       | $V_{DS} = 0V$ , $V_{GS} = 7V$ , $f = 1MHz$   |

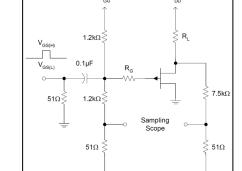

#### LS5019 SWITCHING CHARACTERISTICS @ 25°C (unless otherwise noted)

| SYMBOL              | CHARACTERISTIC     |     | UNITS | CONDITIONS       |                       |

|---------------------|--------------------|-----|-------|------------------|-----------------------|

| t <sub>d(on)</sub>  | Turn On Time       | 15  | ns    |                  | $V_{GS}(L) = 7V$      |

| t <sub>r</sub>      | Turn On Rise Time  | 75  |       | $V_{GS}(H) = 0V$ |                       |

| t <sub>d(off)</sub> | Turn Off Time      | 25  |       | 115              | See Switching Circuit |

| t <sub>f</sub>      | Turn Off Fall Time | 100 |       |                  |                       |

Note 1 - Absolute maximum ratings are limiting values above which LS5019 serviceability may be impaired.

## **LS5019 SWITCHING CIRCUIT PARAMETERS**

| V <sub>DD</sub>    | -6V   |

|--------------------|-------|

| V <sub>GG</sub>    | 8V    |

| R <sub>L</sub>     | 1.8kΩ |

| $R_G$              | 390Ω  |

| I <sub>D(on)</sub> | -3mA  |

Micross Components Europe

Available Packages:

LS5019 in SOT-23 LS5019 in bare die.

Please contact Micross for full package and die dimensions

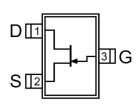

SOT-23 (Top View)

# **SWITCHING TEST CIRCUIT**

Tel: +44 1603 788967

Email: chipcomponents@micross.com Web: http://www.micross.com/distribution

Information furnished by Linear Integrated Systems and Micross Components is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

Note 2 – Pulse test: PW≤ 300 us. Duty Cycle ≤ 3%