# ICs for Communications

ISDN Echocancellation Circuit for NT and Terminal Applications IEC-Q NTE

PSB 21910 Version 5.1

Delta Sheet 01.97

| PSB 21910<br>Revision History:   |                             | Current Version: 01.97                       |

|----------------------------------|-----------------------------|----------------------------------------------|

| Previous Ver                     | sion: none                  |                                              |

| Page<br>(in previous<br>Version) | Page<br>(in new<br>Version) | Subjects (major changes since last revision) |

|                                  |                             |                                              |

|                                  |                             |                                              |

#### Edition 01.97

This edition was realized using the software system FrameMaker®.

Published by Siemens AG, HL IT

© Siemens AG 1997.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose! Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

**Overview**

#### 1 Overview

The PSB 21910 IEC-Q NTE Version 5.1 is a specific version of the PEB 2091 IEC-Q for terminal and PBX applications. It features all necessary functions required for NTs and terminal applications like PC add-on cards and terminal adapters. This Delta Sheet refers to the IEC-Q V 4.3 User's Manual 2.95, IEC-Q V4.4 and V5.1 Delta Sheet and IEC-Q V5.1 Errata Sheet.

# ISDN Echocancellation Circuit for NT and Terminal Applications IEC-Q NTE

**PSB 21910**

#### **Delta Sheet for the Version 5.1**

**CMOS**

#### 2 Features

- Compatible to PEB 2091 IEC-Q V5.1 in NT modes and TE mode

- IOM-2 interface in NT mode compatible to PEB 2081 (SBCX)

- IOM-2 interface in TE mode compatible to PSB2186 and PSB 7110 for D-channel access

The IEC-Q NTE V 5.1 comes in a PLCC-44 package or a T-QFP 64 package.

PSF version with extended temperature range (-40 ... +85 C) available on request.

| Туре            | Ordering Code | Package  |

|-----------------|---------------|----------|

| PSB 21910F V5.1 | Q 67101-H6886 | T-QFP 64 |

| PSB 21910N V5.1 | Q 67107-H6873 | P-LCC-44 |

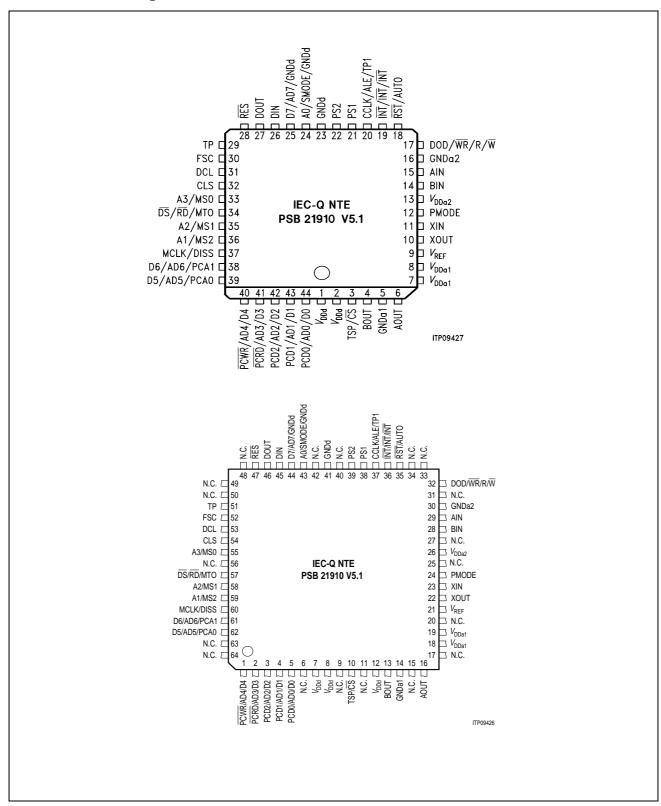

### 2.1 Pin Configuration

Figure 1

Pin Configuration P-LCC-44 and T-QFP 64 Package (top view)

### 2.2 Pin Definitions and Functions

Pin names and pin numbers of the P-LCC 44 package in stand alone mode are as in former versions of the IEC-Q.

| Pin No.  | Pin No. | Symbol | Input (I)  | Function |

|----------|---------|--------|------------|----------|

| P-LCC-44 | T-QFP64 |        | Output (O) |          |

### **Power Supply Pins**

| 1, 2 | 7, 8, 12 | $V_{DDD}$  | I | 5 V ± 5 % digital supply voltage                                                  |

|------|----------|------------|---|-----------------------------------------------------------------------------------|

| 5    | 14       | GNDA1      | 1 | 0 V analog                                                                        |

| 7, 8 | 18, 19   | $V_{DDA1}$ | 1 | 5 V ± 5 % analog supply voltage                                                   |

| 9    | 21       | $V_{REF}$  | 0 | $V_{REF}$ pin to buffer internally generated voltage with capacitor 100 nF vs GND |

| 13   | 26       | $V_{DDA2}$ | 1 | 5 V ± 5 % analog supply voltage                                                   |

| 16   | 30       | GNDA2      | I | 0 V analog                                                                        |

| 23   | 41       | GNDD       | I | 0 V digital                                                                       |

### **Mode Selection Pins**

| 3  | 10 | TSP  | I | Single pulse test mode (Stand alone mode): For activation refer to table 2 on page 48 in the IEC-Q V 4.3 user's manual. When active, alternating 2.5 V pulses are issued in 1.5 ms intervals. Tie to GND if not used. |

|----|----|------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3  | 10 | CS   | I | Chip select (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                                                |

| 18 | 35 | AUTO | I | Auto (Stand alone mode): Selection between auto- and transparent mode for EOC channel processing. (Automode = (1))                                                                                                    |

| 18 | 35 | RST  | 0 | Reset output (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                                                               |

**PSB 21910**

# **SIEMENS**

**Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol   | Input (I)<br>Output (O) | Function                                                                                                       |

|---------------------|--------------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| 24                  | 43                 | GNDd     | I                       | <b>GNDd (Stand alone mode):</b> Must be connected to GNDd in stand alone mode.                                 |

| 24                  | 43                 | SMODE    | I                       | <b>Serial mode pin:</b> SMODE = 1 selects serial mode, SMODE = 0 enables the multiplexed mode.                 |

| 24                  | 43                 | A0       | I                       | Address bus pin (Demultiplexed mode)                                                                           |

| 25                  | 44                 | GNDd     | 1                       | <b>GNDd (Stand alone mode):</b> Must be connected to GNDd in stand alone mode.                                 |

| 25                  | 44                 | D7       | I/O                     | Data bus pin (Multiplexed, demultiplexed modes)                                                                |

| 25                  | 44                 | not used | I                       | (Serial mode) tie to GND.                                                                                      |

| 33                  | 55                 | MS0      | I                       | Mode Selection 0 (Stand alone mode)                                                                            |

| 33                  | 55                 | not used | I                       | (Multiplexed mode) tie to GND.                                                                                 |

| 33                  | 55                 | A3       | I                       | Address bus pin (Demultiplexed mode).                                                                          |

| 33                  | 55                 | not used | I                       | (Serial mode) tie to GND.                                                                                      |

| 35                  | 58                 | MS1      | I                       | Mode Selection 1 (Stand alone mode)                                                                            |

| 35                  | 58                 | not used | I/O                     | (Multiplexed mode) tie to GND.                                                                                 |

| 35                  | 58                 | A2       | I/O                     | Address bus pin (Demultiplexed mode).                                                                          |

| 35                  | 58                 | CDOUT    | 0                       | Controller Data Out (Serial mode): CCLK determines the data rate. CDOUT is "high Z" if no data is transmitted. |

| 36                  | 59                 | MS2      | I                       | Mode Selection 2 (Stand alone mode)                                                                            |

| 36                  | 59                 | not used | I                       | (Multiplexed mode) tie to GND.                                                                                 |

| 36                  | 59                 | A1       | I                       | Address bus pin (Demultiplexed mode).                                                                          |

**PSB 21910**

# **SIEMENS**

**Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                         |

|---------------------|--------------------|--------|-------------------------|------------------------------------------------------------------|

| 36                  | 59                 | CDIN   | I                       | Controller Data In (Serial mode): CCLK determines the data rate. |

| 28                  | 47                 | RES    | I                       | Reset: Low active, must be (0) at least for 10 ns.               |

### **Power Controller Interface Pins**

| Data Bus of power controller interface 0 (Stand alone mode): internal pull-up. | I/O | PCD0     | 5  | 44 |

|--------------------------------------------------------------------------------|-----|----------|----|----|

| Address/Data bus pin (Multiplexed mode)                                        | I/O | AD0      | 5  | 44 |

| Data bus pin (Demultiplexed mode)                                              | I/O | D0       | 5  | 44 |

| (Serial mode) tie to GND.                                                      | I   | not used | 5  | 44 |

| Data Bus of power controller interface 1 (Stand alone mode): Internal pull-up. | I/O | PCD1     | 4  | 43 |

| Address/Data bus pin (Multiplexed mode)                                        | I/O | AD1      | 4  | 43 |

| Data bus pin (Demultiplexed mode)                                              | I/O | D1       | 4  | 43 |

| (Serial mode) tie to GND.                                                      | 1   | not used | 4  | 43 |

| Data Bus of power controller interface 2 (Stand alone mode): Internal pull-up. | I/O | PCD2     | 3  | 42 |

| Address/Data bus pin (Multiplexed mode)                                        | I/O | AD2      | 3  | 42 |

| Data bus pin (Demultiplexed mode)                                              | I/O | D2       | 3  | 42 |

| (Serial mode) tie to GND.                                                      | I   | not used | 3  | 42 |

| Address bus of power controller interface (Stand alone mode).                  | 0   | PCA0     | 62 | 39 |

| Data bus pin (Multiplexed, demultiplexed modes)                                | I/O | D5       | 62 | 39 |

| (Serial mode) tie to GND.                                                      | I   | not used | 62 | 39 |

| Address bus of power controller interface (Stand alone mode).                  | 0   | PCA1     | 61 | 38 |

PSB 21910

# **SIEMENS**

**Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol   | Input (I)<br>Output (O) | Function                                                                                                                                                                     |

|---------------------|--------------------|----------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38                  | 61                 | D6       | I/O                     | Data bus pin (Multiplexed, demultiplexed modes)                                                                                                                              |

| 38                  | 61                 | not used | I                       | (Serial mode) tie to GND.                                                                                                                                                    |

| 41                  | 2                  | PCRD     | 0                       | Power controller bus read request (Stand alone mode): Low active.                                                                                                            |

| 41                  | 2                  | AD3      | I/O                     | Address/Data bus pin (Multiplexed mode)                                                                                                                                      |

| 41                  | 2                  | D3       | I/O                     | Data bus pin (Demultiplexed mode)                                                                                                                                            |

| 41                  | 2                  | not used | 1                       | (Serial mode) tie to GND.                                                                                                                                                    |

| 40                  | 1                  | PCWR     | 0                       | Power controller bus write request (Stand alone mode): Low active.                                                                                                           |

| 40                  | 1                  | D4       | I/O                     | Data bus pin (Multiplexed and demultiplexed modes)                                                                                                                           |

| 40                  | 1                  | not used | 1                       | (Serial mode) tie to GND.                                                                                                                                                    |

| 19                  | 36                 | INT      |                         | Interrupt (Stand alone mode):<br>Change-sensitive. After a change of<br>level has been detected the C/I code<br>"INT" will be issued on IOM. Tie to<br>GND during operation. |

| 19                  | 36                 | ĪNT      | 0                       | Interrupt line (Multiplexed, demultiplexed and serial modes): Low active.                                                                                                    |

| 37                  | 60                 | DISS     | 0                       | <b>Disable power supply (Stand alone mode):</b> This pin is set to '1' after receipt of MON-0 LBBD in auto-mode.                                                             |

| 37                  | 60                 | MCLK     | 0                       | Microprocessor clock output (Multiplexed, demultiplexed and serial modes): provided with four programmable clock rates: 7.68 MHz, 3.84 MHz, 1.92 MHz and 0.96 MHz.           |

| 21                  | 38                 | PS1      | I                       | <b>Power status 1 (primary)</b> . '1' indicates primary power supply ok. The pin value is identical to the overhead bit 'PS1' value.                                         |

**Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                         |

|---------------------|--------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 22                  | 39                 | PS2    |                         | Power status 2 (secondary). '1' indicates secondary power supply ok. The pin value is identical to the overhead bit 'PS2' value. |

### **Miscellaneous Function Pins**

| 10 | 22 | XOUT     | 0 | <b>Crystal OUT:</b> 15.36-MHz crystal is connected with 30 pF in parallel. Leave open if not used.                                                                           |

|----|----|----------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | 23 | XIN      | I | <b>Crystal IN:</b> External 15.36-MHz clock signal or 15.36-MHz crystal with 30 pF in parallel is connected.                                                                 |

| 17 | 32 | DOD      | I | <b>DOUT</b> open drain (Stand alone mode): Select open drain with DOD = (1) (external pull-up resistor required) and tristate with DOD = (0).                                |

| 17 | 32 | WR       | I | Write (Siemens/Intel multiplexed and demultiplexed modes): indicates a write operation, active low.                                                                          |

| 17 | 32 | R/W      | I | Read/Write (Motorola demultiplexed mode): indicates a read (high) or write (low) operation.                                                                                  |

| 17 | 32 | not used | I | (Serial mode) tie to GND.                                                                                                                                                    |

| 29 | 51 | TP       | I | <b>Test pin:</b> Not available to user. Do not connect. Internal pull-down resistor.                                                                                         |

| 20 | 37 | TP1      | I | Test pin (Stand alone mode): Not available to user. Do not connect. Internal pull-down resistor.                                                                             |

| 20 | 37 | ALE      | I | Address Latch Enable (Multiplexed mode): In the Siemens/Intel μP interface modes a high indicates an address on the AD03 pins which is latched with the falling edge of ALE. |

### **Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol   | Input (I)<br>Output (O) | Function                                                                                                                                                                                                     |

|---------------------|--------------------|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20                  | 37                 | ALE      | I                       | Address Latch Enable (Demultiplexed mode): ALE tied to GND selects the Siemens/Intel type. ALE tied to VDD selects the Motorola type.                                                                        |

| 20                  | 37                 | CCLK     | I                       | Controller data clock (Serial mode): Shifts data from or to the device.                                                                                                                                      |

| 32                  | 54                 | CLS      | 0                       | <b>Clock Signal:</b> A 7.68MHz clock, synchronous to the U-interface, is provided on this pin.                                                                                                               |

| 12                  | 24                 | PMODE    | I                       | Processor Interface Enable: Setting PMODE to "1" enables the Processor Interface (Multiplexed, demultiplexed and serial modes). Tie to GND or do not connect to select stand alone mode. Internal pull down. |

| 34                  | 57                 | МТО      | I                       | Monitor procedure timeout (Stand alone mode): Disables the internal 6 ms monitor timeout when set to (1). Internal pull-down resistor.                                                                       |

| 34                  | 57                 | RD       | I                       | Read (Siemens/Intel multiplexed and demultiplexed modes): indicates a read operation, active low.                                                                                                            |

| 34                  | 57                 | DS       |                         | Data Strobe (Motorola demultiplexed mode): indicates a data transfer, active low.                                                                                                                            |

| 34                  | 57                 | not used | I                       | (Serial mode) tie to GND.                                                                                                                                                                                    |

### IOM<sup>®</sup>-Pins

| 31 | 53 | DCL | I/O | Data clock: Clock output 512 or 1536 |

|----|----|-----|-----|--------------------------------------|

|    |    |     |     | kHz. Remains input in processor mode |

|    |    |     |     | until programming of STCR register.  |

### **Features**

| Pin No.<br>P-LCC-44 | Pin No.<br>T-QFP64 | Symbol | Input (I)<br>Output (O) | Function                                                                                                                                                                                                      |

|---------------------|--------------------|--------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30                  | 52                 | FSC    | I/O                     | Frame synchronization clock: The start of the B1-channel in time-slot 0 is marked. FSC = (1) for one DCL-period indicates a superframe marker. FSC = (1) for at least two DCL-periods marks a standard frame. |

|                     |                    |        |                         | Remains input in processor mode until programming of STCR register.                                                                                                                                           |

| 26                  | 45                 | DU     | I                       | <b>Data Upstream:</b> Input of IOM-data synchronous to DCL-clock.                                                                                                                                             |

| 27                  | 46                 | DD     | 0                       | <b>Data Downstream:</b> Output of IOM-data synchronous to DCL-clock.                                                                                                                                          |

### **U-Interface Pins**

| 15 | 29 | AIN  | I | Differential<br>Connect to hy | <b>U-Interface</b><br>brid. | input:  |

|----|----|------|---|-------------------------------|-----------------------------|---------|

| 14 | 28 | BIN  | I | Differential<br>Connect to hy | <b>U-Interface</b> brid.    | input:  |

| 6  | 16 | AOUT | 0 | Differential<br>Connect to hy | <b>U-Interface</b><br>brid. | output: |

| 4  | 13 | BOUT | 0 | Differential<br>Connect to hy | <b>U-Interface</b><br>brid. | output: |

### 2.3 Operation Modes

|         | Input Pins |     |     | Output Pins U<br>Synchronized |            |                            |

|---------|------------|-----|-----|-------------------------------|------------|----------------------------|

| Mode    | MS2        | MS1 | MS0 | DCL<br>OUT                    | CLS<br>OUT | Super-<br>frame-<br>marker |

| NT      | 0          | 0   | 0   | 512                           | 7680       | no                         |

| NT      | 1          | 0   | 0   | 512                           | 7680       | yes                        |

| NT-Auto | 0          | 0   | 1   | 512                           | 7680       | no                         |

| TE      | 0          | 1   | 0   | 1536                          | 7680       | no                         |

| TE      | 1          | 1   | 0   | 1536                          | 7680       | yes                        |

| NT-RP   | 1          | 0   | 1   | 512                           | 7680       | yes                        |

#### **Table 1 Modes of Operation**

The IEC-Q NTE supports the operating modes NT, NT-Auto, TE and NT-Repeater. The selection is done via the MS2-0 inputs in stand alone mode and via the register bits MS2-0 in the STCR register in processor mode.

### 2.4 STCR Register

Default: C4<sub>H</sub>

Name: 7 6 5 4 3 2 1 0 Default TEST2 **STCR** TEST1 MS2 MS1 MS0 TM1 TM2 **AUTO** C4<sub>H</sub>

The <u>Status Control Register</u> (STCR) selects the operating modes of the IEC-Q NTE V 5.1 as given in the section 2.2 on page 47 of the IEC-Q V 4.3 user's manual.

**TEST1:** Test Bit 1

Must be written to '0' together with mode setting of MS2-0 after

reset.

**TEST2:** Test Bit 2

Must be written to '0' together with mode setting of MS2-0 after

reset.

MS2: <u>Mode Selection 2</u>

Selects operation mode according to table above.

MS1: <u>Mode selection 1</u>

Selects operation mode according to table above.

MS0: Mode Selection 0

Selects operation mode according to table above.

TM1: Test-Mode-Bit 1

This bit determines, in combination with STCR:TM2, the

operation modes. See table below.

TM2: Test-Mode-Bit 2

This bit determines, in combination with STCR:TM1, the

operation modes. See table below.

| Test-Mode          | TM1 | TM2 |

|--------------------|-----|-----|

| Normal Mode        | 1   | 0   |

| Send Single-Pulses | 1   | 1   |

| Data-Through       | 0   | 1   |

AUTO: Selection between auto- and transparent mode

AUTO = 1 sets the automode for EOC channel processing.

AUTO = 0 sets the transparent mode for EOC channel

processing.

**Package Outlines**

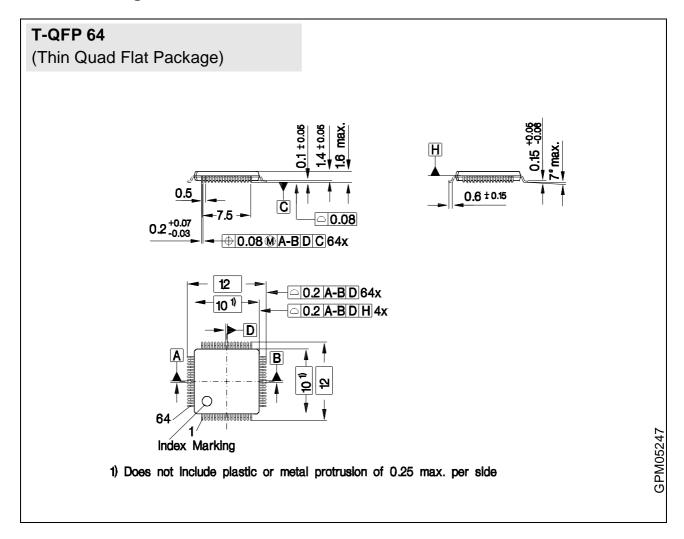

### 3 Package Outlines

For package outlines of the P-LCC 44 package please refer to the PEB 2091 V4.3 User's Manual 2.95, page 217.

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm