### AM-FM RADIO FREQUENCY SYNTHESIZER

- FM INPUT AND PRECOUNTER FOR UP TO 140MHz

- AM INPUT FOR UP TO 40MHz

- 6-BIT SWALLOW COUNTER, 8-BIT PRO-GRAMMABLE COUNTER FOR FM AND SW

- 14-BIT PROGRAMMABLE COUNTER FOR LW AND MW

- THREE WIRES 8-BIT SERIAL INTERFACE

- ON-CHIP REFERENCE OSCILLATOR AND COUNTER

- PROGRAMMABLE SCANNING STEPS FOR AM AND FM

- DIGITAL PHASE DETECTOR AND LOOP FIL-TER

- TWO SEPARATE FREE PROGRAMMABLE FILTER APPLICATIONS AVAILABLE

- TUNING VOLTAGE OUTPUT 0.5 TO 9.5V

- PROGRAMMABLE CURRENT SOURCES TO SET THE LOOP GAIN

- ON-CHIP POWER ON RESET

- STANDBY MODE

#### **DESCRIPTION**

The TDA7326 is a PLL frequency synthesizer in CMOS technology that performs all the function of a PLL radio tuning system for FM and AM (LW, MW, SW)

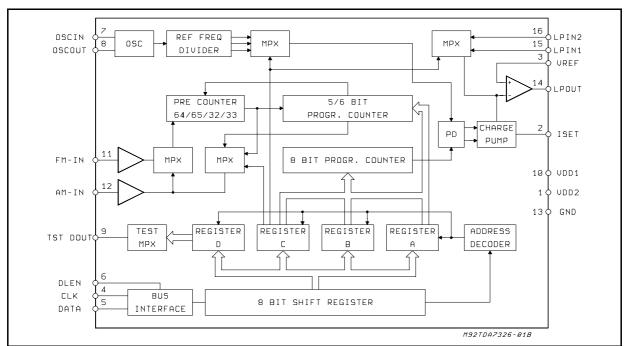

#### **BLOCK DIAGRAM**

September 2003 1/16

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                             | Parameter           | Value                              | Unit |

|------------------------------------|---------------------|------------------------------------|------|

| V <sub>DD1</sub> - V <sub>SS</sub> | Supply Voltage      | - 0.3 to + 7                       | V    |

| V <sub>DD2</sub> - V <sub>SS</sub> | Supply Voltage      | - 0.3 to + 12                      | V    |

| $V_{IN}$                           | Input Voltage       | VSS - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| V <sub>OUT</sub>                   | Output Voltage      | VSS - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| I <sub>IN</sub>                    | Input Current       | - 10 to + 10                       | mA   |

| l <sub>OUT</sub>                   | Output Current      | - 10 to + 10                       | mA   |

| T <sub>stg</sub>                   | Storage Temperature | - 55 to + 125                      | °C   |

| T <sub>A</sub>                     | Ambient Temperature | -40 to + 85                        | °C   |

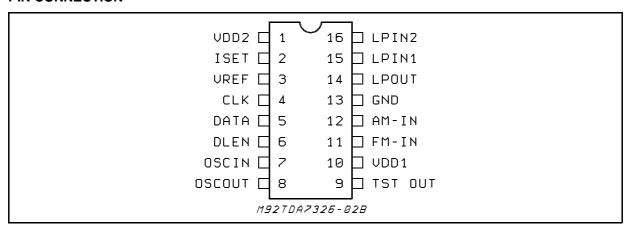

#### **PIN CONNECTION**

#### THERMAL DATA

| Symbol                | Parameter                                     | DIP 16 | SO 16L | Unit |

|-----------------------|-----------------------------------------------|--------|--------|------|

| R <sub>th j-amb</sub> | Rth j-amb Thermal Resistance Junction-ambient |        | 200    | °C/W |

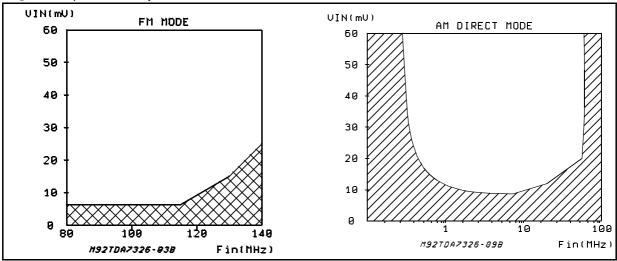

Figure 1:Input Sensitivity

## **ELECTRICAL CHARACTERISTICS** (Tamb = $25^{\circ}$ C ; VDD1 = 5V; VDD2 = 9V fosc = 4MHz; RISET = 68K $\Omega$ ; unless otherwise specified.)

| Symbol           | Parameter Test Condition |                                          | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|------------------------------------------|------|------|------|------|

| V <sub>DD1</sub> | Supply Voltage           |                                          | 4.5  | 5.0  | 5.5  | V    |

| V <sub>DD2</sub> | Supply Voltage           |                                          |      | 9.0  | 10.0 | V    |

| IDD1 FM          | Supply Current           | no output load, FM mode,<br>fin = 100MHz |      | 18   | 25   | mA   |

| IDD1 AM          | Supply Current           | no output load, AM mode, fin = 1MHz      |      | 5    | 10   | mA   |

| IDD1 STB         | Supply Current           | Standby mode                             |      | 3    | 20   | μΑ   |

| IDD2             | Supply Current           |                                          | 0.5  | 2    | 3    | mA   |

| VREF             | Voltage at pin 3         |                                          | 3.0  | 3.5  | 4.0  | V    |

| Viset            | Voltage at pin 2         | RiSET = 68KΩ                             | 7.0  | 8.0  | 9.0  | V    |

#### **RF INPUT** (AMIN FMIN)

| fiAM | Input Frequency AM | Direct Mode, V <sub>in</sub> = 50mV  | 0.5 |      | 20  | MHz   |

|------|--------------------|--------------------------------------|-----|------|-----|-------|

|      |                    | Swallow Mode, V <sub>in</sub> = 50mV | 16  |      | 40  | MHz   |

| fiFM | Input Frequency FM | Sinus, V <sub>in</sub> = 50mV        | 30  |      | 140 | MHz   |

| ViAM | Input Voltage AM   | Direct Mode<br>0.6 to 16MHz (Sinus)  | 40  |      | 600 | mVrms |

|      |                    | Swallow Mode<br>16 to 40MHz (Sinus)  | 40  |      | 600 | mVrms |

| ViFM | Input Voltage FM   | 70 to 120MHz (Sinus)                 | 30  |      | 600 | mVrms |

| Zin  | Input Impedance FM | fin = 120MHz                         |     | 200  |     | Ω     |

| Zin  | Input Impedance AM | fin = 12MHz                          |     | 1400 |     | Ω     |

#### **OSCILLATOR**

| fosc        | Oscillator Frequency |                 |     | 4 |           | MHz |

|-------------|----------------------|-----------------|-----|---|-----------|-----|

| <b>t</b> bu | Built Up Time        | Euro-Quartz ITT |     |   | 100       | ms  |

| Cin         | Internal Capacitance |                 |     | 9 |           | pF  |

| Соит        | Internal Capacitance |                 |     | 9 |           | pF  |

| Zin         | Input Impedance      |                 |     | 4 | 15        | ΚΩ  |

| Vin         | Input Voltage        |                 | 0.5 |   | $V_{DD1}$ | Vpp |

#### **PLL CHARACTERISTICS**

| fstep | Step Width AM    | 1/2.5   | KHz |

|-------|------------------|---------|-----|

| fstep | Step Width FM    | 12.5/25 | KHz |

| fref  | Ref Frequency AM | 1/2.5   | KHz |

| fref  | Ref Frequency FM | 12.5/25 | KHz |

#### **LOOP FILTER INPUT** (LPIN1, LPIN2 = PIN 15,16)

| -lin | Input Leakage Current | VIN = Vss; Phase Detector<br>Output = Tristate | -1 | -0.1 |    | μΑ |

|------|-----------------------|------------------------------------------------|----|------|----|----|

| lin  | Input Leakage Current | VIN = VDD; Phase Detector<br>Output = Tristate |    | 0.1  | +1 | μΑ |

## **ELECTRICAL CHARACTERISTICS** (continued) **LOOP FILTER OUTPUT** (LPOUT = PIN 14)

| Symbol          | symbol Parameter Test Condition                 |                                      | Min.    | Тур.  | Max.     | Unit     |

|-----------------|-------------------------------------------------|--------------------------------------|---------|-------|----------|----------|

| VOL             | Output Voltage Low                              | ILOAD = 0.2mA VDD2; = 10V            |         | 0.5   | 0.8      | V        |

| Vон             | Output Voltage High                             | -ILOAD = 0.2mA VDD2; = 10V           | 9       | 9.5   |          | V        |

| CHARGE F        | PUMP CURRENT GENERATION                         | <b>N</b> (LPIN1, LPIN2 = PIN 15, 16) |         |       |          |          |

| İsi             | Sink Current LPIN1,2                            | CURR1 = 0, CURR2 = 0                 | 2       | 5     | 7        | μΑ       |

|                 |                                                 | CURR1 = 0, CURR2 = 1                 | 120     | 200   | 280      | μΑ       |

|                 |                                                 | CURR1 = 1, CURR2 = 1                 | 180     | 300   | 420      | μΑ       |

|                 |                                                 | CURR1 = 1, CURR2 = 0                 | 370     | 500   | 630      | μΑ       |

| -Iso            | Source Current LPIN1,2                          | CURR1 = 0, CURR2 = 0                 | 2       | 5     | 7        | μΑ       |

|                 |                                                 | CURR1 = 0, CURR2 = 1                 | 120     | 200   | 280      | μΑ       |

|                 |                                                 | CURR1 = 1, CURR2 = 1                 | 180     | 300   | 420      | μΑ       |

|                 |                                                 | CURR1 = 1, CURR2 = 0                 | 370     | 500   | 630      | μΑ       |

| DOUT1 OP        | ENDRAIN OUTPUT(PIN 9)                           |                                      |         |       |          | •        |

| VOL             | Output Voltage Low                              | ILOAD = 1mA                          |         | 0.2   | 0.5      | V        |

| BUS INTER       | RFACE                                           |                                      |         | I.    | I.       |          |

| -lıL            | Input Leakage Current                           | VIN = Vss                            | -1      | 0.1   | 1        | μΑ       |

| Іін             | Input Leakage Current                           | VIN = Vss                            | -1      | 0.1   | 1        | μΑ       |

| VIH             | Input Voltage High                              | Leading edge                         | 3.4     | 4.0   |          | V        |

| VIL             | Input Voltage Low                               | Leading edge                         |         | 1.0   | 1.6      | V        |

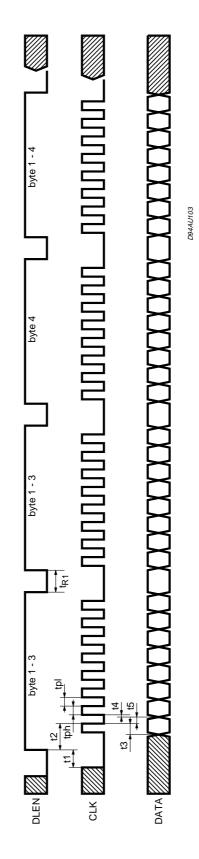

| BUS INTER       | RFACE, WAITING TIME (see fi                     | g. 5) The Data is Acquired at t      | he High | → Low | Clock Tr | ansition |

| t1              | CLK Low to DLEN L $\rightarrow$ H               |                                      | 0.2     |       |          | μs       |

| t3              | DATA Transition to CLK $H \rightarrow L$        |                                      | 0.1     |       |          | μs       |

| <b>t</b> 5      | CLK $H \rightarrow L$ to DATA Transition        |                                      | 0.4     |       |          | μs       |

| BUS INTER       | RFACE, DATA REPETITION T                        | IME (see fig. 5)                     |         |       |          |          |

| t <sub>r1</sub> | Release Time Between 2 bytes, except byte 4     |                                      | 5       |       |          | μs       |

| t <sub>r2</sub> | Release Time after the                          | FM mode                              | 180     |       |          | μs       |

|                 | transmission of byte 4                          | AM mode                              | 2       |       |          | ms       |

| BUS INTER       | RFACE, SETUP TIME (see fig.                     | 5)                                   |         |       |          |          |

| t <sub>2</sub>  | DLEN High to CLK $L \rightarrow H$              |                                      | 0.1     |       |          | μs       |

| BUS INTER       | RFACE, HOLD TIME (see fig. 5                    | i)                                   | •       |       |          |          |

| t <sub>4</sub>  | DATA Transition to CKL L → H                    |                                      | 0       |       |          | μs       |

| t <sub>6</sub>  | CLK $H \rightarrow L$ to DLEN $H \rightarrow L$ |                                      | 0.4     |       |          | μs       |

| fclk            | CLK Frequency                                   |                                      |         |       | 500      | KHz      |

|                 | Duty Cycle                                      |                                      |         | 50    |          | %        |

| tpl             | Clock Pulse Low                                 |                                      | 1       |       |          | μs       |

| <b>t</b> ph     | Clock Pulse High                                |                                      | 1       |       |          | μs       |

#### 2.0 GENERAL DESCRIPTION

This circuit contains a frequency synthesizer and a loop filter for an FM and AM radio tuning system. Only a  $V_{\rm CO}$  is required to build a complete PLL system.

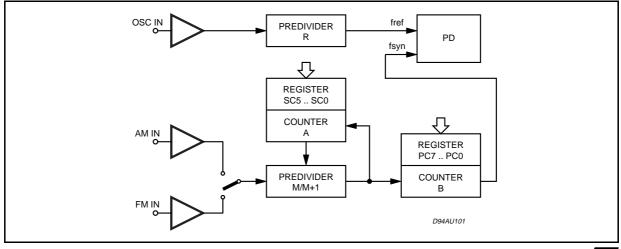

For FM and SW application, the counter works in a two stages configuration.

The first stage is a swallow counter with a four modulus (:32/33/64/65) precounter.

The second stage is an 8-bit programmable counter.

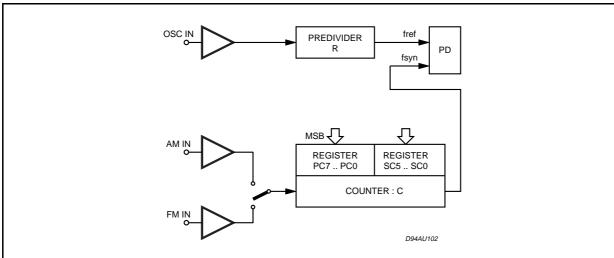

For LW and MW application, a 14-bit programmable counter is available.

The circuit receives the scaling factors for the programmable counters and the values of the reference frequencies via a three line serial bus interface.

The reference frequency is generated by a 4MHz XTAL oscillator followed by the reference divider. An external oscillator (f = 4MHz) can be used instead of the internal one; it must be connected to

OSCIN (pin 7). The reference step-frequency is 1 or 2.5kHz for AM. For FM mode a step frequency of 12.5 and 25kHz can be selected.

The circuit checks the format of the received data words.

Valid data in the interface shift register are stored automatically in buffer registers at the end of transmission.

The output signals of the phase detector are switching the programmable current sources.

Their currents are integrated in the loop filter to a DC voltage. The values of the current sources are programmable by two bits also received via the serial bus.

The loop filter amplifier is supplied by a separate positive power supply, to minimize the noise induced by the digital part of the system.

The loop gain can be set for different conditions. After a power on reset, all registers are reset to zero and the standby mode is activated.

In standby mode, oscillator, reference counter, AM input and FM input are stopped. The power consumption is reduced to a minimum.

### 3.0 DETAILED DESCRIPTION OF THE PLL FREQUENCY SYNTHESIZER

#### 3.1 INPUT AMPLIFIERS

The signals applied on AM and FM input are amplified to get a logic level in order to drive the frequency dividers.

#### 3.1.1 Input Impedance

The typical input impedance: for the FM input is  $200\Omega$  and for AM input is  $1.4k\Omega$ .

#### 3.1.2 Input sensitivity

(see Figures 1a and 1b).

#### 3.2 DATA AND CONTROL REGISTER

#### 3.2.1 Register Location

The data registers (bit2...bit7) for the control register and the data registers PC7...PC0, SC5...SC0 for the counters are organized in four words, identified by two address bits (bit 7 and bit 6), bit 7 is the first bit to be sent by the controller, bit0 is the last one. The order and the number of the bytes to be transmitted is free of choice. The modification of the PC7...PC0 registers is valid for the internal counters only after transmission of byte 4 (SC5...SC0).

### 3.2.2 CONTROL AND STATUS REGISTERS Register Configuration

|          | ADDRES    | SS BITS | DATA BITS |        |        |        |         |           |

|----------|-----------|---------|-----------|--------|--------|--------|---------|-----------|

| BYTE     | MSB-BIT 7 | BIT 6   | BIT 5     | BIT 4  | BIT 3  | BIT 2  | BIT 1   | LSB BIT 0 |

| Function | adr 0     | adr 1   | data 0    | data 1 | data 2 | data 3 | data 4  | data 5    |

| byte 1   | 0         | 0       | test 0    | test 1 | test 2 | SOUT   | CURR2   | fref      |

| byte 2   | 0         | 1       | PC7       | PC6    | LPF1/2 | CURR 1 | SWM/DIR | AM/FM     |

| byte 3   | 1         | 0       | PC5       | PC4    | PC3    | PC2    | PC1     | PC0       |

| byte 4   | 1         | 1       | SC5       | SC4    | SC3    | SC2    | SC1     | SC0       |

| REGISTER NAME | FUNCTION                                              |

|---------------|-------------------------------------------------------|

| SWM/DIR       | Swallow direct-mode switch 1 = SWM, 0 = DIR           |

| AM/FM         | AM - FM band switch 1=AM, 0 = FM                      |

| fref          | Selection of reference frequency (see table 3.4)      |

| CURR1         | Current select of change pump                         |

| CURR2         | Current select of change pump                         |

| LPF1/LPF2     | Loop filter input select 1= IPF1, 0 = IPF2            |

| SOUT          | Switch output condition 1=output high, 0 = output low |

### 3.3 DIVIDER FROM V<sub>CO</sub> FREQUENCY TO REFERENCE FREQUENCY

This divider provides a low frequency fsyn which is phase compared with the reference frequency free.

#### 3.4 OPERATING MODE

Four operating modes are available:

- FM mode,

- AM swallow mode.

- AM direct mode,

- Standby mode

They are user programmable with the SWR/DIR and AM/FM bits in the byte 2.

Standby mode: all functions are stopped. This allows low current consumption without lost of information in all register, it is activated by forcing bit 0 (AM/FM) and bit 1 (SWM/DIR) both at zero value.

| MODE SECTION | SWM/DIR | AM/FM |

|--------------|---------|-------|

| STAND-BY     | 0       | 0     |

| FM           | 1       | 0     |

| AM SWALLOW   | 0       | 1     |

| AM DIRECT    | 1       | 1     |

3.4.1 FM and AM (SW) Operation (Swallow Mode)

The FM or AM signal is applied to a four modulus: 32/33/64/65 high speed prescaler, which is controlled by a 6 bit divider 'A'.This divider is controlled by the 6 bit SC register. In parallel the output of the prescaler is connected to a 8 bit divider 'B'. This divider is controlled by the 8 bit PC register. For FM mode with 25kHz reference frequency operation, the divider A is a 5 bit divider. The high speed prescaler is working in: 32/33 dividing mode. Bit 6 of the SC register has to be kept to "0".

Dividing range calculation:

For FM mode with 12.5kHz reference frequency and SW swallow mode operation:  $f_{VCO} = [65 \cdot A_1 + (B_1 + 1 - A_1) \cdot 64]$ . free or

$$f_{VCO} = (64 \cdot B_1 + A_1 + 64) \cdot f_{REF}$$

Important : For correct operation  $B \ge 64$  and B > A

At FM mode with 25kHz reference frequency :  $f_{VCO} = [33 \cdot A_2 + (B_2 + 1 - A_2) \cdot 32] \cdot f_{REF}$

$$f_{VCO} = (32 \cdot B_2 + A_2 + 32) \cdot f_{REF}$$

Important: For correct operation  $B \ge 32$  and  $B \ge A$ .

A and B are variable values of the dividers.

To keep the actual tuning frequency after a modification of the reference frequency, the values of the dividers have to be modified in the following way.

the following way. Switching from 25kHz to 12.5kHz reference frequency:  $B_1 = B_2$ ,  $A_1 = A_2 \cdot 2$

Switching from 12.5kHz to 25kHz reference frequency:

$$B_2 = B_1$$

,  $A_2 = \frac{A_1}{2}$  and  $A_2 = \frac{(A_1 + 1)}{2}$

for odd values A<sub>1</sub>.

The AM signal is directly applied to the 14 bit static divider 'C'. This divider is controlled by both SC and PC registers. Dividing range:

$$f_{VCO} = (C + 1) \cdot f_{REF}$$

Figure 2: FM and AM (SW) operation (swallow mode)

Figure 3: AM direct mode operation for SW, MW and LW

#### 3.4 REFERENCE FREQUENCY GENERATOR

The crystal oscillator clock is divided by the reference frequency divider to provide the reference frequency to the phase comparator. Reference frequency divider range is selectable by the programming bit 'fREF'. Available reference frequency are shown in following table.

following table.

**TABLE 3.4**

| AM/FM | f <sub>REF</sub> | f <sub>REF</sub> (kHz) |

|-------|------------------|------------------------|

| 0     | 0                | 12.5                   |

| 0     | 1                | 25                     |

| 1     | 0                | 1                      |

| 1     | 1                | 2.5                    |

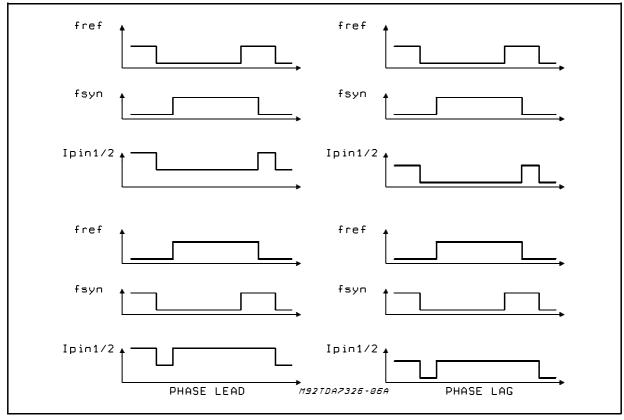

Figure 4: Phase comparator

Figure 5

#### 3.5 THREE STATE PHASE COMPARATOR

The phase comparator generates a phase error signal according to phase difference between f<sub>SYN</sub> and f<sub>REF</sub>. This phase error signal drives the charge pump current generator

#### 3.6 CHARGE PUMP CURRENT GENERATOR

This system generates signed pulses of current. Duration and polarity of those pulses are determined by the phase error signal. The absolute current values are programmable by 'CURR1' and 'CURR2' bits and controlled by an external resistor R<sub>ISET</sub> connected to Pin 2 and GND.

#### 3.7 LOW NOISE CMOS OP-AMP

A low noise Op-Amp is available on chip. The positive input of this Op-Amp is connected to an internal voltage divider and to Pin 3 'V<sub>REF</sub>'. The negative input is connected to the charge pump output. In cooperation with this internal amplifier and external components, an active filter can be provided. To increase the flexibility in application the negative input can be switched to two input pins (Pins 15 and 16). This switch is controlled by 'LPF' register with 'LPF' low Pin 15 is active and 'LPF' high Pin 16 is active. This feature allows two separate active filters with different performance.

#### 3.8 TEST FUNCTION

The test pin (Test Out) is used only for testing: it

has no use in real applications. The three bits test0, test1, test2, of the test REGISTER must be programmed as 0,0,0 in application.

Some device internal signals can be checked at pin 9 (TST OUT) and pin 7 (OSC IN) by programming different codes of the test register according to the Table 1.

For example by programming the code 110 the "fsyn out" will be available at pin 9 and "fREF input" at pin 7.

TABLE 1:

|           | t Regi<br>Status |           | Test Fu           | unction            |

|-----------|------------------|-----------|-------------------|--------------------|

| test<br>0 | test<br>1        | test<br>2 | PIN9 (TEST/OUT)   | PIN 7 (OSCIN)      |

| 0         | 0                | 0         | Sout (appl. mode) | Oscin (appl. mode) |

| 1         | 0                | 0         | fref Output       | Oscin (appl. mode) |

| 0         | 1                | 0         | Phi Output        | fref Input         |

| 1         | 1                | 0         | fsyn Output       | fref Input         |

| 0         | 0                | 1         | Phi input         | Oscin (appl. mode) |

#### 3.9 C-BUS INTERFACE

This interface allows communication between the PLL device and  $\mu p$  systems. A bus control system check the format of transmission, only eight bit word transmission is allowed. Four registers with 6 bit are user programmable. The selection of this four registers is controlled by two address bits.

#### **TDA7326**

#### 4.0 BIT ORGANIZATION OF THE BUS TRANSFER OPERATION

| Loadir | Loading registers for all bytes of the programmable counters and all control registers |          |             |               |          |            |          |         |          |          |         |     |     |                  |       |               |

|--------|----------------------------------------------------------------------------------------|----------|-------------|---------------|----------|------------|----------|---------|----------|----------|---------|-----|-----|------------------|-------|---------------|

| 0      | 1                                                                                      | PC7      | PC6         | LPF1/<br>LPF2 | CURR1    | SWM<br>DIR | AM<br>FM | 1       | 0        | PC5      | PC4     | PC3 | PC2 | PC1              | PCO   | $\Rightarrow$ |

|        |                                                                                        |          |             |               |          |            |          |         |          |          |         |     |     |                  |       |               |

| ®      | 1                                                                                      | 1        | SC5<br>(0)* | SC4           | SC3      | SC2        | SC1      | SC0     | 0        | 0        | 0       | 0   | 0   | S <sub>OUT</sub> | CURR2 | fref          |

| Loadir | ng regis                                                                               | ters for | all byte    | es of th      | e progra | ımmabl     | le coun  | ters an | d all co | ntrol re | gisters |     |     |                  |       |               |

| 0      | 1                                                                                      | PC7      | PC6         | LPF2/<br>LPF1 | CURR1    | SWM<br>DIR | AM<br>FM | 1       | 0        | PC5      | PC4     | PC3 | PC2 | PC1              | PCO   | $\Rightarrow$ |

| •      |                                                                                        |          | •           | •             |          |            |          |         | •        |          |         |     | •   |                  |       |               |

| ®      | 1                                                                                      | 1        | SC5<br>(0)* | SC4           | SC3      | SC2        | SC1      | SC0     |          |          |         |     |     |                  |       |               |

| Loa | Loading registers for 11 or 12 bits of the programmable counters |   |     |     |     |     |     |     |   |   |             |     |     |     |     |     |

|-----|------------------------------------------------------------------|---|-----|-----|-----|-----|-----|-----|---|---|-------------|-----|-----|-----|-----|-----|

| 1   |                                                                  | 0 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | 1 | 1 | SC5<br>(0)* | SC4 | SC3 | SC2 | SC1 | SC0 |

Loading registers for 5 or 6 bits of the programmable counters

1 1  $SC5 \atop (0)^*$  SC4 SC3 SC2 SC1 SC0

Setting control register for loop filter selection charge pump current bit 1, mode AM/FM selection

| 0 1 X X | LPF2/ CURR1 SWM/ AM<br>LPF1 DIR FM |  |

|---------|------------------------------------|--|

|---------|------------------------------------|--|

Test mode inizialization (Test0 = Test1 = Test2 = 0)

0 0 TST0 TST1 TST2 Sour CURR2 free

Setting control register for switch output pin 9, charge pump current bit 2, reference frequency select 0 0 0 0 Sout CURR2 free

(\*) This bit has to be "0" for fref = "1" (fref = 25kHz in FM mode or 2.5KHz AM swallow mode)

#### **5.0 FREQUENCY PROGRAMMATION**

#### 5.1 AM/FM Computation Resume

#### **FM SWALLOW MODE**

$f_{REF} = 12.5KHz$   $F_{VCO} = (64 \cdot PC + SC + 64) \cdot f_{REF}$

$F_{VCO} = (DIV_VAL + 64) \cdot f_{REF}$  swallow 6bit

$f_{REF} = 25KHz$   $F_{VCO} = (32 \cdot PC + SC + 32) \cdot f_{REF}$

Fvco = (DIV\_VAL+ 32) · fref swallow 5bit (bit SC5 = 0)

where: PC = Program Counter Value (PC7 to PC0) SC = Swallow Counter Value (SC5 to SC0) DIV\_VAL = Divider Factor

#### **AM SWALLOW MODE**

$$f_{REF} = 1KHz$$

$F_{VCO} = (64 \cdot PC + SC + 64) \cdot f_{REF}$

$$F_{VCO} = (DIV_VAL + 64) \cdot f_{REF}$$

swallow 6bit

$$f_{REF} = 2.5KHz$$

$F_{VCO} = (32 \cdot PC + SC + 32) \cdot f_{REF}$

#### **AM DIRECT MODE**

#### 5.2: Examples

#### a) CONDITIONS:

FM MODE ( $f_{RF} = 98.1MHz$ ,  $f_{REF} = 25KHz$ ; IF = 10.7MHz

it follows: that  $F_{VCO} = 98.1 + 10.7 = 108.8 MHz$

DIV\_VAL =

$$\frac{F_{VCO}}{f_{ref}}$$

- 32 =4352 - 32 = 4320 = 10 E 0 Hex

| = | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | binary |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------|

|   | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | SC5 | SC4 | SC3 | SC2 | SC1 | SC0 | billar |

binary

$$\Rightarrow$$

SC = 0 (\*)

PC = 135

#### b) CONDITIONS:

FM MODE ( $f_{RF} = 98.8MHz$ ,  $f_{REF} = 25KHz$ ; IF = 10.7MHz

it follows:  $F_{VCO} = 98.8 + 10.7 = 109.5MHz$

DIV\_VAL = 4380 - 32 = 4348 = 10 FC Hex

NOTE: (\*) The bit SC5 is FORCED = 0, and higher weight bits are left shift ed one position.

#### c) CONDITIONS:

FM MODE ( $f_{RF} = 98.8MHz$ ,  $f_{REF} = 12.5KHz$ ; IF = 10.7MHz

it follows:  $F_{VCO} = 98.8 + 10.7 = 109.5MHz$

DIV\_VAL = 8760 - 64 = 8696 = 21 F8 Hex

| • | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| = | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | SC5 | SC4 | SC3 | SC2 | SC1 | SC0 |

binary

$$\Rightarrow$$

SC = 56

PC = 135

#### d) CONDITIONS:

AM DIRECT MODE, ( $f_{RF} = 530KHz$ ,  $f_{REF} = 1KHz$ ; IF = 450KHz

it follows:  $F_{VCO} = 530 + 450 = 980 \text{KHz}$

DIV\_VAL =

$$\frac{F_{VCO}}{f_{REF}} - 1 = \frac{980}{1} - 1 = 979 = 3D3 \text{ Hex}$$

|   | .0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 0   | 1   | 0   | 0   | 1   | 1   |  |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| = | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | SC5 | SC4 | SC3 | SC2 | SC1 | SC0 |  |

binary

#### e) CONDITIONS:

AM DIRECT MODE, (f<sub>RF</sub> = 1710KHz, f<sub>REF</sub> = 1KHz; IF = 450KHz

it follows:  $F_{VCO} = 1710 + 450 = 2160KHz$

DIV\_VAL =

$$\frac{F_{VCO}}{f_{REF}} - 1 = \frac{2160}{1} - 1 = 2159 = 86F \text{ Hex}$$

|   | . 0 | 0   | 1   | 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 1   | 1   | 1   |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| = | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | SC5 | SC4 | SC3 | SC2 | SC1 | SC0 |

binary

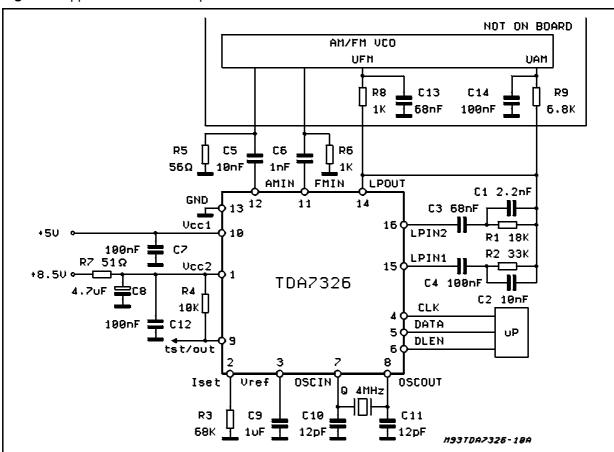

Figure 5: Application with two loop-filters

<sup>\*)</sup> C7 must be connected as closed as possible between pin 10 and pin 13

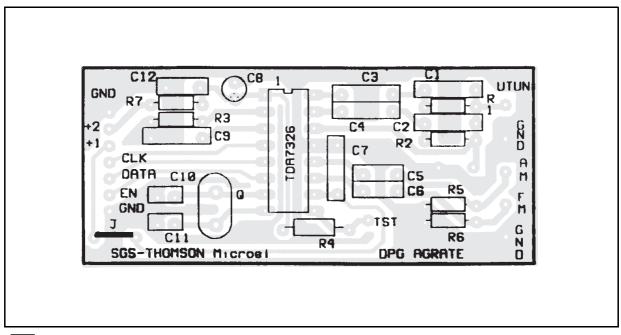

Figure 6: PC Board and Component Layout of fig. 5

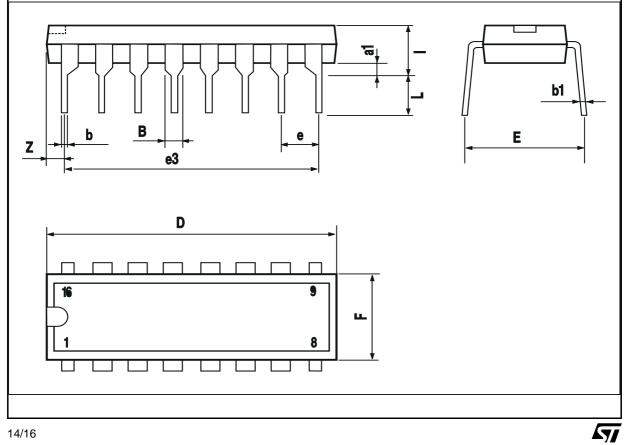

| DIM. |      | mm    |      |       | inch  |       |

|------|------|-------|------|-------|-------|-------|

|      | MIN. | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |

| a1   | 0.51 |       |      | 0.020 |       |       |

| В    | 0.77 |       | 1.65 | 0.030 |       | 0.065 |

| b    |      | 0.5   |      |       | 0.020 |       |

| b1   |      | 0.25  |      |       | 0.010 |       |

| D    |      |       | 20   |       |       | 0.787 |

| Е    |      | 8.5   |      |       | 0.335 |       |

| е    |      | 2.54  |      |       | 0.100 |       |

| e3   |      | 17.78 |      |       | 0.700 |       |

| F    |      |       | 7.1  |       |       | 0.280 |

| I    |      |       | 5.1  |       |       | 0.201 |

| L    |      | 3.3   |      |       | 0.130 |       |

| Z    |      |       | 1.27 |       |       | 0.050 |

|      |      |       |      |       |       | •     |

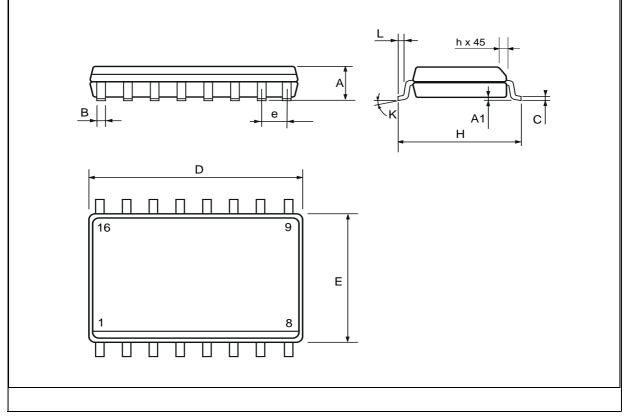

#### **OUTLINE AND MECHANICAL DATA**

DIP16

| DIM. |                    | mm   |       |       | inch  |       |  |  |  |  |

|------|--------------------|------|-------|-------|-------|-------|--|--|--|--|

|      | MIN.               | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |  |  |  |  |

| Α    | 2.35               |      | 2.65  | 0.093 |       | 0.104 |  |  |  |  |

| A1   | 0.1                |      | 0.3   | 0.004 |       | 0.012 |  |  |  |  |

| В    | 0.33               |      | 0.51  | 0.013 |       | 0.020 |  |  |  |  |

| С    | 0.23               |      | 0.32  | 0.009 |       | 0.013 |  |  |  |  |

| D    | 10.1               |      | 10.5  | 0.398 |       | 0.413 |  |  |  |  |

| Е    | 7.4                |      | 7.6   | 0.291 |       | 0.299 |  |  |  |  |

| е    |                    | 1.27 |       |       | 0.050 |       |  |  |  |  |

| Н    | 10                 |      | 10.65 | 0.394 |       | 0.419 |  |  |  |  |

| h    | 0.25               |      | 0.75  | 0.010 |       | 0.030 |  |  |  |  |

| L    | 0.4                |      | 1.27  | 0.016 |       | 0.050 |  |  |  |  |

| К    | 0° (min.)8° (max.) |      |       |       |       |       |  |  |  |  |

# OUTLINE AND MECHANICAL DATA

## SO 10 Wide

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

STMicroelectronics GROUP OF COMPANIES

Australia – Belgium - Brazil - Canada - China – Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com