# MOS INTEGRATED CIRCUIT MC-242443

# MCP (MULTI-CHIP PACKAGE) FLASH MEMORY AND MOBILE SPECIFIED RAM 32M-BIT FLASH MEMORY AND 16M-BIT CMOS MOBILE SPECIFIED RAM

#### **Description**

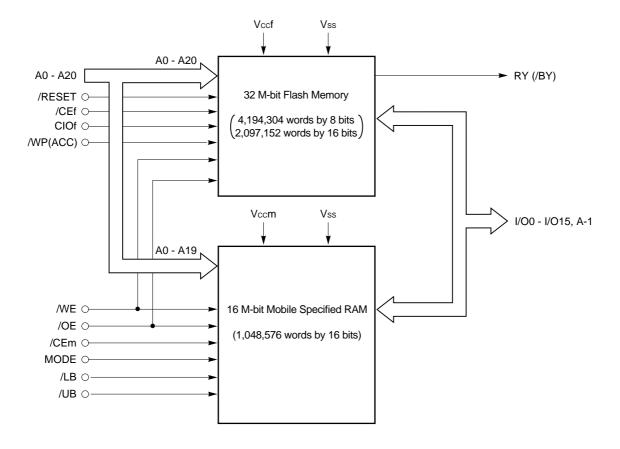

The MC-242443 is a stacked type MCP (Multi-Chip Package) of 33,554,432 bits (BYTE mode: 4,194,304 words by 8 bits, WORD mode: 2,097,152 words by 16 bits) flash memory and 16,777,216 bits (1,048,576 words by 16 bits) Mobile specified RAM.

★ The MC-242443 is packaged in a 77-pin TAPE FBGA and 71-pin TAPE FBGA.

#### **Features**

#### **General Features**

- Fast access time: tACC = 90 ns (MAX.), 85 ns (MAX.) (VCCf ≥ 2.7 V) (Flash Memory)

tAA = 80, 90, 100 ns (MAX.) (Mobile specified RAM)

- Supply voltage: Vccf / Vccm = 2.6 to 3.0 V

- Wide operating temperature :  $T_A = -20 \text{ to } +70 \text{ }^{\circ}\text{C}$

#### **Flash Memory Features**

- Two bank organization enabling simultaneous execution of erase / program and read

- Bank organization: 2 banks (8M bits + 24M bits)

- Memory organization: 4,194,304 words × 8 bits (BYTE mode)

2,097,152 words × 16 bits (WORD mode)

- Sector organization: 71 sectors (8K bytes / 4K words × 8 sectors, 64K bytes / 32K words × 63 sectors)

- Boot sector allocated to the highest address (sector)

- 3-state output

- Automatic program

- Program suspend / resume

- Unlock bypass program

- Automatic erase

- Chip erase

- Sector erase (sectors can be combined freely)

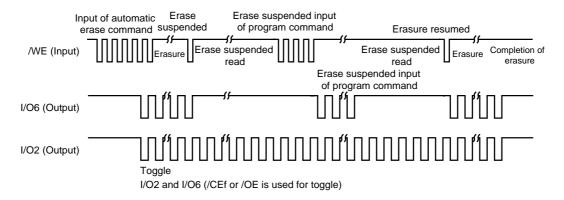

- Erase suspend / resume

- Program / Erase completion detection

- Detection through data polling and toggle bits

- Detection through RY (/BY) pin

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

- Sector group protection

- Any sector can be protected

- Any protected sector can be temporary unprotected

- Sectors can be used for boot application

- Hardware reset and standby using /RESET pin

- Automatic sleep mode

- Boot block sector protect by /WP (ACC) pin

- Conforms to common flash memory interface (CFI)

- Extra One Time Protect Sector provided

#### **Mobile specified RAM Features**

• Memory organization: 1,048,576 words by 16 bits

• Supply current : At operating : 35 mA (MAX.)

At Standby Mode 1 : 100  $\mu$ A (MAX.) At Standby Mode 2 : 10  $\mu$ A (MAX.)

Chip Enable inputs : /CEmByte data control : /LB, /UBStandby Mode input : MODE

• Standby Mode 1 : Normal standby (Memory cell data hold valid)

• Standby Mode 2: Memory cell data hold invalid

# **★** Ordering Information

| Part number                         | Flash Memory             | Flash Memory      | Mobile specified RAM | Package          |

|-------------------------------------|--------------------------|-------------------|----------------------|------------------|

|                                     | Boot sector              | Access time       | Access time          |                  |

|                                     |                          | ns (MAX.)         | ns (MAX.)            |                  |

| MC-242443F9-B90-BT3                 | Highest address (sector) | 90                | 80                   | 77-pin TAPE FBGA |

| MC-242443F9-B95-BT3 <sup>Note</sup> | (T type)                 | 85 (Vccf ≥ 2.7 V) | 90                   | (12×7)           |

| MC-242443F9-B10-BT3                 |                          |                   | 100                  |                  |

| MC-242443F9-B90-BS1 <sup>Note</sup> |                          |                   | 80                   | 71-pin TAPE FBGA |

| MC-242443F9-B95-BS1 <sup>Note</sup> |                          |                   | 90                   | (11 × 7)         |

| MC-242443F9-B10-BS1 <sup>Note</sup> |                          |                   | 100                  |                  |

Note Under development

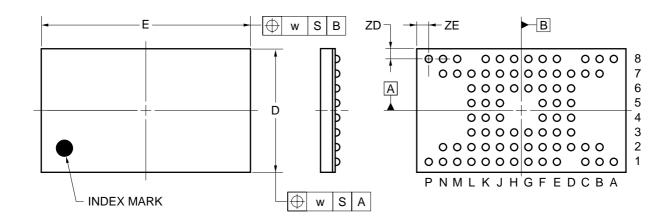

#### ★ Pin Configurations

/xxx indicates active low signal.

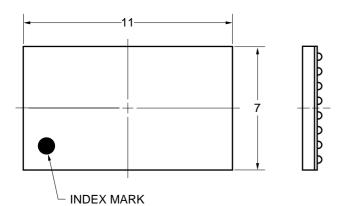

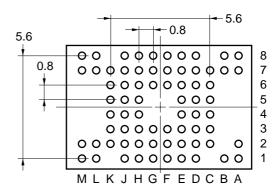

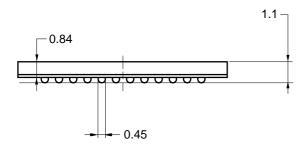

#### 77-pin TAPE FBGA (12 × 7)

|   |    |    |    |         |       |         | Тор | View |            |       |       |    |    |    |

|---|----|----|----|---------|-------|---------|-----|------|------------|-------|-------|----|----|----|

|   | Α  | В  | С  | D       | Е     | F       | G   | Н    | J          | K     | L     | М  | N  | Р  |

| 8 | NC | NC | NC |         | A15   | IC      | IC  | A16  | CIOf       | Vss   |       | NC | NC | NC |

| 7 |    | NC | NC | A11     | A12   | A13     | A14 | NC   | I/O15, A-1 | I/O7  | I/O14 | NC | NC |    |

| 6 |    |    |    | A8      | A19   | A9      | A10 | I/O6 | I/O13      | I/O12 | I/O5  |    |    |    |

| 5 |    |    |    | /WE     | MODE  | A20     |     |      | I/O4       | Vccm  | NC    |    |    |    |

| 4 |    |    |    | /WP(ACC | RESET | RY(/BY) |     |      | I/O3       | Vccf  | I/O11 |    |    |    |

| 3 |    |    |    | /LB     | /UB   | A18     | A17 | I/O1 | I/O9       | I/O10 | I/O2  |    |    |    |

| 2 |    | NC | NC | A7      | A6    | A5      | A4  | Vss  | /OE        | I/O0  | I/O8  | NC | NC |    |

| 1 | NC | NC | NC |         | А3    | A2      | A1  | A0   | /CEf       | /CEm  | NC    | NC | NC | NC |

#### 71-pin TAPE FBGA (11 × 7)

|   |    |    |         |          |         | Тор | View |            |       |       |    |    |

|---|----|----|---------|----------|---------|-----|------|------------|-------|-------|----|----|

|   | Α  | В  | С       | D        | Е       | F   | G    | Н          | J     | K     | L  | М  |

| 8 | NC | NC |         | A15      | NC      | IC  | A16  | CIOf       | Vss   |       | NC | NC |

| 7 | NC | NC | A11     | A12      | A13     | A14 | NC   | I/O15, A-1 | I/O7  | I/O14 | NC | NC |

| 6 |    |    | A8      | A19      | A9      | A10 | I/O6 | I/O13      | I/O12 | I/O5  |    |    |

| 5 |    |    | /WE     | MODE     | A20     |     |      | I/O4       | Vccm  | NC    |    |    |

| 4 |    |    | /WP(ACC | C)/RESET | RY(/BY) |     |      | I/O3       | Vccf  | I/O11 |    |    |

| 3 |    |    | /LB     | /UB      | A18     | A17 | I/O1 | I/O9       | I/O10 | I/O2  |    |    |

| 2 | NC |    | A7      | A6       | A5      | A4  | Vss  | /OE        | I/O0  | I/O8  | NC | NC |

| 1 | NC | NC |         | А3       | A2      | A1  | A0   | /CEf       | /CEm  |       | NC | NC |

#### Common Pins

/OE

# Flash Memory Pins

A0 - A19 : Address inputs A20 : Address inputs

: Output Enable LSB address input (BYTE mode)

/WE : Write Enable /CEf : Chip Enable

Vss : Ground RY (/BY) : Ready (Busy) output NC NO NO NO NO NO Connection /RESET : Hardware reset input IC Note 2 : Internal Connection Vccf : Supply Voltage

/WP(ACC) : Hardware Write Protect (Acceleration)

CIOf : Selects 8-bit or 16-bit mode

Mobile specified RAM Pins

/CEm : Chip Enable

MODE : Standby mode select

Vccm : Supply Voltage

/LB, /UB : Byte data select

Note 1. Some signals can be applied because this pin is not internally connected.

2. Leave this pin connected to Vss or unconnected (Recommended to connected to Vss).

**Remark** Refer to **Package Drawings** for the index mark.

# **Block Diagram**

#### **Bus Operations Table**

| Ор            | eration          |        | Flash | Memo  | ory      | Mol  | bile speci | ified R | AM  |     |     | Common                 |                        |

|---------------|------------------|--------|-------|-------|----------|------|------------|---------|-----|-----|-----|------------------------|------------------------|

|               |                  | /RESET | /CEf  | CIOf  | /WP(ACC) | /CEm | MODE       | /LB     | /UB | /OE | /WE | 1/00 - 1/07            | I/O8-I/O15             |

| Full standby  | Standby Mode 1   | Н      | Н     | ×     | ×        | Н    | Н          | ×       | ×   | ×   | ×   | Hi-Z                   | Hi-Z                   |

|               | Standby Mode 2   |        |       |       |          | Н    | L          |         |     |     |     |                        |                        |

| Output disabl | е                | Н      | L     | ×     | ×        | L    | Н          | ×       | ×   | Н   | Н   | Hi-Z                   | Hi-Z                   |

| Read (Flash   | BYTE mode        | Н      | L     | L     | ×        |      | Note       | 2       |     | L   | Н   | Data Out               | Hi-Z                   |

| Memory Note 1 | ) WORD mode      |        |       | Н     |          |      |            |         |     |     |     | Data Out               | Data Out               |

| Write (Flash  | BYTE mode        | Н      | L     | L     | ×        |      | Note       | 2       |     | Н   | L   | Data In                | Hi-Z                   |

| Memory)       | WORD mode        |        |       | Н     |          |      |            |         |     |     |     | Data In                | Data In                |

| Temporary se  | ector group      | VID    | ×     | ×     | ×        |      | Note       | 2       |     | ×   | ×   | Hi-Z or                | Hi-Z or                |

| unprotect     |                  |        |       |       |          |      |            |         |     |     |     | Data In/Out            | Data In/Out            |

| Boot block se | ector protect    | ×      | ×     | ×     | L        | ×    | ×          | ×       | ×   | ×   | ×   | Hi-Z or<br>Data In/Out | Hi-Z or<br>Data In/Out |

| Flash Memor   | y hardware reset | L      | ×     | ×     | ×        | ×    | ×          | ×       | ×   | ×   | ×   | Hi-Z                   | Hi-Z                   |

| Read          |                  |        | N     | ote 3 |          | L    | Н          | L       | L   | L   | Н   | Data Out               | Data Out               |

| (Mobile speci | fied RAM)        |        |       |       |          |      |            |         | Н   |     |     |                        | Hi-Z                   |

|               |                  |        |       |       |          |      |            | Н       | L   |     |     | Hi-Z                   | Data Out               |

| Write         |                  |        | N     | ote 3 |          | L    | Н          | L       | L   | ×   | L   | Data In                | Data In                |

| (Mobile speci | fied RAM)        |        |       |       |          |      |            |         | Н   |     |     |                        | Hi-Z                   |

|               |                  |        |       |       |          |      |            | Н       | L   |     |     | Hi-Z                   | Data In                |

Caution Other operations except for indicated in this table are inhibited.

**Notes 1.** When  $/OE = V_{IL}$ ,  $V_{IL}$  can be applied to /WE. When  $/OE = V_{IH}$ , a write operation is started.

- 2. Mobile specified RAM should be Standby.

- 3. Flash Memory should be Standby or Hardware reset.

**Remarks 1.**  $H: V_{IH}, L: V_{IL}, \times: V_{IH} \text{ or } V_{IL}$

- 2. Sector group protection and read the product ID are using a command.

- 3. MODE pin must be fixed to H during active operation.

- 4. Refer to DUAL OPERATION FLASH MEMORY 32M BITS A SERIES Information (M14914E) for the flash memory bus operations.

Data Sheet M15171EJ7V0DS 5

# Sector Organization / Sector Address Table (Flash Memory)

# Flash Memory top boot (1/2)

| Bank   | Sector                   | Add                | ress                | Sectors |      |          |     |         |     | ss Tabl | e     |       |     |

|--------|--------------------------|--------------------|---------------------|---------|------|----------|-----|---------|-----|---------|-------|-------|-----|

|        | Organization             | D)/TEI-            | WODD                | Address | 4.00 |          |     | ress Ta |     | 1 4 5   | A 4 4 | 1 440 | 140 |

| Bank 1 | K bytes / K words<br>8/4 | 3FFFFFH            | WORD mode<br>1FFFFH | FSA70   | A20  | A19<br>1 | A18 | A17     | A16 | A15     | A14   | A13   | A12 |

|        | 8/4                      | 3FE000H<br>3FDFFFH | 1FF000H<br>1FEFFFH  | FSA69   | 1    | 1        | 1   | 1       | 1   | 1       | 1     | 1     | 0   |

|        | 8/4                      | 3FC000H<br>3FBFFFH | 1FE000H<br>1FDFFFH  | FSA68   | 1    | 1        | 1   | 1       | 1   | 1       | 1     | 0     | 1   |

|        | 8/4                      | 3FA000H<br>3F9FFFH | 1FD000H<br>1FCFFFH  | FSA67   | 1    | 1        | 1   | 1       | 1   | 1       | 1     | 0     | 0   |

|        | 8/4                      | 3F8000H<br>3F7FFFH | 1FC000H<br>1FBFFFH  | FSA66   | 1    | 1        | 1   | 1       | 1   | 1       | 0     | 1     | 1   |

|        | 8/4                      | 3F6000H<br>3F5FFFH | 1FB000H<br>1FAFFFH  | FSA65   | 1    | 1        | 1   | 1       | 1   | 1       | 0     | 1     | 0   |

|        | 8/4                      | 3F4000H<br>3F3FFFH | 1FA000H<br>1F9FFFH  | FSA64   | 1    | 1        | 1   | 1       | 1   | 1       | 0     | 0     | 1   |

|        | 8/4                      | 3F2000H<br>3F1FFFH | 1F9000H<br>1F8FFFH  | FSA63   | 1    | 1        | 1   | 1       | 1   | 1       | 0     | 0     | 0   |

|        | 64/32                    | 3F0000H<br>3EFFFFH | 1F8000H<br>1F7FFFH  | FSA62   | 1    | 1        | 1   | 1       | 1   | 0       | X     | х     | х   |

|        | 64/32                    | 3E0000H            | 1F0000H             | FSA61   | 1    | 1        | 1   | 1       | 0   | 1       |       |       |     |

|        |                          | 3DFFFFH<br>3D0000H | 1EFFFFH<br>1E8000H  |         |      |          |     |         |     |         | Х     | Х     | х   |

|        | 64/32                    | 3CFFFFH<br>3C0000H | 1E7FFFH<br>1E0000H  | FSA60   | 1    | 1        | 1   | 1       | 0   | 0       | Х     | Х     | Х   |

|        | 64/32                    | 3BFFFFH<br>3B0000H | 1DFFFFH<br>1D8000H  | FSA59   | 1    | 1        | 1   | 0       | 1   | 1       | Х     | Х     | Х   |

|        | 64/32                    | 3AFFFFH<br>3A0000H | 1D7FFFH<br>1D0000H  | FSA58   | 1    | 1        | 1   | 0       | 1   | 0       | Х     | Х     | Х   |

|        | 64/32                    | 39FFFFH<br>390000H | 1CFFFFH<br>1C8000H  | FSA57   | 1    | 1        | 1   | 0       | 0   | 1       | Х     | Х     | Х   |

|        | 64/32                    | 38FFFFH<br>380000H | 1C7FFFH<br>1C0000H  | FSA56   | 1    | 1        | 1   | 0       | 0   | 0       | Х     | Х     | Х   |

|        | 64/32                    | 37FFFFH<br>370000H | 1BFFFFH<br>1B8000H  | FSA55   | 1    | 1        | 0   | 1       | 1   | 1       | Х     | Х     | х   |

|        | 64/32                    | 36FFFFH<br>360000H | 1B7FFFH<br>1B0000H  | FSA54   | 1    | 1        | 0   | 1       | 1   | 0       | Х     | Х     | Х   |

|        | 64/32                    | 35FFFFH<br>350000H | 1AFFFFH<br>1A8000H  | FSA53   | 1    | 1        | 0   | 1       | 0   | 1       | Х     | Х     | Х   |

|        | 64/32                    | 34FFFFH<br>340000H | 1A7FFFH<br>1A0000H  | FSA52   | 1    | 1        | 0   | 1       | 0   | 0       | Х     | Х     | х   |

|        | 64/32                    | 33FFFFH<br>330000H | 19FFFFH<br>198000H  | FSA51   | 1    | 1        | 0   | 0       | 1   | 1       | Х     | Х     | х   |

|        | 64/32                    | 32FFFFH<br>320000H | 197FFFH<br>190000H  | FSA50   | 1    | 1        | 0   | 0       | 1   | 0       | Х     | Х     | Х   |

|        | 64/32                    | 31FFFFH<br>310000H | 18FFFFH<br>188000H  | FSA49   | 1    | 1        | 0   | 0       | 0   | 1       | Х     | Х     | х   |

|        | 64/32                    | 30FFFFH<br>300000H | 187FFFH<br>180000H  | FSA48   | 1    | 1        | 0   | 0       | 0   | 0       | Х     | Х     | х   |

| Bank 2 | 64/32                    | 2FFFFH<br>2F0000H  | 17FFFFH<br>178000H  | FSA47   | 1    | 0        | 1   | 1       | 1   | 1       | Х     | Х     | х   |

|        | 64/32                    | 2EFFFFH<br>2E0000H | 177FFFH<br>170000H  | FSA46   | 1    | 0        | 1   | 1       | 1   | 0       | Х     | Х     | х   |

|        | 64/32                    | 2DFFFFH<br>2D0000H | 16FFFFH<br>168000H  | FSA45   | 1    | 0        | 1   | 1       | 0   | 1       | Х     | Х     | х   |

|        | 64/32                    | 2CFFFFH<br>2C0000H | 167FFFH<br>160000H  | FSA44   | 1    | 0        | 1   | 1       | 0   | 0       | Х     | Х     | х   |

|        | 64/32                    | 2BFFFFH<br>2B0000H | 15FFFFH<br>158000H  | FSA43   | 1    | 0        | 1   | 0       | 1   | 1       | Х     | х     | х   |

|        | 64/32                    | 2AFFFFH<br>2A0000H | 157FFFH<br>150000H  | FSA42   | 1    | 0        | 1   | 0       | 1   | 0       | Х     | Х     | х   |

|        | 64/32                    | 29FFFFH<br>290000H | 14FFFFH<br>148000H  | FSA41   | 1    | 0        | 1   | 0       | 0   | 1       | Х     | х     | х   |

|        | 64/32                    | 28FFFFH<br>280000H | 147FFFH<br>140000H  | FSA40   | 1    | 0        | 1   | 0       | 0   | 0       | х     | х     | х   |

|        | 64/32                    | 27FFFFH<br>270000H | 13FFFFH<br>138000H  | FSA39   | 1    | 0        | 0   | 1       | 1   | 1       | х     | х     | х   |

|        | 64/32                    | 26FFFFH            | 137FFFH             | FSA38   | 1    | 0        | 0   | 1       | 1   | 0       | х     | Х     | х   |

|        | 64/32                    | 260000H<br>25FFFFH | 130000H<br>12FFFFH  | FSA37   | 1    | 0        | 0   | 1       | 0   | 1       | Х     | Х     | х   |

|        | 64/32                    | 250000H<br>24FFFFH | 128000H<br>127FFFH  | FSA36   | 1    | 0        | 0   | 1       | 0   | 0       | Х     | Х     | х   |

|        | 64/32                    | 240000H<br>23FFFFH | 120000H<br>11FFFFH  | FSA35   | 1    | 0        | 0   | 0       | 1   | 1       | Х     | Х     | х   |

|        |                          | 230000H            | 118000H             |         |      |          |     |         |     |         |       |       |     |

\*

(2/2)

| Bank   | Sector                            | Ado                           | Iress                         | Sectors |     | _          |              |        | Addres      | s Tab | le  |     |     |

|--------|-----------------------------------|-------------------------------|-------------------------------|---------|-----|------------|--------------|--------|-------------|-------|-----|-----|-----|

|        | Organization<br>K bytes / K words | BYTE mode                     | WORD mode                     | Address | A20 | Bar<br>A19 | k Add<br>A18 | ress T | able<br>A16 | A15   | A14 | A13 | A12 |

| Bank 2 | 64/32                             | 22FFFFH                       | 117FFFH                       | FSA34   | 1   | 0          | 0            | 0      | 1           | 0     | Х   | х   | X   |

|        | 64/32                             | 220000H<br>21FFFFH            | 110000H<br>10FFFFH            | FSA33   | 1   | 0          | 0            | 0      | 0           | 1     | Х   | Х   | Х   |

|        | 64/32                             | 210000H<br>20FFFFH            | 108000H<br>107FFFH            | FSA32   | 1   | 0          | 0            | 0      | 0           | 0     | х   | х   | х   |

|        | 64/32                             | 200000H<br>1FFFFFH            | 100000H<br>0FFFFH             | FSA31   | 0   | 1          | 1            | 1      | 1           | 1     | Х   | Х   | Х   |

|        |                                   | 1F0000H                       | 0F8000H                       |         |     |            |              |        |             |       |     |     |     |

|        | 64/32                             | 1EFFFFH<br>1E0000H            | 0F7FFFH<br>0F0000H            | FSA30   | 0   | 1          | 1            | 1      | 1           | 0     | Х   | Х   | Х   |

|        | 64/32                             | 1DFFFFH<br>1D0000H            | 0EFFFFH<br>0E8000H            | FSA29   | 0   | 1          | 1            | 1      | 0           | 1     | Х   | Х   | Х   |

|        | 64/32                             | 1CFFFFH<br>1C0000H            | 0E7FFFH<br>0E0000H            | FSA28   | 0   | 1          | 1            | 1      | 0           | 0     | х   | Х   | х   |

|        | 64/32                             | 1BFFFFH<br>1B0000H            | 0DFFFFH<br>0D8000H            | FSA27   | 0   | 1          | 1            | 0      | 1           | 1     | х   | х   | Х   |

|        | 64/32                             | 1AFFFFH<br>1A0000H            | 0D7FFFH<br>0D0000H            | FSA26   | 0   | 1          | 1            | 0      | 1           | 0     | х   | х   | х   |

|        | 64/32                             | 19FFFFH<br>190000H            | 0CFFFH<br>0C8000H             | FSA25   | 0   | 1          | 1            | 0      | 0           | 1     | х   | х   | Х   |

|        | 64/32                             | 18FFFFH                       | 0C7FFFH                       | FSA24   | 0   | 1          | 1            | 0      | 0           | 0     | х   | х   | Х   |

|        | 64/32                             | 180000H<br>17FFFFH            | 0C0000H<br>0BFFFFH            | FSA23   | 0   | 1          | 0            | 1      | 1           | 1     | Х   | Х   | х   |

|        | 64/32                             | 170000H<br>16FFFFH<br>160000H | 0B8000H<br>0B7FFFH<br>0B0000H | FSA22   | 0   | 1          | 0            | 1      | 1           | 0     | х   | Х   | Х   |

|        | 64/32                             | 15FFFFH<br>150000H            | 0AFFFFH<br>0A8000H            | FSA21   | 0   | 1          | 0            | 1      | 0           | 1     | Х   | Х   | Х   |

|        | 64/32                             | 14FFFFH<br>140000H            | 0A7FFFH<br>0A0000H            | FSA20   | 0   | 1          | 0            | 1      | 0           | 0     | х   | х   | х   |

|        | 64/32                             | 13FFFFH<br>130000H            | 09FFFFH<br>098000H            | FSA19   | 0   | 1          | 0            | 0      | 1           | 1     | х   | х   | х   |

|        | 64/32                             | 12FFFFH<br>120000H            | 097FFFH<br>090000H            | FSA18   | 0   | 1          | 0            | 0      | 1           | 0     | Х   | Х   | х   |

|        | 64/32                             | 11FFFFH<br>110000H            | 08FFFFH<br>088000H            | FSA17   | 0   | 1          | 0            | 0      | 0           | 1     | Х   | Х   | х   |

|        | 64/32                             | 10FFFFH<br>100000H            | 087FFFH<br>080000H            | FSA16   | 0   | 1          | 0            | 0      | 0           | 0     | х   | Х   | Х   |

|        | 64/32                             | 0FFFFFH<br>0F0000H            | 07FFFH<br>078000H             | FSA15   | 0   | 0          | 1            | 1      | 1           | 1     | х   | х   | Х   |

|        | 64/32                             | 0EFFFFH<br>0E0000H            | 077FFFH<br>070000H            | FSA14   | 0   | 0          | 1            | 1      | 1           | 0     | Х   | Х   | Х   |

|        | 64/32                             | 0DFFFFH<br>0D0000H            | 06FFFFH<br>068000H            | FSA13   | 0   | 0          | 1            | 1      | 0           | 1     | Х   | Х   | х   |

|        | 64/32                             | 0CFFFFH<br>0C0000H            | 067FFFH<br>060000H            | FSA12   | 0   | 0          | 1            | 1      | 0           | 0     | Х   | х   | Х   |

|        | 64/32                             | 0BFFFFH<br>0B0000H            | 05FFFFH<br>058000H            | FSA11   | 0   | 0          | 1            | 0      | 1           | 1     | х   | х   | Х   |

|        | 64/32                             | 0AFFFFH<br>0A0000H            | 057FFFH<br>050000H            | FSA10   | 0   | 0          | 1            | 0      | 1           | 0     | х   | х   | х   |

|        | 64/32                             | 09FFFFH<br>090000H            | 04FFFH<br>048000H             | FSA9    | 0   | 0          | 1            | 0      | 0           | 1     | Х   | Х   | Х   |

|        | 64/32                             | 08FFFFH<br>080000H            | 047FFFH<br>040000H            | FSA8    | 0   | 0          | 1            | 0      | 0           | 0     | Х   | х   | Х   |

|        | 64/32                             | 07FFFFH<br>070000H            | 03FFFFH<br>038000H            | FSA7    | 0   | 0          | 0            | 1      | 1           | 1     | х   | х   | Х   |

|        | 64/32                             | 06FFFFH<br>060000H            | 037FFFH<br>030000H            | FSA6    | 0   | 0          | 0            | 1      | 1           | 0     | х   | х   | х   |

|        | 64/32                             | 05FFFFH<br>050000H            | 02FFFFH<br>028000H            | FSA5    | 0   | 0          | 0            | 1      | 0           | 1     | Х   | Х   | Х   |

|        | 64/32                             | 04FFFFH<br>040000H            | 027FFFH<br>020000H            | FSA4    | 0   | 0          | 0            | 1      | 0           | 0     | Х   | Х   | Х   |

|        | 64/32                             | 03FFFFH<br>030000H            | 01FFFFH<br>018000H            | FSA3    | 0   | 0          | 0            | 0      | 1           | 1     | Х   | Х   | х   |

|        | 64/32                             | 02FFFFH<br>020000H            | 017FFFH<br>010000H            | FSA2    | 0   | 0          | 0            | 0      | 1           | 0     | х   | х   | х   |

|        | 64/32                             | 01FFFFH<br>010000H            | 00FFFFH                       | FSA1    | 0   | 0          | 0            | 0      | 0           | 1     | х   | х   | х   |

|        | 64/32                             | 00FFFFH                       | 008000H<br>007FFFH            | FSA0    | 0   | 0          | 0            | 0      | 0           | 0     | х   | х   | Х   |

|        |                                   | 000000H                       | 000000H                       |         |     |            |              |        |             |       |     |     |     |

# **★** Sector Group Address Table (Flash Memory)

| Sector group | A20 | A19 | A18 | A17 | A16 | A15 | A14 | A13 | A12 | Size               | Sector      |

|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------|-------------|

| SGA0         | 0   | 0   | 0   | 0   | 0   | 0   | ×   | ×   | ×   | 64 KB (1 Sector)   | FSA0        |

| SGA1         | 0   | 0   | 0   | 0   | 0   | 1   | ×   | ×   | ×   | 192 KB (3 Sectors) | FSA1-FSA3   |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 1   |     |     |     |                    |             |

| SGA2         | 0   | 0   | 0   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA4-FSA7   |

| SGA3         | 0   | 0   | 1   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA8-FSA11  |

| SGA4         | 0   | 0   | 1   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA12-FSA15 |

| SGA5         | 0   | 1   | 0   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA16-FSA19 |

| SGA6         | 0   | 1   | 0   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA20-FSA23 |

| SGA7         | 0   | 1   | 1   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA24-FSA27 |

| SGA8         | 0   | 1   | 1   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA28-FSA31 |

| SGA9         | 1   | 0   | 0   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA32-FSA35 |

| SGA10        | 1   | 0   | 0   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA36-FSA39 |

| SGA11        | 1   | 0   | 1   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA40-FSA43 |

| SGA12        | 1   | 0   | 1   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA44-FSA47 |

| SGA13        | 1   | 1   | 0   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA48-FSA51 |

| SGA14        | 1   | 1   | 0   | 1   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA52-FSA55 |

| SGA15        | 1   | 1   | 1   | 0   | ×   | ×   | ×   | ×   | ×   | 256 KB (4 Sectors) | FSA56-FSA59 |

| SGA16        | 1   | 1   | 1   | 1   | 0   | 0   | ×   | ×   | ×   | 192 KB (3 Sectors) | FSA60-FSA62 |

|              |     |     |     |     | 0   | 1   |     |     |     |                    |             |

|              |     |     |     |     | 1   | 0   |     |     |     |                    |             |

| SGA17        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 8 KB (1 Sector)    | FSA63       |

| SGA18        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 1   | 8 KB (1 Sector)    | FSA64       |

| SGA19        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 0   | 8 KB (1 Sector)    | FSA65       |

| SGA20        | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 1   | 8 KB (1 Sector)    | FSA66       |

| SGA21        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0   | 8 KB (1 Sector)    | FSA67       |

| SGA22        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 1   | 8 KB (1 Sector)    | FSA68       |

| SGA23        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 8 KB (1 Sector)    | FSA69       |

| SGA24        | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 8 KB (1 Sector)    | FSA70       |

$\textbf{Remark} \hspace{0.2cm} \times \hspace{0.1cm} : \hspace{0.1cm} V \hspace{0.1cm} \text{IH or } \hspace{0.1cm} V \hspace{0.1cm} \text{IL} \hspace{0.1cm}$

# **Command Sequence (Flash Memory)**

| Command sequ                        | uence     | Bus      | 1st bus | Cycle | 2nd bu  | s Cycle               | 3rd bus | S Cycle | 4th bus | S Cycle | 5th bus | s Cycle | 6th bus | Cycle |

|-------------------------------------|-----------|----------|---------|-------|---------|-----------------------|---------|---------|---------|---------|---------|---------|---------|-------|

|                                     |           | Cycle    | Address | Data  | Address | Data                  | Address | Data    | Address | Data    | Address | Data    | Address | Data  |

| Read / Reset Note1                  |           | 1        | ×××Н    | F0H   | RA      | RD                    | -       | _       | _       | -       | -       | _       | _       | -     |

| Read / Reset Note1                  | BYTE mode | 3        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | F0H     | RA      | RD      | -       | -       | _       | ı     |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Program                             | BYTE mode | 4        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | A0H     | PA      | PD      | 1       | -       | -       | ı     |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Program Suspend Note 2              |           | 1        | ВА      | вон   | -       | Ī                     | -       | ı       | -       | ı       | -       | ı       | -       | ı     |

| Program Resume Note 3               |           | 1        | ВА      | 30H   | -       | Ī                     | -       | ı       | -       | ı       | -       | ı       | -       | ı     |

| Chip Erase                          | BYTE mode | 6        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 80H     | AAAH    | AAH     | 555H    | 55H     | AAAH    | 10H   |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         | 555H    |         | 2AAH    |         | 555H    |       |

| Sector Erase                        | BYTE mode | 6        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 80H     | AAAH    | AAH     | 555H    | 55H     | FSA     | 30H   |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         | 555H    |         | 2AAH    |         |         |       |

| Sector Erase Suspend Note           | e 4       | 1        | ВА      | вон   | -       | -                     | -       | -       | -       | -       | -       | _       | -       | 1     |

| Sector Erase Resume Not             |           | 1        | ВА      | 30H   | -       | -                     | -       | -       | -       | -       | -       | _       | -       | 1     |

| Unlock Bypass Set                   | BYTE mode | 3        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 20H     | -       | -       | -       | _       | -       | 1     |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Unlock Bypass Program N             | ote 6     | 2        | ×××Н    | A0H   | PA      | PD                    | -       | _       | _       | -       | -       | _       | _       | -     |

| Unlock Bypass Reset Note            |           | 2        | ВА      | 90H   | ×××Н    | 00H <sup>Note11</sup> | -       | -       | -       | -       | -       | _       | -       | 1     |

| Product ID                          | BYTE mode | 3        | AAAH    | AAH   | 555H    | 55H                   | (BA)    | 90H     | IA      | ID      | -       | _       | _       | -     |

|                                     |           |          |         |       |         |                       | AAAH    |         |         |         |         |         |         |       |

|                                     | WORD mode |          | 555H    |       | 2AAH    |                       | (BA)    |         |         |         |         |         |         |       |

|                                     |           |          |         |       |         |                       | 555H    |         |         |         |         |         |         |       |

| Sector Group Protection             | Note 7    | 4        | ×××H    | 60H   | SPA     | 60H                   | SPA     | 40H     | SPA     | SD      | -       | -       | -       | -     |

| Sector Group Unprotect <sup>N</sup> | lote 8    | 4        | хххН    | 60H   | SUA     | 60H                   | SUA     | 40H     | SUA     | SD      | -       | _       | _       | -     |

| Query Note 9                        | BYTE mode | 1        | AAH     | 98H   | -       | -                     | -       | -       | _       | -       | -       | -       | _       | -     |

|                                     | WORD mode |          | 55H     |       |         |                       |         |         |         |         |         |         |         |       |

| Extra One Time Protect              | BYTE mode | 3        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 88H     | _       | -       | -       | -       | _       | _     |

| Sector Entry                        | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Extra One Time Protect              | BYTE mode | 4        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | A0H     | PA      | PD      | 1       | -       | -       | ı     |

| Sector Program Note 10              | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Extra One Time Protect              | BYTE mode | 6        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 80H     | AAAH    | AAH     | 555H    | 55H     | EOTPSA  | 30H   |

| Sector Erase Note 10                | WORD mode | <u> </u> | 555H    |       | 2AAH    |                       | 555H    |         | 555H    |         | 2AAH    |         |         |       |

| Extra One Time Protect              | BYTE mode | 4        | AAAH    | AAH   | 555H    | 55H                   | AAAH    | 90H     | xxxH    | 00H     | _       | _       | _       | _     |

| Sector Reset Note 10                | WORD mode |          | 555H    |       | 2AAH    |                       | 555H    |         |         |         |         |         |         |       |

| Extra One Time Protect S            | Sector    | 4        | ×××Н    | 60H   | EOTPSA  | 60H                   | EOTPSA  | 40H     | EOTPSA  | SD      | -       | -       | -       | -     |

| Protection Note 10                  |           |          |         |       |         |                       |         |         |         |         |         |         |         |       |

Data Sheet M15171EJ7V0DS

- **Notes 1.** Both these read / reset commands reset the device to the read mode.

- **2.** Programming is suspended if B0H is input to the bank address being programmed to in a program operation.

- **3.** Programming is resumed if 30H is input to the bank address being suspended to in a program-suspend operation.

- 4. Erasure is suspended if B0H is input to the bank address being erased in a sector erase operation.

- **5.** Erasure is resumed if 30H is input to the bank address being suspended in a sector-erase-suspend operation.

- 6. Valid only in the unlock bypass mode.

- 7. Valid only when /RESET = VID (except in the Extra One Time Protect Sector mode).

- 8. The command sequence that protects a sector group is excluded.

- 9. Only A0 to A6 are valid as an address.

- 10. Valid only in the Extra One Time Protect Sector mode.

- 11. This command can be used even if this data is F0H.

- Remarks 1. Specify address 555H (A10 to A0) in the WORD mode, and AAAH (A10 to A0, A-1) in the BYTE mode.

- 2. RA: Read address

- RD: Read data

- IA : Address input

- xx00H (to read the manufacturer code)

- xx02H (to read the device code in the BYTE mode)

- xx01H (to read the device code in the WORD mode)

- ID : Code output. Refer to the **Product ID code (Manufacturer code / Device code) (Flash Memory)**.

- PA: Program address

- PD: Program data

- FSA: Erase sector address. The sector to be erased is selected by the combination of this address. Refer to the **Sector Organization / Sector Address Table (Flash Memory)**.

- BA: Bank address. Refer to the Sector Organization / Sector Address Table (Flash Memory).

- SPA: Sector group address to be protected. Set sector group address (SGA) and (A6, A1, A0) = (VIL, VIH, VIL). For the sector group address, refer to the **Sector Group Address Table (Flash Memory)**.

- SUA: Unprotect sector group address. Set sector group address (SGA) and (A6, A1, A0) = (Vih, Vih, Vil). For the sector group address, refer to the **Sector Group Address Table (Flash Memory)**.

- SD: Data for verifying whether sector groups read from the address specified by SPA, SUA, and EOTPSA are protected.

- EOTPSA: Extra One Time Protect Sector area addresses.

- BYTE mode: 3F0000H to 3FFFFFH, WORD mode: 1F8000H to 1FFFFFH

- **3.** The sector group address is don't care except when a program / erase address or read address are selected.

- **4.** For the operation of the bus, refer to **Bus Operations Table**.

- **5.**  $\times$  of address bit indicates ViH or ViL.

- 6. Refer to DUAL OPERATION FLASH MEMORY 32M BITS A SERIES Information (M14914E) for the flash memory commands.

# Product ID Code (Manufacturer Code / Device Code) (Flash Memory)

| Product ID Code   |    | Address inputs |    | Output            |

|-------------------|----|----------------|----|-------------------|

|                   | A6 | A1             | A0 | Hex               |

| Manufacturer Code | L  | L              | L  | 10H               |

| Device code       | L  | L              | Н  | 50H (BYTE mode),  |

|                   |    |                |    | 2250H (WORD mode) |

| Product      | t ID Code |     |     |     |     |     |     |     |     | Code | outp | uts |     |     |     |     |     |       |

|--------------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-------|

|              |           | I/O  | I/O  | I/O | I/O | I/O | I/O | I/O | I/O | Hex   |

|              |           | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7    | 6    | 5   | 4   | 3   | 2   | 1   | 0   | пех   |

| Manufacturer | Code      | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0    | 0    | 0   | 1   | 0   | 0   | 0   | 0   | 10H   |

| Device code  | BYTE mode | A-1 | х   | х   | х   | х   | х   | х   | х   | 0    | 1    | 0   | 1   | 0   | 0   | 0   | 0   | 50H   |

|              | WORD mode | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 0    | 1    | 0   | 1   | 0   | 0   | 0   | 0   | 2250H |

Remark  $H: V_{IH}, L: V_{IL}, x: Hi-Z$

**★** Hardware Sequence Flags, Hardware Data Protection (Flash Memory)

Refer to DUAL OPERATION FLASH MEMORY 32M BITS A SERIES Information (M14914E).

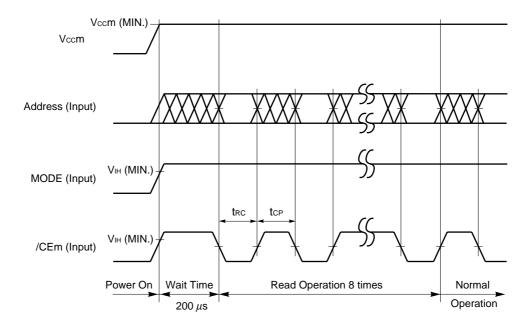

#### Initialization (Mobile specified RAM)

The MC-242443 is initialized in the power-on sequence according to the following.

- (1) To stabilize internal circuits, before turning on the power, a 200  $\mu$ s or longer wait time must precede any signal toggling.

- (2) After the wait time, read operation must be performed at least 8 times. After that, it can be normal operation.

**Figure 1. Initialization Timing Chart**

Cautions 1. Following power application, make MODE and /CEm high level during the wait time interval.

- 2. Following power application, make MODE high level during the wait time and eight read operations.

- 3. The read operation must satisfy the specs described on page 21 (Read Cycle (Mobile specified RAM)).

- 5. Read operation must be executed with toggled the /CEm pin.

- 6. To prevent bus contention, it is recommended to set /OE to high level. However, do not input data to the I/O pins if /OE is low level during a read operation.

#### **Standby Mode (Flash Memory)**

Standby Mode 1 and Standby Mode 2 differ as shown below.

**Table 1. Standby Mode Characteristics**

| Standby Mode | Memory Cell Data Hold | Standby Supply Current (μA) |

|--------------|-----------------------|-----------------------------|

| Mode 1       | Valid                 | 100 (Is <sub>B1</sub> )     |

| Mode 2       | Invalid               | 10 (I <sub>SB2</sub> )      |

#### Standby Mode State Machine (Flash Memory)

#### (1) From Active

To shift from this state to Standby Mode 1, change /CEm from V<sub>I</sub>L to V<sub>I</sub>H.

To shift from this state to Standby Mode 2, change /CEm from V<sub>IL</sub> to V<sub>I</sub> and change MODE from V<sub>I</sub> to V<sub>I</sub>.

# (2) From Standby Mode 1

To shift from this state to Active, change /CEm from VIH to VIL.

To shift from this state to Standby Mode 2, change MODE from  $V_{IH}$  to  $V_{IL}$ .

#### (3) From Standby Mode 2

When shifting from this state to the Active state or to Standby Mode 1, it is necessary to set MODE to V<sub>IH</sub> and perform a Dummy Read operation 8 times after waiting for 200  $\mu$ s, in the same way as at power application.

#### Refer to Figure 35. Standby Mode 2 entry and recovery Timing Chart (Mobile specified RAM).

After shifting to Active state, change /CEm to VIL.

After shifting to Standby Mode 1, do not change either MODE or /CEm.

Figure 2. Standby Mode State Machine

#### **Electrical Specifications**

Before turning on power, input Vss  $\pm$  0.2 V to the /RESET pin until Vccf  $\geq$  Vccf (MIN.).

#### **Absolute Maximum Ratings**

| Parameter                     | Symbol | Сог          | ndition                 | Rating                                              | Unit |

|-------------------------------|--------|--------------|-------------------------|-----------------------------------------------------|------|

| Supply voltage                | Vccf   | with respect | to Vss                  | -0.5 to +4.0                                        | V    |

|                               | Vccm   | with respect | to Vss                  | -0.5 to +4.0                                        |      |

| Input / Output voltage        | VT     | with respect | /WP(ACC), /RESET        | -0.5 <sup>Note 1</sup> to +13.0                     | V    |

|                               |        | to Vss       | except /WP(ACC), /RESET | -0.5 Note 1 to Vccf, Vccm + 0.4 (4.0 V MAX.) Note 2 |      |

| Ambient operation temperature | TA     |              |                         | -20 to +70                                          | °C   |

| Storage temperature           | Tstg   |              |                         | -55 to +125                                         | °C   |

**Notes 1.** -1.0 V (MIN.) (pulse width  $\leq 20 \text{ ns}$ )

2. Vccf, Vccm + 0.5 V (MAX.) (pulse width  $\leq$  20 ns)

Caution Exposing the device to stress above those listed in Absolute Maximum Rating could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

#### Common

| Parameter                     | Symbol     | Condition | MIN. | TYP. | MAX. | Unit |

|-------------------------------|------------|-----------|------|------|------|------|

| Supply voltage                | Vccf, Vccm |           | 2.6  |      | 3.0  | V    |

| Ambient operation temperature | TA         |           | -20  |      | +70  | °C   |

# Flash Memory

| Parameter                | Symbol | Condition | MIN. | TYP. | MAX.       | Unit |

|--------------------------|--------|-----------|------|------|------------|------|

| High level input voltage | ViH    |           | 2.4  |      | Vccf + 0.3 | V    |

| Low level input voltage  | VIL    |           | -0.3 |      | +0.5       | V    |

# Mobile specified RAM

| Parameter                | Symbol | Condition | MIN.       | TYP. | MAX.       | Unit |

|--------------------------|--------|-----------|------------|------|------------|------|

| High level input voltage | VIH    |           | Vccm x 0.8 |      | Vccm + 0.3 | V    |

| Low level input voltage  | VIL    |           | -0.3 Note  |      | Vccm x 0.2 | V    |

Note -0.5 V (MIN.) (Pulse width: 30 ns)

# DC Characteristics (Recommended Operating Conditions Unless Otherwise Noted)

#### Common

| Parameter              | Symbol | Test condition | MIN. | TYP. | MAX. | Unit |

|------------------------|--------|----------------|------|------|------|------|

| Input leakage current  | lы     |                | -1.0 |      | +1.0 | μΑ   |

| Output leakage current | ILO    |                | -1.0 |      | +1.0 | μΑ   |

# Flash Memory

|          | Param        | neter                  | Symbol             | Test cond                                           | ition             | MIN.     | TYP. | MAX. | Unit |

|----------|--------------|------------------------|--------------------|-----------------------------------------------------|-------------------|----------|------|------|------|

| High lev | el output vo | oltage                 | Vон                | Іон = $-500  \mu$ A, Vccf = Vc                      | cf (MIN.)         | Vccf-0.3 |      |      | V    |

| Low leve | el output vo | Itage                  | Vol                | IoL = +1.0 mA, Vccf = Vccf (MIN.)                   |                   |          |      | 0.3  | V    |

| Power    | Read         | BYTE mode              | Icc <sub>1</sub> f | Vccf = Vccf (MAX.),                                 | tcycle = 5 MHz    |          | 10   | 16   | mA   |

| supply   |              |                        |                    | /CEf = VIL, /OE = VIH                               | tcycle = 1 MHz    |          | 2    | 4    |      |

| current  |              | WORD mode              |                    |                                                     | tcycle = 5 MHz    |          | 10   | 16   |      |

|          |              |                        |                    |                                                     | tcycle = 1 MHz    |          | 2    | 4    |      |

|          | Program,     | Erase                  | Icc2f              | Vccf = Vccf (MAX.), /CEf                            | = VIL, /OE = VIH  |          | 15   | 30   | mA   |

|          | Standby      |                        | lccзf              | Vccf = Vccf (MAX.), /CEf                            | = /RESET =        |          | 0.2  | 5    | μΑ   |

|          |              |                        |                    | $/WP(ACC) = Vccf \pm 0.3$                           | V, /OE = VIL      |          |      |      |      |

|          | Standby /    | <sup>'</sup> Reset     | Icc4f              | Vccf = Vccf (MAX.), /RES                            | SET = Vss ± 0.2 V |          | 0.2  | 5    | μΑ   |

|          | Automation   | c sleep mode           | lcc5f              | $V_{IH} = V_{CC}f \pm 0.2 \text{ V}, V_{IL} = 0.00$ | Vss ± 0.2 V       |          | 0.2  | 5    | μΑ   |

|          | Read dur     | ing programming        | Icc6f              | $V_{IH} = V_{CC}f \pm 0.2 \text{ V}, V_{IL} = 0.00$ | Vss ± 0.2 V       |          | 21   | 45   | mA   |

|          | Read dur     | ing erasing            | Icc7f              | $V_{IH} = V_{CC}f \pm 0.2 \text{ V}, V_{IL} = 0.00$ | Vss ± 0.2 V       |          | 21   | 45   | mA   |

|          | Programn     | ning                   | Icc8f              | /CEf = VIL, /OE = VIH,                              |                   |          | 17   | 35   | mA   |

|          | during su    | spend                  |                    | Automatic programming                               | during suspend    |          |      |      |      |

|          | Accelerat    | ed                     | IACC               | /WP (ACC) pin                                       |                   |          | 5    | 10   | mA   |

|          | programn     | ning                   |                    | Vccf                                                |                   |          | 15   | 30   |      |

| /RESET   | high level i | nput voltage           | VID                | High Voltage is applied                             |                   | 11.5     |      | 12.5 | V    |

| Accelera | ated progra  | mming voltage          | VACC               | High Voltage is applied                             |                   | 8.5      |      | 9.5  | V    |

| Low Vcc  | f lock-out v | oltage <sup>Note</sup> | Vlko               |                                                     |                   |          |      | 1.7  | V    |

**<sup>★</sup> Note** When Vccf is equal to or lower than VLKO, the device ignores all write cycles. Refer to **DUAL OPERATION** FLASH MEMORY 32M BITS A SERIES Information (M14914E).

# Mobile specified RAM

| Parameter Symbol Test condit |                | Test condition   | MIN.                                                                    | TYP.                     | MAX. | Unit                     |    |

|------------------------------|----------------|------------------|-------------------------------------------------------------------------|--------------------------|------|--------------------------|----|

| High level output voltage    |                | Vон              | $I_{OH} = -0.5 \text{ mA}$                                              | $\text{Vccm} \times 0.8$ |      |                          | V  |

| Low level output voltage     |                | Vol              | IoL = 1 mA                                                              |                          |      | $\text{Vccm} \times 0.2$ | V  |

| Operating supply             | current        | Icca             | /CEm = $V_{IL}$ , Minimum cycle time, $I_{I/O} = 0$ mA                  |                          |      | 35                       | mA |

| Standby supply               | Standby Mode 1 | I <sub>SB1</sub> | $/CEm \ge Vccm - 0.2 \text{ V}, \text{ MODE } \ge Vccm - 0.2 \text{ V}$ |                          |      | 100                      | μΑ |

| current                      | Standby Mode 2 | I <sub>SB2</sub> | $/CEm \ge Vccm - 0.2 \text{ V}, \text{ MODE} \le 0.2 \text{ V}$         |                          |      | 10                       |    |

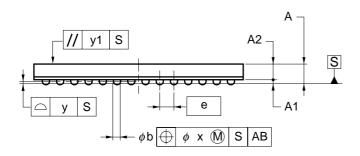

# AC Characteristics (Recommended Operating Conditions Unless Otherwise Noted)

# **AC Test Conditions**

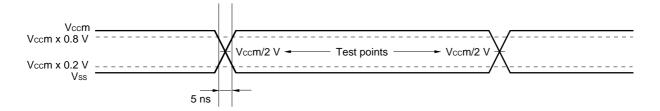

# Flash Memory

# Input Waveform (Rise and Fall Time ≤ 5 ns)

# **Output Waveform**

# **Output Load**

1 TTL + 30 pF

#### **Mobile specified RAM**

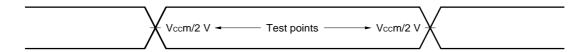

# Input Waveform (Rise and Fall Time ≤ 5 ns)

# **Output Waveform**

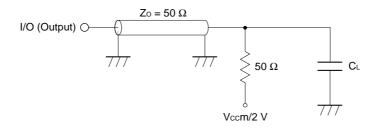

# **Output Load**

AC characteristics directed with the note should be measured with the output load shown in Figure.

CL: 50 pF 5 pF (tcLz, toLz, tBLz, tcHz, toHz, tBHz, tWHz, toW)

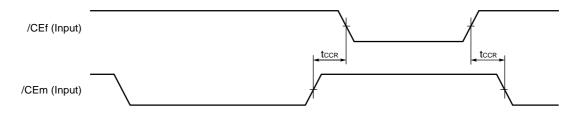

# /CEf, /CEm Timing

| Parameter               | Symbol | Test Condition | MIN. | TYP. | MAX. | Unit | Note |

|-------------------------|--------|----------------|------|------|------|------|------|

| /CEf, /CEm recover time | tccr   |                | 0    |      |      | ns   |      |

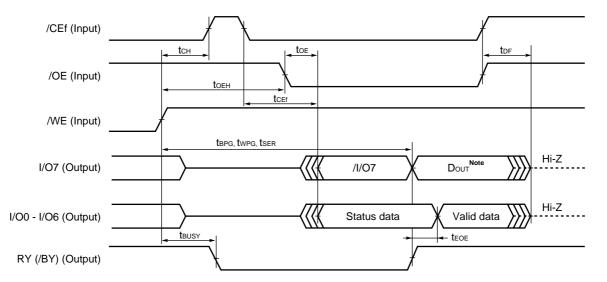

# Read Cycle (Flash Memory)

| Parameter                    |              | Symbol        | Test Condition          | MIN. | TYP. | MAX. | Unit | Note |

|------------------------------|--------------|---------------|-------------------------|------|------|------|------|------|

| Read cycle time              |              | <b>t</b> RC   |                         | 90   |      |      | ns   |      |

|                              | Vccf ≥ 2.7 V |               |                         | 85   |      |      |      |      |

| Address access time          |              | tacc          | /CEf = /OE = VIL        |      |      | 90   | ns   |      |

|                              | Vccf ≥ 2.7 V |               |                         |      |      | 85   |      |      |

| /CEf access time             |              | <b>t</b> CEf  | /OE = VIL               |      |      | 90   | ns   |      |

|                              | Vccf ≥ 2.7 V |               |                         |      |      | 85   |      |      |

| /OE access time              |              | toe           | /CEf = VIL              |      |      | 40   | ns   |      |

| Output disable time          |              | <b>t</b> DF   | /OE = VIL or /CEf = VIL |      |      | 30   | ns   |      |

| Output hold time             |              | <b>t</b> он   |                         | 0    |      |      | ns   |      |

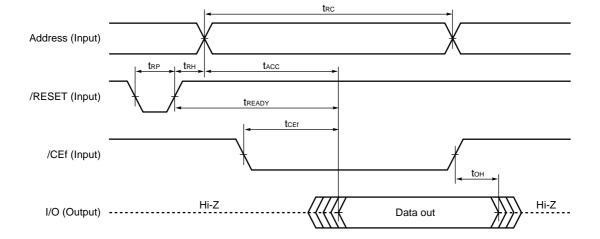

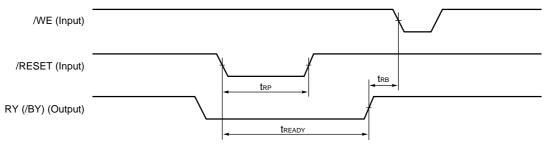

| /RESET pulse width           |              | <b>t</b> RP   |                         | 500  |      |      | ns   |      |

| /RESET hold time before read |              | <b>t</b> RH   |                         | 50   |      |      | ns   |      |

| /RESET low to read mode      |              | tREADY        |                         |      |      | 20   | μs   |      |

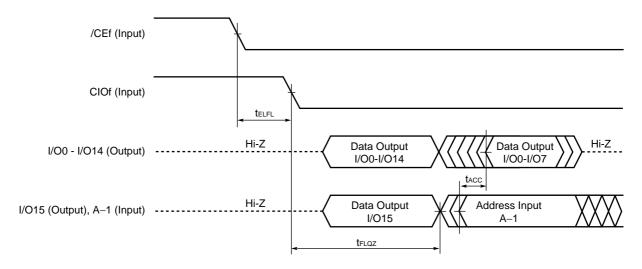

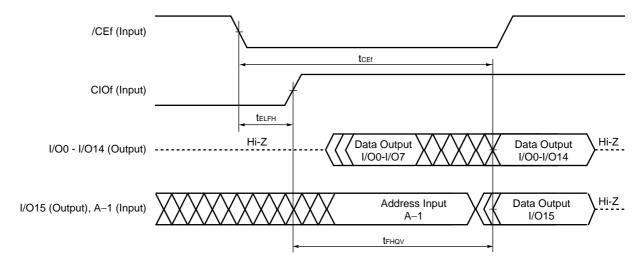

| /CEf low to CIOf low, high   |              | telfl/telfh   |                         |      |      | 5    | ns   |      |

| CIOf low output disable time |              | <b>t</b> FLQZ |                         |      |      | 30   | ns   |      |

| CIOf high access time        |              | <b>t</b> FHQV |                         | 90   |      |      | ns   |      |

|                              | Vccf ≥ 2.7 V |               |                         | 85   |      |      |      |      |

$\textbf{Remark} \quad \text{toF is the time from inactivation of /CEf or /OE to Hi-Z state output.}$

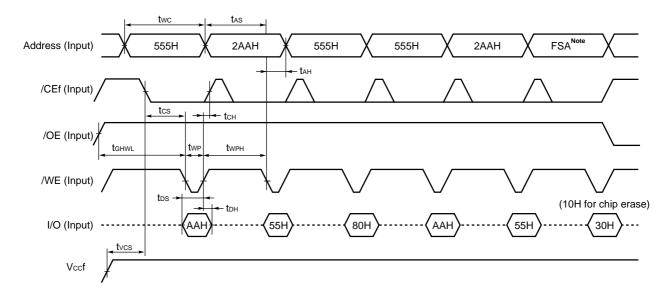

# Write Cycle (Erase / Program) (Flash Memory)

| Parameter Write evole time                          |                          | Symbol        | MIN. | TYP. | MAX. | Unit | Note |

|-----------------------------------------------------|--------------------------|---------------|------|------|------|------|------|

| Write cycle time                                    |                          | twc           | 90   |      |      | ns   |      |

|                                                     | Vccf ≥ 2.7 V             |               | 85   |      |      |      |      |

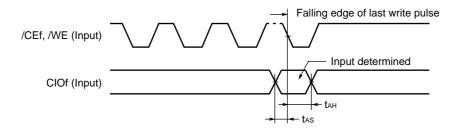

| Address setup time (/WE to address)                 |                          | <b>t</b> as   | 0    |      |      | ns   |      |

| Address setup time (/CEf to address)                |                          | <b>t</b> as   | 0    |      |      | ns   |      |

| Address hold time (/WE to address)                  |                          | <b>t</b> AH   | 45   |      |      | ns   |      |

| Address hold time (/CEf to address)                 |                          | <b>t</b> AH   | 45   |      |      | ns   |      |

| Input data setup time                               |                          | tos           | 35   |      |      | ns   |      |

| Input data hold time                                |                          | tон           | 0    |      |      | ns   |      |

| /OE hold time                                       | Read                     | tоен          | 0    |      |      | ns   |      |

|                                                     | Toggle bit, Data polling |               | 10   |      |      |      |      |

| Read recovery time before write (/OE                | to /CEf)                 | <b>t</b> GHEL | 0    |      |      | ns   |      |

| Read recovery time before write (/OE                | to /WE)                  | <b>t</b> GHWL | 0    |      |      | ns   |      |

| /WE setup time (/CEf to /WE)                        |                          | tws           | 0    |      |      | ns   |      |

| /CEf setup time (/WE to /CEf)                       |                          | tcs           | 0    |      |      | ns   |      |

| /WE hold time (/CEf to /WE)                         |                          | twн           | 0    |      |      | ns   |      |

| /CEf hold time (/WE to /CEf)                        |                          | tсн           | 0    |      |      | ns   |      |

| Write pulse width                                   |                          | twp           | 35   |      |      | ns   |      |

| /CEf pulse width                                    |                          | <b>t</b> CP   | 35   |      |      | ns   |      |

| Write pulse width high                              | <b>t</b> wph             | 30            |      |      | ns   |      |      |

| /CEf pulse width high                               |                          | tсрн          | 30   |      |      | ns   |      |

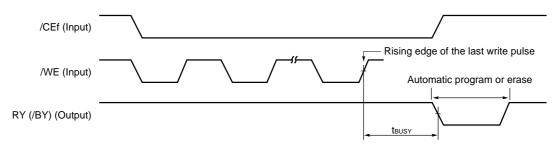

| Byte programming operation time                     |                          | <b>t</b> BPG  |      | 9    | 200  | μs   |      |

| Word programming operation time                     |                          | twpg          |      | 11   | 200  | μs   |      |

| Sector erase operation time                         |                          | tser          |      | 0.7  | 5    | S    | 1    |

| Vccf setup time                                     |                          | tvcs          | 50   |      |      | μs   |      |

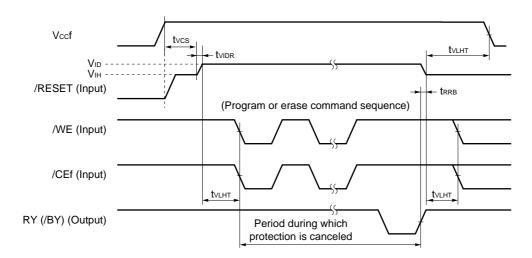

| RY (/BY) recovery time                              |                          | <b>t</b> RB   | 0    |      |      | ns   |      |

| /RESET pulse width                                  |                          | <b>t</b> RP   | 500  |      |      | ns   |      |

| /RESET high-voltage (V <sub>ID</sub> ) hold time fr | om high of RY(/BY)       | <b>t</b> rrb  | 20   |      |      | μs   |      |

| when sector group is temporarily unpr               | otect                    |               |      |      |      |      |      |

| /RESET hold time                                    |                          | tкн           | 50   |      |      | ns   |      |

| From completion of automatic                        |                          | <b>t</b> EOE  |      |      | 90   | ns   |      |

| program / erase to data output time                 | Vccf ≥ 2.7 V             |               |      |      | 85   |      |      |

| RY (/BY) delay time from valid program              | m or erase operation     | <b>t</b> BUSY |      |      | 90   | ns   |      |

| Address setup time to /OE low in togg               | le bit                   | taso          | 15   |      |      | ns   |      |

| Address hold time to /CEf or /OE high               | in toggle bit            | <b>t</b> aht  | 0    |      |      | ns   |      |

| /CEf pulse width high for toggle bit                |                          | <b>t</b> CEPH | 20   |      |      | ns   |      |

| /OE pulse width high for toggle bit                 |                          | <b>t</b> oeph | 20   |      |      | ns   |      |

| Voltage transition time                             |                          | <b>t</b> vlht | 4    |      |      | μs   | 2    |

| Rise time to V <sub>ID</sub> (/RESET)               |                          | tvidr         | 500  |      |      | ns   | 3    |

| Rise time to V <sub>ACC</sub> (/WP(ACC))            |                          | tvaccr        | 500  |      |      | ns   | 2    |

| Erase timeout time                                  |                          | <b>t</b> TOW  | 50   |      |      | μs   | 4    |

| Erase suspend transition time                       |                          | tspd          |      |      | 20   | μs   | 4    |

**Notes 1.** The preprogramming time prior to the erase operation is not included.

- 2. Sector group protection and accelerated mode only

- 3. Sector group protection only.

- 4. Table only.

# Write operation (Erase / Program) Performance (Flash Memory)

| Parameter                    | Description                     |                                | MIN.    | TYP. | MAX. | Unit   |

|------------------------------|---------------------------------|--------------------------------|---------|------|------|--------|

| Sector erase time            | Excludes programming time prior |                                | 0.7     | 5    | s    |        |

| Chip erase time              | Excludes programming time prior |                                | 50      |      | s    |        |

| Byte programming time        | Excludes system-level overhead  | Excludes system-level overhead |         |      | 200  | μs     |

| Word programming time        | Excludes system-level overhead  |                                |         | 11   | 200  | μs     |

| Chip programming time        | Excludes system-level overhead  | BYTE mode                      |         | 40   |      | s      |

|                              |                                 | WORD mode                      |         | 25   |      |        |

| Accelerated programming time | Excludes system-level overhead  |                                | 7       | 150  | μs   |        |

| Erase / Program cycle        |                                 |                                | 100,000 |      |      | cycles |

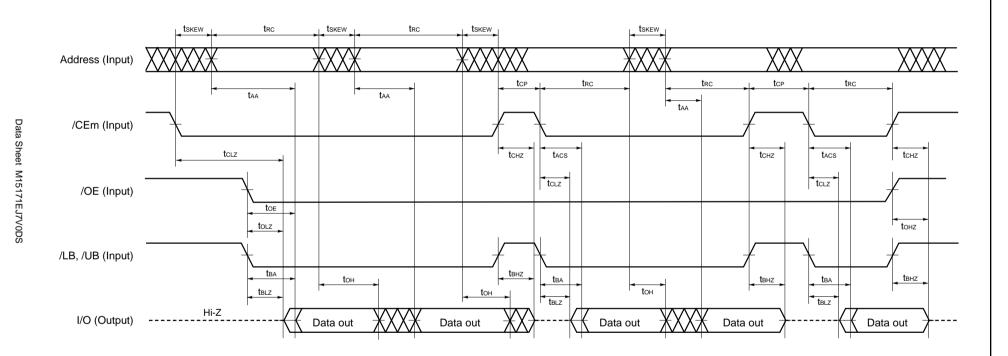

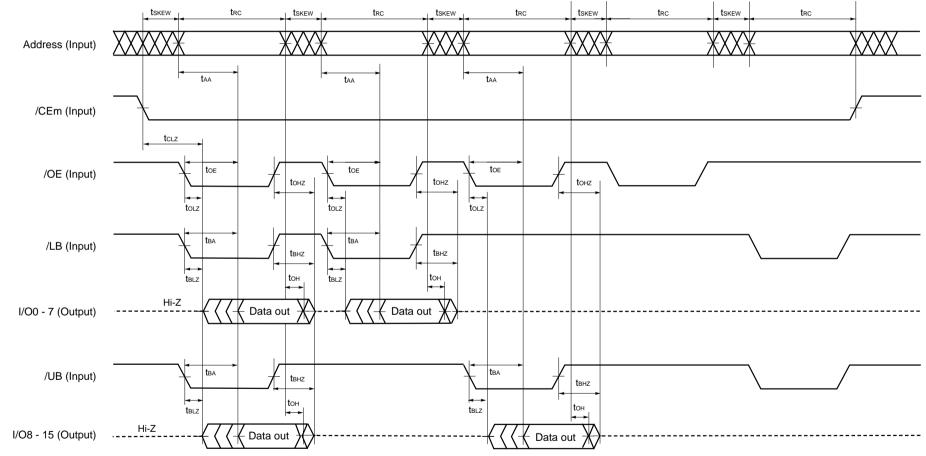

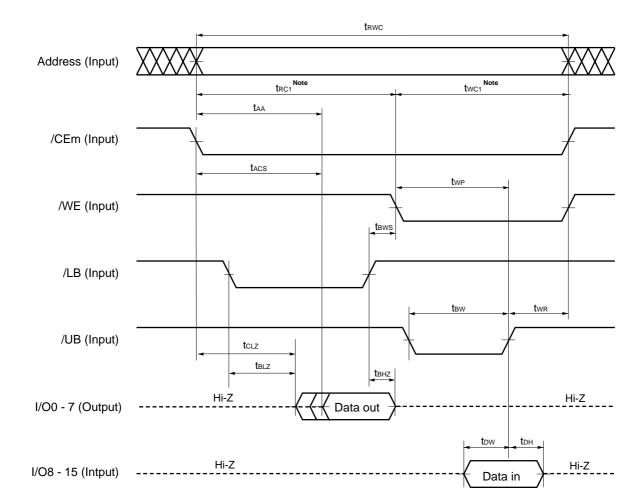

#### Read Cycle (Mobile specified RAM)

| Parameter                            | Symbol           | MC-242 | 443-B90 | MC-242 | 443-B95 | MC-242 | 443-B10 | Unit | Note |

|--------------------------------------|------------------|--------|---------|--------|---------|--------|---------|------|------|

|                                      |                  | MIN.   | MAX.    | MIN.   | MAX.    | MIN.   | MAX.    |      |      |

| Read cycle time                      | trc              | 80     | 10,000  | 90     | 10,000  | 110    | 10,000  | ns   | 1    |

| Identical address read cycle time    | t <sub>RC1</sub> | 80     | 10,000  | 90     | 10,000  | 110    | 10,000  | ns   | 2    |

| Address skew time                    | tskew            |        | 10      |        | 15      |        | 20      | ns   | 3    |

| /CEm pulse width                     | <b>t</b> CP      | 10     |         | 10     |         | 10     |         | ns   |      |

| Address access time                  | <b>t</b> AA      |        | 80      |        | 90      |        | 100     | ns   | 4    |

| /CEm access time                     | tacs             |        | 80      |        | 90      |        | 100     | ns   |      |

| /OE to output valid                  | <b>t</b> oe      |        | 35      |        | 40      |        | 50      | ns   | 5    |

| /LB, /UB to output valid             | <b>t</b> BA      |        | 35      |        | 40      |        | 50      | ns   |      |

| Output hold from address change      | tон              | 10     |         | 10     |         | 10     |         | ns   |      |

| /CEm to output in low impedance      | tclz             | 10     |         | 10     |         | 10     |         | ns   |      |

| /OE to output in low impedance       | tolz             | 5      |         | 5      |         | 5      |         | ns   |      |

| /LB, /UB to output in low impedance  | t <sub>BLZ</sub> | 5      |         | 5      |         | 5      |         | ns   |      |

| /CEm to output in high impedance     | tснz             |        | 25      |        | 25      |        | 25      | ns   |      |

| /OE to output in high impedance      | tонz             |        | 25      |        | 25      |        | 25      | ns   |      |

| /LB, /UB to output in high impedance | <b>t</b> BHZ     |        | 25      |        | 25      |        | 25      | ns   |      |

**Notes 1.** One read cycle (tRC) must satisfy the minimum value (tRC(MIN.)) and maximum value (tRC(MAX.) =  $10 \mu s$ ). tRC indicates the time from the /CEm low level input point or address determination point, whichever is later, to the /CEm high level input point or the next address change start point, whichever is earlier. As a result, there are the following four conditions for tRC.

1) Time from address determination point to /CEm high level input point (address access)

2) Time from address determination point to next address change start point (address access)

3) Time from /CEm low level input point to next address change start point (/CEm access)

4) Time from /CEm low level input point to /CEm high level input point (/CEm access)

- 2. The identical address read cycle time (tRc1) is the cycle time of one read operation when performing continuous read operations toggling /OE , /LB, and /UB with the address fixed and /CEm low level. Perform settings so that the sum (tRc) of the identical address read cycle times (tRc1) is 10 μs or less.

- 3. tskew indicates the following three types of time depending on the condition.

- 1) When switching /CEm from high level to low level, tskew is the time from the /CEm low level input point until the next address is determined.

- 2) When switching /CEm from low level to high level, tskew is the time from the address change start point to the /CEm high level input point.

- 3) When /CEm is fixed to low level, tskew is the time from the address change start point until the next address is determined.

Since specs are defined for tskew only when /CEm is active, tskew is not subject to limitations when /CEm is switched from high level to low level following address determination, or when the address is changed after /CEm is switched from low level to high level.

- **4.** Regarding tax and tacs, only tax is satisfied during address access (refer to 1) and 2) of **Note 1**), and only tacs is satisfied during /CEm access (refer to 3) of **Note 1**).

- **5.** Regarding tbA and toE, only tbA is satisfied if /OE becomes active later than /UB and /LB, and only toE is satisfied if /UB and /LB become active before /OE.

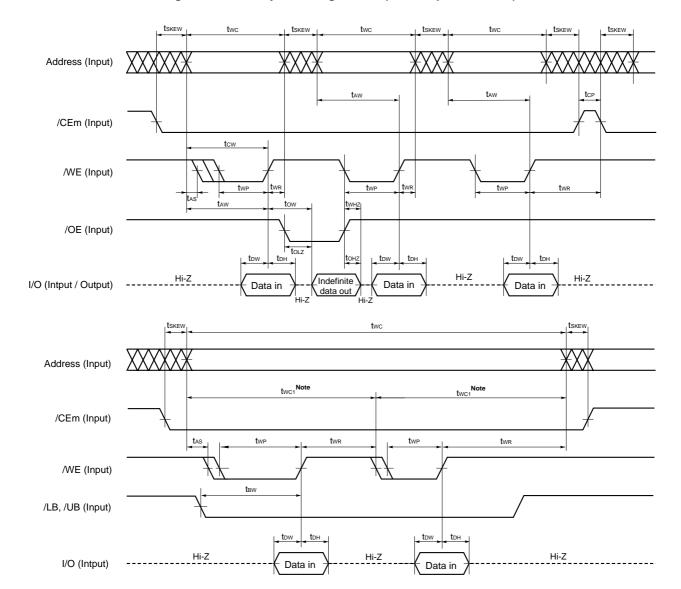

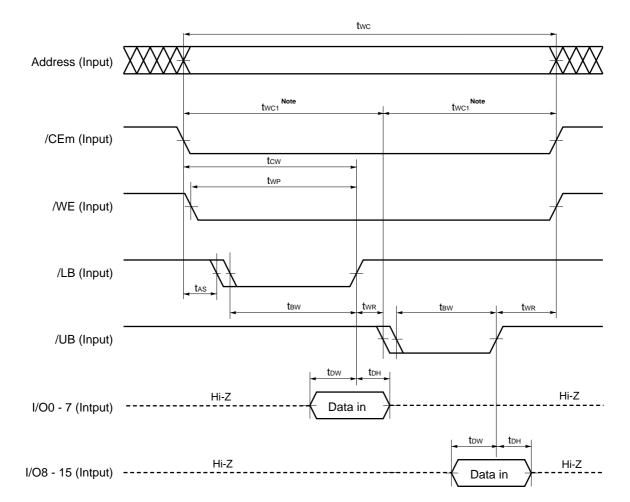

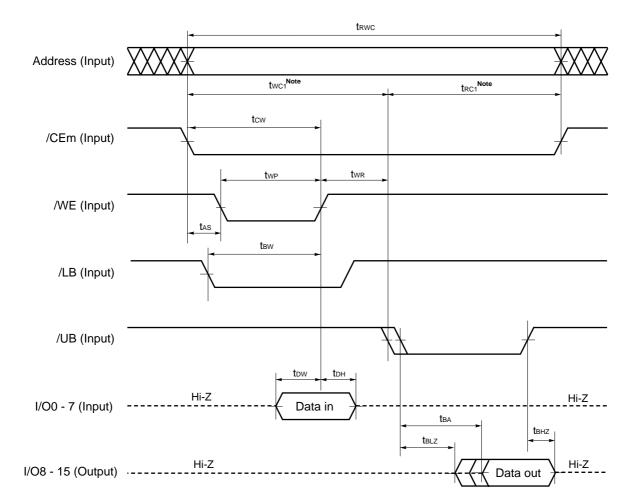

#### Write Cycle (Mobile specified RAM)

| Parameter                          | Symbol          | MC-242 | 443-B90 | MC-242 | 443-B95 | MC-242 | 443-B10 | Unit | Note |

|------------------------------------|-----------------|--------|---------|--------|---------|--------|---------|------|------|

|                                    |                 | MIN.   | MAX.    | MIN.   | MAX.    | MIN.   | MAX.    |      |      |

| Write cycle time                   | twc             | 80     | 10,000  | 90     | 10,000  | 110    | 10,000  | ns   | 1    |

| Identical address write cycle time | twc1            | 80     | 10,000  | 90     | 10,000  | 110    | 10,000  | ns   | 2    |

| Address skew time                  | tskew           |        | 10      |        | 15      |        | 20      | ns   | 3    |

| /CEm to end of write               | tcw             | 40     |         | 50     |         | 60     |         | ns   | 4    |

| /LB, /UB to end of write           | t <sub>BW</sub> | 30     |         | 35     |         | 40     |         | ns   |      |

| Address valid to end of write      | taw             | 35     |         | 45     |         | 55     |         | ns   |      |

| Write pulse width                  | twp             | 30     |         | 35     |         | 40     |         | ns   |      |

| Write recovery time                | twr             | 20     |         | 20     |         | 20     |         | ns   | 5    |

| /CEm pulse width                   | <b>t</b> cp     | 10     |         | 10     |         | 10     |         | ns   |      |

| Address setup time                 | tas             | 0      |         | 0      |         | 0      |         | ns   |      |

| Byte write hold time               | tвwн            | 20     |         | 20     |         | 20     |         | ns   |      |

| Data valid to end of write         | tow             | 20     |         | 25     |         | 30     |         | ns   |      |

| Data hold time                     | tон             | 0      |         | 0      |         | 0      |         | ns   |      |

| /OE to output in low impedance     | tolz            | 5      |         | 5      |         | 5      |         | ns   |      |

| /WE to output in high impedance    | <b>t</b> wnz    |        | 25      |        | 25      |        | 25      | ns   |      |

| /OE to output in high impedance    | tонz            |        | 25      |        | 25      |        | 25      | ns   |      |

| Output active from end of write    | tow             | 5      |         | 5      |         | 5      |         | ns   |      |

**Notes 1.** One write cycle (twc) must satisfy the minimum value (twc(MIN.)) and the maximum value (twc(MAX.) =  $10 \mu s$ ). two indicates the time from the /CEm low level input point or address determination point, whichever is after, to the /CEm high level input point or the next address change start point, whichever is earlier. As a result, there are the following four conditions for twc.

- 1) Time from address determination point to /CEm high level input point

- 2) Time from address determination point to next address change start point

- 3) Time from /CEm low level input point to next address change start point

- 4) Time from /CEm low level input point to /CEm high level input point

- 2. The identical address read cycle time (twc1) is the cycle time of one write cycle when performing continuous write operations with the address fixed and /CEm low level, changing /LB and /UB at the same time, and toggling /WE, as well as when performing a continuous write toggling /LB and /UB. Make settings so that the sum (twc) of the identical address write cycle times (twc1) is 10 μs or less.

- 3. tskew indicates the following three types of time depending on the condition.

- 1) When switching /CEm from high level to low level, tskew is the time from the /CEm low level input point until the next address is determined.

- 2) When switching /CEm from low level to high level, tskew is the time from the address change start point to the /CEm high level input point.

- 3) When /CEm is fixed to low level, tskew is the time from the address change start point until the next address is determined.

Since specs are defined for tskew only when /CEm is active, tskew is not subject to limitations when /CEm is switched from high level to low level following address determination, or when the address is changed after /CEm is switched from low level to high level.

#### 4. Definition of write start and write end

|                       | /CEm   | /WE    | /LB, /UB | Status                                            |  |  |

|-----------------------|--------|--------|----------|---------------------------------------------------|--|--|

| Write start pattern 1 | H to L | L      | L        | If /WE, /LB, /UB are low level, time when /CEm    |  |  |

|                       |        |        |          | changes from high level to low level              |  |  |

| Write start pattern 2 | L      | H to L | L        | If /CEm, /LB, /UB are low level, time when /WE    |  |  |

|                       |        |        |          | changes from high level to low level              |  |  |

| Write start pattern 3 | L      | L      | H to L   | If /CEm, /WE are low level, time when /LB or /UB  |  |  |

|                       |        |        |          | changes from high level to low level              |  |  |

| Write end pattern 1   | L      | L to H | L        | If /CEm, /WE, /LB, /UB are low level, time when   |  |  |

|                       |        |        |          | /WE changes from low level to high level          |  |  |

| Write end pattern 2   | L      | L      | L to H   | When /CEm, /WE, /LB, /UB are low level, time when |  |  |

|                       |        |        |          | /LB or /UB changes from low level to high level   |  |  |

- **5.** Definition of write end recovery time (twr)

- 1) Time from write end to address change start point, or from write end to /CEm high level input point

- 2) When /CEm, /LB, /UB are low level and continuously written to the identical address, time from /WE high level input point to /WE low level input point

- 3) When /CEm, /WE are low level and continuously written to the identical address, time from /LB or /UB high level input point, whichever is later, to /LB or /UB low level input point, whichever is earlier.

- 4) When /CEm is low level and continuously written to the identical address, time from write end to point at which /WE, /LB, or /UB starts to change from high level to low level, whichever is earliest.

#### Read Write Cycle (Mobile specified RAM)

| Parameter             | Symbol       | MC-242443-B90 |        | MC-242443-B95 |        | MC-242443-B10 |        | Unit | Note |

|-----------------------|--------------|---------------|--------|---------------|--------|---------------|--------|------|------|

|                       |              | MIN.          | MAX.   | MIN.          | MAX.   | MIN.          | MAX.   |      |      |

| Read write cycle time | trwc         |               | 10,000 |               | 10,000 |               | 10,000 | ns   | 1, 2 |

| Byte write setup time | <b>t</b> BWS | 20            |        | 20            |        | 20            |        | ns   |      |

| Byte read setup time  | <b>t</b> BRS | 20            |        | 20            |        | 20            |        | ns   |      |

- **Notes 1.** Make settings so that the sum (trwc) of the identical address read cycle time (trc1) and the identical address write cycle time (twc1) is 10  $\mu$ s or less when a write is performed at the identical address using /UB following a read using /LB with /CEm low level, or when a write is performed using /LB following a read using /UB.

- **2.** Make settings so that the sum (t<sub>RWC</sub>) of the identical address read cycle time (t<sub>RC1</sub>) and the identical address write cycle time (t<sub>WC1</sub>) is 10 μs or less when a read is performed at the identical address using /UB following a write using /LB with /CEm low level, or when a read is performed using /LB following a write using /UB.

Figure 3. Alternating Mobile specified RAM to Flash Memory Timing Chart

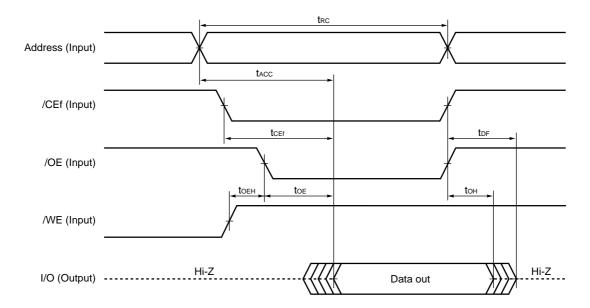

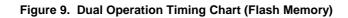

Figure 4. Read Cycle Timing Chart 1 (Flash Memory)

Figure 5. Read Cycle Timing Chart 2 (Flash Memory)

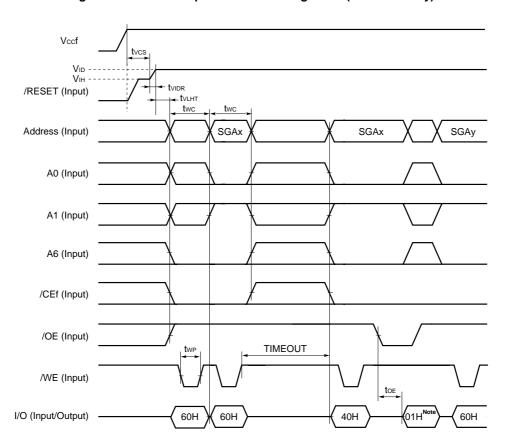

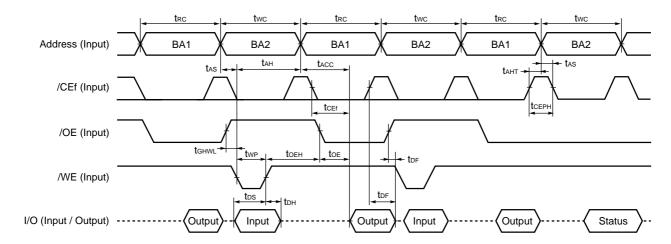

Figure 6. Sector Group Protection Timing Chart (Flash Memory)

**Note** The sector group protection verification result is output.

01H: The sector group is protected.

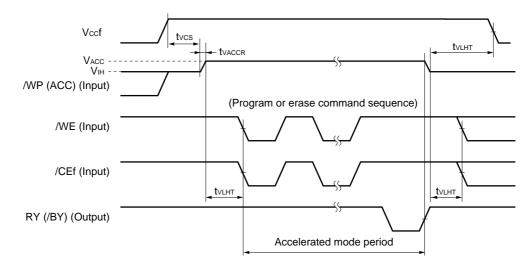

00H: The sector group is not protected.