**APPLICATION NOTE**

# ST75C502 - BULK DELAY MANAGEMENT

## **1 - INTRODUCTION**

The purpose of this application note is to describe the way the user must handle the interrupt reserved for Bulk delay managment.

A V.32bis modem use echo canceller technology, it substract from its received signal an estimation of its own signal echoed by the PSTN. As the transmition can have a very long delay, especially while using satellite (up to 1.4 Second), its is mandatory to memorise all the signal that have been send during the last 1.4 second. To reduce the size of the memory needed, instead of storing the signal, we just store the symbols that were transmitted. However one can see that, if we want to handle two satellites hops, it is necessary to have a 1.4 second \* 2400 symbols by second = 3360 symbols. Each symbol can be packed using a single byte, so the size of this BULK memory is 3360 bytes.

In the ST75C502, instead of adding a 4K byte inside the DSP, just to be used like a FIFO, to store and recall one symbol (Byte) each baud (0.4ms), the Bulk Delay can be implemented using the Host interface Memory. We assume that the host processor have enough memory to allocate a 4K byte inside its own Data Memory.

## 2 - INITIALIZATION

Prior to any operation, the user must assign the Bulk Delay (bulk\_delay\_line) inside its data space. The length of the bulk delay is depending of the Maximum Round Trip Delay (MAX\_BULK\_DELAY) that we want to handle.

#define MAX\_BULK\_DELAY 3360 /\* 1.4 Second Maximum Roud Trip Delay \*/

unsigned char bulk\_delay\_line[MAX\_BULK\_DELAY]; /\* Symbol's Storage Area \*/

Code : 1 /\* "C" Global Declaration \*/

For further understanding we define few prototype functions :

- ST75c5x\_read: read a DUAL RAM location.

- ST75c5x\_write: write a DUAL RAM location.

- ST75c5x\_send\_cci\_command: send a CCI Command to the ST75C502.

/\* Read a DUAL RAM Location: return code is the contain of the RAM \*/ unsigned char ST75c5x\_read(unsigned char address);

/\* Write a DUALRAM Location: write data at address \*/ void ST75c5x\_write(unsigned char address, unsigned char data);

/\* Send a CCI Command to the ST75C502 \*/ unsigned char ST75c5x\_send\_cci\_command(unsigned char opcode, unsigned char param[4]);

## ST75C502 - BULK DELAY MANAGMENT

## Code : 2 /\* "C" Prototype Function \*/

An Example of implementation of ST75c5x\_send\_cci\_command is given at the end of this application note.

The mechanism implemented inside the ST75C502 assumes that the address of the bulk\_delay\_line is a 16 bit word (short int) and that each byte of the bulk\_delay\_line are located continiously (+1). At the begining we must initialize this mechanism by giving it the two addresses **BA\_ADDR** and **TO\_ADDR**.

We assume that the **"C"** compiler contains two functions to convert a pointer into its physical address and an address (as a short int) into a pointer. Let define these two prototypes:

/\* Convert a Pointer into a Physical Address \*/ short int PTR\_ADDR( unsigned char \*var);

/\* Convert a Physical Address into a Pointer \*/ unsigned char \*ADDR\_PTR( short int var);

## Code : 3 /\* "C" Pointer to Interger Conversion Prototype \*/

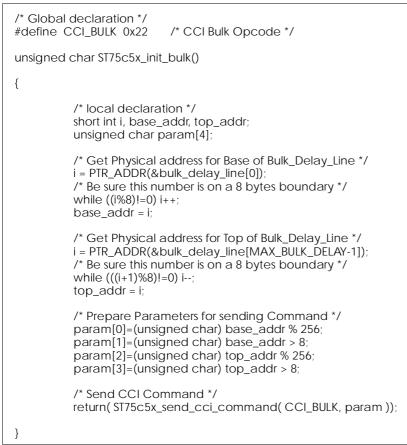

After the CONF command used to select the V.32bis mode of operation, we have to initialize the bulk delay mechanism with a BULK command:

Code : 4 /\* "C" Bulk initialization \*/

There is no particular timming to respect between the **CONF** command, the **HSHK** command and the **BULK** command. However, to work properly, the **BULK** command must be send before the Echo canceller is started (CA-AC transition in answer mode, R1 detection in originate mode).

We can also send the **BULK** command in other mode than V.32 (or V.32 autobaud) this will not have any effect.

At that steep we must known if we want to proceed the bulk delay managment by pooling or by interrupt. As the Interrupt task is very simple we recommand the use of an interrupt; however justpooling the **SYMSTA DUAL RAM** Location will give the same results.

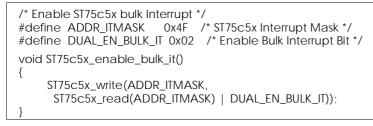

If we use interrupt we must enable the interrupt bit inside the **ITMASK** register, this will allow the ST75C502 to generate a signal on its **SINTR** Pin.

Code : 5 /\* "C" Enable Bulk Interrupt \*/

## 3 - MAIN TASK

Each 8 symbols (3.3ms) it is mandatory to serve the Bulk delay mechanism, otherwise an error occurs that will be signaled into the **SYSERR** bit 2 (**ERR\_SYM**).

The following routine is just the part of the interrupt mandatory to serve the Bulk Delay. Its suppose that the Interrupt **(ITSRCR)** source have been correctely decoded and that the other interrupts (Error, Command, Status, Data\_Tx, Data\_Rx) are well served.

| /* Global Declaration                                                                    | */                                                                                                                                        |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| #define ADDR_SYMSTA<br>#define ADDR_SYMADT<br>#define ADDR_SYMADR<br>#define ADDR_SYMBUF | 0x0F /* Symbol Buffer Status */<br>0x10 /* Symbol Tx Buffer Pointer */<br>0x12 /* Symbol Rx Buffer Pointer */<br>0x14 /* Symbol Buffer */ |

| #define ADDR_ITSRCR<br>#define DUAL_CLR_IT_BULK                                          | 0x50 /* Interrupt Source Byte */<br>0x41 /* Clear IT1 */                                                                                  |

| /* !!!! Only Part of the Interrup                                                        | ot !!!! */                                                                                                                                |

|                                                                                          | on */<br>/* Local address */<br>/* Local Pointer */<br>/* Local Loop Counter */                                                           |

| /* Read Interrupt S<br>if (ST75c5x_read(A                                                | ource */<br>DDR_ITSRCR)&DUAL_IT_BULK)) {                                                                                                  |

| /**** The BULK Se                                                                        | ervice is Required *****/                                                                                                                 |

| addr+=(ST75c5x                                                                           | dress */<br>ST75c5x_read(ADDR_SYMADR);<br>_read(ADDR_SYMADR+1)<8));<br>Idr); /* Convert into a Pointer                                    |

|                                                                                          | JAL RAM to bulk_delay_line */<br>T75c5x_write (ADDR_SYMBUF+i, *p++);                                                                      |

|                                                                                          | . Interrupt Pending Bit */<br>DUAL_CLR_IT_BULK, 0);                                                                                       |

| /* !!!! Continu processing with                                                          | n the other interrupts !!!! */                                                                                                            |

Code 6 : /\* "C" Interrupt Bulk Managment \*/

#### 4 - APPENDIX

| /* Global Definition of DUAL RAM Address */<br>#define ADDR_COMSYS 0x00 /* Command Word */<br>#define ADDR_COMPAR 0x01 /* Parameters */<br>#define ADDR_SYSERR 0x08 /* Error Status */                                                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| /* OPTIONAL: ERROR Return Codes */<br>#define DUAL_ERR_NREADY 0x01 /* ST75c5X not Ready */<br>#define DUAL_ERR_IOCD 0x02 /* Incorrect Opcode */<br>#define DUAL_ERR_IPRM 0x04 /* Incorrect Parameter */<br>#define CCI_ERR_MASK 0x18 /* Mask for IOCD or IPRM */<br>#define CCI_ERR_MASKIO 0x08 /* Mask for IOCD */ |  |

| /* Send a CCI Command to the ST75c5x */                                                                                                                                                                                                                                                                             |  |

| unsigned char ST75c5x_send_cci_command( unsigned char opcode, unsigned char param[4])<br>{                                                                                                                                                                                                                          |  |

| unsigned char i; /* local */                                                                                                                                                                                                                                                                                        |  |

| /* OPTIONAL: Test if the ST75c5x is ready to Execute a command */<br>if (ST75c5x_read(ADDR_COMSYS)!=0x00) return(DUAL_ERR_NREADY);                                                                                                                                                                                  |  |

| /* Write Parameters */<br>for (i=0;i<=3;i++) ST75c5x_write(ADDR_COMPAR+i, param[i]);                                                                                                                                                                                                                                |  |

| /* Last Write opcode to start transfer  */<br>ST75c5x_write(ADDR_COMSYS, opcode);                                                                                                                                                                                                                                   |  |

| /* Wait until COMSYS Empty */<br>while (ST75c5x_read(ADDR_COMSYS)!=0x00) /* wait */;                                                                                                                                                                                                                                |  |

| /* OPTIONAL: Read the Error Status to check if the command was successfull */<br>i = (ST75c5x_read(ADDR_SYSERR)&CCI_ERR_MASK);                                                                                                                                                                                      |  |

| /* OPTIONAL: test if CCI Error */<br>if (i!=0) {<br>if (i&CCI_ERR_MASKIO) return(DUAL_ERR_IOCD);<br>else return(DUAL_ERR_IPRM);<br>}                                                                                                                                                                                |  |

| return (0);                                                                                                                                                                                                                                                                                                         |  |

| }                                                                                                                                                                                                                                                                                                                   |  |

Code : 7 /\* "C" ST75c5x\_send\_cci\_command Example of Implementation \*/

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.