# USB2.0 Device Controller SIR72003 Technical Manual

**SEIKO EPSON CORPORATION**

www.DataSheet4U.com

## NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from anther government agency.

©SEIKO EPSON CORPORATION 2002, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

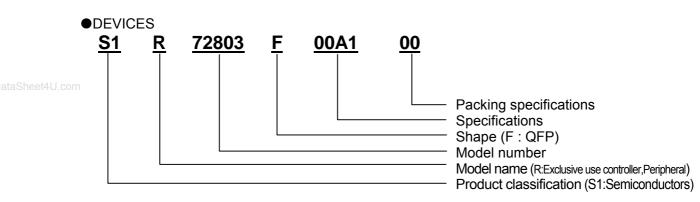

## The information of the product number change

Starting April 1, 2001 the product number has been changed as listed below. Please use the new product number when you place an order. For further information, please contact Epson sales representative.

## Configuration of product number

| 1.          | DES               | SCRIPTIC         | DN      |                                                      | 1  |

|-------------|-------------------|------------------|---------|------------------------------------------------------|----|

| 2.          | FEA               | TURES            |         |                                                      | 1  |

| 3.          | BLC               |                  | GRAM.   |                                                      | 2  |

| 4.          | PIN               | ASSIGN           | MENT.   |                                                      | 3  |

| 5.          |                   |                  |         |                                                      |    |

|             | 5.1               | CPU Int          | erface. |                                                      | 4  |

|             | 5.2               |                  |         | urpose Port Interface                                |    |

|             | 5.3               | USB Int          | erface. |                                                      | 6  |

|             | 5.4               |                  |         | and Others                                           |    |

| aSheet4U.co | 5.5               |                  |         |                                                      |    |

| _           | 5.6               |                  |         | and GND                                              |    |

| 6.          | <b>FUN</b><br>6.1 |                  |         | CRIPTION                                             |    |

|             | 6.1<br>6.2        |                  |         | Engine                                               |    |

|             | 0.2               | 6.2.1            |         | t Handler                                            |    |

|             |                   | 6.2.1            |         | action Manager                                       |    |

|             |                   | 6.2.3            |         | ints                                                 |    |

|             |                   | 6.2.4            |         | nd/Resume Controller                                 |    |

|             | 6.3               |                  | RAM     |                                                      | 8  |

|             | 6.4               |                  |         | r                                                    |    |

|             | 6.5               |                  |         |                                                      |    |

|             | 6.6               |                  |         | dule                                                 |    |

| 7.          | RFC               | ISTER            | -       |                                                      | 9  |

|             | 7.1               |                  |         |                                                      |    |

|             | 7.2               |                  |         | S                                                    |    |

|             |                   | 7.2.1            | 00h     | Main Interrupt Status (MainIntStat)                  | 15 |

|             |                   | 7.2.2            | 01h     | SIE Interrupt Status (SIEIntStat)                    | 16 |

|             |                   | 7.2.3            | 02h     | Bulk Interrupt Status (BulkIntStat)                  | 17 |

|             |                   | 7.2.4            | 03h     | EPr Interrupt Status (EPrIntStat)                    | 18 |

|             |                   | 7.2.5            | 04h     | IDE Interrupt Status (IDEIntStat)                    |    |

|             |                   | 7.2.6            | 05h     | Reserved                                             | 19 |

|             |                   | 7.2.7            | 06h     | Port Interrupt Status (PortIntStat)                  |    |

|             |                   | 7.2.8            | 07h     | Reserved                                             |    |

|             |                   | 7.2.9            | 08h     | EP0 Interrupt Status (EP0IntStat)                    |    |

|             |                   | 7.2.10           | 09h     | EPa Interrupt Status (EPaIntStat)                    |    |

|             |                   | 7.2.11           | 0Ah     | EPb Interrupt Status (EPbIntStat)                    |    |

|             |                   | 7.2.12<br>7.2.13 | 0Bh     | EPc Interrupt Status (EPcIntStat)<br>to 0Fh Reserved |    |

|             |                   | 7.2.13           | 10h     | Main Interrupt Enable (MainIntEnb)                   |    |

|             |                   | 7.2.14           | 11h     | SIE Interrupt Enable (SIEIntEnb)                     |    |

|             |                   | 7.2.15           | 12h     | Bulk Interrupt Enable (BulkIntEnb)                   |    |

|             |                   | 7.2.17           | 13h     | EPr Interrupt Enable (EPrIntEnb)                     |    |

|             |                   | 7.2.18           | 14h     | IDE Interrupt Enable (IDEIntEnb)                     |    |

|             |                   | 7.2.19           | 15h     | Reserved                                             |    |

|             |                   | 7.2.20           | 16h     | Port Interrupt Enable (PortIntEnb)                   |    |

|             |                   | 7.2.21           | 17h     | Reserved                                             | 26 |

|             |                   | 7.2.22           | 18h     | EP0 Interrupt Enable (EP0IntEnb)                     | 26 |

|             |                   | 7.2.23           | 19h     | EPa Interrupt Enable (EPaIntEnb)                     | 27 |

|             |                   | 7.2.24           | 1Ah     | EPb Interrupt Enable (EPbIntEnb)                     |    |

|             |                   | 7.2.25           | 1Bh     | EPc Interrupt Enable (EPcIntEnb)                     |    |

|             |                   | 7.2.26           |         | to 1Fh Reserved                                      |    |

|             |                   | 7.2.27           | 20h     | Chip Reset (ChipReset)                               |    |

|             |                   | 7.2.28           | 21h     | Revision Number (RevisionNum)                        | 28 |

|             |                   |                  |         |                                                      |    |

## Contents

| 7.2.29 | 22h              | Power Management Control (PMControl)                       |    |

|--------|------------------|------------------------------------------------------------|----|

| 7.2.30 | 23h              | USB Control (USBControl)                                   |    |

| 7.2.31 | 24h              | USB Status (USBStatus)                                     |    |

| 7.2.32 | 25h              | Xcvr Control (XcvrControl)                                 |    |

| 7.2.33 | 26h              | USB Test (USBTest)                                         |    |

| 7.2.34 | 27h              | Reserved                                                   |    |

| 7.2.35 | 28h              | USB Address (USBAddress)                                   |    |

| 7.2.36 | 29h              | EPr Control (EPrControl)                                   |    |

| 7.2.37 | 2Ah              |                                                            |    |

| 7.2.38 | 2Bh              | BulkOnly Config (BulkOnlyConfig)                           | 37 |

| 7.2.39 | 2Ch              | to 2Eh Reserved                                            |    |

| 7.2.40 | 2Fh              | Chip Config (ChipConfig)                                   |    |

| 7.2.41 | 30h <sup>-</sup> | to 37h EP0 Setup0 to EP0 Setup7 (EP0Setup_0 to EP0Setup_7) |    |

| 7.2.42 | 38h              | FrameNumber High (FrameNumber_H)                           |    |

| 7.2.43 | 39h              | FrameNumber Low (FrameNumber_L).                           |    |

| 7.2.44 | 3Ah              | to 3Fh Reserved                                            |    |

| 7.2.45 | 40h              | EP0 Config_0 (EP0Control_0)                                |    |

| 7.2.46 | 41h              | Reserved                                                   |    |

| 7.2.47 | 42h              | EP0 Control_0 (EP0Control_0)                               | 42 |

| 7.2.48 | 43h              | EP0 Control_1 (EP0Control_1)                               | 43 |

| 7.2.49 | 44h              | Reserved                                                   |    |

| 7.2.50 | 45h              | EP0 FIFO Remain (EP0FIFORemain)                            |    |

| 7.2.51 | 46h              | EP0 FIFOforCPU (EP0FIFOforCPU)                             |    |

| 7.2.52 | 47h              | EP0 FIFO Control (EP0FIFOControl)                          |    |

| 7.2.52 |                  | to 4Fh Reserved                                            |    |

| 7.2.53 | 4011<br>50h      | EPa Config_0 (EPaConfig_0)                                 |    |

|        |                  |                                                            |    |

| 7.2.55 | 51h              | EPa Config_1 (EPaConfig_1)                                 |    |

| 7.2.56 | 52h              | EPa Control_0 (EPaControl_0)                               |    |

| 7.2.57 | 53h              | EPa Control_1 (EPaControl_1)                               |    |

| 7.2.58 | 54h              | EPa FIFO Remain High (EPaFIFORemain_H)                     |    |

| 7.2.59 | 55h              | EPa FIFO Remain Low (EPaFIFORemain_L)                      |    |

| 7.2.60 | 56h              | EPa FIFO for CPU (EPaFIFOforCPU)                           |    |

| 7.2.61 | 57h              | EPa FIFO Control (EPaFIFOControl)                          |    |

| 7.2.62 | 58h              | EPb Config_0 (EPbConfig_0)                                 |    |

| 7.2.63 | 59h              | EPb Config_1 (EPbConfig_1)                                 |    |

| 7.2.64 | 5Ah              | EPb Control_0 (EPbControl_0)                               |    |

| 7.2.65 | 5Bh              | EPb Control_1 (EPbControl_1)                               |    |

| 7.2.66 | 5Ch              | 5 ( _ /                                                    |    |

| 7.2.67 | 5Dh              |                                                            |    |

| 7.2.68 | 5Eh              | EPb FIFO for CPU (EPbFIFOforCPU)                           | 54 |

| 7.2.69 | 5Fh              | EPb FIFO Control (EPbFIFOControl)                          | 54 |

| 7.2.70 | 60h              | EPc Config_0 (EPcConfig_0)                                 | 55 |

| 7.2.71 | 61h              | EPc Config_1 (EPcConfig_1)                                 | 56 |

| 7.2.72 | 62h              | EPc Control_0 (EPcControl_0)                               | 57 |

| 7.2.73 | 63h              | EPc Control 1 (EPcControl 1)                               | 58 |

| 7.2.74 | 64h              | EPc FIFO Remain High (EPcFIFORemain_H)                     | 58 |

| 7.2.75 | 65h              | EPc FIFO Remain Low (EPcFIFORemain L).                     |    |

| 7.2.76 | 66h              | EPc FIFO for CPU (EPcFIFOforCPU)                           |    |

| 7.2.77 | 67h              | EPc FIFO Control (EPcFIFOControl)                          |    |

| 7.2.78 | 68h              | Iso Max Packet Size High (IsoMaxSize_H)                    |    |

| 7.2.79 | 69h              | Iso Max Packet Size Low (IsoMaxSize_L)                     |    |

| 7.2.80 |                  | to 7Fh Reserved                                            |    |

| 7.2.81 | 80h              | IDE Status (IDEStatus).                                    |    |

| 7.2.82 | 81h              | IDE Config_0 (IDEConfig_0)                                 |    |

| 7.2.83 | 82h              | IDE Config_1 (IDEConfig_1)                                 |    |

| 7.2.84 | 83h              | Reserved                                                   |    |

| 7.2.85 | 84h              | IDE Register Mode (IDE_Rmod)                               |    |

| 1.2.00 | 0411             | ושב הכשוטנפו וווטעב (ושב_הווטע)                            |    |

/ww.DataSheet4U.com

|                |     |            | 7.2.86           | 85h        | DE Transfer Mode (IDE_Tmod)                                                                | 65  |

|----------------|-----|------------|------------------|------------|--------------------------------------------------------------------------------------------|-----|

|                |     |            | 7.2.87           |            | DE Ultra-DMA Transfer Mode (IDE_Umod)                                                      |     |

|                |     |            | 7.2.88           |            | Reserved                                                                                   |     |

|                |     |            | 7.2.89<br>7.2.90 |            | DE Control_0 (IDEControl_0)                                                                |     |

|                |     |            | 7.2.90           |            | Reserved<br>IDE Transfer Byte Count High (IDE Count H)                                     |     |

|                |     |            | 7.2.91           |            | IDE Transfer Byte Count Middle (IDE_Count_M)                                               |     |

|                |     |            | 7.2.93           | 8Ch        | IDE Transfer Byte Count Low (IDE_Count_L)                                                  | 67  |

|                |     |            | 7.2.94           | 8Dh        | IDE CRC Control (IDE_CRCControl)                                                           | 68  |

|                |     |            | 7.2.95           |            | IDE CRC High (IDE_CRC_H)                                                                   |     |

|                |     |            | 7.2.96           |            | IDE CRC Low (IDE_CRC_L)                                                                    |     |

|                |     |            | 7.2.97           |            | DE_CS00 (IDE_CS00)                                                                         |     |

| /w.DataSheet4L |     |            | 7.2.98<br>7.2.99 |            | 9Fh IDE_CS01 to IDE_CS17 (IDE_CS01 to IDE_CS17)<br>BEh CBW_00 to CSW_30 (CBW_00 to CBW_30) |     |

|                |     |            | 7.2.99           |            | Reserved                                                                                   |     |

|                |     |            | 7.2.100          | C0h to     | CCh CSW0_00 to CSW0_12 (CSW0_00 to CSW0_12)                                                | 71  |

|                |     |            |                  | CDh to     | o CFh Reserved                                                                             |     |

|                |     |            |                  |            | DCh CSW1_00 to CSW1_12 (CSW1_00 to CSW1_12)                                                |     |

|                |     |            | 7.2.104          | DDh to     | DFh Reserved                                                                               | 72  |

|                |     |            |                  |            | Port Direction (PortDir)                                                                   |     |

|                |     |            | 7.2.106          | E1h        | Port Data (PortData)                                                                       | 73  |

|                | 8.  | TYP        |                  |            | IONS                                                                                       |     |

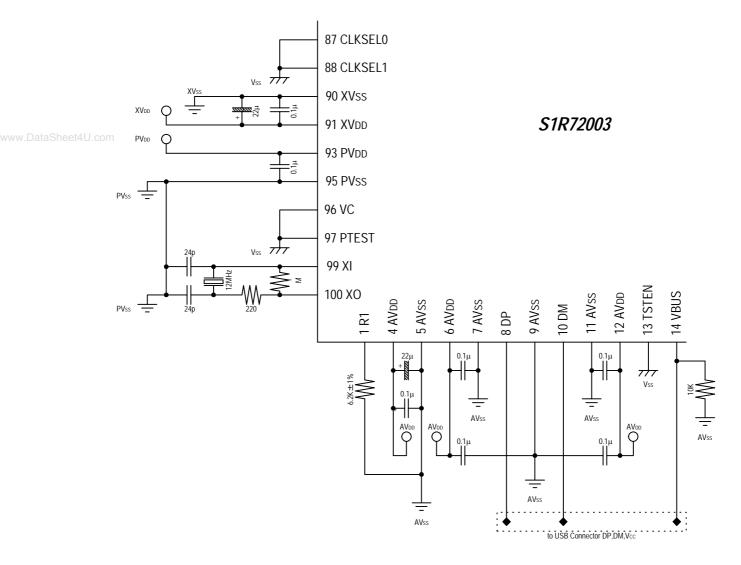

|                |     | 8.1        |                  |            | necting USB Interface and Other Pins                                                       |     |

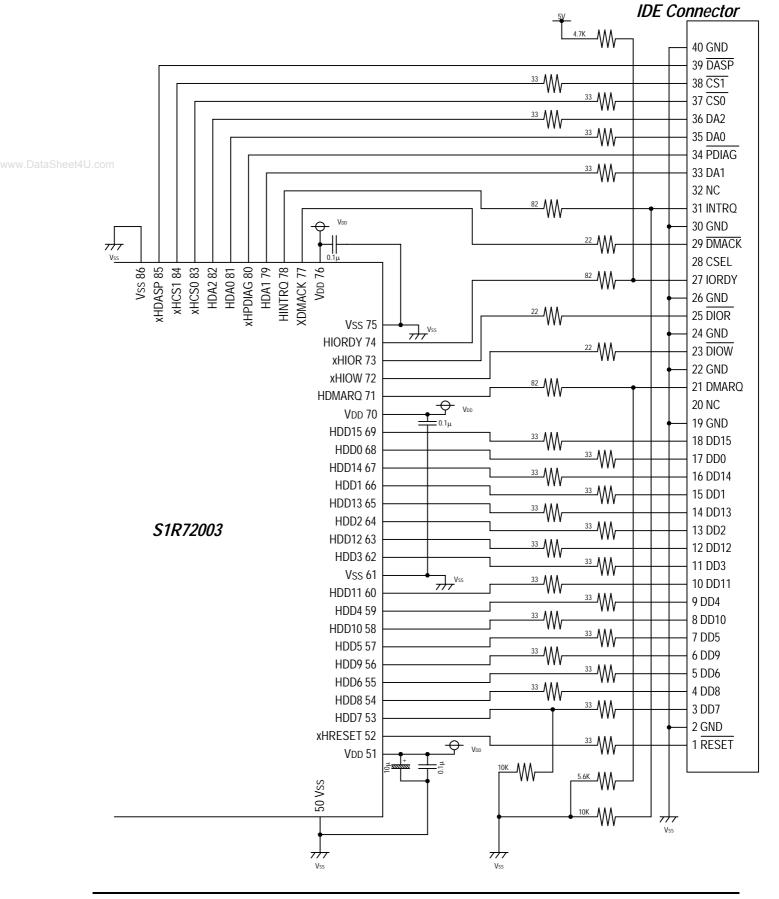

|                |     | 8.2        |                  |            | necting IDE Interface and Other Pins                                                       |     |

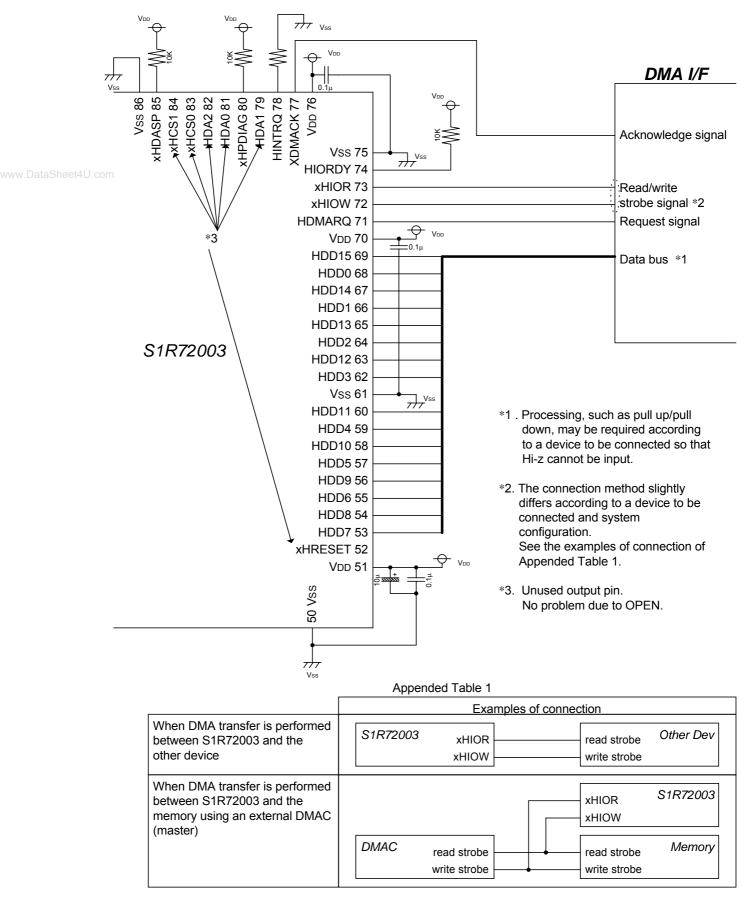

|                |     | 8.3        |                  |            | nnection of IDE I/F Pins (When General-Purpose DMA is Used)                                |     |

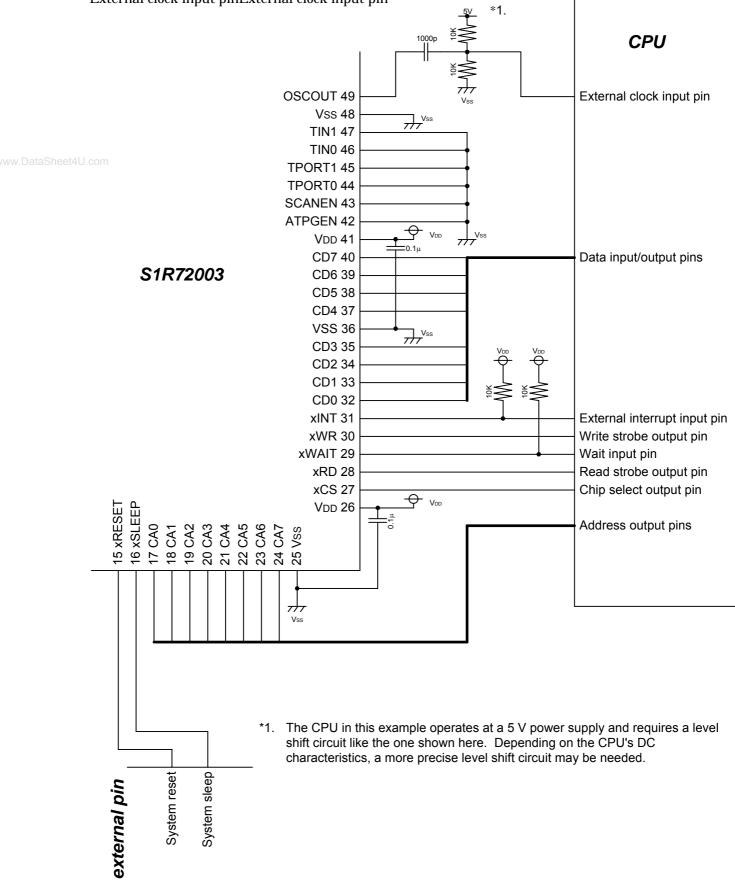

|                |     | 8.4        |                  |            | necting CPU Interface And Other Pins                                                       |     |

|                | 9.  |            |                  |            | ACTERISTICS                                                                                |     |

|                |     | 9.1        |                  |            | um Ratings                                                                                 |     |

|                |     | 9.2        |                  |            | Operating Conditions                                                                       |     |

|                |     | 9.3<br>9.4 |                  |            |                                                                                            |     |

|                |     | 3.4        |                  |            | Access Timing                                                                              |     |

|                |     |            |                  |            | Timing                                                                                     |     |

|                |     |            |                  |            | I-purpose Port I/F Timing                                                                  |     |

|                |     |            |                  |            | Timing                                                                                     |     |

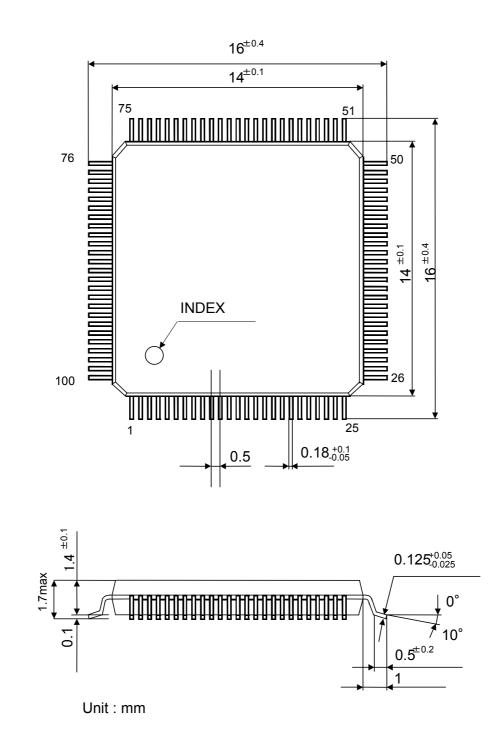

|                | 10. | EXT        | ERNAL F          | ACKAG      | SE                                                                                         | 95  |

|                |     |            |                  |            | ERATION OTHER THAN TRANSFER                                                                |     |

|                | AF  | A.1        |                  |            | ion                                                                                        |     |

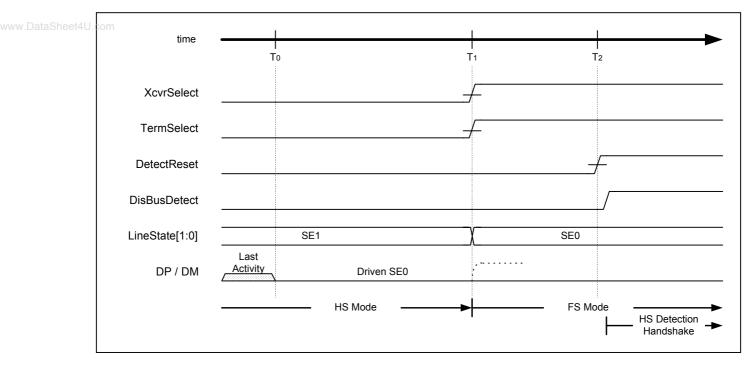

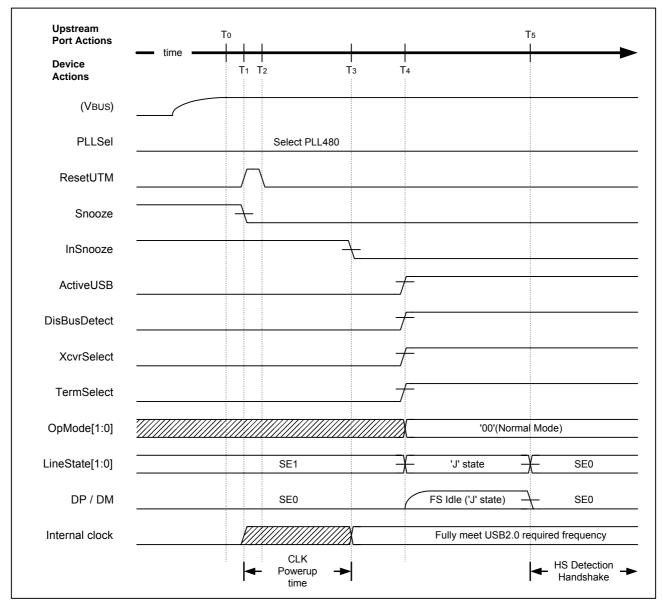

|                |     | A. I       | •                |            | Detection (HS Mode)                                                                        |     |

|                |     |            |                  |            |                                                                                            |     |

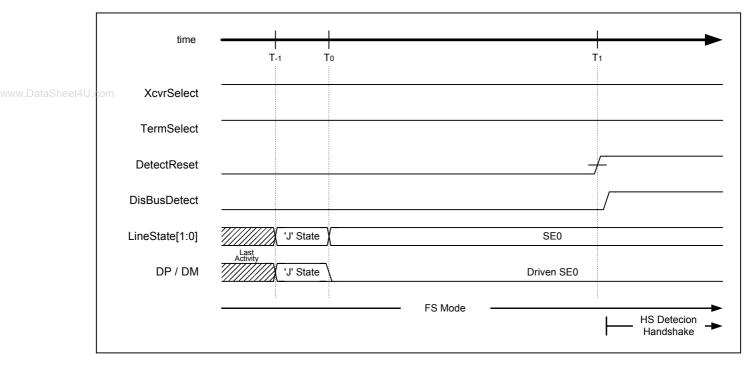

|                |     | A 0        |                  | •          | Detection (FS Mode)                                                                        |     |

|                |     | A.Z        |                  |            |                                                                                            |     |

|                |     |            |                  |            | etection (HS Mode)                                                                         |     |

|                |     |            |                  |            | etection (FS Mode)                                                                         |     |

|                |     | A.3        |                  |            | andshake                                                                                   |     |

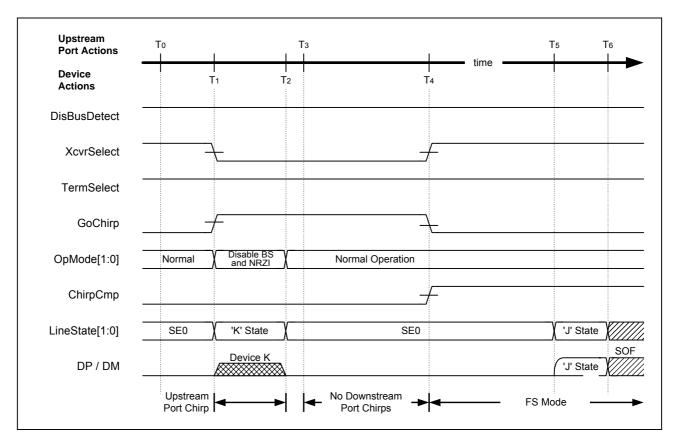

|                |     |            |                  |            | his IC is Connected to FS Downstream Port                                                  |     |

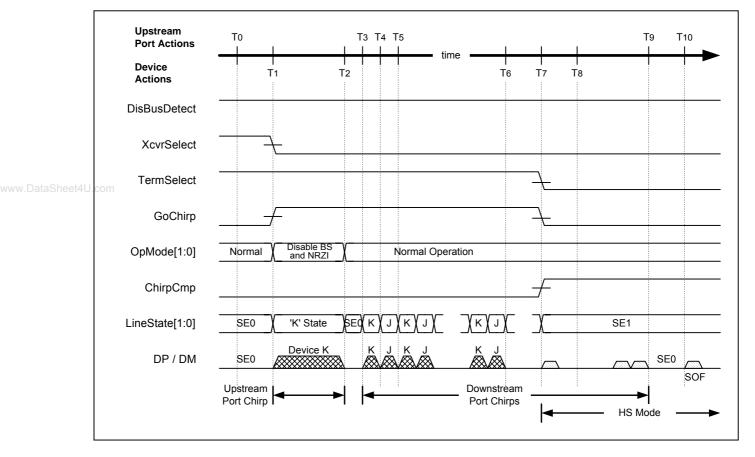

|                |     |            |                  |            | nis IC is Connected to HS Downstream Port                                                  |     |

|                |     |            |                  |            | nis IC is Reset in Snooze                                                                  |     |

|                |     | A.4        |                  |            | e                                                                                          |     |

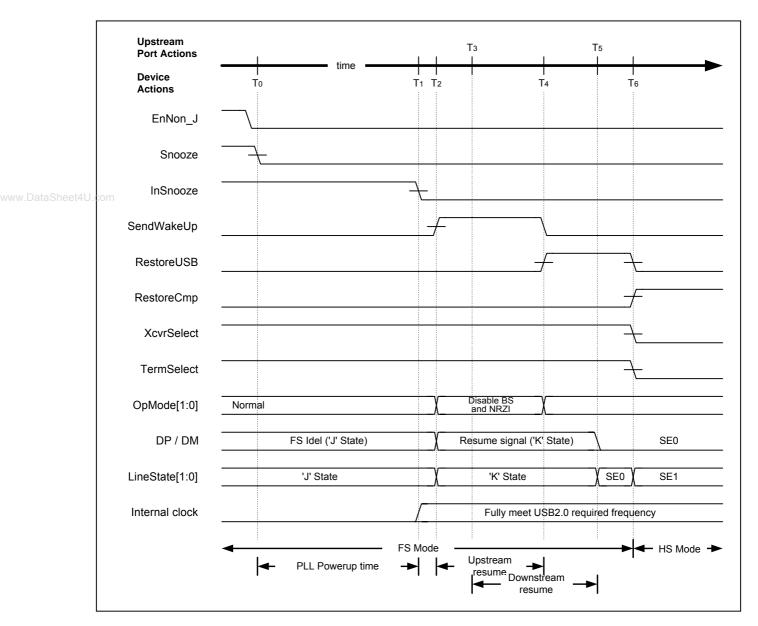

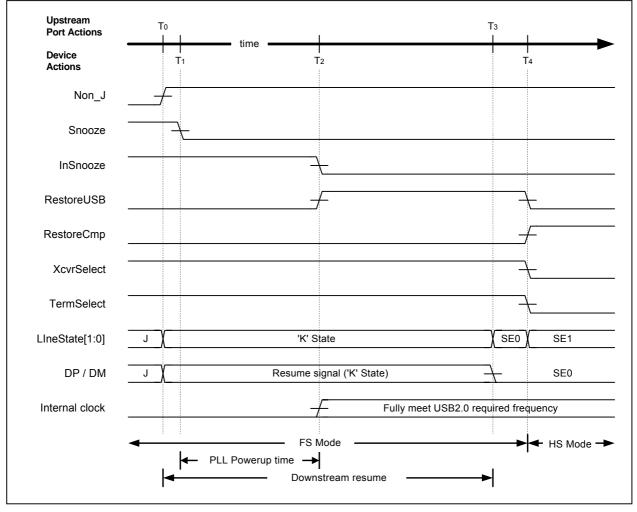

|                |     | A.5        |                  |            | sume                                                                                       |     |

|                |     | A.6        |                  |            |                                                                                            |     |

|                |     | A.7        |                  |            |                                                                                            |     |

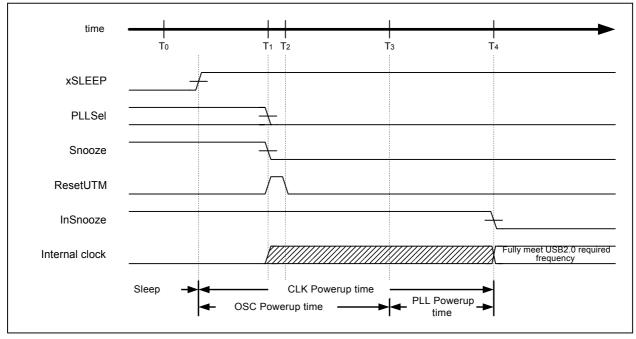

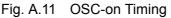

|                |     |            | A.7.1 S          | Start of ( | Oscillator Circuit                                                                         | 115 |

|                |     |            | A.7.2 S          | Sleep (S   | top of Oscillator Circuit)                                                                 | 117 |

|                |     |            |                  |            |                                                                                            |     |

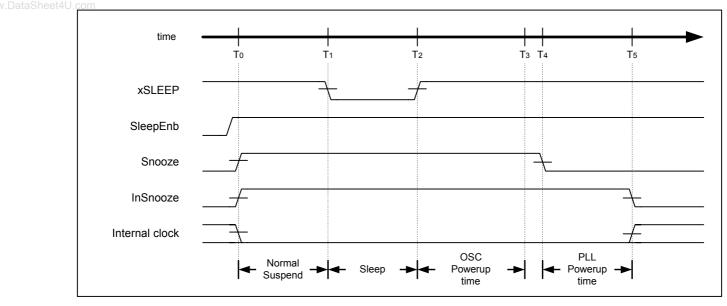

| A.7.        | .3 | PLL Switching                 | 118 |

|-------------|----|-------------------------------|-----|

| APPENDIX-B. | R  | ECOMMENDED OSCILLATOR CIRCUIT | 119 |

/ww.DataSheet4U.com

## 1. DESCRIPTION

The S1R72003F00B100 is a general-purpose USB device controller LSI that supports the USB 2.0 high-speed mode. With the field-proven, UTMI Rev 1.0-compliant transceiver circuit, it assures connectivity of USB devices.

## 2. FEATURES

- Supports HS (480Mbps) and FS (12Mbps) transfers.

- Supports Control, Bulk, Interrupt, and Isochronous transfers.

- Supports three general-purpose Endpoints and Endpoint 0.

- Contains a 2.5-KB programmable FIFO for Endpoint use.

- Incorporates IDE and general-purpose DMA ports.

ww.DataSheet4U.com IDE:

Supports PIO modes 1/2/3/4. Supports Multiword DMA modes 0/1/2. Supports Ultra-DMA modes 1/2/3/4.

General-purpose DMA:

The bus width can be set to 8 or 16 bits. Both master and slave are supported.

- Incorporates an 8-bit, general-purpose CPU interface.

- Accommodates 12, 16, 20, and 24-MHz crystal resonators for clock input.

- Multiple Power management mode Snooze: PLL halt mode triggered by detection of the suspend state of USB. Sleep: Oscillation circuit halt mode triggered by xSLEEP pin assertion.

- Operates on a single 3.3 V power supply

- Uses 5 V tolerant cells for VBUS, CPU interface, and DMA port input pins.

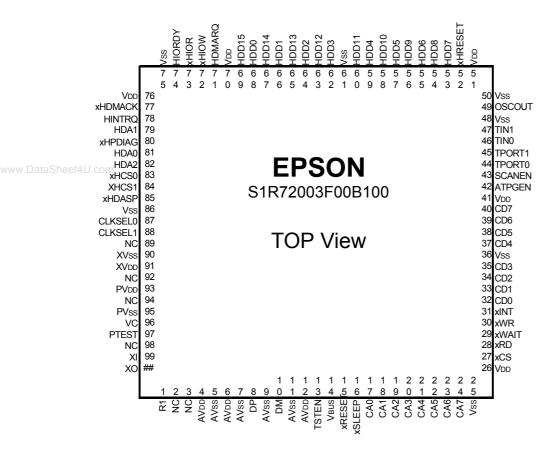

- Supplied as a 100-pin QFP package

\* No radiation resistant design measure has been incorporated.

1

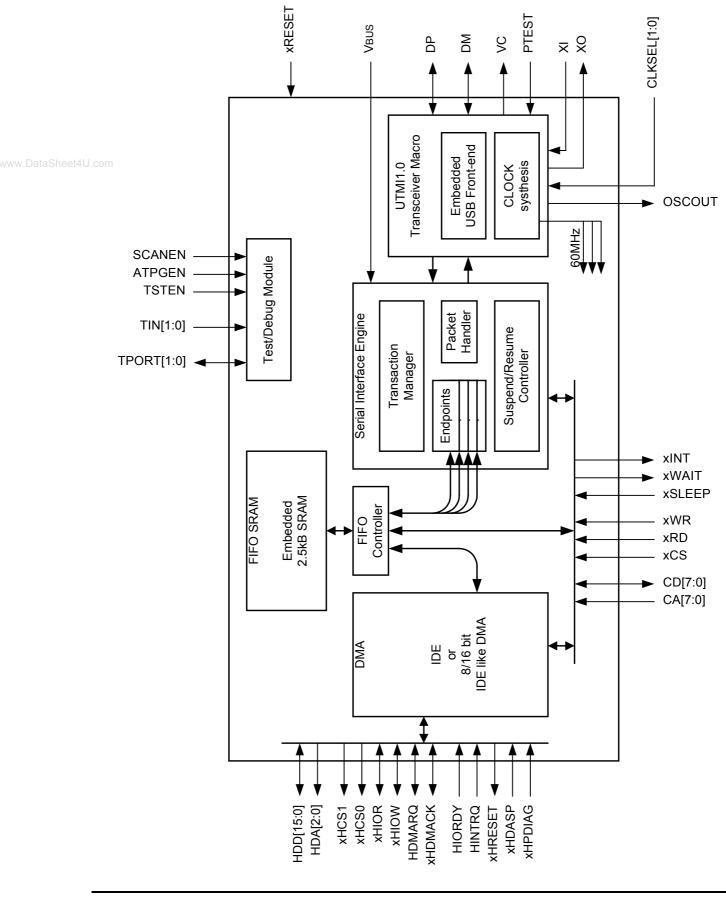

## 3. BLOCK DIAGRAM

2

## 4. PIN ASSIGNMENT

## 5. PIN DESCRIPTION

## 5.1 CPU Interface

|                | Symbol  | Pin Name          | Pin No. | Туре        | Description                                                  |

|----------------|---------|-------------------|---------|-------------|--------------------------------------------------------------|

|                | CD7     | CPU Data          | 40      | I/O         | CPU data bus                                                 |

|                | CD6     |                   | 39      | (3 state    | During reads, register data is output from this bus.         |

|                | CD5     |                   | 38      | pull up)    | During writes, the CPU delivers the register data to         |

|                | CD4     |                   | 37      |             | be set through this bus.                                     |

|                | CD3     |                   | 35      |             | Uses a 5V tolerant cell.                                     |

|                | CD2     |                   | 34      |             |                                                              |

|                | CD1     |                   | 33      |             |                                                              |

| w.DataSheet4U. | com CD0 |                   | 32      |             |                                                              |

|                | CA7     | CPU Address       | 24      | l (pull up) | CPU address bus                                              |

|                | CA6     |                   | 23      |             | This bus specifies the register address.                     |

|                | CA5     |                   | 22      |             | Uses a 5V tolerant cell.                                     |

|                | CA4     |                   | 21      |             |                                                              |

|                | CA3     |                   | 20      |             |                                                              |

|                | CA2     |                   | 19      |             |                                                              |

|                | CA1     |                   | 18      |             |                                                              |

|                | CA0     |                   | 17      |             |                                                              |

|                | xRD     | Read Strobe       | 28      | l (pull up) | CPU read strobe. Uses a 5V tolerant cell.                    |

|                | xWR     | Write Strobe      | 30      | l (pull up) | CPU write strobe. Uses a 5V tolerant cell.                   |

|                | xCS     | Chip Select       | 27      | l (pull up) | Register select signal Uses a 5V tolerant cell.              |

|                | xSLEEP  | Sleep mode        | 16      | l (pull up) | Sleep mode set signal. Uses a 5V tolerant cell.              |

|                |         |                   |         |             | When this pins is asserted during the snooze                 |

|                |         |                   |         |             | mode, the S1R72003F00B100 enters the sleep                   |

|                |         |                   |         |             | mode.                                                        |

|                |         |                   |         |             | The oscillation circuit halts during the sleep mode.         |

|                |         |                   |         |             | You should be careful when the CPU uses                      |

|                |         |                   |         |             | OSCOUT. The S1R72003F00B100 is roused                        |

|                |         |                   |         |             | from sleep mode in the following cases:                      |

|                |         |                   |         |             | When resume is asserted on the USB interface                 |

|                |         |                   |         |             | <ul> <li>When the TPORT1 or TPORT0 signal changes</li> </ul> |

|                |         |                   |         |             | states                                                       |

|                | xINT    | Interrupt signal  | 31      | 0           | Interrupt signal to the CPU. The initial value is            |

|                |         |                   |         |             | Hi-z/0. This can be set to 1 or 0.                           |

|                | xWAIT   | Wait signal       | 29      | 0           | Wait signal to the CPU. The initial value is Hi-z/0.         |

|                |         |                   |         |             | This can be set to 1 or 0.                                   |

|                | OSCOUT  | Oscillator output | 49      | 0           | CPU clock output. The frequency generated by                 |

|                |         |                   |         |             | the resonator connected to XI and XO pins is                 |

|                |         |                   |         |             | output from this pin.                                        |

|                 | Symbol   | Pin Name                | Pin No. | Туре          | Description                                             |

|-----------------|----------|-------------------------|---------|---------------|---------------------------------------------------------|

|                 | HDD15    | IDE Data/               | 69      | I/O           | IDE data bus. Uses a 5V tolerant cell.                  |

|                 | HDD14    | Universal Data Bus      | 67      | (3 state)     | This bus also serves as a general-purpose port          |

|                 | HDD13    |                         | 65      |               | data bus, depending on the settings of the internal     |

|                 | HDD12    |                         | 63      |               | registers. If set to serve as a general-purpose         |

|                 | HDD11    |                         | 60      |               | port, the bus width can be set to 8 or 16 bits.         |

|                 | HDD10    |                         | 58      |               |                                                         |

|                 | HDD9     |                         | 56      |               |                                                         |

|                 | HDD8     |                         | 54      |               |                                                         |

|                 | HDD7     |                         | 53      |               |                                                         |

|                 | HDD6     |                         | 55      |               |                                                         |

| ww.DataSheet4U. | HDD5     |                         | 57      |               |                                                         |

|                 |          |                         |         |               |                                                         |

|                 | HDD4     |                         | 59      |               |                                                         |

|                 | HDD3     |                         | 62      |               |                                                         |

|                 | HDD2     |                         | 64      |               |                                                         |

|                 | HDD1     |                         | 66      |               |                                                         |

|                 | HDD0     |                         | 68      |               |                                                         |

|                 | HDA2     | IDE                     | 82      | 0             | IDE register address signal. Uses a 5V tolerant         |

|                 | HDA1     | Register Address        | 79      |               | cell.                                                   |

|                 | HDA0     |                         | 81      |               | If the general-purpose port function is selected, this  |

|                 |          |                         |         |               | signal is not used.                                     |

|                 | xHCS1    | Control register select | 84      | 0             | Chip select for control register access                 |

|                 |          |                         | •       | C C           | If the general-purpose port function is selected, this  |

|                 |          |                         |         |               | signal is not used.                                     |

| -               | xHCS0    | Command register select | 83      | 0             | Chip select for command block register access           |

|                 | XHCSU    | Command register select | 03      | 0             | -                                                       |

|                 |          |                         |         |               | If the general-purpose port function is selected, this  |

| -               |          |                         |         |               | signal is not used.                                     |

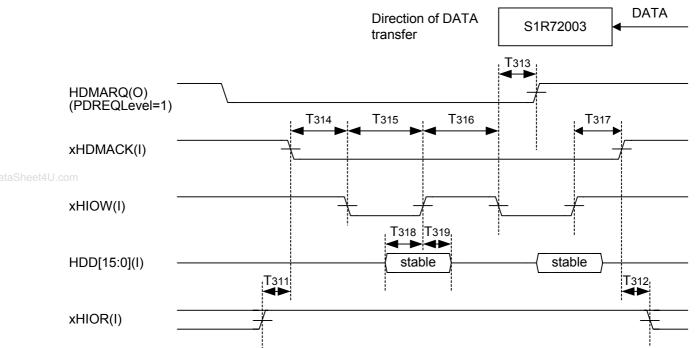

| _               | xHIOR    | IDE Read strobe         | 73      | O (IDE        | IDE read strobe. Uses a 5V tolerant cell.               |

|                 | xHIOW    | IDE Write strobe        | 72      | mode/port     | IDE write strobe. Uses a 5V tolerant cell.              |

|                 |          |                         |         | master mode)  | During IDE, this signal and xHIOR both serve as         |

|                 |          |                         |         | I (port slave | outputs. If the general-purpose port function is        |

|                 |          |                         |         | mode)         | selected, this signal serves as output during master    |

|                 |          |                         |         |               | mode and serves as input during slave mode,             |

|                 |          |                         |         |               | depending on the settings of the internal registers.    |

|                 |          |                         |         |               | For detailed information on the signal timing, refer to |

|                 |          |                         |         |               | the section, "AC Timing."                               |

|                 | HINTRQ   | IDE interrupt request   | 78      | 1             | IDE interrupt request Uses a 5V tolerant cell.          |

|                 | THIN TOO |                         | 10      |               | If the general-purpose port function is selected, this  |

|                 |          |                         |         |               | signal is not used.                                     |

|                 |          | 1/O ready               | 74      |               |                                                         |

|                 | HIORDY   | I/O ready               | 74      | I             | IDE register ready signal Uses a 5V tolerant cell.      |

|                 |          |                         |         |               | If the general-purpose port function is selected, this  |

| Ļ               |          |                         |         |               | signal is not used.                                     |

|                 | HDMARQ   | DMA request             | 71      | I (IDE        | DMA transfer request Uses a 5V tolerant cell.           |

|                 |          |                         |         | mode/port     | This signal serves as input during master mode          |

|                 |          |                         |         | master mode)  | and serves as output during slave mode depending        |

|                 |          |                         |         | O (port slave | on the settings of the internal registers. For          |

|                 |          |                         |         |               |                                                         |

|                 |          |                         |         | mode)         | detailed information on the signal timing, refer to     |

## 5.2 IDE/General-purpose Port Interface

| I   | Symbol  | Pin Name           | Pin No. | Туре          | Description                                         |

|-----|---------|--------------------|---------|---------------|-----------------------------------------------------|

| ſ   | XHDMACK | DMA acknowledge    | 77      | O (IDE        | DMA transfer acknowledge Uses a 5V tolerant         |

|     |         |                    |         | mode/port     | cell.                                               |

|     |         |                    |         | master mode)  | This signal serves as output during master mode     |

|     |         |                    |         | I (port slave | and serves as input during slave mode depending     |

|     |         |                    |         | mode)         | on the settings of the internal registers. For      |

|     |         |                    |         |               | detailed information on the signal timing, refer to |

|     |         |                    |         |               | the section, "AC Timing."                           |

|     | xHPDIAG | Passed diagnostics | 80      | I             | Diagnostic sequence-finished signal                 |

|     |         |                    |         |               | Uses a 5V tolerant cell.                            |

| 111 | xHDASP  | Drive active/      | 85      | I             | Drive active/slave drive present Uses a 5V          |

|     | Som     | Slave present      |         |               | tolerant cell.                                      |

|     | XHRESET | IDE reset          | 52      | 0             | IDE bus reset                                       |

## 5.3 USB Interface

| Symbol | Pin Name                   | Pin No. | Туре | Description                                            |

|--------|----------------------------|---------|------|--------------------------------------------------------|

| DP     | USB positive signal        | 8       | I/O  | USB data line, Data+                                   |

| DM     | USB negative signal        | 10      | I/O  | USB data line, Data-                                   |

| VBUS   | USB bus detect signal      | 14      | -    | USB bus detect signal. Uses a 5V tolerant cell.        |

| R1     | Internal operation set pin | 1       | I/O  | Internal operation set pin                             |

|        |                            |         |      | Connect a 6.2 k $\Omega$ ±1% resistor between this pin |

|        |                            |         |      | and AVSS (pin 5). This resistor must be                |

|        |                            |         |      | connected as close as possible to pins 1 and 5.        |

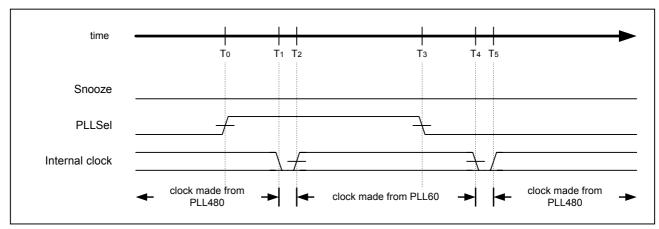

| XI     | Resonator input            | 99      | l    | XI is an input for the internal oscillator circuit or  |

| XO     | Resonator output           | 100     | 0    | input from an external oscillator. XO is an output     |

|        |                            |         |      | for the internal oscillator circuit. Leave these pins  |

|        |                            |         |      | open when using a crystal oscillator.                  |

| VC     | PLLVCO                     | 96      | I    | Internal test pin. During normal use, connect this     |

|        |                            |         |      | pin to GND.                                            |

| PTEST  | PLL test                   | 97      | I    | Internal test pin. During normal use, connect this     |

|        |                            |         |      | pin to GND.                                            |

## 5.4 System Blocks and Others

| Symbol  | Pin Name         | Pin No.   | Туре | Description   |               |                     |  |  |  |  |

|---------|------------------|-----------|------|---------------|---------------|---------------------|--|--|--|--|

| XRESET  | Chip reset       | 15        | -    | Chip reset.   | Uses a 5V to  | lerant cell.        |  |  |  |  |

| CLKSEL1 | Oscillator clock | 88        | Ι    | Oscillation f | requency sele | ct                  |  |  |  |  |

| CLKSEL0 | select           | 87        | Ι    | CLKSEL1       | CLKSEL0       | Frequency of the    |  |  |  |  |

|         |                  |           |      |               |               | connected resonator |  |  |  |  |

|         |                  |           |      | LOW           | LOW           | 12 MHz              |  |  |  |  |

|         |                  |           |      | LOW           | HIGH          | 16 MHz              |  |  |  |  |

|         |                  |           |      | HIGH          | LOW           | 20 MHz              |  |  |  |  |

|         |                  |           |      | HIGH          | HIGH          | 24 MHz              |  |  |  |  |

| NC      | No Connection    | 2, 3, 89, |      | These pins a  | are not conne | cted internally.    |  |  |  |  |

|         |                  | 92, 94,   |      |               |               |                     |  |  |  |  |

|         |                  | 98        |      |               |               |                     |  |  |  |  |

## 5.5 Test Signals

| Symbol | Pin Name           | Pin No. | Туре        | Description                                         |

|--------|--------------------|---------|-------------|-----------------------------------------------------|

| TIN1   | Test mode          | 47      | I           | Mode set input pin                                  |

| TIN0   |                    | 46      | (pull down) | 00: Normal                                          |

|        |                    |         |             | Others: Internal test mode                          |

| TPORT1 | Test Port I/O      | 45      | I/O         | General-purpose input/output port for debugging     |

| TPORT0 |                    | 44      |             |                                                     |

| TSTEN  | Internal test mode | 13      | I           | Internal pulldown. During normal use, connect this  |

|        |                    |         | (pull down) | pin low.                                            |

| ATPGEN | Internal test mode | 42      | I           | Test input pin. During normal use, connect this pin |

|        |                    |         | (pull down) | low.                                                |

| SCANEN | Internal test mode | 43      | I           | Test input pin. During normal use, connect this pin |

|        |                    |         | (pull down) | low.                                                |

## 5.6 Power Supply and GND

| Symbol | Pin Name                  | Pin No.  | Туре | Description                                      |

|--------|---------------------------|----------|------|--------------------------------------------------|

| Vdd    | Power supply for Logic    | 26, 41,  | Р    | 3.3V power supply pin for the logic block        |

|        | part                      | 51, 70,  |      |                                                  |

|        |                           | 76       |      |                                                  |

| Vss    | Ground for Logic part     | 25, 36,  | Р    | Ground pin for the logic block                   |

|        |                           | 48, 50,  |      |                                                  |

|        |                           | 61, 75,  |      |                                                  |

|        |                           | 86       |      |                                                  |

| XVdd   | Power Supply for Logic    | 91       | Р    | 3.3V power supply pin for the transceiver macro  |

|        | Part in UTMI              |          |      | unit logic block                                 |

| XVss   | Ground for Logic part in  | 90       | Р    | Ground pin for the transceiver macro unit logic  |

|        | UTMI                      |          |      | block                                            |

| PVdd   | Power Supply for PLL      | 93       | Р    | 3.3V power supply pin for the transceiver macro  |

|        | Part in UTMI              |          |      | unit PLL                                         |

| PVss   | Ground for PLL Part in    | 95       | Р    | Ground pin for the transceiver macro unit PLL    |

|        | UTMI                      |          |      |                                                  |

| AVDD   | Power Supply for Analog   | 4, 6, 12 | Р    | 3.3V power supply pin for the transceiver macro  |

|        | Part in UTMI              |          |      | unit analog block                                |

| AVss   | Ground for Analog Part in | 5, 7, 9, | Р    | Ground pin for the transceiver macro unit analog |

|        | UTMI                      | 11       |      | block.                                           |

## 6. FUNCTIONAL DESCRIPTION

The function of each block of the S1R72003F00B100 is described below.

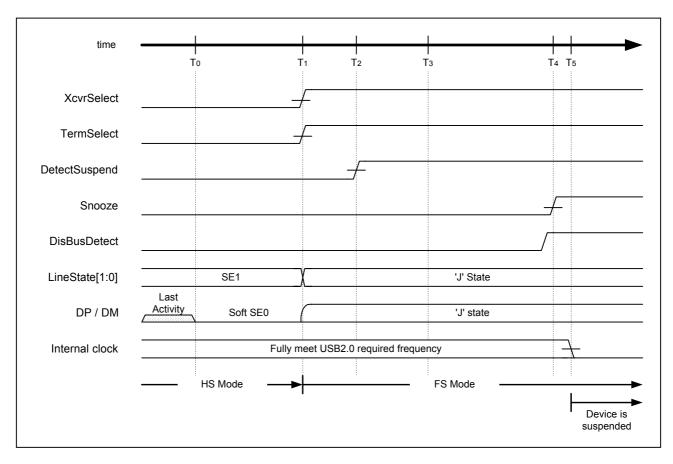

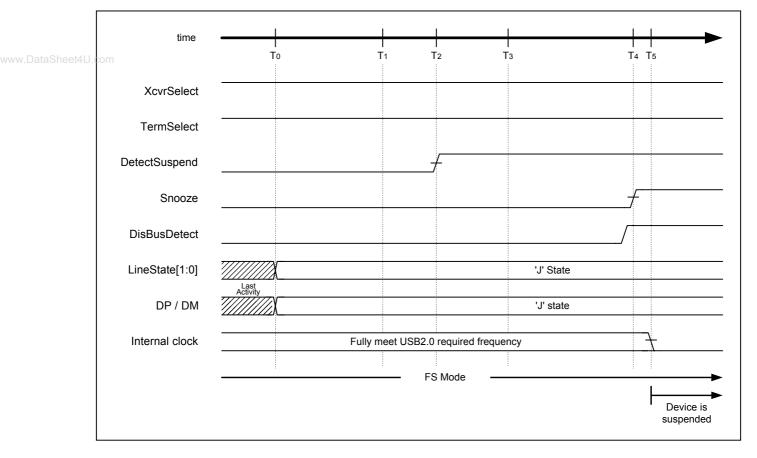

## 6.1 UTMI1.0 Transceiver Macro

This is a UTMI1.0-compliant USB 2.0 transceiver macro. It supports HS mode (480 Mbps) and FS mode (12 Mbps).

The transceiver macro contains an analog HS/FS driver, receiver, and terminator to provide a USB interface. It also contains an oscillator circuit which generates a 480 MHz clock required for HS transfer and a 60 MHz clock required for the operation of the internal logic. This oscillator circuit accepts as its input clock a 12, 16, 20, or 24 MHz crystal resonator. The transceiver macro uses an 8-bit parallel interface for interface with the SIE.

The transceiver macro processes the communication bit stream by NRZI encoding/decoding. It also has an 4U internal data handler that adds SYNC, EOP, and bit stuff to the transmit data. When receiving data, it detects/removes SYNC and EOP and removes the bit stuff.

The transceiver macro incorporates the Elasticity Buffer to counter data underruns/overruns caused by frequency deviations on the data transmit/receive sides in the HS mode, and a squelch circuit to discriminate between serial data and noise.

For more information, refer to the UTMI 1.0 specifications.

## 6.2 Serial Interface Engine

## 6.2.1 Packet Handler

This unit processes the packet (by dissolving it into the various fields: PID, ADDR, DATA, CRC, Endpoint Number, and Frame Number). It also checks and generates CRC.

## 6.2.2 Transaction Manager

This unit manages transactions such as USB address verification and handshake verification/creation.

## 6.2.3 Endpoints

The serial interface incorporates Endpoint 0 (IN/OUT) and three general-purpose Endpoints (EPa, EPb, and EPc). The IN/OUT direction, maximum packet size, and transfer type (Bulk, Interrupt, or Isochronous) of the general-purpose Endpoints can be individually set using an internal register. (isochronous transfer is supported only by EPc.)

## 6.2.4 Suspend/Resume Controller

This unit controls Suspend and Resume.

## 6.3 FIFO SRAM

This buffer is used to accommodate the Endpoints (2.5 KB).

It is user programmable, but total 128 bytes comprised of 64 bytes for endpoint and 64 bytes for CBW/CSW are reserved area.

The FIFO SRAM reserves a space for MaxPacketSize (twice the size with the DoubleBuf setting) according to each endpoint setting. The amount of space the FIFO SRAM reserves must not exceed 2.5 kB.

## 6.4 FIFO Controller

This unit manages the FIFO SRAM address (user programmable), generates timing signals, and arbitrates bus contention.

## 6.5 DMA

The DMA in the S1R72003F00B100 supports general-purpose DMA ports and IDE interface.

The general-purpose DMA ports accommodate both master and slave operations. The bus width can be switched to 8 or 16 bits. The DMA can function as the IDE master, and supports PIO modes 0/1/2/3/4, Multiword DMA modes 0/1/2, and Ultra-DMA modes 0/1/2/3/4.

## 6.6 Test/Debug Module

The operation mode (test mode) of this module is switched by an input signal.

## 7. REGISTER

## 7.1 Register Map

Indicates the register or bit that can be read and/or written even if the controller is in the snooze mode.

|                | Address | Register Name | Reset | bit7              | bit6              | bit5          | bit4                | bit3         | bit2             | bit1          | bit0              |

|----------------|---------|---------------|-------|-------------------|-------------------|---------------|---------------------|--------------|------------------|---------------|-------------------|

|                | 0x00    | MainIntStat   | 0x00  | SIEIntStat        | BulkIntStat       | EPrIntStat    | IDEIntStat          |              | PortIntStat      |               | RcvEP0Setup       |

|                | 0x01    | SIEIntStat    | 0x00  | VBUSChanged       | Non_J             | DetectReset   | DetectSuspend       | RcvSOF       | ChirpCmp         | RestoreCmp    |                   |

|                | 0x02    | BulkIntStat   | 0x00  | CBWCmp            | CBWShort          | CBWLong       | CBWErr              | CSWCmp       | CSWErr           | BulkInCmp     | BulkOutCmp        |

| w DataShaat411 | 0x03    | EPrIntStat    | 0x00  |                   |                   |               |                     | EP0IntStat   | EPaIntStat       | EPbIntStat    | EPcIntStat        |

| w.DataSheet4U  | 0x04    | IDEIntStat    | 0x00  |                   |                   |               |                     |              | DTCmp            | DetectINTRQ   | DetectTerm        |

|                | 0x05    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x06    | PortIntStat   | 0x00  |                   |                   |               |                     |              |                  | PortInt1      | PortInt0          |

|                | 0x07    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x08    | EP0IntStat    | 0x00  | PingTranACK       |                   | INTranACK     | OUTTranACK          | INTranNAK    | OUTTranNAK       | INTranErr     | OUTTranErr        |

|                | 0x09    | EPaIntStat    | 0x00  | PingTranACK       | OUTShortACK       | INTranACK     | OUTTranACK          | INTranNAK    | OUTTranNAK       | INTranErr     | OUTTranErr        |

|                | 0x0A    | EPbIntStat    | 0x00  | PingTranACK       | OUTShortACK       | INTranACK     | OUTTranACK          | INTranNAK    | OUTTranNAK       | INTranErr     | OUTTranErr        |

|                | 0x0B    | EPcIntStat    | 0x00  | PingTranACK       | OUTShortACK       | INTranACK     | OUTTranACK          | INTranNAK    | OUTTranNAK       | INTranErr     | OUTTranErr        |

|                | 0x0C    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x0D    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x0E    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x0F    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | -       | •             |       |                   |                   |               |                     |              |                  | •             |                   |

|                | 0x10    | MainIntEnb    | 0x00  | EnSIEIntStat      | EnBulkIntStat     | EnEPrIntStat  | EnIDEIntStat        |              | EnPortIntStat    |               | EnRcvEP0<br>Setup |

|                | 0x11    | SIEIntEnb     | 0x00  | EnVBUS<br>Changed | EnNon_J           | EnDetectReset | EnDetect<br>Suspend | EnRcvSOF     | EnChirpCmp       | EnRestoreCmp  | ootap             |

|                | 0x12    | BulkIntEnb    | 0x00  | EnCBWCmp          | EnCBWShort        | EnCBWLong     | EnCBWErr            | EnCSWCmp     | EnCSWErr         | EnBulkInCmp   | EnBulkOut<br>Cmp  |

|                | 0x13    | EPrIntEnb     | 0x00  |                   |                   |               |                     | EnEP0IntStat | EnEPaIntStat     | EnEPbIntStat  | EnEPcIntStat      |

|                | 0x14    | IDEIntEnb     | 0x00  |                   |                   |               |                     |              | EnDTCmp          | EnDetectINTRQ | EnDetectTerm      |

|                | 0x15    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x16    | PortIntEnb    | 0x00  |                   |                   |               |                     |              |                  | EnPortInt1    | EnPortInt0        |

|                | 0x17    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x18    | EP0IntEnb     | 0x00  | EnPingTran<br>ACK |                   | EnINTranACK   | EnOUTTran<br>ACK    | EnINTranNAK  | EnOUTTran<br>NAK | EnINTranErr   | EnOUTTranErr      |

|                | 0x19    | EPaIntEnb     | 0x00  | EnPingTran<br>ACK | EnOUTShort<br>ACK | EnINTranACK   | EnOUTTran<br>ACK    | EnINTranNAK  | EnOUTTran<br>NAK | EnINTranErr   | EnOUTTranErr      |

|                | 0x1A    | EPbIntEnb     | 0x00  | EnPingTran<br>ACK | EnOUTShort<br>ACK | EnINTranACK   | EnOUTTran<br>ACK    | EnINTranNAK  | EnOUTTran<br>NAK | EnINTranErr   | EnOUTTranErr      |

|                | 0x1B    | EPcIntEnb     | 0x00  | EnPingTran<br>ACK | EnOUTShort<br>ACK | EnINTranACK   | EnOUTTran<br>ACK    | EnINTranNAK  | EnOUTTran<br>NAK | EnINTranErr   | EnOUTTranErr      |

|                | 0x1C    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x1D    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x1E    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                | 0x1F    | (reserved)    | 0xXX  |                   |                   |               |                     |              |                  |               |                   |

|                  | Address           | Register Name            | Reset        | bit7         | bit6         | bit5          | bit4         | bit3            | bit2         | bit1              | bit0            |

|------------------|-------------------|--------------------------|--------------|--------------|--------------|---------------|--------------|-----------------|--------------|-------------------|-----------------|

|                  | 0x20              | ChipReset                | 0x00         |              |              |               |              |                 |              | ResetSIE          | ResetALL        |

|                  | 0x21              | RevisionNum              | 0x31         |              |              |               |              |                 |              |                   |                 |

|                  | 0x22              | PMContorol               | 0x00         | InSnooze     |              |               | ResetUTM     | PLLSel          | SleepEnb     | Analog            | Snooze          |

|                  | 0x23              | USBControl               | 0x00         | DisBusDetect |              |               |              | SendWakeup      | RestoreUSB   | Pwdown<br>GoChirp | ActiveUSB       |

|                  | 0x24              | USBStatus                | 0xXX         | VBUS         | FSxHS        |               |              |                 |              | LineSta           |                 |

|                  | 0x25              | XcvrControl              | 0x41         | TermSelect   | XcvrSelect   |               |              |                 |              | OpMoo             |                 |

|                  | 0x26              | USBTest                  | 0x00         | EnHSTest     |              |               |              | SE0 NAK         | TEST_J       | TEST_K            | TestPacket      |

|                  | 0x27              | (reserved)               | 0xXX         |              |              |               |              | _               | _            | -                 |                 |

|                  | 0x28              | USBAddress               | 0x00         |              |              |               |              | USBAddress[6:0] |              |                   |                 |

| www.DataSheet4U. | 0 <sub>0x29</sub> | EPrControl               | 0x00         | DMARunning   |              |               | ALLFIFOCIr   |                 | AutoEnShort  | ALLForceNAK       | EPrForce        |

|                  | 0x2A              | BulkOnlyControl          | 0x00         |              |              |               |              |                 | GoCBWMode    | GoCSWMode         | STALL<br>CSWSel |

|                  | 0x2B              | BulkOnlyConfig           | 0x00         |              | CBWEP        | Number        |              |                 | CSWEP        |                   | 0011001         |

|                  | 0x2C              | (reserved)               | 0xXX         |              | 02112        |               |              |                 | 00112        |                   |                 |

|                  | 0x2D              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x2E              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x2F              | ChipConfig               | 0x00         | RDYxWAIT     | WaitMode     | IntMode       |              |                 |              |                   |                 |

|                  | 0/21              | ChipColling              | 0,00         | 10 TAUAT     | Wallwood     | Intinode      |              |                 |              |                   |                 |

|                  | 0x30              | EP0Setup_0               | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x30              | EP0Setup_0<br>EP0Setup_1 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x32              | EP0Setup_1<br>EP0Setup_2 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x32              | EP0Setup_2<br>EP0Setup_3 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x34              | EP0Setup_3<br>EP0Setup_4 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x34              | EP0Setup_4<br>EP0Setup_5 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x36              | EP0Setup_5<br>EP0Setup_6 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x30              | EP0Setup_0<br>EP0Setup_7 | 0x00         |              |              |               |              |                 |              |                   |                 |

|                  | 0x38              | FrameNumber_H            | 0x80         | FnInvalid    |              |               |              |                 | F            | rameNumber[10:8   | 1               |

|                  | 0x39              | FrameNumber_L            | 0x00         | Timvand      |              |               | FrameNu      | mber[7:0]       |              | ramentamber[10.c  | 1               |

|                  | 0x3A              | (reserved)               | 0xXX         |              |              |               | Tranicisa    |                 |              |                   |                 |

|                  | 0x3B              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x3C              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x3D              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x3E              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x3F              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | UNU!              | (                        | 0,000        |              |              |               |              |                 |              |                   |                 |

|                  | 0x40              | EP0Config 0              | 0x00         | INxOUT       |              |               |              |                 |              |                   |                 |

|                  | 0x40              | (reserved)               | 0x00<br>0xXX |              |              |               |              |                 |              |                   |                 |

|                  |                   | EP0Control 0             | 0x00         | AutoForceNAK | InEnShortPkt |               |              | InForceNAK      | InForceSTALL | OutForceNAK       | OutForce        |

|                  | 0x42              | -                        |              |              | MENSHOLLAK   | InTegrals 0-4 | InTegrals OF |                 | MFUICESTALL  |                   | STALL           |

|                  | 0x43              | EP0Control_1             | 0x00         | InToggleStat |              | InToggleSet   | InToggleClr  | OutToggleStat   |              | OutToggleSet      | OutToggleClr    |

|                  | 0x44              | (reserved)               | 0xXX         |              |              |               | 50051        |                 | 10.01        |                   |                 |

|                  | 0x45              | EP0FIFORemain            | 0x00         |              |              |               |              | FORemain Count  | er[6:0]      |                   |                 |

|                  | 0x46              | EP0FIFOforCPU            | 0xXX         | FIFOFmate    | FIFOE        |               | EPUFIF       | OData           | FIFOOIs      | E. E.E.O.         | E-EIEO-d        |

|                  | 0x47              | EP0FIFOControl           | 0x80         | FIFOEmpty    | FIFOFull     |               |              |                 | FIFOCIr      | EnFIFOwr          | EnFIFOrd        |

|                  | 0x48              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x49              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4A              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4B              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4C              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4D              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4E              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

|                  | 0x4F              | (reserved)               | 0xXX         |              |              |               |              |                 |              |                   |                 |

| А          | ddress | Register Name       | Reset | bit 7        | bit 6      | bit 5                 | bit 4        | bit 3            | bit 2     | bit 1             | bit0      |

|------------|--------|---------------------|-------|--------------|------------|-----------------------|--------------|------------------|-----------|-------------------|-----------|

|            | 0x50   | EPaConfig_0         | 0x00  | INxOUT       |            |                       |              |                  | EndPointN | lumber[3:0]       |           |

|            | 0x51   | EPaConfig_1         | 0x00  | JoinIDE      | ToggleMode | EnEndPoint            | DoubleBuf    |                  | r         | MaxPacketSize[2:  | 0]        |

|            | 0x52   | EPaControl_0        | 0x00  | AutoForceNAK | EnShortPkt | AutoForceNAK<br>Short |              |                  |           | ForceNAK          | ForceSTAL |

|            | 0x53   | EPaControl_1        | 0x00  |              |            |                       |              | ToggleStat       |           | ToggleSet         | ToggleClr |

|            | 0x54   | EPaFIFORemain_H     | 0x00  |              |            |                       | EPaFIFORema  | in Counter[15:8] |           |                   |           |

|            | 0x55   | EPaFIFORemain_L     | 0x00  |              |            |                       | EPaFIFORema  | ain Counter[7:0] |           |                   |           |

|            | 0x56   | EPaFIFOforCPU       | 0xXX  |              |            |                       | EPaFI        | FOData           |           |                   |           |

|            | 0x57   | EPaFIFOControl      | 0x80  | FIFOEmpty    | FIFOFull   |                       |              |                  | FIFOCIr   | EnFIFOwr          | EnFIFOrd  |

|            | 0x58   | EPbConfig_0         | 0x00  | INxOUT       |            |                       |              |                  | EndPointN | lumber[3:0]       |           |

| Sheet4U.co | 0x59   | EPbConfig_1         | 0x00  | JoinIDE      | ToggleMode | EnEndPoint            | DoubleBuf    |                  | 1         | /laxPacketSize[2: | 0]        |

|            | 0x5A   | EPbControl_0        | 0x00  | AutoForceNAK | EnShortPkt | AutoForceNAK<br>Short |              |                  |           | ForceNAK          | ForceSTAL |

|            | 0x5B   | EPbControl_1        | 0x00  |              |            | Short                 |              | ToggleStat       |           | ToggleSet         | ToggleClr |

|            | 0x5C   | EPbFIFORemain_H     | 0x00  |              |            |                       | EPbFIFORema  | in Counter[15:8] |           |                   |           |

|            | 0x5D   | <br>EPbFIFORemain_L | 0x00  |              |            |                       |              | ain Counter[7:0] |           |                   |           |

|            | 0x5E   | -<br>EPbFIFOforCPU  | 0xXX  |              |            |                       |              | FOData           |           |                   |           |

|            | 0x5F   | EPbFIFOControl      | 0x80  | FIFOEmpty    | FIFOFull   |                       |              |                  | FIFOCIr   | EnFIFOwr          | EnFIFOrd  |

|            |        |                     |       | . 19         |            |                       |              |                  |           |                   |           |

|            | 0x60   | EPcConfig_0         | 0x00  | INxOUT       | ISO        |                       |              |                  | EndPointN | lumber[3:0]       |           |

|            |        | EPcConfig_1         | 0x00  | JoinIDE      | ToggleMode | EnEndPoint            | DoubleBuf    |                  |           | /axPacketSize[2:  | 01        |

| -          |        |                     |       |              |            | AutoForceNAK          | DoubleDui    |                  |           | ForceNAK          | -         |

|            |        | EPcControl_0        | 0x00  | AutoForceNAK | EnShortPkt | Short                 |              |                  |           |                   | ForceSTAL |

|            | 0x63   | EPcControl_1        | 0x00  |              |            |                       |              | ToggleStat       |           | ToggleSet         | ToggleCl  |

|            | 0x64   | EPcFIFORemain_H     | 0x00  |              |            |                       |              | in Counter[15:8] |           |                   |           |

|            |        | EPcFIFORemain_L     | 0x00  |              |            |                       |              | in Counter[7:0]  |           |                   |           |

|            |        | EPcFIFOforCPU       | 0xXX  |              |            |                       | EPcFI        | OData            |           | 1                 |           |

|            | 0x67   | EPcFIFOControl      | 0x80  | FIFOEmpty    | FIFOFull   |                       |              |                  | FIFOCIr   | EnFIFOwr          | EnFIFOrd  |

|            | 0x68   | IsoMaxSize_H        | 0x00  |              |            |                       |              |                  | Iso       | MaxPacketSize[1   | 0:8]      |

|            | 0x69   | IsoMaxSize_L        | 0x00  |              |            | IsoMaxPack            | (etSize[7:2] |                  |           |                   |           |

|            | 0x6A   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x6B   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x6C   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x6D   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x6E   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x6F   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            |        |                     | -     |              |            |                       |              |                  | 1         | T                 |           |

|            | 0x70   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x71   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x72   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x73   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x74   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x75   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x76   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x77   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x78   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x79   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |

|            | 0x7A   | (reserved)          | 0xXX  |              |            |                       |              |                  |           |                   |           |