# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

#### DS3598-3.4

# **MA9000 Series** SILICON-ON-SAPPHIRE RADIATION HARD GATE ARRAYS

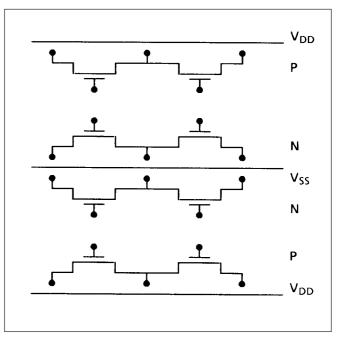

The logic building block for the GPS double level metal CMOS/SOS gate arrays is a four transistor 'cell-unit' equivalent in size to a 2 input NAND gate. Back to back cellunits as illustrated, organised in rows, form the core of the array

GEC PLESSEY

SEMICONDUCTORS

The interconnection patterns that cause groups of cell units within a row, to become defined logic cells, and the models which are used to simulate these cells, are stored as software in LIBRARIES. Cells up to the complexity of, say, multiple bit shift registers are treated in this way.

Higher complexity functions are described by MACROS as the interconnection of defined cells. Macros are 'hard', 'soft', or 'firm' according to the constraints that are applied to the distribution of the component cells within the array and whether the full function is simulated by a model or by the additive effects of the component cells.

### **FEATURES**

- Radiation Hard to 1MRad(Si)

- High SEU Immunity, Latch-Up Free

- Double-Level-Metal CMOS/SOS Technology

- 2.5 Micron Design Rules

- Typical Gate Delay 1.2nS With 2 Loads, 60MHz Toggle Speeds

- Comprehensive Library of Logic Cells and Logic Function **Building Macros**

- 100% Automatic Place and Route for Typically 70% Utilisation

#### **ARRAY OPTIONS**

| Array  |       |     |       | Pads  |

|--------|-------|-----|-------|-------|

| Туре   | Units | I/O | Power | Total |

| MA9007 | 748   | 46  | 2     | 48    |

| MA9024 | 2484  | 80  | 4     | 84    |

| MA9040 | 4048  | 102 | 4     | 106   |

Each cell-unit is equivalent to a 2 input NAND gate.

Any I/O site may be configured as a power pad to give flexible bonding options, but to standardise testing, preferred positions exist.

Figure 1: Cell Unit

# **MA9000 Series**

# **CHARACTERISITICS & RATINGS**

| Symbol          | Parameter             | Min. | Max.                  | Units |

|-----------------|-----------------------|------|-----------------------|-------|

| V <sub>DD</sub> | Supply voltage        | -0.5 | 7                     | V     |

| V <sub>I</sub>  | Input voltage         | -0.3 | V <sub>DD</sub> + 0.3 | V     |

| T <sub>A</sub>  | Operating temperature | -55  | 125                   | °C    |

| T <sub>S</sub>  | Storage temperature   | -65  | 150                   | °C    |

Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions, or at any other condition above those indicated in the operations section of this specification. is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 1: Absolute Maximum Ratings

| Symbol           | Parameter                | Conditions             | Min. | Тур. | Max. | Units            |

|------------------|--------------------------|------------------------|------|------|------|------------------|

| V <sub>DD</sub>  | Supply voltage           | -                      | 4.5  | 5.0  | 5.5  | V                |

| V <sub>IH1</sub> | TTL input high voltage   | -                      | 2.0  | -    | -    | V                |

| V <sub>IL1</sub> | TTL input low voltage    | -                      | -    | -    | 0.8  | V                |

| V <sub>IH2</sub> | CMOS input high voltage  | -                      | 80   | -    | -    | %V <sub>DD</sub> |

| V <sub>IL2</sub> | CMOS input low voltage   | -                      | -    | -    | 20   | %V <sub>DD</sub> |

| V <sub>OH1</sub> | TTL output high voltage  | I <sub>ОН</sub> = -2mА | 2.4  | -    | -    | V                |

| V <sub>OL1</sub> | TTL output low voltage   | $I_{OL} = 5mA$         | -    | -    | 0.4  | V                |

| V <sub>OH2</sub> | CMOS output high voltage | I <sub>ОН</sub> = -4mА | 90   | -    | -    | %V <sub>DD</sub> |

| V <sub>OL2</sub> | CMOS output low voltage  | $I_{OL} = 4mA$         | -    | -    | 10   | %V <sub>DD</sub> |

| IL.              | Input leakage current    | -                      | -    | -    | 10   | μA               |

| l <sub>oz</sub>  | Output leakage current   | Tristate Output        | -    | -    | 30   | μA               |

| I <sub>DD</sub>  | Power supply current     | -                      | -    | 0.1  | *    | mA               |

$V_{\text{DD}}$  = 5V ±10%, over full operating temperature.

\* Dependent on array type.

Table 2: Electrical Characteristics

## **AC CHARACTERISTICS**

| Cell Name | Function                | O/P Edge         | Inherent Delay | Per 1pF Load* | Units |

|-----------|-------------------------|------------------|----------------|---------------|-------|

| NOP       | Push/Pull Output Buffer | Rising           | 0.5            | 0.4           | ns    |

|           |                         | Falling          | 0.3            | 0.2           |       |

| NOR2      | 2 Input NOR             | Rising           | 1.6            | 13.6          | ns    |

|           |                         | Falling          | 0.8            | 5.0           |       |

|           |                         | Rising CK - QB   | 4.6            | 13.7          |       |

|           |                         | Falling CK - QB  | 7.8            | 13.6          |       |

| RDT       | Reset D Type            | Data Set-up time | 7.1            | -             | ns    |

|           |                         | Data Hold time   | 4.4            | -             |       |

\* 1pF is equivalent to fanout of 5 standard gates

Table 3: Electrical Characteristics

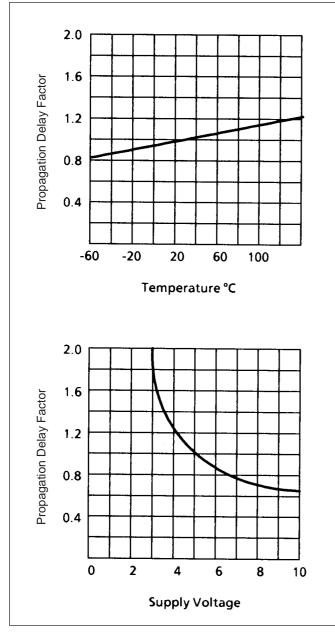

#### **PROPAGATION DELAY**

Worst case maximum propagation delays for 5 volts working and 25°C are stated in the cell libraries. These are for the data change or state change which gives the greatest delay. Typical process figures under the same conditions are generally 60% of those listed.

Use the following normalised graphs to obtain converstion factors to predict delays at any other working temperature or voltage:

Figure 2: Propogation Delay vs Temperature & Propogation Delay vs Supply Voltage

## **PACKAGE OPTIONS**

|                                                                                                                                   | MA9007             | MA9024    | MA9040    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|-----------|--|--|--|

|                                                                                                                                   | 196 x 129          |           |           |  |  |  |

|                                                                                                                                   | 100 x 120          | 247 7 240 | 001 X 002 |  |  |  |

| DIL14                                                                                                                             | Х                  |           |           |  |  |  |

| DIL16                                                                                                                             | Х                  |           |           |  |  |  |

| DIL20                                                                                                                             | Х                  |           |           |  |  |  |

| DIL24                                                                                                                             | Х                  | Х         |           |  |  |  |

| DIL28                                                                                                                             | Х                  | Х         |           |  |  |  |

| DIL40                                                                                                                             | Х                  | Х         |           |  |  |  |

| DIL48                                                                                                                             |                    | Х         | Х         |  |  |  |

| DIL64                                                                                                                             |                    | Х         | Х         |  |  |  |

| LCC28                                                                                                                             | Х                  |           |           |  |  |  |

| LCC40                                                                                                                             | Х                  | Х         |           |  |  |  |

| LCC44                                                                                                                             | Х                  |           |           |  |  |  |

| LCC48                                                                                                                             |                    | Х         | Х         |  |  |  |

| LCC68                                                                                                                             |                    | Х         | Х         |  |  |  |

| LCC84                                                                                                                             |                    | Х         | Х         |  |  |  |

| FPK16                                                                                                                             | Х                  |           |           |  |  |  |

| FPK20                                                                                                                             | Х                  |           |           |  |  |  |

| FPK24                                                                                                                             | Х                  |           |           |  |  |  |

| FPK28                                                                                                                             | Х                  | Х         |           |  |  |  |

| FPK64                                                                                                                             |                    | Х         | Х         |  |  |  |

| FPK68                                                                                                                             |                    | Х         | Х         |  |  |  |

| FPK84                                                                                                                             |                    | Х         | Х         |  |  |  |

| PGA68                                                                                                                             |                    | Х         | Х         |  |  |  |

| PGA84                                                                                                                             |                    | Х         | Х         |  |  |  |

| PGA120                                                                                                                            |                    | Х         | Х         |  |  |  |

| PGA144                                                                                                                            |                    | Х         | Х         |  |  |  |

| DIL = Dual in li                                                                                                                  | DIL = Dual in line |           |           |  |  |  |

| LCC = Leadless chip carrier                                                                                                       |                    |           |           |  |  |  |

| FPK = Leaded                                                                                                                      | flatpack           |           |           |  |  |  |

| PGA = Pin grid                                                                                                                    | array              |           |           |  |  |  |

| These are standard packages. If your package requirement is not shown above, discuss other options with an applications engineer. |                    |           |           |  |  |  |

### **MA9000 Series**

#### **RADIATION TOLERANCE**

For product procured to guaranteed total dose radiation levels, each wafer lot will be approved when all sample devices from each lot pass the total dose radiation test.

The sample devices will be subjected to the total dose radiation level (Cobalt-60 Source), defined by the ordering code, and must continue to meet the electrical parameters specified in the data sheet. Electrical tests, pre and post irradiation, will be read and recorded.

GPS can provide radiation testing compliant with MIL-STD-883C remote sensing method 1019 notice 5.

| Total Dose (Function to specification)*      | 3x10 <sup>5</sup> Rad(Si)             |

|----------------------------------------------|---------------------------------------|

| Transient Upset (Stored data loss)           | 5x10 <sup>10</sup> Rad(Si)/sec        |

| Transient Upset (Survivability)              | >1x10 <sup>12</sup> Rad(Si)/sec       |

| Neutron Hardness (Function to specification) | >1x10 <sup>15</sup> n/cm <sup>2</sup> |

| Single Event Upset**                         | <1x10 <sup>-10</sup> Errors/bit day   |

| Latch Up                                     | Not possible                          |

\* Other total dose radiation levels available on request

\*\* Worst case galactic cosmic ray upset - interplanetary/high altitude orbit

Table 4: Radiation Hardness Parameters

#### **CELL LIBRARY QUICK GUIDE**

8 input NOR

| Cell Name                                                                                                                                                          | Function                                                                                                                                                                                                                                                                                                                                                                  | Cell Units                                                                                        | Cell Name                                                                                                                                                  | Function                                                                                                                                                                                                                                                                                                                                                                | Cell Units                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| COMBINAT                                                                                                                                                           | IONAL GATES                                                                                                                                                                                                                                                                                                                                                               |                                                                                                   | NOR12<br>NOR16                                                                                                                                             | 12 input NOR<br>16 input NOR                                                                                                                                                                                                                                                                                                                                            | 8<br>11                                                                                          |

| INV<br>DUALINV<br>INVB<br>INVC<br>BUFF<br>BUFFC<br>NAND2<br>NAND2<br>NAND2<br>NAND3<br>NAND4<br>NAND4<br>NAND12<br>NAND16<br>AND2<br>AND3<br>AND4<br>NOR2<br>NOR2B | Inverter<br>Dual inverter<br>Fast inverter<br>Super fast inverter<br>Non-inverting buffer<br>Fast non-inverting buffer<br>2 input NAND<br>Fast 2 input NAND<br>3 input NAND<br>4 input NAND<br>12 input NAND<br>16 input NAND<br>2 input AND<br>3 input AND<br>2 input AND<br>3 input AND<br>3 input AND<br>4 input AND<br>4 input AND<br>5 input NOR<br>Fast 2 input NOR | 1<br>1<br>2<br>1<br>2<br>3<br>1<br>2<br>2<br>2<br>6<br>8<br>11<br>2<br>3<br>1<br>2<br>3<br>1<br>2 | NOR16<br>OR2<br>OR3<br>OR4<br>ANDNOR<br>ANDOR<br>ORNAND<br>ORAND<br>A2N01<br>A201<br>02NA1<br>02A1<br>EXNOR<br>EXORN<br>SEL21NV<br>SEL2<br>SEL41NV<br>SEL4 | 2 input NOR<br>2 input OR<br>3 input OR<br>4 Input OR<br>2 + 2 input AND/NOR<br>2 + 2 input AND/OR<br>2 + 2 OR/NAND<br>2 + 2 OR/AND<br>2 + 1 Input AND/NOR<br>2 + 1 input AND/OR<br>2 + 1 input OR/NAND<br>2 + 1 input OR/NAND<br>2 + 1 input OR/NAND<br>Exclusive NOR<br>Exclusive OR<br>Select 1 of 2 (inverting)<br>Select 1 of 2<br>4 bit data selector (inverting) | 2<br>2<br>3<br>2<br>3<br>2<br>3<br>2<br>2<br>2<br>2<br>2<br>3<br>3<br>3<br>3<br>3<br>3<br>6<br>7 |

| NOR3<br>NOR4                                                                                                                                                       | 3 input NOR<br>4 input NOR                                                                                                                                                                                                                                                                                                                                                | 2<br>2                                                                                            |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                  |

6

NOR8

# MA9000 Series

| Cell Name        | Function                                   | Cell Units | Cell Name                         | Function                                                                                               | Cell Units    |  |

|------------------|--------------------------------------------|------------|-----------------------------------|--------------------------------------------------------------------------------------------------------|---------------|--|

| DECODERS         |                                            |            | REGISTERS                         | SHIFT REGISTERS                                                                                        |               |  |

| DEC2T4<br>DEC3T8 | 2 to 4 line decoder<br>3 to 8 line decoder | 6<br>11    | SHRx<br>RSHRx                     | Multibit (x = 2-8) serial register<br>Multibit (x = 2-8) serial reg. with r                            |               |  |

| DEC4T16          | 4 to 16 line decider                       | 40         | DREGx<br>DREGTx                   | Multibit parallel register (x = 2-8)<br>Multibit parallel register (x = 2-8)<br>with tri-state outputs | 8-22<br>12-36 |  |

|                  |                                            |            | HPLSx                             | Half parallel loading shift register                                                                   | s 22-64       |  |

| HAD              | Half adder<br>Full adder                   | 5          |                                   | (x = 2-8)                                                                                              |               |  |

| FAD<br>FLAD      | Full adder<br>Fast look ahead adder        | 8<br>6     | INVERTING T                       | RI-STATE BUFFERS                                                                                       |               |  |

| LAH2             | 2 bit look ahead unit                      | 10         |                                   |                                                                                                        |               |  |

| LAH3             | 3 bit look ahead unit                      | 14         | TRIBUFF                           | Tristate buffer (enable high)                                                                          | 2             |  |

| LAH4             | 4 bit look ahead unit                      | 24         | TRIBUFFL                          | Tristate buffer (enable low)                                                                           | 2             |  |

| ADD4             | 4 bit look ahead adder                     | 50         | TRINV                             | Tristate inv buffer (enable high)                                                                      | 2             |  |

| ADD8             | 8 bit look ahead adder                     | 106        | TRINVL                            | Tristate inv. buffer (enable low)                                                                      | 2             |  |

| SIMPLE LATCHES   |                                            |            | INPUT OUTPUT AND PERIPHERAL CELLS |                                                                                                        |               |  |

| NASR             | NAND set reset-latch                       | 3          | DIP                               | Direct input (protection cicuit only                                                                   | /)            |  |

| NOSR             | NOR set-reset latch                        | 3          | PUP                               | Pull up (approx 30 Kohms)                                                                              | ,             |  |

|                  |                                            |            | PDO                               | Pull down (approx 40 Kohms)                                                                            |               |  |

| TRANSPARE        | NT LATCHES                                 |            | TSCHMITT                          | TTL compatible Schmitt                                                                                 | 6             |  |

|                  |                                            |            | CSCHMITT                          | CMOS compatible Schmitt                                                                                | 6             |  |

| DL               | D-latch (Active low)                       | 4          | CMOSIN                            | CMOS buffer (non-inverting)                                                                            | 1             |  |

| DLH              | D-latch(Actlve high)                       | 4          | TTLIN                             | TTL buffer (non-inverting)                                                                             | 3             |  |

| SDL              | Set D-latch                                | 4          | NOP                               | Push/pull output buffer (inverting                                                                     | )             |  |

| RDL              | Reset D-latch                              | 4          | WNOP                              | Multiple NOP                                                                                           |               |  |

| SRDL             | Set/reset D-latch                          | 5          | BOP                               | Push/pull output buffer (non inve                                                                      | rting)        |  |

|                  |                                            |            | ZOP                               | Tri-state output buffer                                                                                |               |  |

| EDGE TRIGG       | ERED LATCHES                               |            | ODN                               | Open drain output pull down                                                                            |               |  |

|                  |                                            | _          | ODP                               | Open drain output pull up                                                                              |               |  |

| RETS             | Latch with reset                           | 7          | TRIOP                             | Tristate I/O buffer                                                                                    | 4             |  |

| SRETS            | Latch with reset and set                   | 8          | BUSINT<br>STEPUP                  | Bus interface<br>Output Buffer                                                                         | 6<br>6        |  |

| MASTER-SLA       | VE FLIP-FLOPS                              |            | STEPUP                            |                                                                                                        | 0             |  |

|                  |                                            |            | POWER SUP                         | PLY PADS                                                                                               |               |  |

| DT               | D-type                                     | 6          |                                   |                                                                                                        |               |  |

| D2T              | Dual input D-type                          | 8          | VDD                               | V <sub>DD</sub> pad                                                                                    |               |  |

| SDT              | Set D-type                                 | 7          | VSS                               | V <sub>ss</sub> pad                                                                                    |               |  |

| RDT              | Reset D-type                               | 7          |                                   |                                                                                                        |               |  |

| SRDT             | Set/reset D-type                           | 8          |                                   |                                                                                                        |               |  |

| JK               | JK flip-flop                               | 10         |                                   |                                                                                                        |               |  |

| SDK              | JK flip-flopwith set                       | 11         |                                   |                                                                                                        |               |  |

| RJK              | JK flip-flop with reset                    | 11         |                                   |                                                                                                        |               |  |

| SRJK             | JK flip-flop with reset and set            | 12         |                                   |                                                                                                        |               |  |

| TOGGLE FLIP      | TOGGLE FLIP-FLOPS                          |            |                                   |                                                                                                        |               |  |

| STT  | Set T-type       | 7 |

|------|------------------|---|

| RTT  | Reset T-type     | 7 |

| SRTT | Set/reset T-type | 8 |

#### SYNCHRONOUS COUNTER

| SYNC  | Synchronous counter stage | 10 |

|-------|---------------------------|----|

| 01110 | Cynchronous counter stage | 10 |

#### MACROS

The following Macros are included in the MA9000 library. GPS are constantly adding new Macros to the library, please contact our nearest office for information on the latest additions.

| Macro name                                                                                                                        | Macro name                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACOUNTn<br>ALU4<br>GCOUNTn<br>JCOUNTn<br>LADDn<br>MCOMPn<br>PARITYn<br>RADDn<br>SEL8<br>SEL16<br>M2901<br>M2909<br>M2902<br>M2910 | Asynchronous counters<br>ALU<br>Gray counters<br>Johnson counters<br>Lookahead adders<br>Magnitude comparators<br>Parity detectors<br>Ripple carry adders<br>Select 1 of 8<br>Select 1 of 16<br>4 bit slice microprocessor<br>4 bit microprogram controller<br>Look ahead carry unit<br>12 bit microprogram sequencer |

| M2918                                                                                                                             | Pipeline register                                                                                                                                                                                                                                                                                                     |

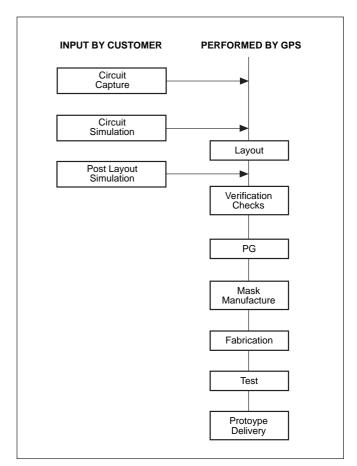

#### **DEVELOPMENT INTERFACES**

Circuit design, captive and simulation activities are carried out by the customer. Schematic capture and simulation libraries for Dazix and Mentor Graphics CAE systems are provided by GPS. GPS will accept a simulated design and perform layout, verification checks and PG. GPS will then procure masks and fabricate and test parts prior to prototype delivery. The MA9000 arrays fall within the ESA capability domain.

DAZIX is a trademark of Intergraph UK

Mentor Graphics is a trademark of Mentor Graphics Corporation.

Figure 3: Development Interfaces

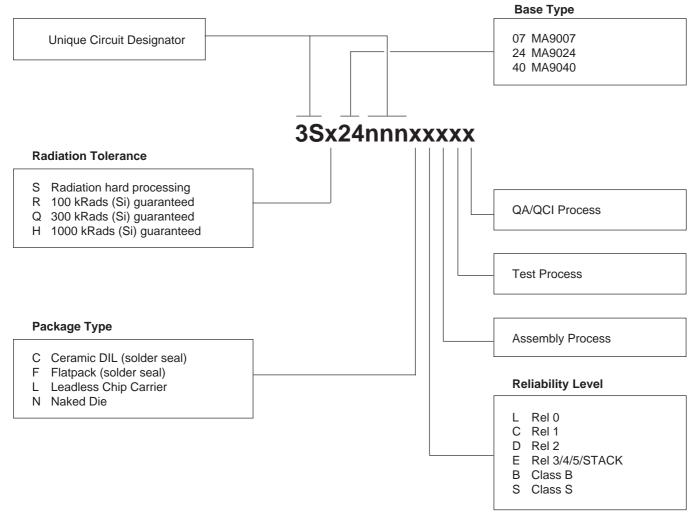

#### **ORDERING INFORMATION**

For details of Reliability, QA/QCI, Test, and Assembly options, see 'Manufacturing Capability and Quality Assurance Standards'.

# GEC PLESSEY

#### HEADQUARTERS OPERATIONS

#### GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire, SN2 2QW, United Kingdom. Tel: (01793) 518000 Fax: (01793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

#### CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260 Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon, UK Tel: (01793) 518527/518566 Fax: (01793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1995 Publication No. DS3598-3.4 May 1995

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any peducts whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.