#### **Features**

- SpaceWire Router

- Logical to Physical addressing translation

- Priority Management

- Header Deletion Capability

- Eight Bidirectional SpaceWire links

- Full duplex communication

- Data rate from 2 up to 200 Mbit/s in each direction

- Two External Interfaces

- Dedicated Input and Output FIFOs

- 9-bit wide Interface

- Configuration Port

- Read/Write Accesses to internal registers

- Accessible from both the spacewire links (8 channels) and the external interfaces

- Remote Memory Access Protocol (RMAP) support

- Time Code Interface

- Master/Slave Capability

- Error/Status Interface

- Operating range

- Voltages

- 3V to 3.6V

- Temperature

- - 55°C to +125°C

- Maximum Power consumption

- All spacewire links active at 200Mbit/s: 4W -TBC

- Radiation Performance

- Total dose tested successfully up to 300 Krad (Si)

- No single event latchup below a LET of 80 MeV/mg/cm2

- ESD better than 2000V

- Quality Grades

- QML-Q or V with SMD

- Package: 196pins MQFPF

- Mass: 12grams

# SpW-10X SpaceWire Router

## **AT7910E**

## 1. Description

The SpW-10X SpaceWire routing switch is capable of connecting many nodes, providing a means of routing packets between the nodes connected to it. It comprises eight SpaceWire link interfaces and a routing matrix. The routing matrix enables packets arriving at one link interface to be transferred to and sent out of another link interface on the routing switch.

The AT7910E was designed by Austrian Aerospace (Austria) and the University of Dundee (Scotland). It is manufactured using the SEU hardened cell library from Atmel MH1RT CMOS 0.35µm radiation hardened sea of gates technology.

For any technical question relative to the functionality of the AT7910E please contact Atmel technical support at <a href="mailto:assp-applab.hotline@nto.atmel.com">assp-applab.hotline@nto.atmel.com</a>.

This document must be read in conjunction with the **University of Dundee "SpaceWire Router SpW-10X User Manual"** available at <u>www.atmel.com</u>.

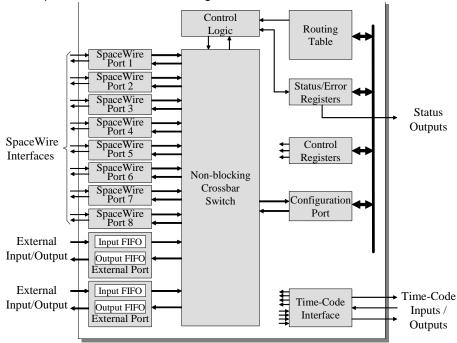

The SpaceWire router comprises the following functional logic blocks:

- Eight SpaceWire bi-directional serial ports.

- Two external parallel input/output ports each comprising an input FIFO and an output FIFO.

- A non-blocking crossbar switch connecting any input port to any output port.

- An internal configuration port accessible via the crossbar switch from the external parallel input/output port or the SpaceWire input/output ports.

- A routing table accessible via the configuration port which holds the logical address to output port mapping.

- Control logic to control the operation of the switch, performing arbitration and group adaptive routing.

- Control registers than can be written and read by the configuration port and which hold control information e.g. link operating speed.

- An external time-code interface comprising tick\_in, tick\_out and current tick count value

- Internal status/error registers accessible via the configuration port

- External status/error signals

A block diagram of the routing switch is given in the following figure:

Figure 1-1. SpaceWire Router Block Diagram

#### 1.1 SpaceWire Ports

The SpaceWire router has eight bi-directional SpaceWire links each conformant to the SpaceWire standard.

Each SpaceWire link is controlled by an associated link register and routing control logic. Packets received on SpaceWire links are routed by the routing control logic to the configuration port, other SpaceWire link ports or the external FIFO ports depending on the packet address.

Packets with invalid addresses are discarded by the SpaceWire router. The SpaceWire link status is recorded in the associated link register and error status is held by the router until cleared by a configuration command.

#### 1.2 External Ports

The SpaceWire router has two bi-directional parallel FIFO interfaces that can be used to connect the router to an external host system. The external port FIFO is two data characters deep.

Each FIFO is written to or read from synchronously with the 30MHz system clock. An eight-bit data interface and an extra control bit for end of packet markers are provided by each external port FIFO. Packets received by the external port are routed by the routing control logic to the configuration port, SpaceWire link ports or the other external port depending on the packet address.

Packets with invalid addresses are discarded by the SpaceWire router.

### 1.3 Configuration Port

The SpaceWire router has one configuration port which performs read and write operations to internal router registers.

Packets are routed to the configuration port when a packet with a leading address byte equal to zero is received. The Remote Memory Access Protocol (RMAP) is used to access the configuration port.

If an invalid command packet is received then the error is flagged to an associated status register and the packet is discarded.

### 1.4 Routing table

The SpaceWire router routing table is set by the router command packets to assign logical addresses to physical destination ports on the router.

A group of destination ports can be set, in each routing table location, to enable group adaptive routing. When a packet is received with a logical address the routing table is checked by the routing control logic and the packet is routed to the destination port when the port is ready. Routing table locations are set to invalid at power on or at reset.

The routing table logical addresses can also be set to support high priority and header deletion. High priority packets are routed before low priority packets and header deletion of logical addresses can be used to support regional logical addressing.

An invalid routing address will cause the packet to be spilled by the control logic.

### 1.5 Routing control logic and crossbar

The routing control logic is responsible for arbitration of output ports, group adaptive routing and the crossbar switching. Arbitration is performed when two or more source ports are requesting to use the same destination port.

A priority based arbitration scheme with two priority levels, high and low, is used where high priority packets are routed before low priority packets. Fair arbitration is performed on packets which have the same priority levels to ensure each packet gets equal access to the output port.

Group adaptive routing control selects one of a number of output ports for sending out the source packet.

## 1.6 Time Code Processing

An internal time-code register is used in the router to allow the router to be a time-code master or a time-code slave.

In master mode the time-code interface is used to provide a tick-in to the SpaceWire routing causing time-codes to be propagated through the network. Two modes of time master operation are supported, an automatic mode where a time-code is propagated on each external tick-in and a normal mode where the time-code is propagated dependent on the external time-in signal.

In time-code slave mode a valid received time-code, one plus the value of the router time-code register, causes a tick-out to be sent to the SpaceWire links and the external time-code interface. The time-code is propagated to all time-code ports except the port on which the time-code was received. If the time-code received is not one plus the value of the time-code register then the time-code register is updated but the tick-out is not performed.

## 1.7 Control/Status Registers

The control and status registers in the SpaceWire router provide the means to control the operation of the router, set the router configuration and parameters or monitor the status of the device. The registers are accessed using RMAP command packets received by the configuration port.

# 2. Pin Configuration

Table 1. Pin assignment

| Pin<br>Number | Name       | Pin<br>Number | Name     | Pin<br>Number | Name          | Pin<br>Number | Name           | Pin<br>Number | Name         |

|---------------|------------|---------------|----------|---------------|---------------|---------------|----------------|---------------|--------------|

| 1             | VDDB       | 41            | VSSB     | 81            | SIN-7         | 121           | EXTINDATA9_6   | 161           | EXTTIMEIN2   |

| 2             | CLK        | 42            | VSSA     | 82            | SOUT-7        | 122           | EXTINDATA9_7   | 162           | EXTTIMEIN3   |

| 3             | RST        | 43            | VDDA     | 83            | SOUT+7        | 123           | EXTINDATA9_8   | 163           | EXTTIMEIN4   |

| 4             | TESTIOE    | 44            | VDDB     | 84            | VSSB          | 124           | EXTINFULL9     | 164           | EXTTIMEIN5   |

| 5             | TESTE      | 45            | DOUT-3   | 85            | VDDB          | 125           | VSSB           | 165           | EXTTIMEIN6   |

| 6             | FEEDBDIV0  | 46            | DOUT+3   | 86            | DOUT-7        | 126           | VDDB           | 166           | EXTTIMEIN7   |

| 7             | VSSA       | 47            | DIN+4    | 87            | DOUT+7        | 127           | EXTINWRITE9    | 167           | SELEXTTIME   |

| 8             | VDDA       | 48            | DIN-4    | 88            | DIN+8         | 128           | EXTOUTDATA10_0 | 168           | TIMECTRRST   |

| 9             | FEEDBDIV1  | 49            | LVDS_REF | 89            | DIN-8         | 129           | EXTOUTDATA10_1 | 169           | EXTTICKOUT   |

| 10            | FEEDBDIV2  | 50            | SIN+4    | 90            | SIN+8         | 130           | EXTOUTDATA10_2 | 170           | EXTTIMEOUT0  |

| 11            | VSSB       | 51            | SIN-4    | 91            | VSSA          | 131           | EXTOUTDATA10_3 | 171           | EXTTIMEOUT1  |

| 12            | VDDPLL     | 52            | SOUT-4   | 92            | VDDA          | 132           | EXTOUTDATA10_4 | 172           | EXTTIMEOUT2  |

| 13            | VCOBias    | 53            | SOUT+4   | 93            | SIN-8         | 133           | EXTOUTDATA10_5 | 173           | EXTTIMEOUT3  |

| 14            | LOOPFILTER | 54            | DOUT-4   | 94            | SOUT-8        | 134           | VSSB           | 174           | VSSB         |

| 15            | VSSPLL     | 55            | DOUT+4   | 95            | SOUT+8        | 135           | VDDB           | 175           | VDDB         |

| 16            | VDDB       | 56            | VSSA     | 96            | DOUT-8        | 136           | EXTOUTDATA10_6 | 176           | EXTTIMEOUT4  |

| 17            | DIN+1      | 57            | VDDA     | 97            | DOUT+8        | 137           | EXTOUTDATA10_7 | 177           | EXTTIMEOUT5  |

| 18            | DIN-1      | 58            | VSSB     | 98            | VSSB          | 138           | EXTOUTDATA10_8 | 178           | EXTTIMEOUT6  |

| 19            | SIN+1      | 59            | VDDB     | 99            | VDDB          | 139           | EXTOUTEMPTY10  | 179           | EXTTIMEOUT7  |

| 20            | SIN-1      | 60            | DIN+5    | 100           | EXTOUTDATA9_0 | 140           | VSSA           | 180           | STATMUXADDR0 |

| 21            | SOUT-1     | 61            | DIN-5    | 101           | EXTOUTDATA9_1 | 141           | VDDA           | 181           | STATMUXADDR1 |

| 22            | SOUT+1     | 62            | SIN+5    | 102           | EXTOUTDATA9_2 | 142           | EXTOUTREAD10   | 182           | STATMUXADDR2 |

| 23            | DOUT-1     | 63            | SIN-5    | 103           | EXTOUTDATA9_3 | 143           | EXTINDATA10_0  | 183           | STATMUXADDR3 |

| 24            | DOUT+1     | 64            | SOUT-5   | 104           | EXTOUTDATA9_4 | 144           | EXTINDATA10_1  | 184           | VSSB         |

| 25            | DIN+2      | 65            | SOUT+5   | 105           | VSSA          | 145           | EXTINDATA10_2  | 185           | VDDB         |

| 26            | DIN-2      | 66            | DOUT-5   | 106           | VDDA          | 146           | EXTINDATA10_3  | 186           | STATMUXOUT0  |

| 27            | SIN+2      | 67            | DOUT+5   | 107           | EXTOUTDATA9_5 | 147           | EXTINDATA10_4  | 187           | STATMUXOUT1  |

| 28            | SIN-2      | 68            | DIN+6    | 108           | VSSB          | 148           | EXTINDATA10_5  | 188           | STATMUXOUT2  |

| 29            | VSSB       | 69            | DIN-6    | 109           | VDDB          | 149           | EXTINDATA10_6  | 189           | VSSA         |

| 30            | VDDB       | 70            | SIN+6    | 110           | EXTOUTDATA9_6 | 150           | EXTINDATA10_7  | 190           | VDDA         |

| 31            | SOUT-2     | 71            | SIN-6    | 111           | EXTOUTDATA9_7 | 151           | EXTINDATA10_8  | 191           | STATMUXOUT3  |

| 32            | SOUT+2     | 72            | VSSB     | 112           | EXTOUTDATA9_8 | 152           | EXTINFULL10    | 192           | STATMUXOUT4  |

| 33            | DOUT-2     | 73            | VDDB     | 113           | EXTOUTEMPTY9  | 153           | EXTINWRITE10   | 193           | STATMUXOUT5  |

| 34            | DOUT+2     | 74            | SOUT-6   | 114           | EXTOUTREAD9   | 154           | VSSA           | 194           | STATMUXOUT6  |

| 35            | DIN+3      | 75            | SOUT+6   | 115           | EXTINDATA9_0  | 155           | VDDA           | 195           | STATMUXOUT7  |

| 36            | DIN-3      | 76            | DOUT-6   | 116           | EXTINDATA9_1  | 156           | VSSB           | 196           | VSSB         |

| 37            | SIN+3      | 77            | DOUT+6   | 117           | EXTINDATA9_2  | 157           | VDDB           |               |              |

| 38            | SIN-3      | 78            | DIN+7    | 118           | EXTINDATA9_3  | 158           | EXTTICKIN      |               |              |

| 39            | SOUT-3     | 79            | DIN-7    | 119           | EXTINDATA9_4  | 159           | EXTTIMEIN0     |               |              |

| 40            | SOUT+3     | 80            | SIN+7    | 120           | EXTINDATA9_5  | 160           | EXTTIMEIN1     |               |              |

## 3. Pin Description

Table 2. Pin description

| Signal Name <sup>(1)(3)</sup> | Type <sup>(2)</sup> | Function                                                                                                                                 | Buffer type |

|-------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| VDDA<br>VDDB<br>VDDPLL        |                     | 3.3V Power for the device                                                                                                                | POWER       |

| VSSA<br>VSSB<br>VSSPLL        |                     | Ground for the device                                                                                                                    | POWER       |

| LVDSRef                       |                     | LVDS Power reference for the device                                                                                                      | POWER       |

| VCOBias                       |                     | Bias for the PLL VCO (Rvco)                                                                                                              |             |

| LoopFilter                    |                     | Internal PLL filter                                                                                                                      |             |

| CLK                           | I                   | System Clock - Provides the reference clock for all the AT7910E modules except the SpaceWire interface receivers                         | CMOS3V3     |

| RST                           | ı                   | Asynchronous active low system reset                                                                                                     | CMOS3V3     |

| FEEDBDIV[2:0]                 | ı                   | PLL feedback divider configuration - Set the internal PLL output clock rate                                                              | CMOS3V3     |

| DOUT+[1:8]<br>DOUT-[1:8]      | 0                   | Differential output pair - Data part of Data-Strobe SpaceWire link 1 to 8.                                                               | LVDS+ LVDS- |

| SOUT+[1:8]<br>SOUT-[1:8]      | 0                   | Differential output pair - Strobe part of Data-Strobe SpaceWire link 1 to 8.                                                             | LVDS+ LVDS- |

| DIN+[1:8]<br>DIN-[1:8]        | ı                   | Differential input pair - Data part of Data-Strobe SpaceWire link 1 to 8.                                                                | LVDS+ LVDS- |

| SIN+[1:8]<br>SIN-[1:8]        | ı                   | Differential input pair - Strobe part of Data-Strobe SpaceWire link 1 to 8.                                                              | LVDS+ LVDS- |

| EXTOUTDATA9[8:0]              | 0                   | Output data from external port zero FIFO. Bit eight determines the data type data, EOP or EEP                                            | CMOS3V3     |

| EXTINDATA9[8:0]               | 1                   | Input data from external port zero FIFO. Bit eight determines the data type data, EOP or EEP                                             | CMOS3V3     |

| EXTOUTEMPTY9                  | o                   | FIFO ready signal for external output port zero. When high the FIFO has data. When low the FIFO is empty                                 | CMOS3V3     |

| EXTOUTREAD9                   | ı                   | Asserted Low to read from the external output port zero FIFO.                                                                            | CMOS3V3     |

| EXTINFULL9                    | o                   | FIFO ready signal for external input port zero. When high there is space in the FIFO so it can be written to. When low the FIFO is full. | CMOS3V3     |

| EXTINWRITE9                   | ı                   | Asserted Low to write to the external input port zero FIFO.                                                                              | CMOS3V3     |

| EXTOUTDATA10[8:0]             | o                   | Output data from external port one FIFO. Bit eight determines the data type data, EOP or EEP                                             | CMOS3V3     |

| EXTINDATA10[8:0]              | ı                   | Input data from external port one FIFO. Bit eight determines the data type data, EOP or EEP                                              | CMOS3V3     |

| EXTOUTEMPTY10                 | o                   | FIFO ready signal for external output port one. When high the FIFO has data. When low the FIFO is empty                                  | CMOS3V3     |

| Signal Name <sup>(1)(3)</sup> | Type <sup>(2)</sup> | Function                                                                                                                                                                                                                                       | Buffer type |

|-------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| EXTOUTREAD10                  | I                   | Asserted Low to read from the external output port one FIFO.                                                                                                                                                                                   | CMOS3V3     |

| EXTINFULL10                   | 0                   | FIFO ready signal for external input port one. When high there is space in the FIFO so it can be written to. When low the FIFO is full.                                                                                                        | CMOS3V3     |

| EXTINWRITE10                  | I                   | Asserted Low to write to the external input port one FIFO.                                                                                                                                                                                     | CMOS3V3     |

|                               |                     |                                                                                                                                                                                                                                                |             |

| EXTTICKIN                     | 1                   | The rising edge of the EXT_TICK_IN signal is used to indicate when a time-code is to be sent                                                                                                                                                   | CMOS3V3     |

| EXTTIMEIN[7:0]                | ı                   | EXT_TIME_IN(7:0) provides the value of the time-code to be distributed by the router                                                                                                                                                           | CMOS3V3     |

| SELEXTTIME                    | ı                   | If SEL_EXT_TIME is high on the rising edge of EXT_TICK_IN the value on EXT_TIME_IN(7:0) is loaded into the internal time-code register and propagated by the router.                                                                           | CMOS3V3     |

| TIMECTRRST                    | I                   | This signal causes the internal time-code counter to be reset to zero.                                                                                                                                                                         | CMOS3V3     |

| EXTTICKOUT                    | 0                   | The falling edge of EXT_TICK_OUT is used to indicated the reception of a time-code.                                                                                                                                                            | CMOS3V3     |

| EXTTIMEOUT[7:0]               | 0                   | Received time-code value which is valid when EXT_TICK_OUT is asserted.                                                                                                                                                                         | CMOS3V3     |

| STATMUXADDR[3:0]              | ı                   | Select the error indication status signals to be output on STAT_MUX_OUT                                                                                                                                                                        | CMOS3V3     |

| STATMUXOUT[7:0]               | I/O                 | After reset the STAT_MUX_OUT pins are inputs which define the power on configuration status of the router.  After the power on reset configuration of the router has been read from STAT_MUX_OUT the pins are driven as outputs by the router. | CMOS3V3     |

| TESTEN                        | 1                   | Shall be tied to ground                                                                                                                                                                                                                        | CMOS3V3     |

| TESTIOEN                      | ı                   | Shall be tied to ground                                                                                                                                                                                                                        | CMOS3V3     |

- Notes: 1. Groups of pins represent busses where the highest number is the MSB.

- 2. O = Output; I = Input; I/O = Input/Output

- 3.  $\overline{XXX}$  = active low signal

#### 4. Interfaces

The AT7910E provides a routing capability between eight SpaceWire links according to the SpaceWire Standard ECSS-E-50-12A. In addition for use as a node interface, the AT7910E integrates other interfaces such as:

- External ports

- Configuration port

- Time-code interface

- Control/Status interface

### 4.1 Spacewire ports

The SpaceWire router has eight bi-directional SpaceWire links each compliant with the SpaceWire standard ECSS-E-50-12A.

Each SpaceWire link is controlled by an associated link register and routing control logic. Network level error recovery is performed when an error is detected on the SpaceWire link as defined in the SpaceWire standard. Packets received on SpaceWire links are routed by the routing control logic to the configuration port, other SpaceWire link ports or the external FIFO ports.

Packets with invalid addresses are discarded by the SpaceWire router dependent on the packet address. The SpaceWire link status is recorded in the associated link register and error status is held by the router until cleared by a configuration command.

#### 4.2 External ports

The SpaceWire router has two bi-directional parallel FIFO interfaces to an external host system. Each FIFO is written to or read from synchronously to the 30MHz system clock. An eight-bit data interface and an extra control bit for end of packet markers are provided by each external port FIFO.

Packets received by the external port are routed by the routing control logic to the configuration port, SpaceWire link ports or the other external port dependent on the packet address.

Packets with invalid addresses are discarded by the SpaceWire router.

#### 4.3 Configuration port

The SpaceWire router has one configuration port which performs read and write operations to internal router registers. Packets are routed to the configuration port when a packet with a leading address byte of zero is received.

The SpaceWire Router supports the Remote Memory Access Protocol (RMAP) as command packet format.

If an invalid command packet is received then the error is flagged to the associated status register and the packet is discarded.

#### 4.4 Time-code interface

An internal time-code register is used in the router to allow the router to be a time-code master or a time-code slave.

In master mode the time-code interface is used to provide a tick-in to the SpaceWire routing causing time-codes to be propagated through the network. Two modes of time master operation are supported, an automatic mode where a time-code is propagated on each external tick-in and a normal mode where the time-code is propagated dependent on the external time-in signal.

In time-code slave mode a valid received time-code, one plus the value of the router time-code register, causes a tick-out to be sent to the SpaceWire links and the external time-code interface. The time-code is propagated to all time-code ports except the port on which the time-code was received. If the time-code received is not one plus the value of the time-code register then the time-code register is updated but the tick-out is not performed. In this way, circular network paths do not cause a constant stream of time-codes to be sent in a loop.

#### 4.5 Control/Status interface

The control and status registers in the SpaceWire router provide the means to control the operation of the router, set the router configuration and parameters or monitor the status of the device. The registers are accessed using RMAP commands packets received by the configuration port.

## 5. Typical Applications

The AT7910E SpaceWire router is perfectly suited for development of applications requiring a standalone router, a terminal node with SpaceWire interface or a mixed configuration of the two previous ones.

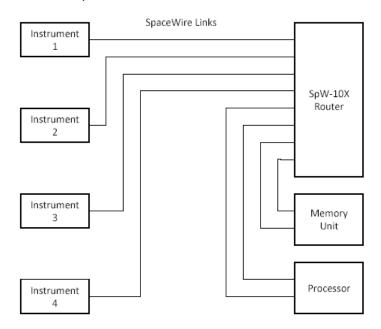

#### 5.1 Stand-alone router

The AT7910E SpaceWire Router may be used as a stand-alone router with up to eight SpaceWire links connected to it. Configuration of the routing tables etc. may be done by sending SpaceWire packets containing configuration commands to the router.

Figure 5-1. AT7910E as SpaceWire router

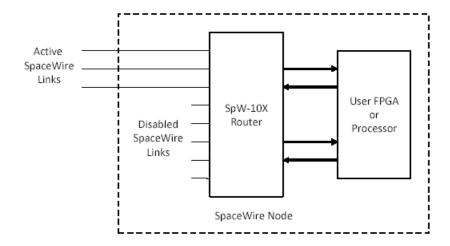

#### 5.2 Node interface

The SpaceWire Router has two external ports which enable the device to be used as a node interface. The equipment to be connected to the SpaceWire network is attached to one or both external ports. One or more SpaceWire ports are used to provide the connection into the SpaceWire network. Unused SpaceWire ports may be disabled and their outputs tri-stated to save power. In this arrangement configuration of the routing tables and other parameters may be done by sending configuration packets from the local host via an external port or from a remote network manager via a SpaceWire port.

Figure 5-2. AT7910E as SpaceWire node interface

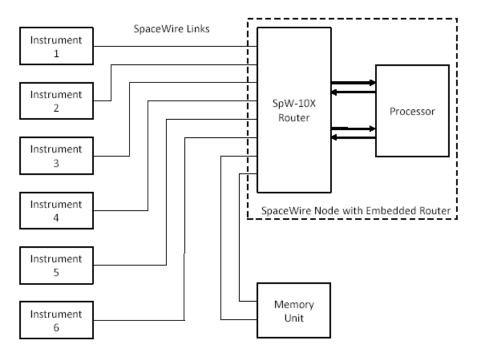

#### 5.3 Embedded router

The SpaceWire Router device can also be used to provide a node with an embedded router. In this case the external ports are used to provide the local connections to the node and the SpaceWire ports are used to make connections to other ports in the network.

Figure 5-3. AT7910E as Embedded Router

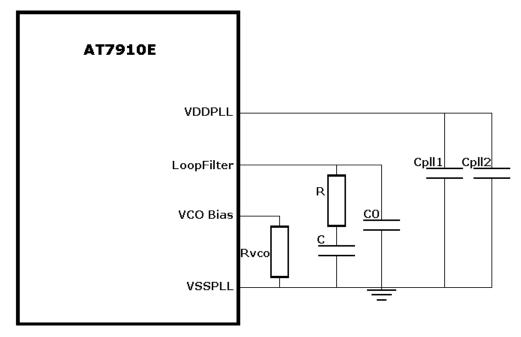

#### 6. PLL Filter

The AT7910E uses an internal PLL to provide the base transmit clock signal for the SpaceWire interfaces. External components are required to implement the PLL loop filter and to provide a bias for the PLL VCO.

Note that RVCO, C and C0 are all connected to a quiet common ground track.

Dedicated decoupling capacitors are also required for the PLL power supply.

Figure 6-1. PLL filter and decoupling capacitors

Table 6-1.

PLL filter recommended components

| R    | 10kΩ ± 5%, ¼W                          |

|------|----------------------------------------|

| С    | 120pF, ± 5%                            |

| C0   | 3.3pF, ± 5%                            |

| RVCO | 4.7k $\Omega$ for 100-150MHz operation |

|      | 1.8k $\Omega$ for 150-200MHz operation |

Table 6-2.

PLL decoupling capacitors

| Cpll1 | 100nF, ± 5% |  |

|-------|-------------|--|

| Cpll2 | 1μF, ± 5%   |  |

#### 7. Electrical Characteristics

### 7.1 Absolute Maximum Ratings

Table 7-1. Absolute Maximum Ratings

| Parameter                                | Symbol | Value             | Unit |

|------------------------------------------|--------|-------------------|------|

| Supply Voltage                           | VCC    | -0.5 to +4        | V    |

| I/O Voltage                              |        | -0.5 to VCC + 0.5 | V    |

| Operating Temperature<br>Range (Ambient) | TA     | -55 to +125       | °C   |

| Junction Temperature                     | TJ     | 175               | °C   |

| Storage Temperature<br>Range             | Tstg   | -65 to +150       | °C   |

| Thermal resistance<br>Junction to case   | RThJC  | 5                 | °C/W |

Stresses above those listed may cause permanent damage to the device.

#### 7.2 DC Electrical Characteristics

Table 7-2.

3.3V operating range DC Characteristics

| Parameter                    | Symbol | Min. | Max. | Unit | Conditions                        |

|------------------------------|--------|------|------|------|-----------------------------------|

| Operating Voltage            | VCC    | 3.0  | 3.6  | V    |                                   |

| Input HIGH Voltage           | VIH    | 2.0  |      | V    |                                   |

| Input LOW Voltage            | VIL    |      | 0.8  | V    |                                   |

| Output HIGH Voltage          | VOH    | 2.4  |      | V    | IOL = 3, 6, 12mA / VCC = VCC(min) |

| Output LOW Voltage           | VOL    |      | 0.4  | V    | IOH = 3, 6, 12mA / VCC = VCC(min) |

| Output Short circuit current | IOS    |      | 23   | mA   | VOUT = VCC                        |

|                              |        |      | 13   | mA   | VOUT = GND                        |

|                              |        |      |      |      |                                   |

### 7.3 Power consumption

Maximum power consumption figures at Vcc = 3.6V are presented in the following table.

Table 7-3.3.3V Power Consumption

| Operation Mode                                  | Power consumption [W] <sup>2</sup> |

|-------------------------------------------------|------------------------------------|

| ICCSB - Standby                                 | 1.3 - TBC                          |

| ICCOP <sup>1</sup> - 200Mb/s on SpaceWire links | 3.8 - TBC                          |

| ICCOP <sup>1</sup> - 100Mb/s on SpaceWire links | 1.9 - TBC                          |

| ICCOP <sup>1</sup> - 10Mb/s on SpaceWire links  | 0.9 - TBC                          |

Notes: 1. Dynamic power with all interfaces active including external ports.

If a SpW IF is not active (switched off) assume a reduction of the static and dynamic power by 5%.

## 7.4 AC Electrical Characteristics

The following table gives the worst case timings measured by Atmel on the 3.0 V to 3.6 V operating range

**Table 7-4.** 3.3V operating range timings<sup>(1)</sup>

| Parameter                               | Symbol | Min. | Max. | Unit |

|-----------------------------------------|--------|------|------|------|

| Propagation delay CLK Low to DOUT0 High | Tp0    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT1 High | Tp1    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT2 High | Tp2    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT3 High | Тр3    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT4 High | Tp4    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT5 High | Tp5    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT6 High | Tp6    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT7 High | Tp7    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT0 Low  | Tp8    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT1 Low  | Тр9    |      | 16   | ns   |

| Propagation delay CLK Low to DOUT2 Low  | Tp10   |      | 16   | ns   |

| Propagation delay CLK Low to DOUT3 Low  | Tp11   |      | 16   | ns   |

| Propagation delay CLK Low to DOUT4 Low  | Tp12   |      | 16   | ns   |

| Propagation delay CLK Low to DOUT5 Low  | Tp13   |      | 16   | ns   |

| Propagation delay CLK Low to DOUT6 Low  | Tp14   |      | 16   | ns   |

| Propagation delay CLK Low to DOUT7 Low  | Tp15   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT0 High | Tp16   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT1 High | Tp17   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT2 High | Tp18   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT3 High | Tp19   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT4 High | Tp20   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT5 High | Tp21   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT6 High | Tp22   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT7 High | Tp23   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT0 Low  | Tp24   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT1 Low  | Tp25   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT2 Low  | Tp26   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT3 Low  | Tp27   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT4 Low  | Tp28   |      | 16   | ns   |

| Parameter                              | Symbol | Min. | Max. | Unit |

|----------------------------------------|--------|------|------|------|

| Propagation delay CLK Low to SOUT5 Low | Tp29   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT6 Low | Tp30   |      | 16   | ns   |

| Propagation delay CLK Low to SOUT7 Low | Tp31   |      | 16   | ns   |

Note:

1. The timing parameters presented in the above table are measured under production configuration (PLL bypassed and test mode enabled). During normal operation (PLL active and test mode disabled) the propagation delay is directly linked to the PLL. Then, the timing figures are not applicable under application conditions.

For guaranteed timings refer to the "Switching Characteristics" section of the 'SpW-10X SpaceWire Router User Manual'.

## 8. Package Drawings

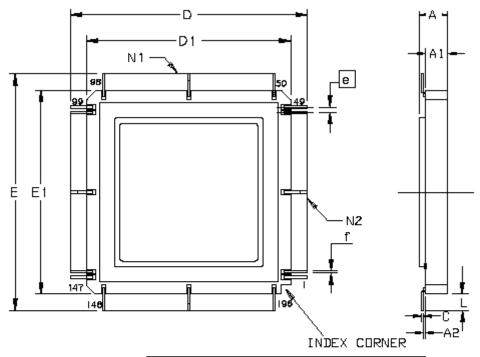

### 8.1 MQFPF196

Here is a presentation of the mechanical outline of the 196 pins Ceramic Quad Flat Pack (CQFP 196) package used for the AT7910E.

Figure 8-1. MQFPF 196 package

|       | Min    | Мах            | Min       | Мах    |

|-------|--------|----------------|-----------|--------|

| Α     | 2. 13  | 2. 65          | . 084     | . 104  |

| A1    | 1. 83  | 2. 24          | . 072     | . 088  |

| A2    | 0. 20  | 3 REF          | . 008     | REF    |

| С     | 0. 102 | 0. 203         | . 004     | . 008  |

| D/E   | 46. 73 | 47. <b>9</b> 4 | 1. 640    | 1. 867 |

| D1/E1 | 34. 03 | 34. 54         | 1. 340    | 1. 360 |

| P     | 0. 63  | 5 BSC          | . 025 RSC |        |

| £.    | 0. 20  | REF            | . 008     | REF    |

| L     | 6. 35  | 6. 70          | . 250     | . 264  |

| N1    | 4      | 9              | 4         | 9      |

| N2    | 4      | 9              | 4         | 9      |

Lid connected to ground

## 9. Ordering Information

| Part-number  | Temperature Range | Package  | Quality Flow       |

|--------------|-------------------|----------|--------------------|

| AT7910EKB-E  | 25°C              | MQFPF196 | Engineering sample |

| AT7910EKB-MQ | -55°C to +125°C   | MQFPF196 | Mil Level B (*)    |

| AT7910EKB-SV | -55°C to +125°C   | MQFPF196 | Space Level B (*)  |

<sup>(\*)</sup> according to Atmel Quality flow document 4288, see Atmel web site.

## 10. Document Revision History

#### 10.1 7796 Rev. B.

1. Corrected pinout error: pin 190 is VDDA and not VSSB. See Table 1 on page 6.

#### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com

**Technical Support** aero@nto.atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.