# **New ASIC Solution Platform ISSP**<sup>™</sup>

ISSP1-STD Series ISSP1-HSI Series

# **ISSP1 Series ISSP90 Series**

ISSP90-STD Series New product ISSP90-HSI Series Preliminary

<A New Platform Never Seen Before> - High-performance LSIs realized quickly, easily, and at low cost -

# **ISSP**

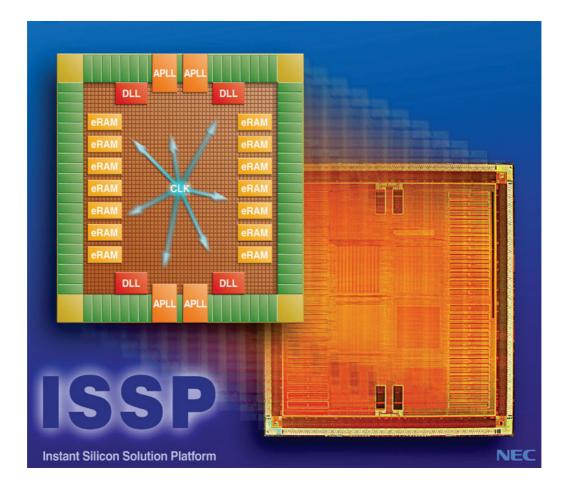

ISSP (Instant Silicon Solution Platform) is a new ASIC platform device that helps you create high-performance LSIs quickly, easily, and at low cost.

As a designer today, you face shorter deadlines for designing LSI products than ever before.

ISSP offers you a risk management solution that enables fast time to market and lower total costs. This solution helps NEC Electronics satisfy needs that could not be satisfied by conventional ASIC products and FPGA.

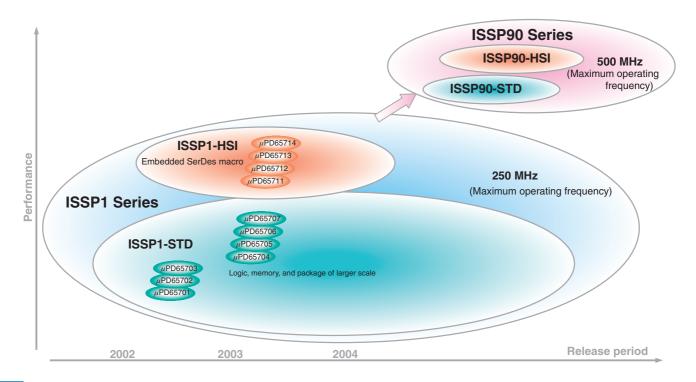

### **ISSP Lineup**

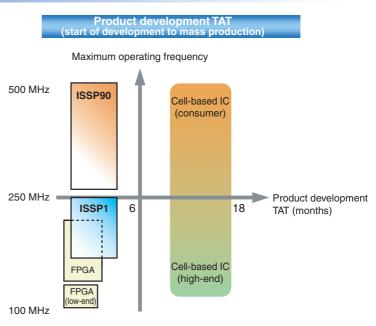

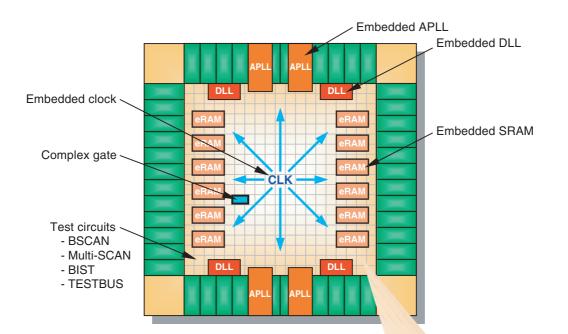

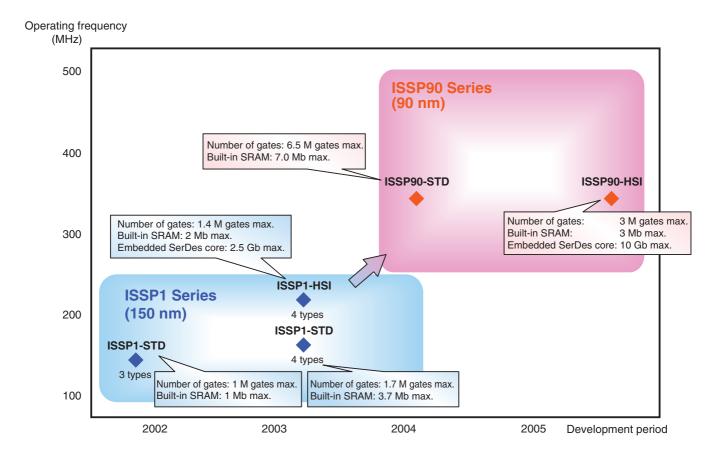

The ISSP1-STD Series, NEC Electronics' first-generation ISSP, is a standard type platform that integrates large-scale SRAM, and APLL and DLL circuits. The ISSP1-STD Series realizes an operating frequency of up to 250 MHz by employing 5-layer AL routing technology using a 0.15  $\mu$ m CMOS process. The main applications of this ISSP include high-speed and high-capacity (broadband) communications or network equipment, computer peripheral equipment, high-performance measuring instruments, and consumer electronic systems.

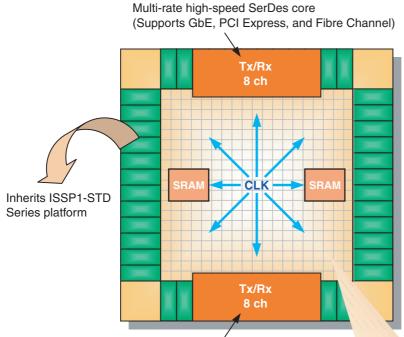

The ISSP1-HSI Series is a high-speed interface core version of the first-generation ISSP. It supports high-speed interfaces including PCI Express, Gigabit Ethernet, and Fibre Channel, by embedding a high-performance 2.5 Gbps SerDes (Serializer/ Deserializer). In addition, IP cores necessary for communications and networks such as SPI4.2 (Dynamic), 10/100M Ethernet MAC, 1G Ethernet MAC, POS PHY Level 3, and UTOPIA are available as firmware macros, providing the ideal solution for high-speed, high-capacity (broadband) communications, network equipment, and server equipment.

The ISSP90 Series, NEC Electronics' second-generation ISSP, employs a state-of-the-art 90 nm CMOS process. The internal operating frequency of this series is as high as 500 MHz. In addition, the number of user gates is to 6.5 million gates, four times the number of the first generation, and the SRAM capacity has been increased three-fold to 11.5 Mb. An embedded SerDes core with a data transmission rate of up to 10 Gbps is also available, as are the IP cores already provided with the ISSP1 Series. This core can realize a serial interface standard of up to10 Gb and a Serial ATA high-speed interface of 3 Gb. A 10 Gbps Ethernet MAC is also available.

### Features of ISSP

- (1) Can realize high-performance system LSIs at lower cost than conventional ASIC/FPGA

- (2) Substantially easier design through employment of new architecture

- (3) Many IP cores and high-speed interfaces available

- (4) High-mix low volume production possible in a short time.

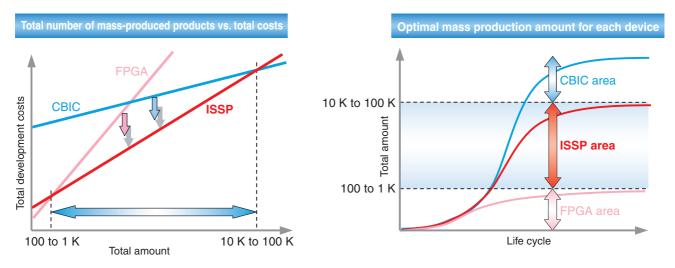

### Low Development Risk

Progress in ASIC process technology has accelerated in recent years and ASICs with improved performance and functionality are now widely available to satisfy an ever diverse range of demands. In the meantime, however, new problems have arisen. For example, an increase in the number of process steps means a larger number of masks are required. This leads directly to higher development costs. Test design, clock design, and signal integrity problems also lengthen the development period, further raising the development costs, and the risk to the developer. In the development stage of a new product, an increase in initial costs makes it difficult to estimate payback of investment, placing heavy pressure on the developer's cash flow. In some cases, mass production does not justify the investment.

ISSP can reduce such investment risks by supplying high-performance system LSIs at an initial cost equivalent to that of gate arrays.

Total development costs = Labor costs + NRE + Total amount x Unit price

### Short Development Period

The main causes that extend the development period of conventional ASICs are problems of test design and mutual interference of signals (signal integrity) resulting from increased miniaturization. FPGAs, on the other hand, require a long time to verify circuits if high-speed circuits exceeding 100 MHz are to be designed. If the cell utilization rate is high, the design convergence degrades and, in the worst case, the specifications must be reviewed.

With ISSP, the user can concentrate on designing circuits without having to be aware of test design because a test circuit is embedded in advance in the base wafer. In addition, the design period can be shortened due to the employment of a leading-edge process and an embedded clock tree, which increase the performance, and by a new cell structure that counters signal integrity.

# **ISSP**

## IP Core Lineup

|                               |                       |              | ISSP1        |              | ISSP90       |              |  |

|-------------------------------|-----------------------|--------------|--------------|--------------|--------------|--------------|--|

|                               | 1                     | STD S        | Series       | HSI          | STD          | HSI          |  |

|                               | Macro                 | μ PD65701 to | μ PD65704 to | Series       | Series       | Series       |  |

|                               |                       | μ PD65703    | μ PD65707    |              |              |              |  |

| DDR Controller                | 133 MHz, 64 bit       | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| 10/100 M Ethernet             | MAC                   | $\sqrt{}$    | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| 10/100/1000 M                 | MAC (Triple)          | $\sqrt{}$    | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| Ethernet MAC                  | TBI (125 MHz, 10 bit) | $\sqrt{}$    | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| 10 G Ethernet MA              | C                     | -            | -            | -            | -            | $\checkmark$ |  |

| SPI4.2                        | Static                | $\sqrt{}$    | -            | $\checkmark$ | -            | -            |  |

|                               | Dynamic               | -            | $\sqrt{}$    | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| POS PHY/UTOPIA                | Level 3               | $\sqrt{}$    | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| PCI-X                         | I/O only              | -            | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| SerDes                        | Up to 2.5 G bps       | -            | -            | $\sqrt{}$    | -            | $\checkmark$ |  |

|                               | Up to 10 G bps        | -            | -            | -            | -            | $\checkmark$ |  |

| PCI Controller 66 MHz, 32 bit |                       | $\sqrt{}$    | $\sqrt{}$    | $\sqrt{}$    | $\checkmark$ | $\checkmark$ |  |

| PCI Express                   | PCS                   | -            | -            | $\sqrt{}$    | -            | $\checkmark$ |  |

| XAUI                          | PCS                   | -            | -            | _            | -            | $\checkmark$ |  |

| Fibre Channel                 | PCS                   | -            | _            |              | -            | $\checkmark$ |  |

$\sqrt[n]{}$  : Supported  $\sqrt{}$  : To be supported - : Not supported

## Embedded APLL/DLL

| ٠ | APLL   |                  |                                                                                              |

|---|--------|------------------|----------------------------------------------------------------------------------------------|

|   | High-s | peed version:    | Functions: Clock skew control function, clock multiplication function, phase shift function, |

|   |        |                  | DDR interface                                                                                |

|   |        |                  | Input frequency: 25 MHz to 400 MHz                                                           |

|   |        |                  | Output frequency: 25 MHz to 800 MHz                                                          |

|   | Mediu  | m-speed version: | Functions: Clock skew control function, clock multiplication function                        |

|   |        |                  | Input frequency: 12.5 MHz to 400 MHz                                                         |

|   |        |                  | Output frequency: 12.5 MHz to 400 MHz                                                        |

| ٠ | DDL    | Functions:       | DDR interface                                                                                |

|   |        |                  |                                                                                              |

Input frequency: 100 MHz to 175 MHz Output frequency: 100 MHz to 175 MHz

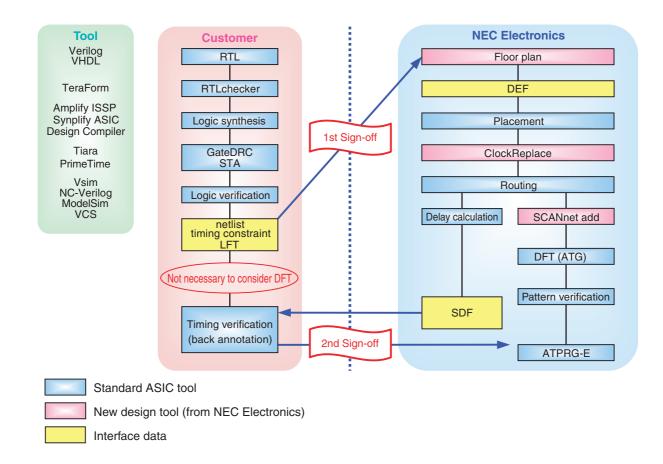

### **ISSP (Tool Environment)**

| Function            | Тс                    | bol                                            |

|---------------------|-----------------------|------------------------------------------------|

| Function            | NEC Electronics       | Third party                                    |

| Framework           | OPENCAD™ ISSP         | _                                              |

| RTL check           | -                     | Teraform®                                      |

| Schematic editor    | Vdraw                 | -                                              |

| Synthesis           | -                     | Design Compiler, Synplify® ASIC, Amplify® ASIC |

| Physical synthesis  | _                     | Amplify ISSP                                   |

| Wave editor         | Wave Editor           | -                                              |

| Logic verification  | V.sim                 | ModelSim, NC-Verilog, VCS                      |

| STA                 | Tiara                 | PrimeTime                                      |

| Design rule check   | GateDRC, STADRC       | _                                              |

| Formal verification | Zero                  | Conformal-LEC, Formality                       |

| Floor plan          | Galet, Ace-Floor Plan | Amplify ISSP, SoC ENCOUNTER                    |

| Place & route       | Galet, Y-Place        | Amplify ISSP, SoC ENCOUNTER                    |

### **ISSP (Development Flow)**

### **Product Overview**

The ISSP1-STD Series includes large-scale SRAM and APLL and DLL circuits, and employs 5-layer AL routing technology using a 0.15  $\mu$ m CMOS process, realizing an operation speed of up to 250 MHz.

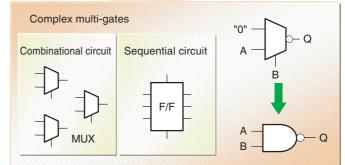

A newly developed complex gate structure is employed for the cells. The lower three routing layers are embedded in advance in the base wafer as complex gate routing, core connection routing, test circuit routing, clock tree routing, and power routing. As a result, the user does not have to consider test design and can concentrate on designing circuits. This results in a substantially shorter design period. In addition, the development costs can also be reduced because the user can customize the circuit by using just the higher two routing layers.

The main applications of the ISSP1-STD Series include high-speed, high-capacity (broadband) communications and network systems, computer peripheral equipment, high-performance measuring instruments, and consumer electronic equipment.

### Chip Image of ISSP1-STD Series

| Individual mask | Layer 5 (M5) | Circuit routing for                                                           |  |

|-----------------|--------------|-------------------------------------------------------------------------------|--|

| Î               | Layer 4 (M4) | E had a start when                                                            |  |

|                 | Layer 3 (M3) | Power supply,                                                                 |  |

| Shared mask     | Layer 2 (M2) | <ul> <li>new cell connection routin<br/>test routing, clock domain</li> </ul> |  |

|                 | Layer 1 (M1) | test routing, clock domain                                                    |  |

# **ISSP1-STD Series**

### Master Lineup

| Master   | Number of            | SRAM Size | SR   | AM  | AP                    | 'LL                     | DLL | Package                    |

|----------|----------------------|-----------|------|-----|-----------------------|-------------------------|-----|----------------------------|

| Master   | Usable ISSP<br>Gates | (Bits)    | 16 K | 4 K | High-speed<br>version | Medium-speed<br>version | DEL | i dokuge                   |

| μPD65701 | 214 K                | 262 K     | 16   | 0   | 3                     | 1                       | 8   | TBGA: 532/420 pins         |

| μPD65702 | 407 K                | 786 K     | 48   | 0   | 3                     | 1                       | 8   | TBGA: 420/500/576/680 pins |

| μPD65703 | 941 K                | 1 M       | 64   | 0   | 3                     | 1                       | 16  | TBGA: 500/576/680/768 pins |

| μPD65704 | 1 M                  | 3.7 M     | 216  | 32  | 4                     | 0                       | 32  | ABGA: 500/756/888 pins     |

| μPD65705 | 1.7 M                | 2.2 M     | 128  | 32  | 4                     | 0                       | 32  |                            |

| μPD65706 | 1 M                  | 3.7 M     | 216  | 32  | 4                     | 0                       | 32  | FCBGA: 1155/1521Note pins  |

| μPD65707 | 1.7 M                | 2.2 M     | 128  | 32  | 4                     | 0                       | 32  |                            |

Note Under development

### Specifications

| lte                   | em                    | Specification                                                                                  |  |  |  |  |

|-----------------------|-----------------------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Process               |                       | 0.15 µm process, Si gate CMOS, 2-layer customized routing                                      |  |  |  |  |

| Maximum number        | of usable gates       | 1.7 M gates (number of usable ISSP gates)                                                      |  |  |  |  |

|                       |                       | 3.7 Mb (RAM capacity)                                                                          |  |  |  |  |

| Package               | TBGA                  | 352/420/500/576/768 pins                                                                       |  |  |  |  |

|                       | ABGA                  | 500/756/888 pins                                                                               |  |  |  |  |

|                       | FCBGA                 | 1155/1521 pins                                                                                 |  |  |  |  |

| Supply voltage        | I/O block             | Conforms to 3.3 V, 2.5 V, and other high-speed interface standards                             |  |  |  |  |

|                       | Internal block        | 1.5 V                                                                                          |  |  |  |  |

| Power consumption     | Combinational circuit | 0.0267 µW/MHz/gate                                                                             |  |  |  |  |

| (internal gates)      | Sequential circuit    | 0.0215 $\mu$ W/MHz/gate (data line cycle/clock line cycle = 4)                                 |  |  |  |  |

| Maximum operating fre | quency (system clock) | 250 MHz (166 MHz) (Maximum operating frequency differs depending on the circuit configuration) |  |  |  |  |

| Interface level       |                       | 3.3 V/2.5 V LVTTL                                                                              |  |  |  |  |

|                       |                       | 3.3 V PCI, PCI-X                                                                               |  |  |  |  |

|                       |                       | LVDS, HSTL, SSTL, PECL, etc.                                                                   |  |  |  |  |

| Embedded macro        | SRAM                  | 1- or 2-port compiled synchronous                                                              |  |  |  |  |

|                       | APLL                  | High-speed type, medium-speed type                                                             |  |  |  |  |

|                       | DLL                   | For high-speed SDRAM interface                                                                 |  |  |  |  |

| Other macros          |                       | SRAM: Distributed compiled synchronous SRAM                                                    |  |  |  |  |

|                       |                       | SPI4.2 (Dynamic), 10/100/1000 M Ethernet MAC, 10/100 M Ethernet MAC,                           |  |  |  |  |

|                       |                       | POS PHY Level 3, UTOPIA, DDR controller, PCI controller                                        |  |  |  |  |

| Embedded clock        |                       | Global clock: 2 lines                                                                          |  |  |  |  |

|                       |                       | Local clock: 2 to 32 lines                                                                     |  |  |  |  |

| Embedded test-rela    | ated                  | Scan path test, boundary scan, BIST, test bus                                                  |  |  |  |  |

# **ISSP1-HSI Series**

### **Product Overview**

The ISSP1-HSI Series supports high-speed interfaces including PCI Express, Gigabit Ethernet (GbE), and Fibre Channel, by embedding up to 16 high-performance 2.5 Gbps SerDes (Serializer/Deserializer) cores, as well as the functions of the ISSP1-STD Series.

In addition, IP cores necessary for communications and networks such as SPI4.2 (Dynamic), 10/100 M Ethernet MAC, 1 G Ethernet MAC, POS PHY Level 3, and UTOPIA are available as firmware macros, providing an ideal solution for high-speed, high-capacity (broadband) communications and network equipment and server equipment. The same high-performance 0.15  $\mu$ m CMOS process as the existing ISSP1-STD Series is used. Circuits can also be customized by using just two routing layers. Test circuits and clock tree routing are prepared in advance. Therefore, the design and production periods can be dramatically shortened and development costs reduced.

Multi-rate high-speed SerDes core

| Individual mask | Layer 5 (M5) | Circuit routing for             |  |  |

|-----------------|--------------|---------------------------------|--|--|

| Î               | Layer 4 (M4) | customization                   |  |  |

| Ţ               | Layer 3 (M3) | Power supply                    |  |  |

| Shared mask     | Layer 2 (M2) | New cell connection and routing |  |  |

|                 | Layer 1 (M1) | Clock domain                    |  |  |

|                 |              |                                 |  |  |

# **ISSP1-HSI Series**

# Master Lineup

| Master                 | Number of<br>Usable<br>ISSP Gates | SRAM Size<br>(Bits) | 16 K | SRAM<br>4 K | 1<br>128 | APPL<br>(High-Speed<br>Version) | DLL | Number of<br>SerDes<br>Channels | Package                |

|------------------------|-----------------------------------|---------------------|------|-------------|----------|---------------------------------|-----|---------------------------------|------------------------|

| <mark>µ</mark> РD65711 | 695 K                             | 729 K               | 42   | 0           | 32       | 4                               | 8   | 8                               | ABGA: 576/756 pins     |

| <mark>μPD657</mark> 12 | 1 M                               | 1 M                 | 56   | 0           | 64       | 4                               | 16  | 16                              | ABGA: 576/756/888 pins |

| <mark>μPD657</mark> 13 | 1.4 M                             | 2 M                 | 112  | 20          | 64       | 4                               | 32  | 16                              | ABGA: 756/888 pins     |

| <mark>μPD657</mark> 14 | 1.4 M                             | 2 M                 | 112  | 20          | 64       | 4                               | 32  | 16                              | FCBGA: 1155 pins       |

## Specifications

| lte                   | em                     | Specification                                                                              |  |  |  |  |

|-----------------------|------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| Process               |                        | 0.15 μm process, Si gate CMOS, 2 layer customized routing                                  |  |  |  |  |

| Maximum number o      | of usable gates        | 1.4 M gates (number of usable ISSP gates)                                                  |  |  |  |  |

|                       |                        | 2 Mb (RAM capacity)                                                                        |  |  |  |  |

| Package               | ABGA                   | 576/756/888 pins                                                                           |  |  |  |  |

|                       | FCBGA                  | 1155 pins                                                                                  |  |  |  |  |

| Supply voltage        | I/O block              | Conforms to 3.3 V, 2.5 V, and other high-speed interface standards                         |  |  |  |  |

|                       | Internal block         | 1.5 V                                                                                      |  |  |  |  |

| Power consumption     | Combinational circuit  | 0.0267 µW/MHz/gate                                                                         |  |  |  |  |

| (internal gate)       | Sequential circuit     | 0.0215 $\mu$ W/MHz/gate (data line cycle/clock line cycle = 4)                             |  |  |  |  |

| Maximum operating fre | equency (system clock) | 250 MHz (166 MHz) (Maximum operating frequency differs depending on circuit configuration) |  |  |  |  |

| Interface level       |                        | 3.3 V/2.5 V LVTTL                                                                          |  |  |  |  |

|                       |                        | 3.3 V PCI, PCI-X                                                                           |  |  |  |  |

|                       |                        | LVDS, HSTL, SSTL, PECL, etc.                                                               |  |  |  |  |

| Embedded high-sp      | eed interface macro    | SerDes: Supports GbE/PCI Express/Fibre Channel                                             |  |  |  |  |

| Embedded macro        | SRAM                   | 1- or 2-port compiled synchronous type                                                     |  |  |  |  |

|                       | APLL                   | High-speed type                                                                            |  |  |  |  |

|                       | DLL                    | For high-speed SDRAM interface                                                             |  |  |  |  |

| Other macros          |                        | SPI4.2 (Dynamic), 10/100/1000 M Ethernet MAC, 10/100 M Ethernet MAC,                       |  |  |  |  |

|                       |                        | POS PHY Level 3, UTOPIA, DDR controller, PCI controller                                    |  |  |  |  |

| Embedded clock        |                        | Global clock: 2 lines                                                                      |  |  |  |  |

|                       |                        | Local clock: 2 to 32 lines                                                                 |  |  |  |  |

| Embedded test-rela    | ated                   | Scan path test, boundary scan, BIST, test bus                                              |  |  |  |  |

# **ISSP90 Series**

### **Product Overview**

The ISSP90 Series employs a leading-edge 90 nm CMOS process and features an operating frequency of 500 MHz, double that of the ISSP1 Series. In addition, the number of user gates is four times higher (6.5 million gates), and a two-fold SRAM capacity of 7.0 Mb is provided.

In addition to the IP cores available in the ISSP1 Series, the ISSP90 Series supplies a SerDes embedded core with a data transmission rate of 10 Gbps as a high-speed interface indispensable for next-generation applications such as communications, server, and storage. This core can realize a high-speed serial interface standard of 10 Gb and high-speed Serial ATA interface of 3 Gb. A 10 Gbps Ethernet MAC is also available.

### **Development of ISSP90 Series**

Remark SerDes (Serializer/Deserializer): Serial/parallel converter

# **ISSP90-STD Series**

## Master Lineup

### New product

| I/O<br>Interface | Master    | Number of<br>Usable ISSP<br>Gates | SRAM Size<br>(Bits) | I/O Lineup              | Maximum Clock <sup>Note</sup> /<br>Maximum System<br>Clock <sup>Note</sup> | Package<br>(FCBGA) |

|------------------|-----------|-----------------------------------|---------------------|-------------------------|----------------------------------------------------------------------------|--------------------|

| 3.3 V            | μPD69551  | 1.74 M                            | 1.11 M              | SSTL2 (2.5 V)           | 333 MHz/                                                                   | 729 pins           |

|                  | μPD69552  | 2.68 M                            | 1.92 M              | SSTL18 (1.8 V)          | 250 MHz                                                                    | 1155 pins          |

|                  | μPD69553  | 3.45 M                            | 2.95 M              | DDR2 (1.8 V)            | (High density version)                                                     | 1155 pins          |

|                  | μPD69554  | 4.00 M                            | 1.77 M              | HSTL18 (1.8 V)          |                                                                            | 1521 pins          |

|                  | μPD69555  | 4.67 M                            | 4.20 M              | PECL (2.5 V)            |                                                                            |                    |

|                  | μPD69556  | 5.53 M                            | 2.36 M              | LVDS (High speed:3.3 V  |                                                                            |                    |

|                  | μPD69557  | 5.40 M                            | 5.68 M              | only)                   |                                                                            | 1155 pins          |

|                  | μPD69558  | 6.50 M                            | 3.02 M              | LVDS (Middle and low    |                                                                            | 1521 pins          |

| 2.5 V            | μPD69559  | 5.23 M                            | 7.08 M              | speed:2.5 V only)       |                                                                            | 1849 pins          |

| 3.3 V            | μPD69561  | 0.87 M                            | 0.77 M              | SSTL2 (2.5 V)           | 500 MHz/                                                                   | 729 pins           |

|                  | μPD69562  | 1.34 M                            | 1.34 M              | SSTL18 (1.8 V)          | 333 MHz                                                                    | 1155 pins          |

|                  | μPD69563  | 1.73 M                            | 2.06 M              | DDR2 (1.8 V)            | (High speed version)                                                       | 1155 pins          |

|                  | μPD69564  | 2.00 M                            | 1.24 M              | HSTL18 (1.8 V)          |                                                                            | 1521 pins          |

|                  | μPD69565  | 2.34 M                            | 2.94 M              | PECL (2.5 V)            |                                                                            |                    |

|                  | μPD69566  | 2.76 M                            | 1.65 M              | LVDS (High speed: 3.3 V |                                                                            |                    |

|                  | μPD69567  | 2.70 M                            | 3.97 M              | only)                   |                                                                            | 1155 pins          |

|                  | μ PD69568 | 3.25 M                            | 2.12 M              | LVDS (Middle and low    |                                                                            | 1521 pins          |

| 2.5 V            | μ PD69569 | 2.62 M                            | 4.94 M              | speed: 2.5 V only)      |                                                                            | 1849 pins          |

Note Depends on the circuit configuration.

## Specifications

| Ite                   | em                     | Specification                                                                              |  |  |  |

|-----------------------|------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Process               |                        | 90 nm CMOS process, 7 layers (2 customized routing layers)                                 |  |  |  |

| Maximum number        | of usable gates        | 6.5 M gates (number of usable ISSP gates)                                                  |  |  |  |

|                       |                        | 7.0 Mb (RAM capacity)                                                                      |  |  |  |

| Package               | FCBGA                  | 729/1155/1521/1849 pins                                                                    |  |  |  |

| Supply voltage        | I/O block              | Conforms to 3.3 V, 2.5 V, 1.8 V, and other high-speed interface standards                  |  |  |  |

|                       | Internal block         | 1.0 V                                                                                      |  |  |  |

| Maximum operating fre | equency (system clock) | 500 MHz (333 MHz) (Maximum operating frequency differs depending on circuit configuration) |  |  |  |

| Interface level       |                        | 2.5 V LVCMOS, LVPECL 2.5 input, 3.3 V LVTTL, 2.5 V LVDS, HSTL class 1/HSTL class 3,        |  |  |  |

|                       |                        | SSTL2 class 1/SSTL2 class 2, SSTL18.                                                       |  |  |  |

| Embedded macro        | SRAM                   | 2-port compiled synchronous type                                                           |  |  |  |

|                       | APLL                   | High-speed type                                                                            |  |  |  |

| DLL                   |                        | For high-speed SDRAM interface (3.3 V master only)                                         |  |  |  |

| Other macros          |                        | SPI4.2 (Dynamic), 10 G Ethernet MAC, 10/100/1000 M Ethernet MAC,                           |  |  |  |

|                       |                        | 10/100 M Ethernet MAC, POS PHY Level 3, UTOPIA, DDR controller, PCI controller             |  |  |  |

| Embedded test-rela    | ated                   | Scan path test, boundary scan, BIST, test bus                                              |  |  |  |

# **ISSP90-HSI Series**

# Specifications

### Preliminary

| lte                   | em                     | Specification                                                                              |  |  |  |

|-----------------------|------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Process               |                        | 90 nm CMOS process, 7 layers (2 customized routing layers)                                 |  |  |  |

| Maximum number        | of usable gates        | 3 M gates (number of usable ISSP gates)                                                    |  |  |  |

|                       |                        | 3 Mb (RAM capacity)                                                                        |  |  |  |

| Package               | FCBGA                  | 729/1155/1521/1849 pins                                                                    |  |  |  |

| Supply voltage        | I/O block              | Conforms to 3.3 V, 2.5 V, 1.8 V, and other high-speed interface standards                  |  |  |  |

|                       | Internal block         | 1.0 V                                                                                      |  |  |  |

| Maximum operating fre | equency (system clock) | 500 MHz (333 MHz) (Maximum operating frequency differs depending on circuit configuration) |  |  |  |

| Interface level       |                        | 2.5 V LVCMOS, LVPECL 2.5 input, 3.3 V LVTTL, 2.5 V LVDS, HSTL class 1/HSTL class 3,        |  |  |  |

|                       |                        | SSTL2 class 1/SSTL2 class 2, SSTL18.                                                       |  |  |  |

| High-speed interfac   | ce embedded macro      | SerDes: Supports 10 G serial interface standard (such as 10 G BASE-R)/3 G serial ATA/      |  |  |  |

|                       |                        | XAUI/GbE/InfiniBand/PCI Express/Fibre Channel.                                             |  |  |  |

| Embedded macro        | SRAM                   | 2-port compiled synchronous type                                                           |  |  |  |

|                       | APLL                   | High-speed type                                                                            |  |  |  |

| DLL                   |                        | For high-speed SDRAM interface (3.3 V master only)                                         |  |  |  |

| Other macros          |                        | SPI4.2 (Dynamic), 10 G Ethernet MAC, 10/100/1000 M Ethernet MAC,                           |  |  |  |

|                       |                        | 10/100 M Ethernet MAC, POS PHY Level 3, UTOPIA, DDR controller, PCI controller             |  |  |  |

| Embedded test-rela    | ated                   | Scan path test, boundary scan, BIST, test bus                                              |  |  |  |

ISSP and OPENCAD are trademarks of NEC Electronics Corporation.

Teraform is a registered trademark of Tera Systems, Inc.

Synplify and Amplify are registered trademarks of Synplicity, Inc.

Other company names and product names described in this pamphlet are trademarks or registered trademarks of the respective company.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of September, 2004. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

For further information, please contact:

### **NEC Electronics Corporation**

1753, Shimonumabe, Nakahara-ku, Kawasaki, Kanagawa 211-8668, Japan Tel: 044-435-5111 http://www.necel.com/

### [North America]

### **NEC Electronics America, Inc.**

2880 Scott Blvd. Santa Clara, CA 95050-2554, U.S.A. Tel: 408-588-6000 800-366-9782 http://www.necelam.com/

### [Europe]

#### NEC Electronics (Europe) GmbH Arcadiastrasse 10

40472 Düsseldorf, Germany Tel: 0211-65030 http://www.ee.nec.de/

### Sucursal en España

Juan Esplandiu, 15 28007 Madrid, Spain Tel: 091-504-2787

### Succursale Française

9, rue Paul Dautier, B.P. 52 78142 Velizy-Villacoublay Cédex France Tel: 01-3067-5800

#### Filiale Italiana

Via Fabio Filzi, 25/A 20124 Milano, Italy Tel: 02-667541

### **Branch The Netherlands**

Boschdijk 187a 5612 HB Eindhoven The Netherlands Tel: 040-2445845

### **Tyskland Filial**

P.O. Box 134 18322 Taeby, Sweden Tel: 08-6380820

### United Kingdom Branch

Cygnus House, Sunrise Parkway Linford Wood, Milton Keynes MK14 6NP, U.K. Tel: 01908-691-133

### [Asia & Oceania]

NEC Electronics Hong Kong Ltd. 12/F., Cityplaza 4, 12 Taikoo Wan Road, Hong Kong Tel: 2886-9318

#### Seoul Branch

11F., Samik Lavied'or Bldg., 720-2, Yeoksam-Dong, Kangnam-Ku, Seoul, 135-080, Korea Tel: 02-558-3737

#### NEC Electronics Shanghai Ltd.

Room 2509-2510, Bank of China Tower, 200 Yincheng Road Central, Pudong New Area, Shanghai P.R. China P.C:200120 Tel: 021-5888-5400

### NEC Electronics Taiwan Ltd.

7F, No. 363 Fu Shing North Road Taipei, Taiwan, R. O. C. Tel: 02-2719-2377

### NEC Electronics Singapore Pte. Ltd.

238A Thomson Road, #12-08 Novena Square, Singapore 307684 Tel: 6253-8311