# CXA1875AP/AM

### 8-bit D/A Converter Compatible with I<sup>2</sup>C Bus

#### Description

The CXA1875AP/AM is developed as a 8-bit 5 ch D/A converter compatible with  $I^2C$  bus.

#### Features

- Serial control through I<sup>2</sup>C bus

- 5 channels of 8-bit D/A converter

- 4 built-in general purpose I/O ports (Digital I/O)

- I/O can be specified to respective ports independently

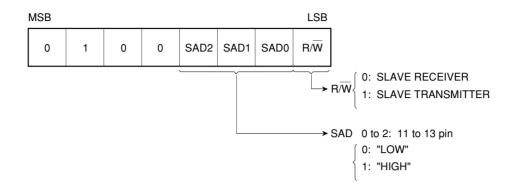

- Selection of 8 slave addresses possible through address select pins (3 pins)

#### Applications

I<sup>2</sup>C bus can control ICs that do not correspond to I<sup>2</sup>C bus by connecting the DC control pins of them.

#### Structure

Bipolar silicon monolithic IC

#### Absolute Maximum Ratings (Ta=25°C)

|                                         | - ·   | ,           |    |

|-----------------------------------------|-------|-------------|----|

| <ul> <li>Supply voltage</li> </ul>      | Vcc   | 7           | V  |

| Operating temperature                   | Topr  | –20 to +75  | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg  | –65 to +150 | °C |

| Allowable power dissipation             | ation |             |    |

|                                         | PD    | 960         | mW |

|                                         |       |             |    |

#### **Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vcc  | 5±0.5      | V  |

|------------------------------------|------|------------|----|

| Operating temperature              | Topr | –20 to +75 | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

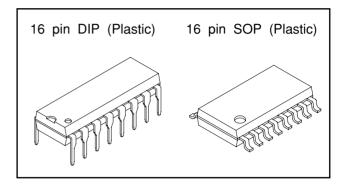

#### Pin Configuration (Top View)

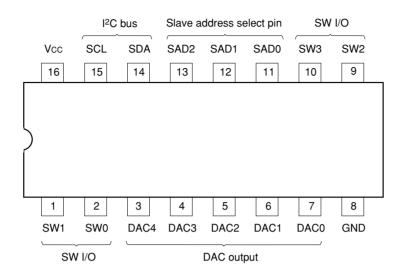

#### **Block Diagram**

### **Pin Description**

| No.                   | Symbol                               | Equivalent circuit               | Description                                                                        |

|-----------------------|--------------------------------------|----------------------------------|------------------------------------------------------------------------------------|

| 1                     | SW1                                  | Vçc                              | I/O pin for general purpose I/O port                                               |

| 2                     | SW0                                  |                                  | Vi∟max: 1.5 V                                                                      |

| 9                     | SW2                                  |                                  | VIHmin: 3 V                                                                        |

| 10                    | SW3                                  |                                  | Volmax: 0.4 V                                                                      |

| 14<br>15              | SDA<br>SCL                           | 4.5k                             | SDA I/O pin for I²C bus                                                            |

| 3<br>4<br>5<br>6<br>7 | DAC4<br>DAC3<br>DAC2<br>DAC1<br>DAC0 | Vcc Vcc $22k$<br>777 $20k$ $777$ | D/A converter output pin                                                           |

| 8                     | GND                                  |                                  | GND pin                                                                            |

| 11<br>12<br>13        | SAD0<br>SAD1<br>SAD2                 | Vcc<br>Vcc<br>150<br>4.5k        | Slave address input pin<br>Input at positive logic<br>Vı∟max: 1.5 V<br>Vıнmin: 3 V |

| 16                    | Vcc                                  |                                  | Power supply pin                                                                   |

#### Electrical Characteristics (Ta=25 °C, Vcc=5 V) D/A Converter Block

| No. | ltem            | Symbol | Test<br>circuit | Test contents  | Min. | Тур. | Max. | Unit |

|-----|-----------------|--------|-----------------|----------------|------|------|------|------|

| 1   | Circuit current | Icc    | 1               | DAC 0 to 4=127 | 6    | 9    | 12   | mA   |

| 2 | Differential linearity    | DLE  | 1 | $\frac{V(DAC0 \text{ to } 4=n+1)-V(DAC0 \text{ to } 4=N)}{V(DAC0 \text{ to } 4=191)-V(DAC0 \text{ to } 4=63)} \times 128-1$ n=0 to 127 | -1  | 0   | +1  | LSB |

|---|---------------------------|------|---|----------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|

| 3 | Minimum output<br>voltage | Vmin | 1 | DAC 0 to 4=0                                                                                                                           | 0.1 | 0.4 | 0.7 | V   |

| 4 | Maximum<br>output voltage | Vmax | 1 | DAC 0 to 4=255                                                                                                                         | 4.3 | 4.6 | 4.9 | V   |

| 5 | Output current            | lout | 2 | Current that can be flowed from Pins 3 to 7                                                                                            | -1  |     | +1  | mA  |

| 6 | Output<br>impedance       | Zo   | 2 | DAC 0 to 4=127, $\frac{V(-1 \text{ mA}) - V(1 \text{ mA})}{2 \text{ mA}}$                                                              | 0   | 3   | 6   | Ω   |

#### SW, SAD Pins

| No. | Item                     | Symbol | Text<br>circuit | Test contents                                  |     | Тур. | Max. | Unit |

|-----|--------------------------|--------|-----------------|------------------------------------------------|-----|------|------|------|

| 7   | Low level input voltage  | VIL    | 3               | ST 0 to 3 an input voltage that turns to '0'   |     | _    | 1.5  | V    |

| 8   | High level input voltage | Vih    | 3               | ST 0 to 3 an input voltage that turns to '1'   | 3.0 | _    | _    | V    |

| 9   | Low level input current  | lι∟    | 3               | Input current when 0.4 V is applied            | -10 | 0    | +10  | μA   |

| 10  | High level input current | Ін     | 3               | Input current when 4.5 V is applied            | -10 | 0    | +10  | μA   |

| 11  | Low level input voltage  | Vol    | 4               | SW 0 to 3=1, Output voltage when 1 mA flows in | 0   | 0.2  | 0.4  | V    |

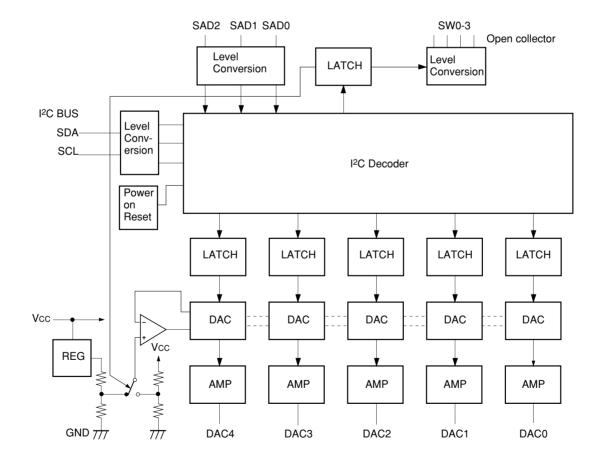

#### I2C Bus Block Items (SDA, SCL)

| No. | Item                                                     | Symbol  | Min. | Тур. | Max. | Unit |

|-----|----------------------------------------------------------|---------|------|------|------|------|

| 12  | High level input voltage                                 | Viн     | 3.0  | —    | 5.0  | V    |

| 13  | Low level input voltage                                  | VIL     | 0    | —    | 1.5  | V    |

| 14  | High level input current                                 | Ін      | —    | —    | 10   | μA   |

| 15  | Low level input current                                  | lı.     | —    | —    | 10   | μA   |

| 16  | Low level output voltage<br>At 3 mA flow to SDA (Pin 14) | Vol     | 0    | _    | 0.4  | V    |

| 17  | Maximum flowing current                                  | lol     | 3    | —    | —    | mA   |

| 18  | Input capacitance                                        | Сі      | —    | —    | 10   | рF   |

| 19  | Maximum clock frequency                                  | fsc∟    | 0    | —    | 100  | kHz  |

| 20  | Data change minimum waiting time                         | tBUF    | 4.7  | —    | —    | μs   |

| 21  | Data transfer start minimum waiting time                 | thd:sta | 4.0  | —    | —    | μs   |

| 22  | Low level clock pulse width                              | t∟ow    | 4.7  | —    | —    | μs   |

| 23  | High level clock pulse width                             | tніgн   | 4.0  | —    | —    | μs   |

| 24  | Minimum start preparation waiting time                   | tsu:sta | 4.7  | —    | —    | μs   |

| 25  | Minimum data hold time                                   | thd:dat | 5    | —    | —    | μs   |

| 26  | Minimum data preparation time                            | tsu:dat | 250  | _    | —    | ns   |

| 27  | Rise time                                                | tR      | —    | —    | 1    | μs   |

| 28  | Fall time                                                | tF      | —    | —    | 300  | ns   |

| 29  | Minimum stop preparation waiting time                    | tsu:sto | 4.7  | —    | _    | μs   |

$I^2C$  bus load conditions: Pull up resistance 4 k $\Omega$  (Connected to +5 V)

Load capacitance 200 pF (Connected to GND)

—4—

#### I<sup>2</sup>C Bus Control Signal

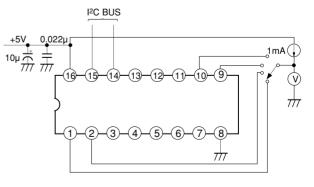

#### **Electrical Characteristics Test Circuit**

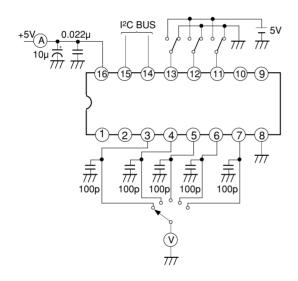

Test circuit 1

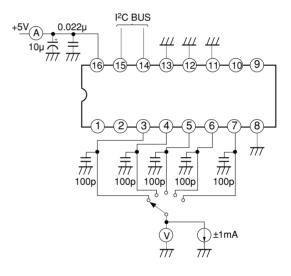

Test circuit 2

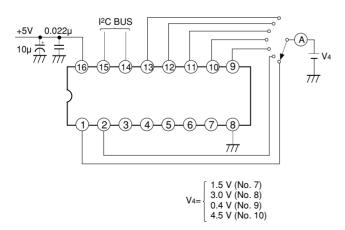

Test circuit 4

#### Definition of I<sup>2</sup>C Register

#### <Slave address>

<Register table>

- With the IC reset all registers are reset to 0

- \*: Not defined

- $\times$ : Don't care

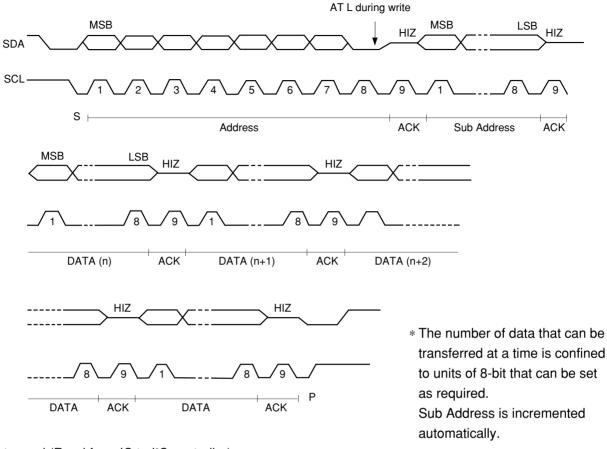

- Sub address is auto incremented

- It can be used as a 6-bit D/A converter by setting the lower two bits of DAC 0-4 registors to 0, but take care that the max. voltage of DA output will lower about 100 mV compared with the use of 8 bits.

| Sub address | BIT7     | BIT6 | BIT5 | BIT4 | BIT3  | BIT2 | BIT1 | BITO |

|-------------|----------|------|------|------|-------|------|------|------|

| ××××× 000   | REF      | *    | *    | *    | SW3   | SW2  | SW1  | SW0  |

| ××××× 001   |          |      | •    | DAC  | 0 (8) |      |      |      |

| ××××× 010   |          |      |      | DAC  | 1 (8) |      |      |      |

| ××××× 011   |          |      |      | DAC  | 2 (8) |      |      |      |

| ××××× 100   | DAC3 (8) |      |      |      |       |      |      |      |

| ××××× 101   |          |      |      | DAC  | 4 (8) |      |      |      |

#### **Control Register**

#### **Status Register**

| BIT7   | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BITO |

|--------|------|------|------|------|------|------|------|

| PONRES | 0    | 0    | 0    | ST3  | ST2  | ST1  | ST0  |

#### <Registers> In brackets () number of bits

- REF

(1):

Switches D/A converter reference voltage

0:Standardizes the inner regulator

1:Standardizes voltage resistance divided from Vcc

- SW0 to 3 (1): Selects ON/OFF of Pins 1, 2, 9 and 10 (Each pin is the open collector output of NPN transistor) 0:OFF 1:ON

- DAC0 to 4 (8): Digital data input register of D/A converter 0:Output voltage turns to minimum 255:Output voltage turns to maximum

- PONRES (1):

Detects POWER ON RESET

0:Master passes from the bus and is reset to 0 after having read this status

1:Set to 1 when power supply is turned on or when there has been a power dip

- ST0 to 3 (1): Detects and registers the voltage condition of Pins 1, 2, 9 and 10 0:1.5 V and below 1:3.0 V and above Note) SW0 to 3 effective during 0

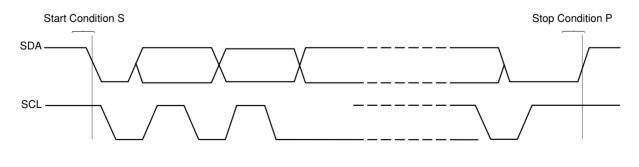

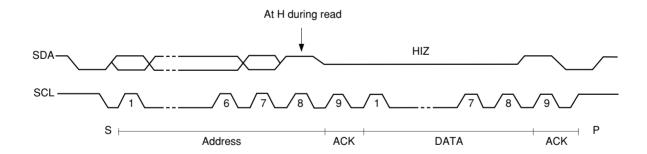

#### I<sup>2</sup>C Bus Signal

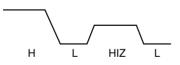

There are 2 signals in I<sup>2</sup>C bus. SDA (Serial DAta) and SCL (Serial Clock). SDA is double-way.

• As SDA is double-way it has 3 state outputs, H, L and HIZ.

• I<sup>2</sup>C transfer begins with Start Condition and ends with Stop Condition.

—7—

• I<sup>2</sup>C data write (Write from I<sup>2</sup>C controller to IC)

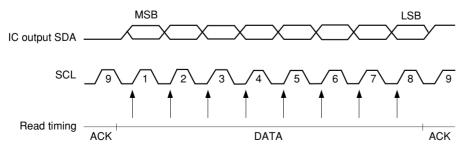

• I<sup>2</sup>C data read (Read from IC to I<sup>2</sup>C controller)

Read timing

\* Data read is performed with SCL rise.

—8—

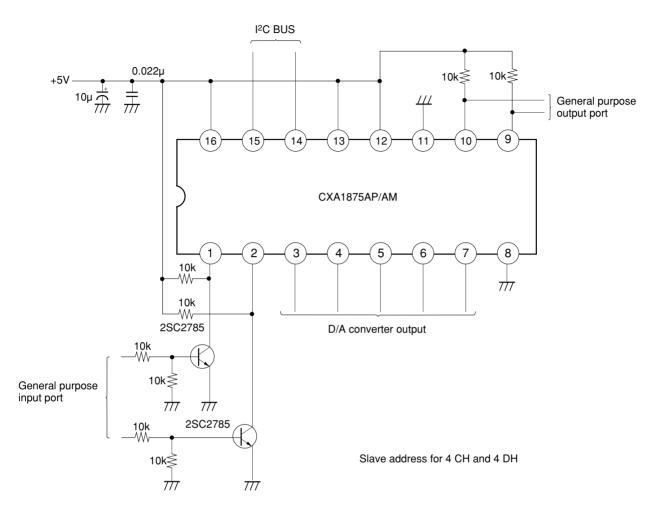

#### **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

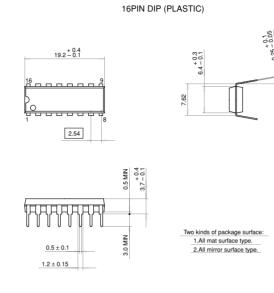

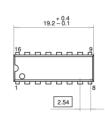

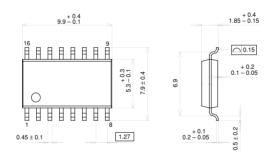

## Package Outline Unit : mm CXA1875AP

PACKAGE STRUCTURE

PACKAGE MATERIAL

EPOXY RESIN

SONY CODE

DIP-16P-01

LEAD TREATMENT

SOLDER PLATING

EIAJ CODE

DIP016-P-0300

LEAD MATERIAL

COPPER ALLOY

JEDEC CODE

Similar to MO-001-AE

PACKAGE MASS

1.0 g

#### CXA1875AP Kokubu Ass'y

#### 16PIN DIP (PLASTIC)

0° to 15

Two kinds of package surface: 1.All mat surface type. 2.All mirror surface type.

#### PACKAGE STRUCTURE

|            |                      | PACKAG  |

|------------|----------------------|---------|

| SONY CODE  | DIP-16P-01           | LEAD TR |

| EIAJ CODE  | DIP016-P-0300        | LEAD M  |

| JEDEC CODE | Similar to MO-001-AE | PACKAG  |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 1.0 g          |

|                  |                |

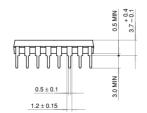

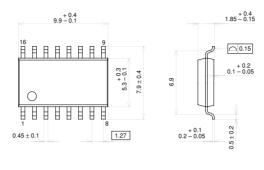

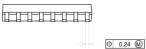

#### Package Outline Unit : mm CXA1875AM

#### 16PIN SOP (PLASTIC)

### ⊕ 0.24 M

PACKAGE MASS

EPOXY RESIN

0.2g

SOLDER PLATING COPPER ALLOY

|            |               |   | PACKAGE STRUCTUR |      |  |  |  |

|------------|---------------|---|------------------|------|--|--|--|

|            |               | - | PACKAGE MATERIAL | EPO  |  |  |  |

| SONY CODE  | SOP-16P-L01   |   | LEAD TREATMENT   | SOL  |  |  |  |

| EIAJ CODE  | SOP016-P-0300 |   | LEAD MATERIAL    | COP  |  |  |  |

| JEDEC CODE |               | 1 | LEAD WAI ERIAL   | COP  |  |  |  |

| JEDEO OODE |               |   | DAOKAOE MAGO     | 0.20 |  |  |  |

#### CXA1875AM SCT Ass'y

16PIN SOP (PLASTIC)

|            |               |   | PACKAGE STRUCTURE |                |

|------------|---------------|---|-------------------|----------------|

|            |               | 1 | PACKAGE MATERIAL  | EPOXY RESIN    |

| SONY CODE  | SOP-16P-L01   |   | LEAD TREATMENT    | SOLDER PLATING |

| EIAJ CODE  | SOP016-P-0300 |   | I FAD MATERIAI    | COPPER ALLOY   |

| JEDEC CODE |               |   | BACKAGE MARE      | 0.20           |

#### LEAD PLATING SPECIFICATIONS

| ITEM               | SPEC.           |  |

|--------------------|-----------------|--|

| LEAD MATERIAL      | COPPER ALLOY    |  |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |  |

| PLATING THICKNESS  | 5-18µm          |  |

Purchase of Sony's I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.