# 12-BIT, 2MHz SELF-CALIBRATING A/D CONVERTER

#### DESCRIPTION

The CAT5412 is a 12-bit BiMOS A/D converter utilizing a self-calibration technique and digital error correction. This self-calibration circuitry ensures 12-bit accuracy over operating life and temperature range of the device, eliminating any manual calibration requirements.

The high throughput is achieved by using a 2-step flash A/D conversion technique in addition to two track-and-hold amplifiers.

The CAT5412 uses an advanced BiMOS process which provides both low power consumption (700mW) and an increased reliability inherent to monolithic devices.

#### **FEATURES**

- Resolution: 12 bits

- Maximum non-linearity: 1/2 LSB

- Throughput rates to 2MHz

- Total harmonic distortion: 0.02%

- Dynamic range: 72dB

- No missing codes to 12 bits

- Self-calibrating for accuracy over time and temperature

- Fast recovery from input overdrive

- Low power dissipation: 700mW

- Monolithic BiMOS sampling ADC

- on chip track-and-hold amplifier

- microprocessor interface

#### PIN CONFIGURATION

| ·         |            |

|-----------|------------|

| HOLD 1    | 40 D OVRNG |

| RST ☐2    | 39 D11     |

| CCNV 3    | 38 D10     |

| AGND1 4   | 37 D9      |

| AIN 15    | 36 D8      |

| VREF- 6   | 35 D7      |

| VREF+ 7   | 34 T D6    |

| VA1+ □8   | 33 DGND    |

| VA1- □ 9  | 32 VA5+    |

| AGND2 10  | 31 🗖 VD+   |

| VA2+ 🖸 11 | 30 🗖 VD-   |

| VA3+ ☐ 12 | 29 CLKIN   |

| VA2- 🗖 13 | 28 🕇 XIN   |

| VA3- 🗖 14 | 27 🗖 D5    |

| VA4+ □ 15 | 26 D4      |

| TST1 ☐ 16 | 25 🕽 D3    |

| TST2 ☐ 17 | 24 D2\     |

| CAL [ 18  | 23 🗖 D1    |

| RD [ 19   | 22 D0      |

| CS ☐ 20   | 21 DRDY    |

|           |            |

This document contains information for a new product. Catalyst Semiconductor, Inc. reserves the right to modify this product without notice.

#### PIN DESCRIPTIONS

**Power Supply Connections**

VD+: Positive Digital Power, PIN 31

Positive digital supply voltage. Nominally +5V.

VD-: Negative Digital Power, PiN 30 Negative digital supply voltage. Nominally -5V.

DGND: Digital Ground, PIN 33 Digital ground reference.

VA+: Positive Analog Power, PINS 8,11, 12,15,32

Positive analog supply voltage. Nominally +5V.

VA-: Negative Analog Power, PINS 9,13,14 Negative analog supply voltage. Nominally -5V.

AGND: Analog Ground, PIN 4,10 Analog ground reference.

#### Oscillator

CLKIN; XIN: Clock In, PIN 29; Crystal In, PIN 28 Used to generate the internal master clock. A crystal can be tied across the two pins or an external CMOS-compatible clock can be driven into CLKIN if XIN is left floating.

#### Digital Inputs

HOLD: Hold input, PIN 1\_

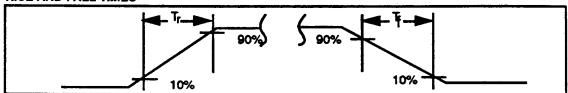

A negative transition on HOLD puts the track-and-hold amplifier into the hold state and initiates the conversion sequence. Conversions must be synchronized with the master clock at f<sub>CLK</sub>/8N where N=1,2,3. The HOLD input is CMOS-compatible.

CCNV: Continuous Convert, PIN 3

When held high with the HOLD input high or low, throughput will proceed at 1/8th the master clock frequency.

CS: Chip Select, PIN 20

Activates the RD and CAL inputs. When CS is high, these inputs have no effect and the data bus

(D0 through D11) is held in a high impedance state.

RD: Read, PIN 29

When held low with  $\overline{CS}$  also low, enables D0-D11.

RST: Reset, PIN 2

When taken low, all internal logic is reset to its cleared or default state. When brought high again a full calibration results. The CAT5412 will not operate while RST is low nor during the resulting full calibration cycle.

CAL: Calibrate, PIN 18

Same as RST, but logically inverted and enabled by CS.

#### Analog Inputs

VREF+: Positive Voltage Reference, PIN 7

Represents positive full scale voltage. Typically +1.5V with respect to AGND (bipolar system) or +3V with respect to AGND and VREF- (unipolar system).

VREF-: Negative Voltage Reference, PIN 6

Represents negative full scale voltage, typically

-1.5V with respect to AGND (bipolar system) or

tied to AGND (unipolar system).

AIN: Analog Input, PIN 5

Analog input to the track-and-hold amplifier.

Digital Outputs

**OVRNG: Overrange, PIN 40**

Goes high if the sampled analog input voltage exceeds VREF+ or VREF-. OVRNG also goes high during reset and calibration cycles and can therefore be used to indicate end of calibration

DRDY: Data Ready, PIN 21

Falls when new data is becoming available at the outputs. Returns high three master clock cycles later.

# CAT5412 A/D Converter

# PIN CONFIGURATIONS, continued

# Digital Input/Outputs

# D0 through D11: Data Bus, PINS 22 through 27,

34 through 39

Three-state data bus.

#### Miscellaneous Pins

TST1: Test, PIN 16

Reserved for factory use. Must be tied to DGND for proper device operation.

TST2: Test, PIN 17

Reserved for factory use. Must be tied to DGND

for proper device operation.

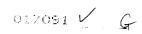

# **BLOCK DIAGRAM**

# **APPLICATIONS**

- High Speed Measurement Systems

- Board Level DAS for Computers

- Automatic Test Equipment

- Analytic and Medical Instruments

- Signal Processing

- Vibration Analysis

- Image Enhancement Systems

- \* Radar Systems

- Digital Oscilloscopes

- Electro-Optics Systems

- Computer Aided Tomography and Magnetic Resonance Systems

#### THEORY OF OPERATION

To achieve high speed and high accuracy, the CAT5412 implements a standard 2-step flash A/D conversion using self-calibration and digital error correction. Throughput is further maximized by the addition of a second T/H. This allows the next input to be acquired while the previous sample is being converted.

#### DIGITAL ERROR CORRECTION

The use of digital correction decreases the conversion time because the flash converter comparators do not need to be auto-zeroed. This time savings is significant because the auto-zero offset voltage must be allowed to settle to 12 bits of accuracy. Other advantages obtained by not auto-zeroing include less dynamic noise on the ladder, simpler clock timing and fast recovery from input overload.

The digital error correction is capable of correcting comparator errors from the first flash conversion step. These errors can be as large as 1/128 of full scale. The first flash provides the top seven MSB's. The second flash step provides the bottom six bits. The one bit of overlap is used to correct the errors in the seventh MSB that might have occurred during the first flash ADC.

Flash step #1 1 0 1 0 1 0 1

Flash step #2 0 1 0 1 0 1 0 1 Resulting Code 1 0 1 0 1 0 1 0 0 1 0 1 Bit Position 12 11 10 9 8 7 6 5 4 3 2 1

#### 2-STEP A/D CONVERSION

A/D conversion speed is optimized by using a single step flash technique where an N-bit conversion compares the analog input signal to 2<sup>n-1</sup> graduated voltage levels. The correct binary output is generated by processing and encoding the 2<sup>n-1</sup> comparator outputs. One drawback to this approach is that for each additional bit of resolution the number, as well as the accuracy requirement of the comparator doubles. This limitation makes single step flash converters impractical for resolution greater than 8- or 10-bits.

The 2-step technique that the CAT5412 uses employs slightly more complex sub-circuit blocks to achieve high resolution and results in negligible speed degradation. As shown in the block diagram, the CAT5412 consists of two track-and-hold amplifiers, a 7-bit flash ADC, a 7bit DAC (the resistor ladder), and a residue amplifier. When the command is issued, T/H-1 holds the analog input signal and the flash ADC does a 7-bit conversion to determine the seven MSB's. The MSB's, once decoded are latched into the digital error correction logic. The flash converter's outputs are also loaded into the DAC. The DAC voltage is then subtracted from the analog input and the difference is multiplied to create the input for the second flash conversion. The six bits of data from the second flash conversion and the seven bits from the first flash conversion are used by the digital correction to calculate a 12-bit accurate result.

ANALOG CHARACTERISTICS ( $T_A = 25^{\circ}$ C (Note 1); All VA+ pins, VD+ = 5V; All VA- pins, VD- = -5V; VREF- = -1.5V;  $f_{CLK} = 16$ MHz for -1, 8MHz for -2; 100kHz Full Scale Input Sinewave; Continuous Convert Mode unless otherwise specified.)

| Parameter                                                                                                  |            | AT5412           | 2-C                                           | CAT5412-I         |              | -1          | CAT5412-M  |                          |            | Units |

|------------------------------------------------------------------------------------------------------------|------------|------------------|-----------------------------------------------|-------------------|--------------|-------------|------------|--------------------------|------------|-------|

| Resolution                                                                                                 | min<br>12  | typ              | max                                           | min<br>10         | tvp          | max         | min<br>12  | typ                      | max        | Bits  |

|                                                                                                            |            |                  | . <u>.                                   </u> | 12                |              |             |            |                          |            |       |

| Specified Temperature Range                                                                                |            | 0 to 7           | <u> </u>                                      | _                 | 40 to +8     | 15          |            | 5 to +1                  | 25         | •C    |

| Dynamic Performanc                                                                                         | <i>e</i>   |                  |                                               |                   |              |             |            |                          |            |       |

| Peak Harmonic or Spurious Noise<br>25°C J<br>-K                                                            | 74<br>77   | 76<br>79         |                                               | 74<br>77          | 76<br>79     |             | 74<br>77   | 76<br>79                 |            |       |

| 100kHz Input<br>T <sub>min</sub> to T <sub>max</sub> -K<br>(Note 1)                                        | TBD<br>TBD | 75<br>75         |                                               | TBD<br>TBD        | 75<br>75     |             | TBD<br>TBD | 75<br>75                 |            | dB    |

| 490kHz Input J<br>-K                                                                                       |            | 72<br>72         |                                               |                   | 72<br>72     |             |            | 72<br>72                 |            | :     |

| Total Harmonic -J<br>Distortion -K                                                                         |            | 0.02<br>0.02     |                                               |                   | 0.02<br>0.02 |             |            | 0.02<br>0.02             |            | %     |

| Signal-to-(Noise plus Distortion) 25°C -K OdB Input (Full Scale)                                           | 65<br>68   | <b>6</b> 7<br>70 |                                               | 65<br>68          | 67<br>70     |             | 65<br>68   | <b>67</b> 70             |            |       |

| T <sub>min</sub> to T <sub>max</sub> -K<br>(Note 1)                                                        | TBD<br>TBD | 67<br>70         |                                               | TBD<br>TBD        | 67<br>70     |             | TBD<br>TBD | <b>6</b> 7<br><b>7</b> 0 |            | dΒ    |

| -40dB Input -K                                                                                             |            | 32<br>32         |                                               |                   | 32<br>32     |             |            | 32<br>32                 |            |       |

| dc Accuracy                                                                                                |            | -                |                                               |                   |              |             |            |                          |            |       |

| Linearity Error (Note 1)  -J. T <sub>min</sub> to T <sub>max</sub> -K T <sub>min</sub> to T <sub>max</sub> |            | ±1<br>±3/4       | ±2.5<br>±1.5                                  |                   | ±1<br>±3/4   | ±2.5<br>TBD |            | ±1<br>±3/4               | TBD<br>TBD | LSB   |

| Differential Linearity  √ T <sub>min</sub> to T <sub>max</sub>                                             |            |                  | No                                            | i<br>Missing<br>I | Codes        | Guara       | i<br>nteed |                          |            |       |

| -K T <sub>min</sub> to T <sub>max</sub><br>(Note 1)                                                        |            |                  | ±0.9                                          |                   |              | ±0.9        |            |                          | TBD        | LSB   |

| Full Scale Error T <sub>min</sub> to T <sub>max</sub>                                                      |            | ±1/2             |                                               |                   | ±1.5         |             |            | <u>±</u> 3               |            | LSB   |

| Offset Error                                                                                               |            | ±1/2             |                                               |                   | ±1/2         |             |            | ±2                       |            | LSB   |

Notes: 1. All Tmin to Tmax specifications apply after calibration at the temperature of interest.

Temperatures specified define ambient conditions in free-air during test and do not refer to the junction temperature of the device.

# ANALOG CHARACTERISTICS (continued)

| Parameter                                                          | CAT5412     |     |              | CAT5412I    |          |              | CAT5412M    |     |              | Units    |

|--------------------------------------------------------------------|-------------|-----|--------------|-------------|----------|--------------|-------------|-----|--------------|----------|

|                                                                    | min         | typ | max          | min         | tvp      | max          | min         | typ | max          |          |

| Analog Input                                                       |             |     |              |             |          |              |             |     |              |          |

| Aperture Time                                                      | 35          |     |              |             | 35       |              | 35          |     |              | nS       |

| Aperture Jitter                                                    |             | 50  |              |             | 50       |              |             | 50  |              | ps,rms   |

| Input Bandwidth (Note 3)<br>Small Signal, -3dB<br>Full Power, -3dB | 4 3         |     |              | 4 3         |          |              | 4<br>3      |     |              | MHz      |

| Analog Input Impedance at dc                                       |             | 10  |              |             | 10       |              |             | 10  |              | МΩ       |

| Input Capacitance<br>VREF-pin<br>AIN, VREF+ pins                   | 50<br>10    |     |              | 50<br>10    |          |              | 50<br>10    |     | pF           |          |

| Conversion and T                                                   | hroughp     | ut  |              |             |          |              | · · · · ·   |     |              |          |

| Conversion Time -1<br>(Notes 5,6) -2                               | 625<br>1.25 |     | 688<br>1.375 | 625<br>1.25 |          | 688<br>1.375 | 625<br>1.25 |     | 688<br>1.375 | nS<br>μS |

| Throughput Rate -1 (Note 6) -2                                     | 2           |     | -            | 2           |          |              | 2           |     |              | MHz      |

| Acquisition Time                                                   | 300         |     | 300          |             | 300      |              | nS          |     |              |          |

| Power Supplies                                                     |             |     |              |             |          |              |             |     |              |          |

| Power Supply Current<br>(Note 8)<br>I <sub>A+</sub>                |             | 70  | 90           |             | 70       | 90           |             | 70  | 90           |          |

| I <sub>A</sub> .                                                   |             | -70 | -90          |             | -70      | -90          |             | -70 | -90          |          |

| I <sub>D+</sub>                                                    |             | 5   | 10           |             | 5        | 10           |             | 5   | 10           | mA       |

| ID.                                                                |             | -5  | -10          |             | -5       | -10          |             | -5  | -10          |          |

| Power Dissipation (Note 8)                                         |             | 750 | 1000         |             | 750      | 1000         |             | 750 | 1000         | mW       |

| Power Supply Rejection Positive Supplies Negative Supplies         | 50<br>50    |     | 50<br>50     |             | 50<br>50 |              |             | dB  |              |          |

Notes:

- 3. Input 40dB below full scale.

- 4. Measured from falling transition on HOLD to falling transition on DRDY.

- Applies for conversions triggered externally. In Continuous Convert mode throughput proceeds at one-eighth the master clock frequency with a fixed 10 clock cycle conversion time at full throughput.

- 6. All outputs unloaded. All inputs CMOS levels.

#### **Preliminary**

# SEMICONDUCTOR, INC.

CAT5412 A/D Converter

SWITCHING CHARACTERISTICS ( $T_A = T_{min}$  to  $T_{max}$ ; All VA+ pins, VD+ = 5V  $\pm$  5%; All VA- pins, VD-=  $5V \pm 5\%$ ; Inputs: Logic 0 = 0V, Logic 1 = VD+;  $C_L$  = 50 pF.)

| Parameter                                                                                                              | Symbol                                                                   | Min                     | Тур      | Max         | Units    |

|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|----------|-------------|----------|

| Master Clock Frequency:<br>-1<br>-2                                                                                    | <sup>f</sup> CLK                                                         | 3<br>3                  | •        | 16<br>8     | MHz      |

| Master Clock Duty Cycle                                                                                                | •                                                                        | 40                      | -        | 60          | %        |

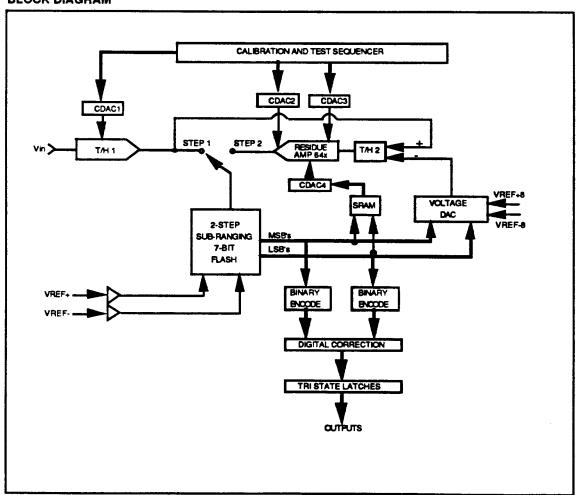

| Rise Times: Any Digital<br>Input (Note 7)<br>Any Digital Output                                                        | <sup>t</sup> rise                                                        | •                       | 20       | 1.0<br>-    | μS<br>nS |

| Fall Times: (Note 7) Any Digital Input Any Digital Output                                                              | <sup>t</sup> fall                                                        | <u>.</u>                | -<br>20  | 1.0<br>-    | μS<br>nS |

| HOLD, CLKIN Relationship<br>State 7 to HOLD Low<br>HOLD Low to State 0<br>State 0 to HOLD High<br>HOLD High to State 7 | <sup>t</sup> ha<br><sup>t</sup> hb<br><sup>t</sup> hc<br><sup>t</sup> hd | 62.5<br>0.0<br>75<br>30 |          | -<br>-<br>- | nS       |

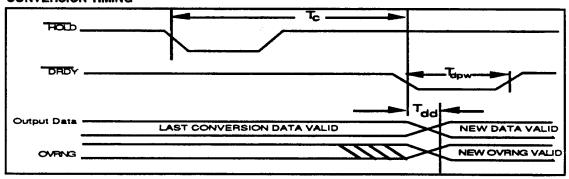

| Conversion Time (Note 8)                                                                                               | tc                                                                       | 10                      | •        | 11          | WCC.     |

| DRDY Pulse Width                                                                                                       | <sup>t</sup> dpw                                                         | .=                      | 3        | •           | WCC.     |

| Data Delay Time                                                                                                        | ਚਿਰ                                                                      | -                       | 40       | TBD         | nS       |

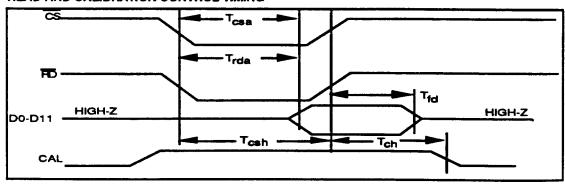

| Access Times: CS Low to Data Valid (Note 9) RD Low to Data Valid                                                       | <sup>t</sup> csa<br><sup>t</sup> rda                                     | -                       | 90<br>90 | 90<br>90    | nS       |

| Output Float Delay<br>CS or RD High to Output<br>High-Z                                                                | Чd                                                                       | -                       | 50       | TBD         | nS       |

| Hold Times: CS High to CAL Invalid (Note 10)                                                                           | <sup>t</sup> ch                                                          | TBD                     | 20       | •           | nS       |

| Cal Pulse Width: CAL & CS Low                                                                                          | <sup>t</sup> csh                                                         | 2                       |          | -           | WCC.     |

| RST Pulse Width                                                                                                        | t <sub>rpw</sub>                                                         | 2                       | -        | •           | WCC.     |

Notes: 7. HOLD and CLKIN should be driven with signals which have rise and fall times of at least 25ns.

- 8. Conversion time in the Continuous Convert mode is a fixed 10 clock cycles.

9. Data goes valid when both CS and RD are low simultaneously. Each access time assumes the other control input is already low or falls concurrently.

10. If CAL is brought low while CS is low, a calibration cycle will be initiated.

<sup>\*</sup>MCC = Master Clock Cycles

# **RISE AND FALL TIMES**

#### HOLD/MASTER CLOCK PHASE RELATIONSHIP

# **CONVERSION TIMING**

# **READ AND CALIBRATION CONTROL TIMING**

DIGITAL CHARACTERISTICS (TA = Tmin to Tmax; All VA+ pins, VD+ =  $5V \pm 5\%$ ; All VA- pins, VD- =  $-5V \pm 5\%$ .) All measurements below are performed under static conditions.

| Parameter                             | Symbol           | Min        | Тур | Max | Units |

|---------------------------------------|------------------|------------|-----|-----|-------|

| High-Level Input Voltage (Note 12)    | V <sub>IH</sub>  | 2.0        | •   | -   | V     |

| Low-Level Input Voltage (Note 12)     | V <sub>IL</sub>  | -          | •   | 0.8 | ٧     |

| High-Level Output Voltage (Note 13)   | VOH              | VD+ - 1.0V | -   | -   | ٧     |

| Low-Level Output Voltage Iout = 1.6MA | V <sub>OL</sub>  | •          | -   | 0.4 | V     |

| Input Leakage Current                 | l <sub>in</sub>  | -10        | •   | +10 | μА    |

| 3-State Leakage Current               | 1 <sub>OZ</sub>  | -10        | •   | +10 | μА    |

| Digital Output Pin Capacitance        | C <sub>out</sub> | -          | 9   |     | pF    |

Notes:

- 12. All pins except  $\overline{\text{HOLD}}$  and CLKIN which accept only CMOS-compatible inputs ( $V_{\text{IL}} = 0.5V$  and  $V_{\text{IH}} = VD+ 0.5V$ ).

- 13.  $l_{\text{Out}}$  = -100 $\mu$ A. This specification guarantees TTL compatibility (V<sub>OH</sub> = 2.4V @  $l_{\text{out}}$  = -40 $\mu$ A).

# RECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0V, see note 14.)

| Paramete             | Symbol                                                                     | Min                                   | Тур                            | Max                        | Units                                |             |

|----------------------|----------------------------------------------------------------------------|---------------------------------------|--------------------------------|----------------------------|--------------------------------------|-------------|

| DC Power Supplies    | Positive Digital<br>Negative Digital<br>Positive Analog<br>Negative Analog | VD+<br>VD-<br>VA1+ - VA5+<br>VA1 VA3- | 4.75<br>-4.75<br>4.75<br>-4.75 | 5.0<br>-5.0<br>5.0<br>-5.0 | VA2+, VA5+<br>-5.25<br>5.25<br>-5.25 | >>>>        |

| Analog Input Voltage | V <sub>AIN</sub>                                                           | VREF-                                 | -                              | VREF+                      | V                                    |             |

| Analog Reference Vo  | oltages<br>Unipolar Input Range<br>Bipolar Input Range                     | VREF+<br>VREF-<br>VREF+<br>VREF-      | 2.0<br>-<br>1.0<br>-1.0        | AGND                       | 3.0<br>-<br>1.5<br>-1.5              | V<br>V<br>V |

Notes: 14. All voltages with respect to ground.

# ABSOLUTE MAXIMUM RATINGS (A<sub>GND</sub>, $D_{GND} = 0V$ , all voltage with respect to ground.

| Parameter                                  |                  | Symbol           | Min         | Max                                   | Units       |

|--------------------------------------------|------------------|------------------|-------------|---------------------------------------|-------------|

| DC Power Supplies:                         | Positive Digital | VD+              | -0.3        | VA2+,VA5+ +0.3                        | V           |

|                                            | Negative Digital | VD-              | 0.3         | -6.0                                  | ٧           |

| (Note 15)                                  | Positive Analog  | VA1+ - VA5+      | -0.3        | 6.0                                   | ٧           |

|                                            | Negative Analog  | VA1 Va3-         | 0.3         | -6.0                                  | V           |

| Input Current, Anyu F<br>Supplies (Note 16 | Pin Except       | Į.               | _           | +10                                   | mA          |

|                                            |                  | l lin            | -           | +10                                   | MA          |

| Analog Input Voltage                       |                  |                  |             | · · · · · · · · · · · · · · · · · · · | <del></del> |

| (AIN and VREF pins)                        |                  | V <sub>ina</sub> | VA1 VA3 0.3 | VA2+,VA5+ +0.3                        | V           |

| Digital Input Voltage                      |                  | V <sub>ind</sub> | -0.3        | VA2+, VA5+ +0.3                       | ٧           |

| Ambient Operating Te                       | emperature       | TA               | -55         | 125                                   | •c          |

| Storage Temperature                        |                  | T <sub>stg</sub> | -65         | 150                                   | °C          |

Notes:

WARNING:

Operating at or beyond these limits may result in permanent damage to tthe device. Normal operation is not guaranteed at these extremes.

<sup>15.</sup> VA1+, VA3+, VA4+ must never exceed VA2+ and VA5+ by more than 0.3V.

<sup>16.</sup> Transient currents of up to 100mA will not cause SCR latch-up.

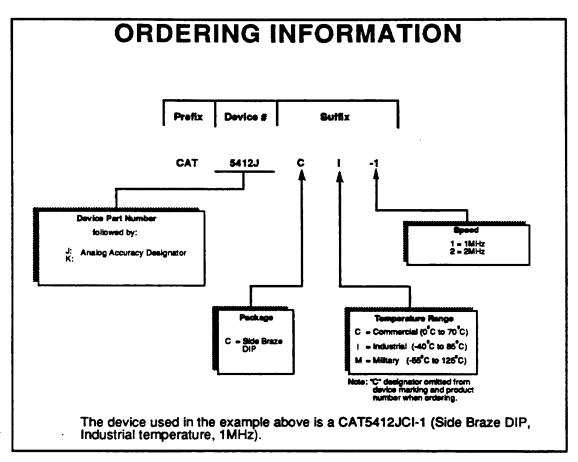

# Ordering Guide

|              |                   | Signal to (Noise | Linearity |               |                       |

|--------------|-------------------|------------------|-----------|---------------|-----------------------|

| Model        | <b>Throughput</b> | plus Distortion  | Error     | Temp. Range   | <u>Package</u>        |

| CAT5412JC-1  | 1MHz              | 65 dB            | ±1 LSB    | 0 to 70°C     | 40-pin Ceramic SB DIP |

| CAT5412KC-1  | 1MHz              | 68 dB            | ±1/2 LSB  | 0 to 70°C     | 40-pin Ceramic SB DIP |

| CAT5412JC-2  | 2MHz              | 65 dB            | ±1 LSB    | 0 to 70°C     | 40-pin Ceramic SB DIP |

| CAT5412KC-2  | 2MHz              | 68 dB            | ± 1/2 LSB | 0 to 70°C     | 40-pin Ceramic SB DIP |

| CAT5412JCI-1 | 1MHz              | 65 dB            | ±1 LSB    | -40 to +85°C  | 40-pin Ceramic SB DIP |

| CAT5412KCI-1 | 1MHz              | 68 dB            | ±1/2 LSB  | -40 to +85°C  | 40-pin Ceramic SB DIP |

| CAT5412JCI-2 | 2MHz              | <b>65</b> dB     | ±1 LSB    | -40 to +85°C  | 40-pin Ceramic SB DIP |

| CAT5412KCI-2 | 2MHz              | 68 dB            | ±1/2 LSB  | -40 to +85°C  | 40-pin Ceramic SB DIP |

| CAT5412JCM-1 | 1MHz              | 65 dB            | TBD       | -55 to +125°C | 40-pin Ceramic SB DIP |

| CAT5412KCM-1 | 1 MHz             | 68 dB            | ±1 LSB    | -55 TO +125°C | 40-pin Ceramic SB DIP |

CAT5412 A/D Converter

**Preliminary**

### LIMITED WARRANTY

Devices sold by Catalyst Semiconductor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Catalyst Semiconductor, Inc. makes no warranty, express, statutory, implied, or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Catalyst Semiconductor, Inc. makes no warranty of merchantability or fitness for any purpose. Catalyst Semiconductor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Catalyst Semiconductor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Catalyst Semiconductor, Inc. product. No other circuits, patents or licenses are implied.

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Catalyst Semiconductor's products are not authorized for use as critical components in life support devices or systems.

- Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 9/89