# Complete 14-Bit 2.2 MSPS Monolithic A/D Converter

**AD878**

**FEATURES**

Monolithic 14-Bit 2.2 MSPS A/D Converter Low Power Dissipation: 500 mW

No Missing Codes Guaranteed

Differential Nonlinearity Error: 0.5 LSB

Complete: On-Chip Track-and-Hold Amplifier and

Voltage Reference

Signal-to-Noise and Distortion Ratio: 80 dB

Spurious-Free Dynamic Range: 85 dB

Out-of-Range Indicator 44-Pin PLCC

### PRODUCT DESCRIPTION

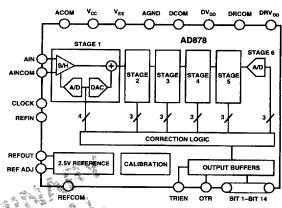

The AD878 is a monolithic 14-bit, 2.2 Msps analog-to-digital converter with an on-chip, high performance sample-and-hold amplifier and voltage reference. The AD878 uses a multistage pipelined architecture with factory programmed calibration circuitry and output error correction logic to provide 14-bit accuracy at 2.2 Msps data rates. The AD878 combines a merged high speed bipolar/CMOS process and a novel architecture to achieve the resolution and speed of hybrid implementations at a fraction of the power consumption. Additionally, the greater reliability of monolithic construction offers improved system reliability and lower costs than hybrid designs.

The high input impedance, fast-settling input sample-and-hold (S/H) amplifier is well suited for both multiplexed systems that switch negative to positive full-scale voltage levels in successive channels and sampling single-channel inputs at frequencies up to the Nyquist rate. The AD878's wideband input combined with the power and cost savings over previously available hybrids will allow new design opportunities in communications, imaging and medical applications. The AD878 provides both reference output and reference input pins, allowing the onboard reference to serve as a system reference. An external reference can also be substituted to suit the dc accuracy and temperature drift requirements of the application. A single clock input is used to control all internal conversion cycles. The digital output data is presented in binary output format. An out-of-range signal indicates an overflow condition. It can be used with the most significant bit to determine low or high overflow.

#### FUNCTIONAL BLOCK DIAGRAM

The AD878 is fabricated on Analog Devices' ABCMOS process which utilizes high speed bipolar and CMOS transistors on a single chip. High speed, precision analog circuits are now combined with high density logic circuits.

The AD878 is packaged in a 44-pin plastic leaded chip carrier (PLCC) package and is specified for operation from 0°C to +70°C and -40°C to +85°C.

### PRODUCT HIGHLIGHTS

The AD878 offers a complete single-chip sampling 14-bit, 2.2 Msps analog-to-digital conversion function in a 44-pin PLCC surface mount package.

Low Power: The AD878 at 650 mW max consumes a fraction of the power of presently available hybrids.

On-Chip Sample-and-Hold (S/H): The high impedance S/H input eliminates the need for external buffers.

Out of Range (OTR): The OTR output bit indicates when the input signal is beyond the AD878's input range.

Ease-of-Use: The AD878 is complete with S/H and voltage reference.

This is a preliminary data sheet. To obtain the most recent version or complete data sheet, call our fax retrieval system at 1-800-446-6212.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

REV. 0

■ 0816800 0043350 65T **■**

ANALOG-TO-DIGITAL CONVERTERS 2-173

### AD878-SPECIFICATIONS

## DC SPECIFICATIONS (T<sub>MIN</sub> to T<sub>MAX</sub> with $V_{CC}=+5$ V , $DV_{DD}=+5$ V, $DRV_{DD}=+5$ V, $V_{EE}=-5$ V, $f_{SAMPLE}=2.2$ Msps, unless otherwise noted)

| Parameter                                                                                                                                                             | J Grade <sup>1</sup>               | A Grade <sup>1</sup>               | Units                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| RESOLUTION                                                                                                                                                            | 14                                 | 14                                 | Bits min                                                                                                                          |

| MAX CONVERSION RATE                                                                                                                                                   | 2.2                                | 2.2                                | MHz min                                                                                                                           |

| ACCURACY Integral Nonlinearity (INL) Differential Nonlinearity (DNL) No Missing Codes Zero Error (@ +25°C) <sup>2</sup> Gain Error (@ +25°C) <sup>2</sup>             | ±2.5<br>±0.5<br>14<br>±TBD<br>±TBD | ±2.5<br>±0.5<br>14<br>±TBD<br>±TBD | LSB typ<br>LSB typ<br>Bits Guaranteed<br>% FSR max<br>% FSR max                                                                   |

| TEMPERATURE DRIFT <sup>3</sup> Zero Error Gain Error <sup>3, 4</sup> Gain Error <sup>3, 5</sup>                                                                       | ±TBD<br>±TBD<br>±TBD               | ±TBD<br>±TBD<br>±TBD               | % FSR max<br>% FSR max<br>% FSR max                                                                                               |

| POWER SUPPLY REJECTION <sup>6</sup> $V_{CC} (+5 \text{ V} \pm 0.25 \text{ V})$ $DV_{DD} (+5 \text{ V} \pm 0.25 \text{ V})$ $V_{EE} (-5 \text{ V} \pm 0.25 \text{ V})$ | ±TBD<br>±TBD<br>±TBD               | ±TBD<br>±TBD<br>±TBD               | % FSR max<br>% FSR max<br>% FSR max                                                                                               |

| ANALOG INPUT Input Range Input Resistance Input Capacitance                                                                                                           | ±2.5<br>1                          | ±2.5<br>1                          | Volts max MΩ typ pF typ                                                                                                           |

| INTERNAL VOLTAGE REFERENCE Output Voltage Output Voltage Tolerance Output Current (Available for External Loads) (External Load Should Not Change During Conversion)  | 2.5<br>±25<br>2.5                  | 2.5<br>±25<br>2.5                  | Volts typ<br>mV max<br>mA typ                                                                                                     |

| REFERENCE INPUT RESISTANCE                                                                                                                                            | 2                                  | 2                                  | kΩ typ                                                                                                                            |

| POWER SUPPLIES Supply Voltages V <sub>CC</sub> V <sub>EE</sub> DV <sub>DD</sub> , DRV <sub>DD</sub> Supply Current                                                    | +5<br>-5<br>+5                     | +5<br>-5<br>+5                     | V (±5% V <sub>CC</sub> Operating) V (±5% V <sub>EE</sub> Operating) V (±5% DV <sub>DD</sub> , DRV <sub>DD</sub> Operating) mA max |

| IV <sub>CC</sub> IV <sub>EE</sub> IV <sub>E</sub>                                                                                                                     | 45                                 | 45                                 | mA max<br>mA max                                                                                                                  |

| IDRV <sub>DD,</sub> IDV <sub>DD</sub> POWER CONSUMPTION                                                                                                               | 500<br>650                         | 500<br>650                         | mW typ<br>mW max                                                                                                                  |

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

2-174 ANALOG-TO-DIGITAL CONVERTERS

- O816800 0043351 596 **-**

REV. 0

<sup>&</sup>lt;sup>1</sup>Temperature ranges are as follows: J Grade: 0°C to +70°C; A Grade: -40°C to +85°C.

<sup>&</sup>lt;sup>2</sup>Adjustable to zero with external potentiometers (See Zero and Gain Error Calibration section).

$<sup>^3+25^{\</sup>circ}\text{C}$  to  $T_{\text{MIN}}$  and  $+25^{\circ}\text{C}$  to  $T_{\text{MAX}}$ .

<sup>&</sup>lt;sup>4</sup>Includes internal voltage reference error.

<sup>&</sup>lt;sup>5</sup>Excludes internal reference drift.

<sup>&</sup>lt;sup>6</sup>Change in Gain Error as a function of the dc supply voltage.

Specification subject to change without notice.

### AC SPECIFICATIONS $(T_{MIN} \text{ to } T_{MAX} \text{ with } V_{CC} = +5 \text{ Y}, \text{ DV}_{DD} = +5 \text{ Y}, \text{ DRV}_{DD} = +5 \text{ Y}, V_{EE} = -5 \text{ Y}, f_{SAMPLE} = 2.2 \text{ Msps.}$ unless otherwise noted)<sup>1</sup>

| Parameters                                    | J Grade | A Grade | Units      |

|-----------------------------------------------|---------|---------|------------|

| SIGNAL-TO-NOISE AND DISTORTION RATIO (S/N+D)  |         |         |            |

| $f_{INPUT} = 100 \text{ kHz}$                 | 80      | 80      | dB typ     |

|                                               | TBD     | TBD     | dB min     |

| $f_{INPUT} = 1 MHz$                           | TBD     | TBD     | dB typ     |

| TOTAL HARMONIC DISTORTION (THD)               |         |         |            |

| $f_{INPUT} = 100 \text{ kHz}$                 | -83     | -83     | dB typ     |

|                                               | TBD     | TBD     | dB max     |

| $f_{INPUT} = 1.0 \text{ MHz}$                 | TBD     | TBD     | dB typ     |

| SPURIOUS FREE DYNAMIC RANGE (SFDR)            |         |         |            |

| $f_{INPUT} = 100 \text{ kHz}$                 | 85      | 85      | dB typ     |

| INTERMODULATION DISTORTION (IMD) <sup>2</sup> |         | .,,     |            |

| Second Order Products                         | 80      | 80      | dB typ     |

| Third Order Products                          | 80      | 80      | dB typ     |

| FULL POWER BANDWIDTH                          | 2.0     | 2.0     | MHz typ    |

| SMALL SIGNAL BANDWIDTH                        | 5       | 5       | MHz typ    |

| APERTURE DELAY                                | TBD     | TBD     | ns typ     |

| APERTURE JITTER                               | 20      | TBD     | ps rms typ |

| ACQUISITION TO FULL-SCALE STEP                | 200     | 200     | ns typ     |

| OVERVOLTAGE RECOVERY TIME                     | ТВД     | TBD     | ns typ     |

#### NOTES

###

| Parameters                                              | Symbol                     | J, A Grades | Units  |

|---------------------------------------------------------|----------------------------|-------------|--------|

| LOGIC INPUTS                                            |                            |             |        |

| High Level Input Voltage                                | $V_{IH}$                   | +3.8        | V min  |

| Low Level Input Voltage                                 | $V_{IL}$                   | +0.95       | V max  |

| High Level Input Current $(V_{IN} = DV_{DD})$           | I <sub>IH</sub>            | ±10         | μA max |

| Low Level Input Current $(V_{IN} = 0 \text{ V})$        | I <sub>IL</sub>            | ±10         | uA max |

| Input Capacitance                                       | $\widetilde{C_{	ext{IN}}}$ | 5           | pF typ |

| LOGIC OUTPUTS                                           |                            |             |        |

| High Level Output Voltage ( $I_{OH} = 0.5 \text{ mA}$ ) | $v_{oh}$                   | +2.4        | V min  |

| Low Level Output Voltage ( $I_{OL} = 1.6 \text{ mA}$ )  | $V_{OL}$                   | +0.4        | V max  |

| Output Capacitance                                      | C <sub>OUT</sub>           | 5           | pF typ |

Specifications subject to change without notice.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

REV. 0

**■** 0816800 0043352 422 **■**

ANALOG-TO-DIGITAL CONVERTERS 2-175

<sup>16,</sup> amplitude = -0.5 dB full scale unless otherwise indicated. All measurements referred to a 0 dB (2.5 V pk) input signal unless otherwise indicated.

$<sup>^{2}</sup>$ fa = 100 kHz, fb = 95 kHz with  $f_{SAMPLE}$  = 2.2 MHz.

Specifications subject to change without notice.

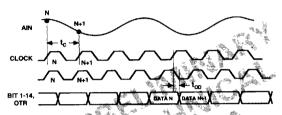

## SWITCHING SPECIFICATIONS $^{(T_{MIN}}$ to $T_{MAX}$ with $V_{cc}=+5$ V, $DV_{DD}=+5$ V, $DRV_{DD}=+5$ V, $V_{EE}=-5$ V; $V_{IL}=0.95$ V, $V_{IH}=5$ SWITCHING SPECIFICATIONS $^{(T_{MIN})}$ to $^{(T_{MIN})}$ to

| Parameters                    | Symbol J, A Grades                    |     | Units                |  |

|-------------------------------|---------------------------------------|-----|----------------------|--|

| Clock Period <sup>1</sup>     | t <sub>C</sub>                        | 455 | ns min               |  |

| CLOCK Pulse Width High        | t <sub>CH</sub>                       | 227 | ns min               |  |

| CLOCK Pulse Width Low         | t <sub>CL</sub>                       | 227 | ns min               |  |

| Clock Duty Cycle <sup>2</sup> |                                       | TBD | % min (50% typ)      |  |

| Clock Daily Cycle             |                                       | TBD | % max                |  |

| Output Delay                  | t <sub>OD</sub>                       | 20  | ns min               |  |

| Pipeline Delay (Latency)      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 4   | Clock Cycles max     |  |

| Data Access Time              | t <sub>DD</sub>                       | TBD | ns typ (100 pF Load) |  |

| Output Float Delay            | t <sub>HL</sub>                       | TBD | ns typ (10 pF Load)  |  |

### NOTES

Specifications subject to change without notice.

Figure 1. Timing Diagram

### ABSOLUTE MAXIMUM RATINGS

|                     | With        |          |                  |       |  |

|---------------------|-------------|----------|------------------|-------|--|

| Parameter           | Respect to  | Min      | Max              | Units |  |

| $\overline{v_{cc}}$ | ACOM        | -0.5     | +6.5             | Volts |  |

| $V_{EE}$            | ACOM        | -6.5     | +0.5             | Volts |  |

| $DV_{DD}$           | DCOM        | -0.5     | +6.5             | Volts |  |

| $DRV_{DD}$          | DRCOM       | -0.5     | +6.5             | Volts |  |

| ACOM                | DCOM        | -1.0     | +1.0             | Volts |  |

| AINCOM              | ACOM        | -1.0     | +1.0             | Volts |  |

| REFCOM              | ACOM        | -1.0     | +1.0             | Volts |  |

| DRCOM               | DCOM        | -1.0     | +1.0             | Volts |  |

| $V_{CC}$            | $DV_{DD}$   | -6.5     | +6.5             | Volts |  |

| Clock Input         | DCOM        | -0.5     | $DV_{DD} + 0.5$  | Volts |  |

| Digital Outputs     | DCOM        | -0.5     | $DRV_{DD} + 0.3$ | Volts |  |

| AIN, REF IN         | AGND        | TBD      | TBD              | Volts |  |

| REF IN              | $V_{CC}$    | $V_{EE}$ | 0                | Volts |  |

| REF IN              | $V_{EE}$    | 0        | $V_{CC}$         | Volts |  |

| Junction Temper     |             |          | +150             | °C    |  |

| Storage Tempera     | ature       | -65      | +150             | °C    |  |

| Lead Temperatu      | re (10 sec) |          | +300             | °C    |  |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may effect device reliability.

This information applies to a product under development. Its characteristics and specifications are subject to change without notice. Analog Devices assumes no obligation regarding future manufacture unless otherwise agreed to in writing.

2-176 ANALOG-TO-DIGITAL CONVERTERS

**2** 0816800 0043353 369 **2**

REV. 0

<sup>&</sup>lt;sup>1</sup>Conversion rate is operational to TBD without degradation in specified performance.

<sup>&</sup>lt;sup>2</sup>See Clock Input section for clock periods of TBD ns or greater.