# ATA00501D1C

# **AGC TRANSIMPEDANCE AMPLIFIER**

**SONET OC-1 Preliminary** REV 4

# **APPLICATIONS**

- **SONET OC-1 Receiver**

- **FITL**

- Low Noise RF Amplifier

### **FEATURES**

- Single +5 Volt Supply

- **Automatic Gain Control**

- **Excellent Sensitivity**

- 0 dBm Optical Overload

**ELECTRICAL CHARACTERISTICS** (1) ( $T_A$ = 25°C, VDD=+5.0V ± 10%,  $C_{DIODE}$ + $C_{STRAY}$  = 0.5 pF, Det. Cathode to  $I_{IN}$ )

| PARAMETER                                            | MIN   | ТҮР   | MAX   | UNIT               |

|------------------------------------------------------|-------|-------|-------|--------------------|

| Transresistance (R <sub>I</sub> =□,Idc<500nA)        |       | 55    |       | K□                 |

| Transresistance (R <sub>I</sub> =50□) <sup>(1)</sup> | 15    | 28    |       | K□                 |

| Bandwidth -3dB                                       | 50    | 70    |       | MHz                |

| Input Resistance (2)                                 |       | 1500  |       |                    |

| Output Resistance                                    | 30    | 50    | 60    |                    |

| Supply Current                                       |       | 30    | 45    | mA                 |

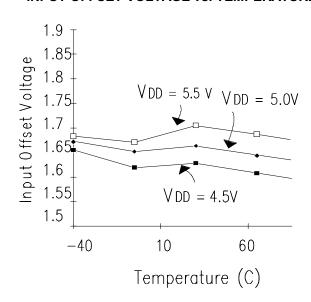

| Input Offset Voltage                                 | 1.5   | 1.6   | 1.9   | Volts              |

| Output Offset Voltage                                |       | 1.8   |       | Volts              |

| AGC Threshold (I <sub>IN</sub> ) (3)                 | 5     | 10    |       | μΑ                 |

| Optical Overload (4)                                 | -3    | 0     |       | dBm                |

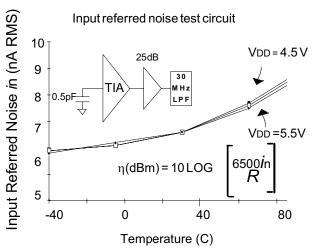

| Input Noise Current (5)                              |       | 7     | 12    | nA RMS             |

| AGC Time Constant (6)                                |       | 16    |       | □sec               |

| Offset Voltage Drift                                 |       | 1     |       | mV/ <sup>O</sup> C |

| Optical Sensitivity (7)                              | - 40  | - 43  |       | dBm                |

| Operating Voltage Range                              | + 4.5 | + 5.0 | + 6.0 | Volts              |

| Operating Temperature Range                          | - 40  |       | 85    | ° C                |

- 1) f=50MHz

- 2) Measured with I<sub>IN</sub> below AGC Threshold. During AGC, input impedance will decrease proportionally to I<sub>IN</sub>.

3) Defined as the I<sub>IN</sub> where Transresistance has decreased by 50%.

- 4) See note on "Indirect Measurement of Optical Overload".

- 5) See note on "Measurement of Input Referred Noise Current".

- 6)  $C_{AGC} = 220 pF$

- 7) Parameter is guaranteed (not tested) by design and characterization data @ 51Mb/s, assuming detector responsivity of 0.9

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD1</sub> | 7.0 V                          |

|------------------|--------------------------------|

| $V_{DD2}$        | 7.0 V                          |

| I <sub>IN</sub>  | 5 mA                           |

| T <sub>A</sub>   | Operating Temp 40 °C to 125 °C |

| T <sub>S</sub>   | Storage Temp 65 °C to 150 °C   |

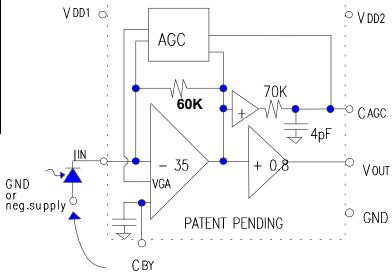

# ATA00501D1C EQUIVALENT CIRCUIT

Photodector cathode must be connected to IIN for proper AGC operation

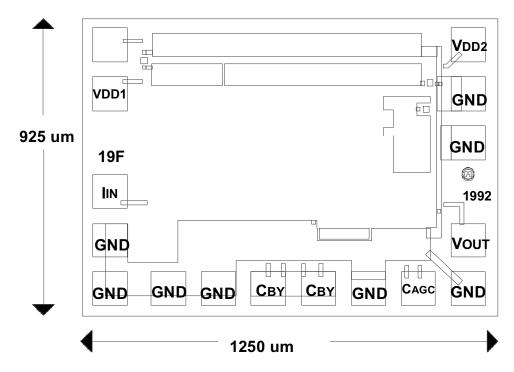

# ATA00501D1C PAD DESCRIPTION

| PAD              | Description                       | Comment                                       |

|------------------|-----------------------------------|-----------------------------------------------|

| V <sub>DD1</sub> | V <sub>DD1</sub>                  | Positive supply for input gain stage          |

| V <sub>DD2</sub> | V <sub>DD2</sub>                  | Positive supply for second gain stage         |

| I <sub>IN</sub>  | TIA Input Current                 | Connect detector cathode for proper operation |

| VOUT             | TIA Output Voltage                | Requires external DC block                    |

| C <sub>AGC</sub> | External AGC Capacitor            | 70K * C <sub>AGC</sub> = AGC time constant    |

| C <sub>BY</sub>  | Input gain stage bypass capacitor | >56 pF                                        |

# POWER SUPPLIES AND GENERAL LAYOUT CONSIDERATIONS

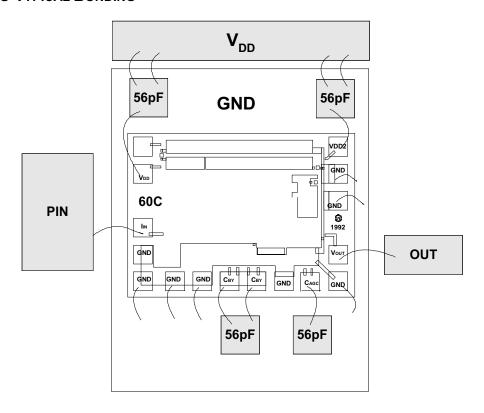

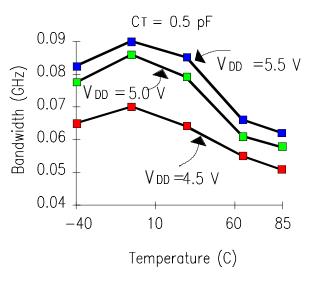

The ATA00501D1C may be operated from a positive supply as low as +4.5 V and as high as +6.0 V. Below +4.5 V, bandwidth, overload and sensitivity will degrade, while at +6.0 V, bandwidth, overload and sensitivity improve (see "Bandwidth vs. Temperature" curves). Use of surface mount (preferably MIM type capacitors), low inductance power supply bypass capacitors (>=56pF) are essential for good high frequency and low noise performance. The power supply bypass capacitors should be mounted on or connected to a good low inductance ground plane.

## GENERAL LAYOUT CONSIDERATIONS

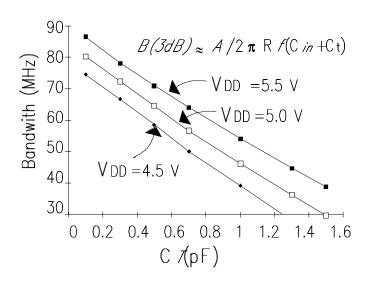

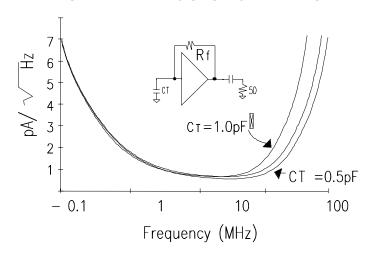

Since the gain stages of the transimpedance amplifier have an open loop bandwidth in excess of 1.0 GHz, it is essential to maintain good high frequency layout practices. To prevent oscillations, a low inductance RF ground plane should be made available for power supply bypassing. Traces that can be made short should be made short, and the utmost care should be taken to maintain very low capacitance at the photodiode-TIA interface ( $I_{\mbox{IN}}$ ), as excess capacitance at this node will cause a degradation in bandwidth and sensitivity (see Bandwidth vs.  $C_{\mbox{T}}$  curves).

# ATA00501D1C BONDING PADS

# ATA00501D1C TYPICAL BONDING

#### **BANDWIDTH vs. TEMPERATURE**

### **BANDWIDTH vs. CT**

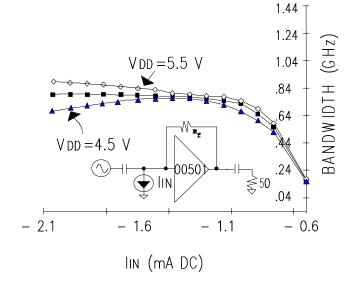

Note: All performance curves are typical @  $T_A$  =25 $^{\circ}$  C unless otherwise note.

# IN CONNECTION

(Refer to the equivalent circuit diagram.) Bonding the detector cathode to  $I_{IN}$  (and thus drawing current from the ATA00501) improves the dynamic range. Although the detector may be used in the reverse direction for input currents not exceeding 250  $\square$ A, the specifications for optical overload will not be met.

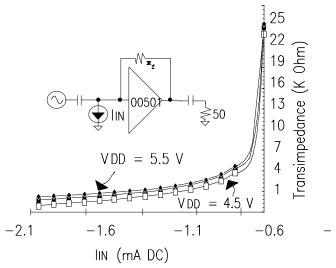

# TRANSIMPEDANCE vs. I<sub>IN</sub>

BANDWIDTH vs. I<sub>IN</sub>

# **VOLIT CONNECTION**

The output pad should be connected via a coupling capacitor to the next stage of the receiver channel (filter or decision circuits), as the output buffers are not designed to drive a DC coupled 50 ohm load (this would require an output bias current of approximately 36 mA to maintain a quiescent 1.8 Volts across the output load). If V OUT is connected to a high input impedance decision circuit (>500 ohms), then a coupling capacitor may not be required, although caution should be exercised since DC offsets of the photo detector/TIA combination may cause clipping of subsequent gain or decision circuits.

### INPUT OFFSET VOLTAGE vs. TEMPERATURE

# **CBY CONNECTION**

The C<sub>BY</sub> pad must be connected via a low inductance path to a surface mount capacitor of at least 56pF (additional capacitance can be added in <u>parallel</u> with the 56 pF or 220 pF capacitors to improve low frequency response and noise performance). Referring to the equivalent circuit diagram and the typical bonding diagram, it is critical that the connection from CBY to the bypass capacitor use two bond wires for low inductance, since any high frequency impedance at this node will be fed back to the open loop amplifier with a resulting loss of transimpedance bandwidth. Two pads are provided for this purpose

## **SENSITIVITY AND BANDWIDTH**

In order to guarantee sensitivity and bandwidth performance, the TIA is subjected to a comprehensive series of tests at the die sort level (100% testing at 25 °C) to verify the DC parametric performance and the high frequency performance (i.e. adequate |S21|) of the amplifier. Acceptably high |S21| of the internal gain stages will ensure low amplifier input capacitance and hence low input referred noise current. Transimpedance sensitivity and bandwidth are then guaranteed by design and correlation with RF and DC die sort test results.

# INDIRECT MEASUREMENT OF OPTICAL OVERLOAD

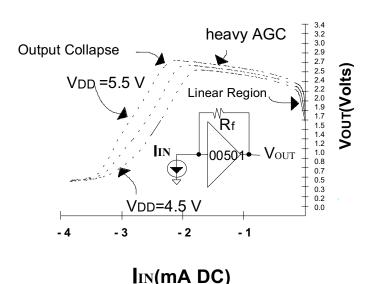

Optical overload can be defined as the maximum optical power above which the BER (bit error rate) increases beyond 1 error in  $10^{10}$  bits. The ATA00501D1C is 100% tested at die sort by a DC measurement which has excellent correlation with an PRBS optical overload measurement. The measurement consists of sinking a negative current (see  $V_{OUT}$  vs  $I_{IN}$  figure) from the TIA and determining the point of output voltage collapse. Also the input node virtual ground during "heavy AGC" is checked to verify that the linearity (i.e. pulse width distortion) of the amplifier has not been compromised.

## MEASUREMENT OF INPUT REFERRED NOISE CURRENT

The "Input Noise Current" is directly related to sensitivity. It can be defined as the output noise voltage (Vout), with no input signal, (including a 30 MHz lowpass filter at the output of the TIA) divided by the AC transresistance.

### **AGC CAPACITOR**

It is important to select an external AGC capacitor of high quality and appropriate size. The ATA00501D1C has an on-chip 70 K□ resistor with a shunt 4 pF capacitor to ground. Without external capacitance the chip will provide an AGC time constant of 280 nS. For the best performance in a typical 51MB/s SONET receiver, a minimum AGC capacitor of 56pF is recommended. This will provide the minimum amount of protection against pattern sensitivity and pulse width distortion on repetitive data sequences during high average optical power conditions. Conservative design practices should be followed when selecting an AGC capacitor, since unit to unit variability of the internal time constant and various data conditions can lead to data errors if the chosen value is too small.

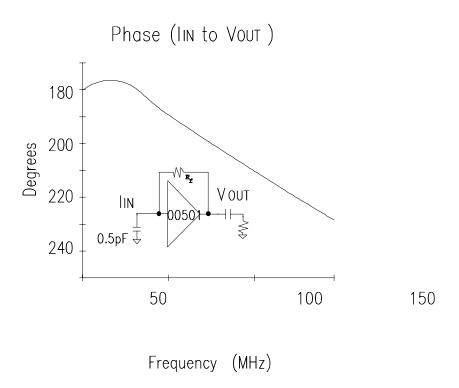

### PHASE RESPONSE

At frequencies below the 3dB bandwidth of the device, the transimpedance phase response is characteristic of a single pole transfer function (as shown in the Phase vs Frequency curve). The output impedance is essentially resistive up to 1000 MHz.

#### INPUT REFERRED NOISE SPECTRAL DENSITY

# INPUT REFERRED NOISE vs. TEMPERATURE

# ANADIGICS, Inc.

35 Technology Drive Warren, New Jersey 07059 Tel: (908) 668-5000 Fax: (908) 668-5132

Mktg@anadigics.com

# IMPORTANT NOTICE

ANADIGICS, Inc. reserves the right to make changes to its products or discontinue any product at any time without notice. The Advanced Product data sheets and product specifications contained in this data sheet are subject to change prior to a products formal introduction. The information in this data sheet has been carefully checked and is assumed to be reliable. However, ANADIGICS assumes no responsibility for inaccuracies. ANADIGICS strongly urges customers to verify that the information they are using is current before placing orders.

#### WARNING

ANADIGICS products are not intended for use in life support appliances, devices, or systems. Use of an ANADIGICS product in any such application without written consent is prohibited.