# PLS105-40, PLSCE105H-37

## Advanced Micro Devices

# 28-Pin TTL/CMOS Programmable Logic Sequencer

## DISTINCTIVE CHARACTERISTICS

- Field-programmable replacement for sequential control logic

- Advanced Mealy state machine/sequencer architecture

- Programmable AND/programmable OR array for flexibility

- Full drive: 24 mA loL, three-state outputs

- Dedicated hardware features to enhance testability

- Diagnostic Mode access to buried state register

- Register Preload and Power-up Preset of all flip-flops

- User-programmable pin for asynchronous flip-flop Preset/Output Enable

- Automatic "Hold" state via S-R flip-flops

- Security bit hides proprietary designs from competitors

- Supported by PALASM<sup>®</sup> software and standard PLD programmers

- Available in 28-pin plastic SKINNYDIP<sup>®</sup> and PLCC packages

- Fabricated with high-performance bipolar and electrically erasable CMOS technology

## GENERAL DESCRIPTION

The PLS105 is a field-programmable replacement for sequential logic. The device functions as a Mealy state machine with a registered output. The PLS105 utilizes the familiar AND/OR PLA logic structure to implement sum-of-product equations. Both arrays are user-programmable to implement transition terms causing changes in the internal state register or output register. The PLS105-40 device is fabricated in Advanced Micro Devices' advanced oxide-isolated bipolar process. The

PLSCE105H-37 device is fabricated in a high-speed, EE CMOS process; it offers significant power improvement (Icc of 100 mA) over competing parts.

The PLS105 device is fully supported by industry-standard CAD tools, including the PALASM design software package. Device programming is accomplished by using standard PLD programmers.

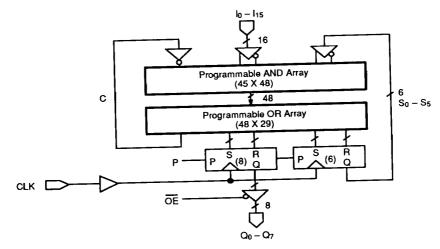

### **BLOCK DIAGRAM**

10250-001A

PALASM and SKINNYDIP are registered trademarks of Advanced Micro Devices.

This part is covered by verious U.S. and foreign patents owned by Advanced Micro Devices

Publication # 10250 Rev. D Amendment /0

Issue Date: January 1990

3-3

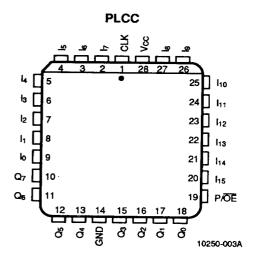

### **CONNECTION DIAGRAMS**

#### SKINNYDIP ськ П 28 🗍 Vcc l7 🛮 2 27 la le [] 3 26 🛮 b ls 25 110 24 1 111 5 13 F 112 23 22 I l<sub>13</sub> l<sub>2</sub> d В 21 111 ol 0 9 20 ] l<sub>15</sub> Q7 [] 10 19 P/OE Q6 [] 11 18 🛮 Q<sub>0</sub> Q5 12 17 🛮 Q1 Q4 [] 13 16 🛛 Q<sub>2</sub> GND 15 🛮 Qз

Note: Pin 1 is marked for orientation

10250-002A

### **PIN DESIGNATIONS**

CLK Output/state register clock

GND Ground

lo-l<sub>15</sub> Inputs to AND array P/OE Programmable asynchronous function pin;

default is active-high Preset (all registers go HIGH), programmed is active-low

**Output Enable**

Q<sub>0</sub>-Q<sub>7</sub> Output register outputs

Vcc Supply Voltage

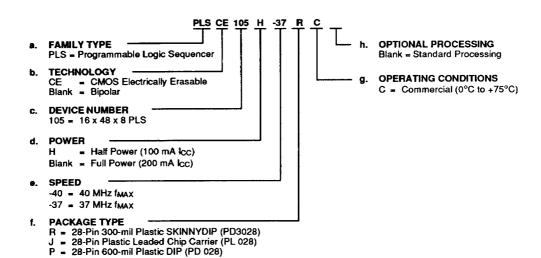

### ORDERING INFORMATION **Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

- a. Family Type

- b. Technology

- c. Device Number

- d. Power

- e. Speed

- f. Package Type g. Operating Conditions

- h. Optional Processing

| Valid Combinations |            |  |  |  |

|--------------------|------------|--|--|--|

| PLSCE105H-37       | DC 10 DC   |  |  |  |

| PLS105-40          | RC, JC, PC |  |  |  |

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

Note: Marked with AMD logo.

## FUNCTIONAL DESCRIPTION State Machine Implementation

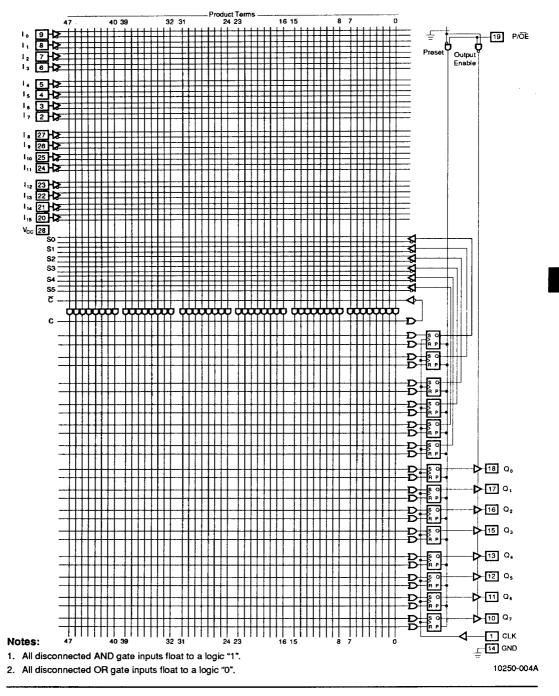

State machines contain conditional input logic, state memory and output generation logic. The PLS105 device is built around a programmable AND/OR logic array which serves as both conditional input and output generation logic. Forty-eight product or transition terms are found in the AND array. The AND array is driven from several sources: there are sixteen external inputs, six internal feedback signals from the buried state registers, and the complement term.

The OR array drives the output registers, buried state registers, and the complement array term. The PLS105 device offers eight output registers and six buried state registers.

## **Architectural Details**

| Architectural | Detail | <del></del> - | Fig. Flore | Outputs |

|---------------|--------|---------------|------------|---------|

| Part Number   | Pins   | Inputs        | Flip-Flops | Output  |

| PLS105        | 28     | 16            | 14         | L       |

# State and Output Registers

The state and output registers are both implemented with edge-triggered S-R type flip-flops. If neither input is active, the flip-flop will retain its contents when clocked. This free "hold" state saves product terms. The registers may change only on the LOW-to-HIGH transition of the clock pulse. There are eight output registers and six buried state registers on the device.

# Logic Implementation

All transition terms can include True, False, or Don't Care states of the controlling variables. The OR array merges one or more product terms to generate the desired user logic functions for the output and next-state registers. This sharing of OR-terms minimizes the overall logic required to implement complicated control functions.

# **Complement Array Term**

An internal variable (C) known as the complement array term directly implements the "else" logic clause at any state. This often reduces the number of product terms required for a conditional "else" transition. The complement array can also be used for illegal state recovery and designing modulo counters.

### Initialization

Starting the state machine in a known state is facilitated by power-up preset circuitry which unconditionally loads a "1" into each flip-flop during power-up or by using the asynchronous Preset function. Synchronous transitions to the initial state can be made by having an input be an OR term on all the state register S inputs, and ANDing its complement with all of the R logic terms. Whenever this input is active the machine will synchronously change to the state with all outputs high.

## **Output Enable**

The Preset input can be converted to a three-state Output Enable function by an architecture bit. Expansion to larger control functions can be accommodated by connecting several PLS devices to a control bus and selectively enabling them to each handle a segment of the control algorithm. This user-programmable option is specified as an auxiliary equation in the design file or optionally by use of a keyword.

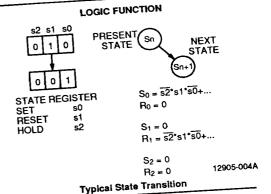

## **Typical Operation**

The details of device operation may be illustrated by the simple state transition indicated. The state register initially contains 010 and will become 001 after the next clock. For this to occur, state bit 0 must be set, state bit 1 must be reset and state bit 2 must hold its value. The transition term fragments listed produce this result. The So and R1 product terms detect the bit pattern for the current state (010) and produce a logic one. All other terms evaluate to a zero, producing the transition to state 001.

## Security Bit

A security bit is provided on the PLS 105 as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors.

On the PLSCE105, programming and verification are also defeated by the security bit. The bit can only be erased in conjunction with the array during an erase cycle. The security bit also prevents preload and observability.

# **Programming and Erasing**

The PLS105 can be programmed on standard logic programmers. Approved programmers are listed in the Programmer Reference Guide.

The PLSCE105 may be erased to reset a previously configured device back to its virgin state. Erasure is automatically performed by the programming hardware. No special erase operation is required.

**PLS105**

### **LOGIC DIAGRAM**

PLS105 3-7

## ABSOLUTE MAXIMUM RATINGS

-65°C to +150°C Storage Temperature

Ambient Temperature with

-55°C to +125°C **Power Applied**

Supply Voltage with Respect

-0.5 V to +7.0 V to Ground -0.5 V to +5.5 V DC Input Voltage

-30 mA to +5 mA DC Input Current

DC Output or I/O Pin

-0.5 to Vcc Max. Voltage

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

Commercial (C) Devices

Ambient Temperature (TA)

0°C to +75°C Operating in Free Air

Supply Voltage (Vcc) with

+4.75 V to +5.25 V Respect to Ground

Operating Ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                    | Min. | Мах. | Unit |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|

| Vон                 | Output HIGH Voltage                      | I <sub>OH</sub> = -3.2 mA V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> V <sub>CC</sub> = Min.              | 2.4  |      | ×    |

| Vol                 | Output LOW Voltage                       | I <sub>OL</sub> = 24 mA V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> V <sub>CC</sub> = Min.                |      | 0.5  | ٧    |

| V <sub>IH</sub>     | Input HIGH Voltage                       | Guaranteed Input Logical HIGH Voltage for all Inputs (Note 1)                                                      | 2.0  | 5.5  | ٧    |

| VIL                 | input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                    |      | 0.8  | V    |

| Vı                  | Input Clamp Voltage                      | I <sub>IN</sub> = -18 mA, V <sub>CC</sub> = Min.                                                                   |      | -1.2 | V    |

| JIH.                | Input HIGH Current                       | V <sub>IN</sub> = 2.4 V, V <sub>CC</sub> = Max. (Note 2)                                                           |      | 20   | μΑ   |

| I <sub>IL</sub>     | Input LOW Current                        | V <sub>IN</sub> = 0.4 V, V <sub>CC</sub> = Max. (Note 2)                                                           |      | -250 | μА   |

|                     | Maximum Input Current                    | V <sub>IN</sub> = 5.5 V, V <sub>CC</sub> = Max.                                                                    |      | 25   | μА   |

| Іохн                | Off-State Output Leakage<br>Current HIGH | V <sub>CUT</sub> = 2.7 V, V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> (Note 2) |      | 20   | μА   |

| lozL                | Off-State Output Leakage Current LOW     | V <sub>OUT</sub> = 0.4 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> (Note 2)  |      | 20   | μА   |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max. (Note 3)                                                          | -30  | -130 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (I <sub>OUT</sub> = 0 mA)<br>V <sub>CC</sub> = Max.                            |      | 200  | mA   |

#### Notes:

- 1. These are absolute values with respect to the device ground and all overshoots due to system and tester noise are included.

- 2. I/O pin leakage is the worst case of  $l_{\rm IL}$  and  $l_{\rm OZL}$  (or  $l_{\rm IH}$  and  $l_{\rm OZH}$ ).

- 3. Not more than one output should be tested at a time. Duration of the short-circuit test should not exceed one second. Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

PLS105-40 (Com'l)

### **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description            | Test Conditions          |                                                     | Тур. | Unit |

|---------------------|----------------------------------|--------------------------|-----------------------------------------------------|------|------|

| CiN                 | Input Capacitance CLK, OE Others | V <sub>IN</sub> = 2.0 V  | V <sub>CC</sub> = 5.0 V,<br>T <sub>A</sub> = +25°C, | 7    | pF   |

| Солт                | Output Capacitance               | V <sub>OUT</sub> = 2.0 V | f = 1 MHz                                           | 8    |      |

### Note:

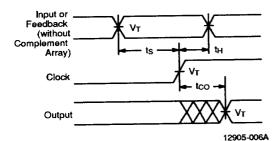

## SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

| Parameter<br>Symbol | Parameter Des         | scription                                           |                  |      |               | Min. | Max. | Unit |

|---------------------|-----------------------|-----------------------------------------------------|------------------|------|---------------|------|------|------|

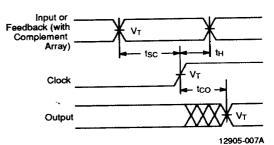

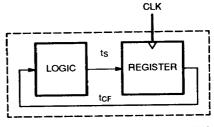

| ts                  | Setup Time fro        | Input or Feedback to Clock Without Complement Array |                  |      |               | 15   |      | ns   |

| tsc                 | Setup Time fro        | m Input or Feedback to Clock With Complement Array  |                  |      |               | 30   |      | ns   |

| t <sub>H</sub>      | Hold Time             |                                                     |                  |      |               | 0    |      | ns   |

| tco                 | Clock to Outpu        | Clock to Output                                     |                  |      |               |      | 10   | ns   |

| tcF                 | Clock to Feedb        | Clock to Feedback (Note 3)                          |                  |      |               |      | 3    | ns   |

| tap                 | Asynchronous          | Preset to Output                                    |                  |      |               |      | 15   | ns   |

| tapw                | Asynchronous          | nronous Preset Width                                |                  |      |               | 10   |      | ns   |

| tapr                | Asynchronous          | chronous Preset Recovery Time                       |                  |      |               | 8    |      | ns   |

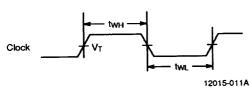

| twL                 |                       | LOW                                                 |                  |      |               | 8    |      | ns   |

| twn                 | Clock Width           | HIGH                                                |                  |      |               | 8    |      | ns   |

| fmax                |                       | External Feedback                                   | Without          |      | 1/(ts + tco)  | 40   |      | MHz  |

|                     | Maximum               | Internal Feedback                                   | Complen<br>Array | nent | 1/(ts + tcF)  | 55.5 |      | MHz  |

| fwaxc               | Frequency<br>(Note 4) | External Feedback                                   | With             |      | 1/(tsc + tco) | 25   |      | MHz  |

| - MAXC              |                       | Internal Feedback                                   | Complen<br>Array | nent | 1/(tsc+tcr)   | 30   |      | MHz  |

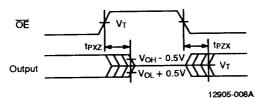

| tezx                | OE to Output I        | Enable                                              |                  |      |               |      | 15   | ns   |

| tpxz                | OE to Output I        | Disable                                             |                  |      |               |      | 10   | ns   |

#### Notes:

- 2. See Switching Test Circuit for test conditions.

- 3. Calculated from measured fMAX internal.

- 4. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

<sup>1.</sup> These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

Ambient Temperature with

Power Applied -55°C to +125°C

Supply Voltage with Respect

to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to +7.0 V

DC Output or I/O Pin

Voltage -0.5 V to +7.0 V

Static Discharge Voltage 2001 V

**Latchup Current**

$(T_A = 0^{\circ}C \text{ to } +75^{\circ}C)$  100 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

### Commercial (C) Devices

Ambient Temperature (T<sub>A</sub>)

Operating in Free Air 0°C to +75°C

Supply Voltage (Vcc) with

Respect to Ground +4.75 V to +5.25 V

Operating Ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                 | Min. | Max. | Unit |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>ОН</sub>     | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$ $V_{CC} = \text{Min.}$                          | 2.4  |      | ٧    |

| Vol                 | Output LOW Voltage                       | $I_{OL} = 24 \text{ mA}$ $V_{IN} = V_{IH} \text{ or } V_{IL}$ $V_{CC} = \text{Min.}$                            |      | 0.5  | ٧    |

| VIH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                                                | 2.0  |      | ٧    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 1)                                                 |      | 0.8  | ٧    |

| lн                  | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max. (Note 2)                                                       |      | 10   | μА   |

| l <sub>IL</sub>     | Input LOW Leakage Current                | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max. (Note 2)                                                          |      | -10  | μА   |

| Іохн                | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 5.25 \text{ V}, V_{CC} = \text{Max.},$<br>$V_{IN} = V_{IL} \text{ or } V_{IH} \text{ (Note 2)}$      |      | 10   | μА   |

| lozu                | Off-State Output Leakage<br>Current LOW  | V <sub>OUT</sub> = 0 V, V <sub>CC</sub> = Max.<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> (Note 2) |      | -10  | μА   |

| Isc                 | Output Short-Circuit<br>Current          | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max. (Note 3)                                                       | -30  | -130 | mA   |

| lcc                 | Supply Current                           | $V_{\text{IN}} = 0$ V, Outputs Open ( $I_{\text{OUT}} = 0$ mA) $V_{\text{CC}} = \text{Max}$ .                   |      | 100  | mA   |

#### Notes:

- 1. These are absolute values with respect to the device ground and all overshoots due to system and tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- Not more than one output should be tested at a time. Duration of the short-circuit test should not exceed one second.

VOUT = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

PLSCE105H-37 (Com'I)

### **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditions          |                                     | Тур. | Unit |

|---------------------|-----------------------|--------------------------|-------------------------------------|------|------|

| CiN                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V  | V <sub>CC</sub> = 5.0 V,            | 5    | pF   |

| Cour                | Output Capacitance    | V <sub>OUT</sub> = 2.0 V | T <sub>A</sub> = 25°C,<br>f = 1 MHz | 8    |      |

### Note:

## SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

| Parameter<br>Symbol | Parameter Des              | scription                                             |                  |      |                                       | Min. | Max. | Unit |

|---------------------|----------------------------|-------------------------------------------------------|------------------|------|---------------------------------------|------|------|------|

| ts                  | Setup Time fro             | n Input or Feedback to Clock Without Complement Array |                  |      |                                       | 17   |      | ns   |

| tsc                 | Setup Time fro             | om Input or Feedback to Clock With Complement Array   |                  |      |                                       | 30   |      | ns   |

| t <sub>H</sub>      | Hold Time                  | Hold Time                                             |                  |      |                                       | 0    |      | ns   |

| tco                 | Clock to Outpu             | Clock to Output                                       |                  |      |                                       |      | 10   | ns   |

| tcF                 | Clock to Feedback (Note 3) |                                                       |                  |      |                                       | 3    | ns   |      |

| tap                 | Asynchronous               | nchronous Preset to Output                            |                  |      |                                       |      | 15   | ns   |

| tapw                | Asynchronous               | synchronous Preset Width                              |                  |      |                                       | 10   |      | ns   |

| tapr                | Asynchronous               | chronous Preset Recovery Time                         |                  |      |                                       | 8    |      | ns   |

| tw.                 |                            | LOW                                                   |                  |      |                                       | 8    |      | ns   |

| twn                 | Clock Width                | HIGH                                                  |                  |      |                                       | 8    |      | ns   |

| fmax                |                            | External Feedback                                     | Without          |      | 1/(t <sub>S</sub> + t <sub>CO</sub> ) | 37   |      | MHz  |

|                     | Maximum                    | Internal Feedback                                     | Complet<br>Array | ment | 1/(ts + tcr)                          | 50   |      | MHz  |

| fMAXC               | Frequency<br>(Note 4)      | External Feedback                                     | With             |      | 1/(tsc + tco)                         | 25   |      | MHz  |

| IMAXC               | ,                          | Internal Feedback                                     | Complei<br>Array | ment | 1/(tsc+tcr)                           | 30   |      | MHz  |

| tpzx                | ŌĒ to Output B             | nable                                                 | -                |      |                                       |      | 15   | ns   |

| texz                | OE to Output [             | Disable                                               | .,               |      |                                       |      | 10   | ns   |

#### Notes:

- 2. See Switching Test Circuit for test conditions.

- 3. Calculated from measured fMAX internal.

- 4. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where frequency may be affected.

<sup>1.</sup> These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

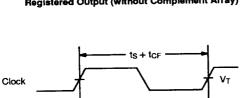

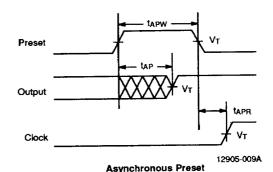

### SWITCHING WAVEFORMS

Registered Output (without Complement Array)

Clock to Feedback (f<sub>MAX</sub> Internal) See Path at Right

12149-025B

**Clock Width**

OE to Output Disable/Enable

Registered Output (with Complement Array)

12015-021A

### Notes:

- 1. VT = 1.5 V

- 2. Input pulse amplitude 0 V to 3.0 V.

- 3. Input rise and fall times 2-5 ns typical.

PLS105

3-12

### **KEY TO SWITCHING WAVEFORMS**

| WAVEFORM        | INPUTS                                 | OUTPUTS                                             |

|-----------------|----------------------------------------|-----------------------------------------------------|

|                 | Must be<br>Steady                      | Will be<br>Steady                                   |

|                 | May<br>Change<br>from H to L           | Will be<br>Changing<br>from H to L                  |

|                 | May<br>Change<br>from L to H           | Will be<br>Changing<br>from L to H                  |

|                 | Don't Care;<br>Any Change<br>Permitted | Changing,<br>State<br>Unknown                       |

| <b>&gt;&gt;</b> | Does Not<br>Apply                      | Center<br>Line is High-<br>Impedance<br>"Off" State |

KS000010-PAL

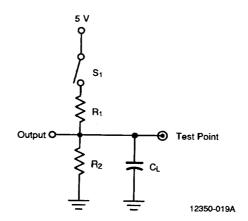

### **SWITCHING TEST CIRCUIT**

| Specification    | S <sub>1</sub>               | C∟    | R₁    | R <sub>2</sub> | Measured Output Value                                                            |

|------------------|------------------------------|-------|-------|----------------|----------------------------------------------------------------------------------|

| tco, tcf         | Closed                       |       |       |                | 1.5 V                                                                            |

| tpzx             | Z → H: Open<br>Z → L: Closed | 50 pF | 200 Ω | 390 Ω          | 1.5 V                                                                            |

| t <sub>PXZ</sub> | H → Z: Open<br>L → Z: Closed | 5 pF  |       |                | $H \rightarrow Z: V_{OH} \rightarrow 0.5 V$<br>$L \rightarrow Z: V_{OL} + 0.5 V$ |

PLS105

3-13

### **ENDURANCE CHARACTERISTICS**

The PLSCE105 is manufactured using AMD's advanced electrically erasable process. This technology uses an EE cell to replace the fuse link used in bipolar

parts. As a result, the device can be erased and reprogrammed – a feature which allows 100% testing at the factory.

### **Endurance Characteristics**

| Symbol          | Parameter                        | Min. | Units  | Test Conditions                                    |

|-----------------|----------------------------------|------|--------|----------------------------------------------------|

|                 | 10                               |      | Years  | Max. Storage<br>Temperature (150°C)                |

| t <sub>DR</sub> | Min. Pattern Data Retention Time | 20   | Years  | Max. Operating<br>Temperature<br>(Military; 125°C) |

| N               | Min. Reprogramming Cycles        | 100  | Cycles | Normal Programming Conditions                      |

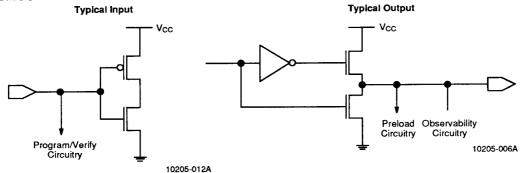

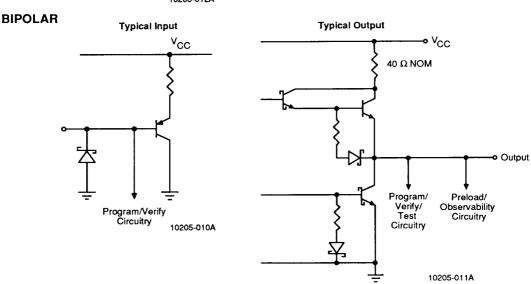

# INPUT/OUTPUT EQUIVALENT SCHEMATICS CMOS

3-14 PLS105

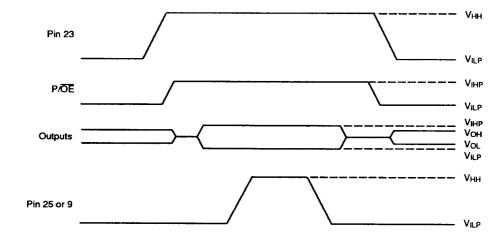

# OUTPUT REGISTER PRELOAD (Bipolar Only)

The preload function allows the register to be loaded from the output pins. This feature aids functional testing of sequential designs by allowing direct setting of output states. The procedure for preloading follows.

- 1. Raise  $V_{CC}$  to 5.0 V  $\pm$  0.5 V.

- 2. Raise pin 23 to V<sub>HH</sub>.

- 3. Disable output pins by raising P/OE to VIHP.

- 4. Apply VIHP/VILP as desired to all output pins.

- Pulse pin 25 or pin 9 from V<sub>ILP</sub> to V<sub>HH</sub> and back to V<sub>ILP</sub>. Pin 25 will preload output registers while pin 9 will preload buried state registers.

- 6. Remove VILP/VIHP from output pins.

- 7. Enable output pins by lowering P/OE pin to VILP.

- 8. Lower pin 23 to VILP.

| Parameter<br>Symbol | Parameter Description               | Min. | Rec. | Max. | Unit |

|---------------------|-------------------------------------|------|------|------|------|

| V <sub>HH</sub>     | Super-level input voltage           | 11.5 | 12   | 12.5 | V    |

| Vilp                | Low-level input voltage             | 0    | 0    | 0.5  | V    |

| ViHP                | High-level input voltage            | 2.4  | 5.0  | 5.5  | V    |

| to                  | Delay time                          | 1    |      |      | μs   |

| dV₁/dt              | V <sub>HH</sub> Rise Time Slew Rate | 10   |      | 100  | V/µs |

| dV₁/dt              | V <sub>HH</sub> Fall Time Slew Rate |      | 2.0  | 3.0  | V/µs |

| Preioad Data                         | Preloaded Register             |

|--------------------------------------|--------------------------------|

| Q <sub>0</sub> –Q <sub>7</sub>       |                                |

| D <sub>0</sub> D <sub>7</sub>        | Q <sub>0</sub> –Q <sub>7</sub> |

| D <sub>0</sub> -D <sub>5</sub> ,X, X | S <sub>0</sub> -S <sub>5</sub> |

10205-007A

#### **Output Register Preload Waveform**

PLS105 3-15

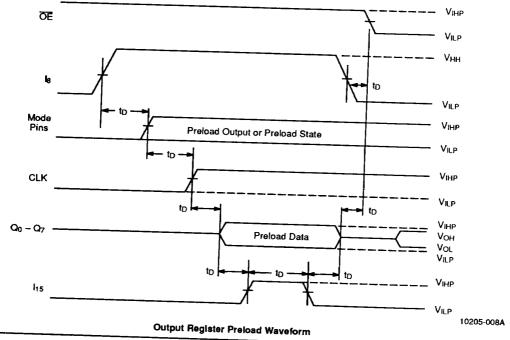

# OUTPUT REGISTER PRELOAD (CMOS Only)

The preload function allows the register to be loaded from the output pins. This feature aids functional testing of sequential designs by allowing direct setting of output states. The procedure for preloading follows.

- 1. Set OE to VIHP to disable outputs.

- 2. With Mode pins LOW raise Is to  $V_{HH}$ .

- 3. Use Mode pins to select Preload Output or Preload State.

- 4. Raise CLK to VIHP.

- Apply either V<sub>IHP</sub> or V<sub>ILP</sub> to all outputs. Use V<sub>IHP</sub> to preload a LOW in the flip-flop; use V<sub>ILP</sub> to preload a HIGH in the flop-flop.

- 6. Pulse  $I_{15}$  from  $V_{ILP}$  to  $V_{IHP}$  to  $V_{ILP}$ .

- 7. Remove preload data from outputs.

- 8. Lower Is to VILP.

- 9. Lower  $\overline{OE}$  to  $V_{ILP}$  to enable the outputs.

- Verify VoL/VoH at all outputs. To verify state registers, use the observability mode.

| Parameter<br>Symbol | Darameter December                  |       |      |       |      |  |

|---------------------|-------------------------------------|-------|------|-------|------|--|

|                     | Parameter Description               | Min.  | Rec. | Max.  | Unit |  |

| V <sub>HH</sub>     | Super-level input voltage           | 13.25 | 13.5 | 13.75 | -    |  |

| VILP                | Low-level input voltage             |       |      |       | V    |  |

| VIHP                | High-level input voltage            | 0     | 0    | 0.5   | / V  |  |

| to                  | Delay time                          | 4.0   | 5.0  | Vcc+1 | V    |  |

| dV₁/dt              | V <sub>HH</sub> Rise Time Slew Rate | 1     |      |       | μs   |  |

| dV₅/dt              | V <sub>HH</sub> Fall Time Slew Rate | 10    |      | 100   | V/µs |  |

|                     | THE SIEW Hate                       |       | 2.0  | 3.0   | V/us |  |

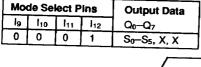

| Мо | de Se           | lect P | ins | Preload Data                        | Preloaded Register                    |

|----|-----------------|--------|-----|-------------------------------------|---------------------------------------|

| lg | I <sub>10</sub> | 111    | 112 | Q <sub>0</sub> -Q <sub>7</sub>      | · · · · · · · · · · · · · · · · · · · |

| 0  | 1               | 1      | 0   | D <sub>0</sub> D <sub>7</sub>       | Q <sub>0</sub> -Q <sub>7</sub>        |

| 1  | 1               | 1      | 0   | D <sub>0</sub> D <sub>5</sub> ,X, X | S <sub>0</sub> -S <sub>5</sub>        |

3-16 PLS105

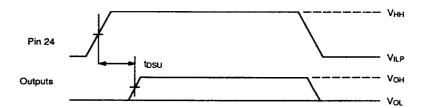

# OBSERVABILITY (Bipolar Only)

The observability function allows the state register to be sent to the output pins. This feature aids functional testing of sequential designs by allowing direct observation of the buried state register. The procedure for observability follows.

- 1. Apply V<sub>HH</sub> to pin 24.

- 2. Observe S<sub>0</sub>-S<sub>5</sub> on pins Q<sub>0</sub>-Q<sub>5</sub>.

| Parameter<br>Symbol | Parameter<br>Description  | Min. | Rec. | Мах. | Unit |

|---------------------|---------------------------|------|------|------|------|

| V <sub>HH</sub>     | Super-level input voltage | 11.5 | 12   | 12.5 | ٧    |

| tosu                | Delay time                | 250  |      |      | ns   |

10205-009A

**Observability Waveforms**

PLS105 3-17

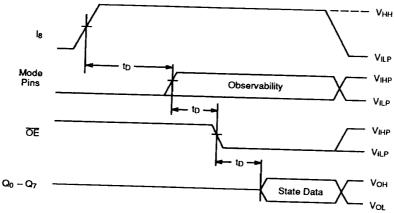

# OBSERVABILITY (CMOS Only)

The observability function allows the state register to be sent to the output pins. This feature aids functional testing of sequential designs by allowing direct observation of the buried state register. The procedure for observability follows.

1. Set OE to VIHP to disable outputs.

| 2. | With M | ode pins | LOW | raise | 18 | to | V <sub>HH</sub> |

|----|--------|----------|-----|-------|----|----|-----------------|

|----|--------|----------|-----|-------|----|----|-----------------|

- 3. Use Mode pins to select Observability.

- 4. Lower  $\overline{\text{OE}}$  to  $V_{\text{ILP}}$  to enable the state data to the outputs.

- 5. Lower Is to VILP.

**Observability Waveforms**

12905-012A

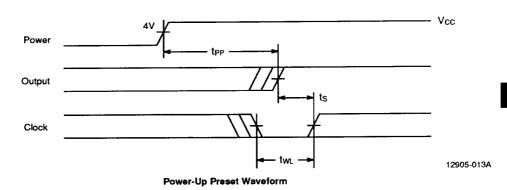

### **POWER-UP PRESET**

The power-up preset feature ensures that all flip-flops will be preset to HIGH after the device has been powered up. This feature is valuable in simplifying state machine initialization. A timing diagram and parameter table are shown below. Due to the synchronous operation of the power-up preset and the wide range of ways Vcc can rise to its steady state, two conditions are required to ensure a valid power-up preset. These conditions are:

- 1. The V<sub>CC</sub> rise must be monotonic.

- Following preset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

| Parameter<br>Symbol | Parameter Description        | Max.   | Unit      |

|---------------------|------------------------------|--------|-----------|

| tpp                 | Power-up Preset Time         | 1000   | ns        |

| ts                  | Input or Feedback Setup Time | See Sw | vitching  |

| twL                 | Clock Width LOW              | Charac | teristics |