# G5364 G5365

# **Microcircuits**

## **CMOS 8192 x 8 ROM**

#### Features

- Low power CMOS technology 200 μA Standby 15 mA Operating

- Single +5 volt power supply

- · Three-state data outputs

- Fully TTL compatible

- · User-selected power down

- · Output Enable (G5365)

- Three programmable chip selects (G5365)

- Pin compatible with 2764 EPROM (G5365)

### General Description

The GTE G5364/65 Read Only Memories are 8192-word by 8-bit devices with a maximum access time of 250 nanoseconds. The devices are manufactured using the state-of-the-art CMOS process. For both devices, a manufacturing mask stage defined by the user programs the non-volatile memory.

The 5364 is packaged in a 24-pin package which offers upward compatibility with the GTE 2316 and GTE 2332 ROMs. The user has the option of a  $\overrightarrow{CE}$  pin, which offers a power down feature, or a  $CS/\overrightarrow{CS}$  pin, which offers faster CS access times (tAcs).

The 5365 is packaged in the industry standard 28-pin package which offers campatibility with 64K EPROMs (2764). The user has the option of three user programmed CS/CE pins.

Bus-oriented application systems are catered for by the inclusion of three-state data outputs. The G5365 also provides an output enable to reduce system bus contention. The G5364/65s are available in both cerdip and plastic dual-in-line packages.

#### Pin Function

| Pin    | Description   |

|--------|---------------|

| A0-A12 | Address       |

| CE     | Chip Enable   |

| CS/CS  | Chip Select   |

| ŌĒ     | Output Enable |

| Pin         | Description          |

|-------------|----------------------|

| 01-08       | Outputs              |

| VDD         | +5 Volt Power Supply |

| <b>V</b> ss | Ground               |

| NC          | No Connection        |

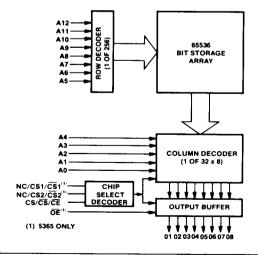

#### Block Diagram

#### Pin Configuration

# **PRELIMINARY INFORMATION**

Supplementary data may be published at a later date

# <del>a</del>

### **Absolute Maximum Ratings: (Note 1)**

| Parameter                                          | Symbol | Value          |  |  |

|----------------------------------------------------|--------|----------------|--|--|

| Voltage to Any Pin With<br>Respect to Vss (Note 9) | VDC    | -0.5V to 7.0V  |  |  |

| Current Into/From Output                           | IDD    | 50 mA          |  |  |

| Operation Ambient Temp.<br>Range                   | TA     | 0°C to 70°C    |  |  |

| Storage Temp. Range                                | Ts     | -65°C to 150°C |  |  |

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

DC Characteristics: VDD = 5.0V ±10%, TA = 0°C to 70°C

| Parameter                      | Symbol | Min  | Тур | Max  | Unit | Conditions      |

|--------------------------------|--------|------|-----|------|------|-----------------|

| Input High Level               | VIH    | 2.0  |     | VDD  | V    |                 |

| Input Low Level                | ViL    | -0.5 |     | +0.8 | V    |                 |

| Input Leakage Current          | lu     | -10  |     | +10  | μА   | Note 2          |

| Output Leakage Current         | ILO    | -10  |     | +10  | μА   | Note 3          |

| Output Voltage High            | Vон    | 2.4  |     |      | V    | IOH = -220 μA   |

| Output Voltage Low             | Vol    |      |     | 0.4  | V    | IOL = 3.3 mA    |

| Power Supply Current (Active)  | IDD    |      | 6   | 15   | mA   | Note 11         |

| Power Supply Current (Standby) | IDD    |      |     | 200  | μА   | Note 6          |

| Input Capacitance              | CIN    |      | 4   | 7    | pF   | Note 5          |

| Output Capacitance             | Соит   |      | 5   | 10   | pF   | Vo = 0V, Note 5 |

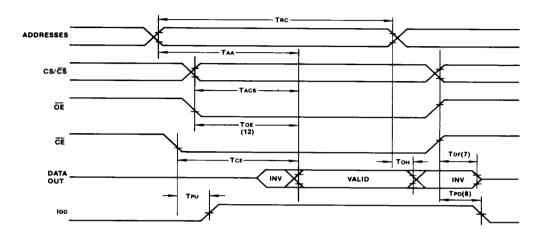

### AC Characteristics—Read Cycle: VDD = 5.0V ±10%, TA = 0° C to 70° C. See Notes 4, 10.

| Parameter                       | Symbol | -25 |     | -3  |     | -4  |     |       |            |

|---------------------------------|--------|-----|-----|-----|-----|-----|-----|-------|------------|

|                                 |        | Min | Max | Min | Max | Min | Max | Units | Conditions |

| Address Access Time             | TAA    |     | 250 |     | 300 |     | 450 | nS    |            |

| Read Cycle Time                 | TRC    | 250 |     | 300 |     | 450 |     | nS    |            |

| Chip Select Access Time         | TACS   |     | 100 |     | 120 |     | 150 | nS    |            |

| Output Enable to Output Delay   | TOE    |     | 100 |     | 120 |     | 150 | nS    | Note 12    |

| Chip Enable Access Time         | TCE    |     | 250 |     | 300 |     | 450 | nS    |            |

| Power Up Time                   | TPU    | 0   |     | 0   |     | 0   |     | nS    |            |

| Data Valid After Address Change | Тон    | 20  |     | 20  |     | 20  |     | nS    |            |

| Chip Deselect Delay Time        | TDF    | 0   | 110 | 0   | 130 | 0   | 150 | nS    | Note 7     |

| Power Down Time                 | TPD    |     | 60  |     | 60  |     | 100 | nS    | Note 8     |

### **Timing Diagram**

#### Notes:

- Exceeding these ratings may cause permanent damage, functional operation under these conditions is not implied.

- 2. VIN = 0V (VDD = 5.5V)

- 3. Devices unselected, Vout =0V to 5.5V (VDD = 5.5V)

- Measured with two TTL loads and 100 pF (transition times = 10 nS)

- Capacitance measured with Boonton meter or effective capacitance calculated from the equation:

$$C = \frac{\triangle Q}{\triangle V}$$

with  $\triangle V = 3.0$  volts

- ČE is high, all address inputs at Vss to Vss + 0.5V, or VDD to VDD -0.5V

- TDF is specified from OE, CS/CS or CE whichever occurs first.

- 8. TPD is specified CE only

- 9. Output voltage minimum = -0.3V

- Inputs are driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Input timing reference level = 0.8V and 2.0V. Output timing reference = 0.8V and 2.0V.

- 11. Ouput load disconnected.

- 12. These AC characteristics are for the G5365 only.

### **Order Entry Information**

GTE Microcircuits' preferred method of receiving a ROM code is by submittal of a set of programmed EPROM(s). Two sets of EPROMs must be submitted for each code. One set has the ROM code; the other set is blank. GTE Microcircuits will load the ROM code from the EPROM set into our computer system. This information will then be used to program the blank EPROM set, which will be sent back to the customer along with a listing of the code. The customer will approve this listing and return it to GTE.

Chip Select information must also be provided with the ROM code. For the G5364/G5365, Pin 20 may be programmed as a Chip Enable ( $\overline{CE}$ ), high active Chip Select ( $\overline{CS}$ ), or a low active Chip Select ( $\overline{CS}$ ). On the G5365, Pin 26 and Pin 27 may be programmed as a high active Chip Select ( $\overline{CS}$ ), low active Chip Select ( $\overline{CS}$ ), or a No Connection (NC).

ROM code information may also be transmitted in the following optional methods:

- 1. ROMs

- 2. Paper Tape

- 3. Card Deck

Please consult the GTE Microcircuits factory for details.