#### **DESCRIPTION:**

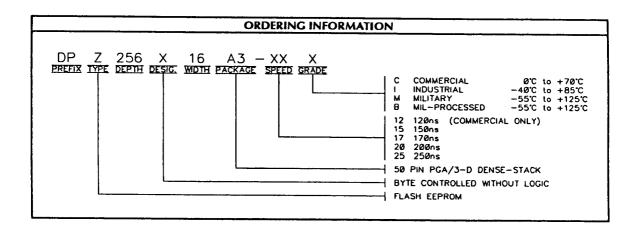

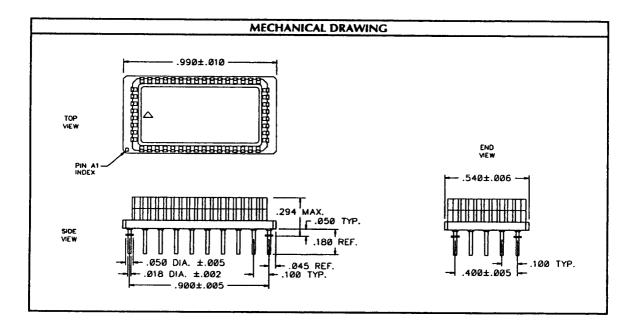

The DPZ256X16A3 "DENSE-STACK" module is a revolutionary new memory subsystem using Dense-Pac Microsystems' ceramic Stackable Leadless Chip Carriers (SLCC) mounted on a co-fired ceramic substrate. It offers 4 Megabits of FLASH EEPROM in a single package envelope of .990" x .540" x .294".

The DPZ256X16A3 is built with two stacked SLCC packages each containing two 128K x 8 FLASH memory devices. Each SLCC is hermetically sealed making the module suitable for commercial, industrial and military applications.

By using SLCCs, the "Dense-Stack" family of modules offers a higher board density of memory than available with conventional through-hole, surface mount, module, or most hybrid techniques.

#### **FEATURES:**

- Organization: 256K x 16

- Fast Access Times: 120\*, 150, 170, 200, 250ns (max.)

- Fully Static Operation

- No clock or refresh required

- TTL Compatible Inputs and Outputs

- · Common Data Inputs and Outputs

- Automatic Erase Function

- Reduces CPU overhead

- 10,000 Erase/Program Cycles (min.)

- 50 Pin PGA "DENSE-STACK" Package

- \* Available in commercial only.

|     |            |             | PIN-U    | UI DIA      | JKAM      |            | <u> </u>        | IN NAMES                        |

|-----|------------|-------------|----------|-------------|-----------|------------|-----------------|---------------------------------|

|     |            |             |          |             |           | (TOP VIEW) | A0 - A16        | Address Inputs                  |

| ١.  | A          | В           | <u>C</u> | <u>D</u>    | E_        | ÀBCDÉ      | 1/00 - 1/015    | Data Input/Output               |

| 1 2 | CE1<br>VSS | N.C.<br>CE3 | N.C.     | N.C.<br>VPP | VDD       | 10000      | CEO - CE3       | Chip Enables                    |

| 3   | N.C.       | A16         | WE.      | N.C.        | A15       | 300000     | WE              | Write Enable                    |

| 4   | A14        | A12         | Α7       | A8          | A13       | 400000     | ŌĒ              | Output Enable                   |

| 6   | A6<br>A4   | A5<br>A3    | OE<br>A2 | A11<br>CEØ  | A9<br>A10 | 500000     | V <sub>PP</sub> | Programming Voltage<br>(+12.5V) |

| 8   | 1/01Ø      | AØ<br>1/09  | 1/013    | 1/012       | 1/011     | 700000     | V <sub>DD</sub> | Power (+5V)                     |

| 9   | VSS        | 1/01        | 1/03     | 1/05        | VDD       | 900000     | Vss             | Ground                          |

| 10  | 1/00       | 1/02        | 1/04     | 1/06        | 1/07      | 100000     | N.C.            | No Connect                      |

<sup>\*\*</sup> CEO and CE2 control I/OO - I/O7, CET and CE3 control I/O8 - I/O15.

30A076-02 REV. A BIN OUT DIACRAM

#### **DEVICE OPERATION:**

The FLASH devices are electrically erasable and programmable memory that functions similar to an EPROM device, but can be erased without being removed from the system and exposed to ultraviolet light. Each 128K x 8 device can be erased individually eliminating the need to re-program the entire module when partial code changes are required.

#### READ:

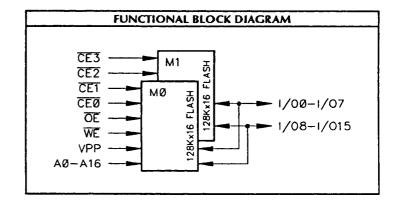

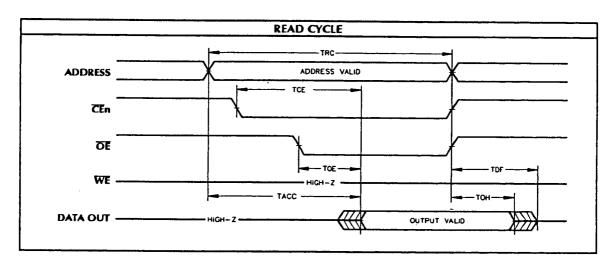

With VPP = 0V to VDD (VPPLO), the devices are read-only memories and can be read like a standard EPROM. By selecting the device to be read (see Truth Table and Functional Block Diagram), the data programmed into the device will appear on the appropriate I/O pins.

When V<sub>PP</sub> = +12.5V ± 5.0V (V<sub>PPHI</sub>), reads can be accomplished in the same manner as described above but must be preceded by writing 00H to the command register prior to reading the device. When V<sub>PP</sub> is raised to V<sub>PPHI</sub> the contents of the command register default to 00H and remain that way until the command register is altered.

#### STANDBY:

When the appropriate CE's are raised to a logic-high level, the standby operation disables the FLASH devices reducing the power consumption substantially. The outputs are placed in a high-impedance state, independent of the OE input. If the module is deselected during programming, erasure, or autoerase, the device upon which the operation was being performed, will continue to draw active current until the operation is completed.

#### PROGRAM:

The programming and erasing functions are accessed via the command register when high voltage is applied to Vpp. The contents of the command register control the functions of the memory device (see Command Definition Table).

The command register is not an addressable memory location. The register stores the address, data, and command information required to execute the command. When VPP = VPPLO the command register is reset to 00H returning the device to the read-only mode.

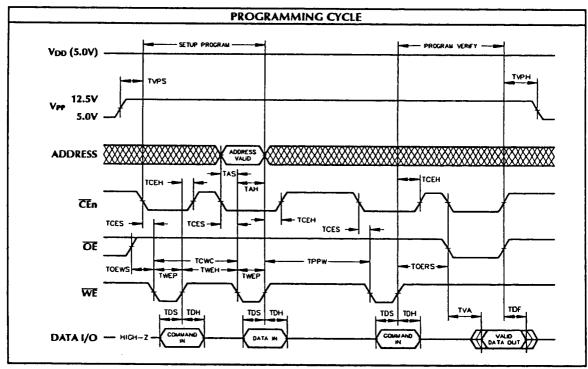

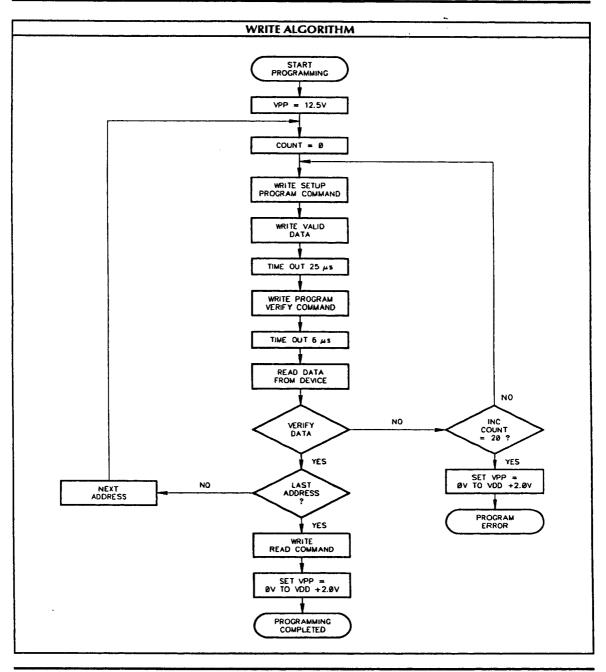

The command register is written by enabling the device upon which that the operation is to be performed (see Functional Block Diagram). While the device is enabled bring WE to a logic-low (VIL), the address is latched on the falling edge of WE and data is latched on the rising edge of WE. Programming is initiated by writing 40H (program setup command) to the command register. On the next falling edge of WE the address to be programmed will be latched followed by the data being latched on the rising edge of WE (see AC Operating and Characteristics Table).

#### **PROGRAM VERIFY:**

The FLASH devices are programmed one byte at a time. Each byte may be programmed sequentially or at random. Following each programming operation, the byte must be verified.

To initiate the program-verify mode, COH must be written to the command register of the device just programmed. The programming operation is terminated on the rising edge of WE the program-verify command is written to the command register.

After the program-verify command is written to the command register, the memory device applies an internally generated margin voltage to the byte just written. After waiting 6µs the data byte can be verified by doing a read. If true data is read from the device, the byte write was successful and the next byte may be programmed.

If the device fails to verify, the program/verify operation is repeated up to 20 times.

#### **ERASE:**

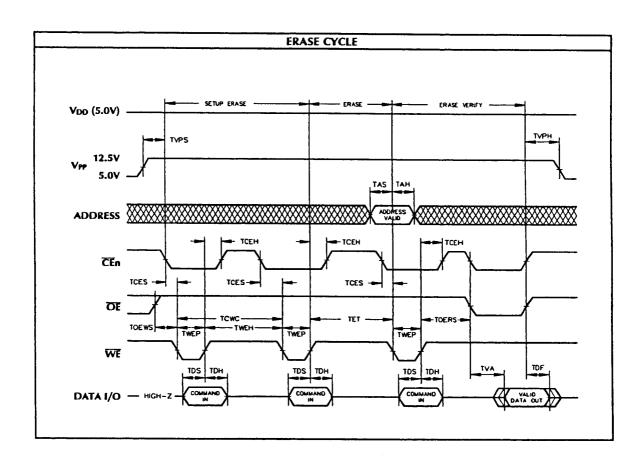

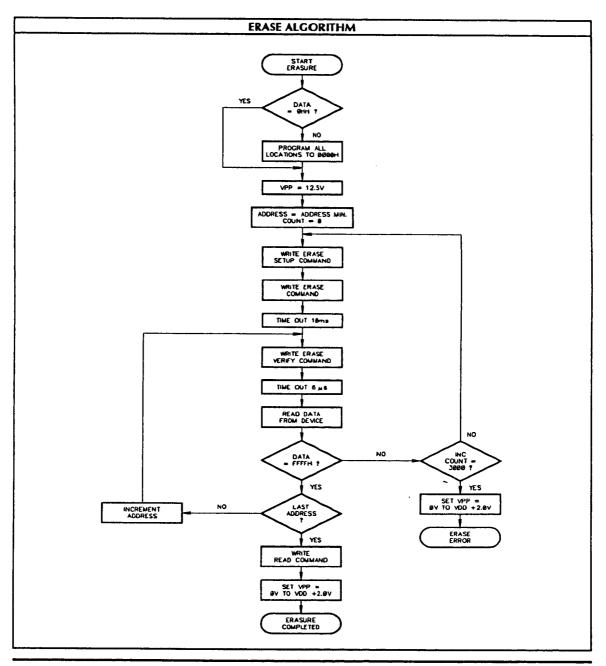

The erase function is a command-only operation and can only be executed while Vpp = VppHI.

To setup the chip-erase, 20H must be written to the command register. The chip-erase is then executed by once again writing 20H to the command register (see AC Operating and Characterstics Table).

To ensure a reliable erasure, all bits in the device to be erased should be programmed to their charged state (data = 00H) prior to starting the erase operation. With the algorithm provided, this operation should take approximately 2 minutes.

#### **ERASE VERIFY:**

The erase operation erases all bytes in the device selected in parallel. Upon completion of the erase operation, each byte must be verified. This operation is initiated by writing AOH to the command register. The address to be verified must be supplied because it is latched on the falling edge of WE.

The memory device internally generates a margin voltage and applies it to the addressed byte. If FFH is read from the device, it indicates the byte is erased. The erase/verify command is issued prior to each byte verification to latch the address of the byte to be verified. This continues until FFH is not read from the device or the last address for the device being erased is read.

If FFH is not read from the byte being verified, an additional erase operation is performed. Verification then resumes from the last byte verified. Once all locations in the device being erased are verified, the erase operation is complete. The verify operation should now be terminated by writing a valid command such as program set-up to the command register.

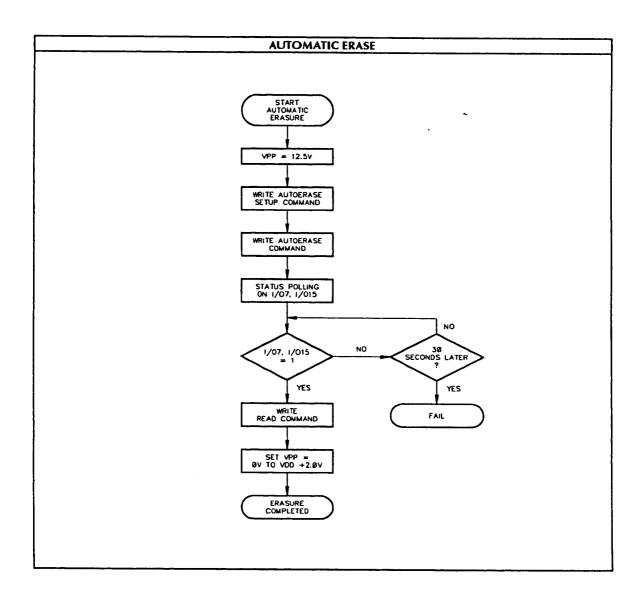

#### **AUTOMATIC ERASE:**

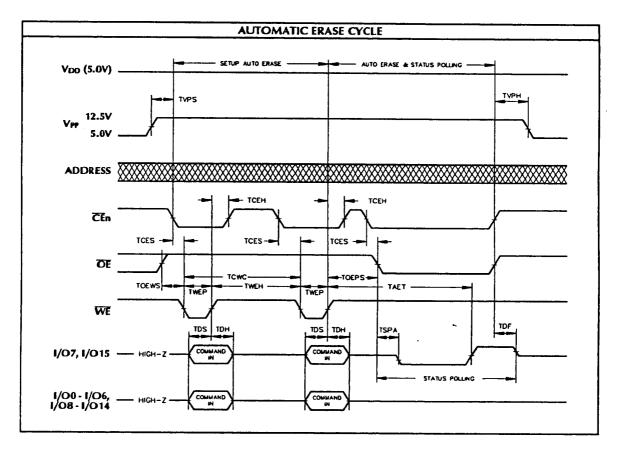

An automatic erase function is also available eliminating the need to program all locations to 00H or do an erase verify. The automatic erase will program all locations to 00H and do a continuous erase/verify until all locations in the device are erased.

To setup the chiperase, 30H must be written to the command register. The chiperase is then executed by once again writing 30H to the command register (see AC Operating Characteristics Table).

To determine if the automatic erase cycle is complete, the most-significant (MSB) I/O pin for the device being erased (I/O7, I/O15) is read. If the data = 0 on each of these bits, the cycle is not complete. The erase cycle is complete when the data = 1 on the MSB of the device being erased.

#### **DESIGN CONSIDERATIONS:**

VPP traces should use similar trace widths and layout considerations as the Vpp power bus. The VpP supply traces should also be decoupled to help decrease voltage spikes.

Power-up sequencing should be such that Vpp doesn't go above Vpp + 2.0V before Vpp reaches a steady state voltage, while on power-down Vpp should be below Vpp + 2.0V before Vpp is lowered.

It is recommended that a 4.7 $\mu$ F to 10 $\mu$ F electrolytic capacitor be placed near the memory module connected accross V<sub>DD</sub> and Vss for bulk storage. Decoupling capacitors should also be placed near the module connected across V<sub>PP</sub> and Vss.

|                             |                 | COMMAN    | D DEFINITION    | ON TABLE |           |                 |      |  |

|-----------------------------|-----------------|-----------|-----------------|----------|-----------|-----------------|------|--|

|                             | Bus             |           | First Bus Cycle |          | s         | econd Bus Cycle | :    |  |

| COMMAND                     | Cycles<br>Reg'd | Operation | Address         | Data     | Operation | Address         | Data |  |

| Read Memory                 | 1               | Write     | X               | 00H      |           | -               |      |  |

| Setup Erase / Erase         | 2               | Write     | х               | 20H      | Write     | X               | 2011 |  |

| Erase Verify                | 2               | Write     | EA              | AOH      | Read      | X               | EVD  |  |

| Setup Autoerase / Autoerase | 2               | Write     | X               | 30H      | Write     | X               | 30H  |  |

| Setup Program / Program     | 2               | Write     | X               | 40H_     | Write     | PA              | PO   |  |

| Program Verify              | 2               | Write     | х               | СОН      | Read      | x               | PVD  |  |

| Reset                       | 2               | Write     | Х               | FFH      | Write     | X               | FFH  |  |

EA - Address to Verify

EVD = Data Read from Location EA

PA - Address to Program

PD = Data to be Programmed at Location PA

PVA = Data to be Read from Location PA at Program Verify

|              |                |     | TRUTHT | ABLE |                          |          |                |  |

|--------------|----------------|-----|--------|------|--------------------------|----------|----------------|--|

| MODE         | DESCRIPTION    | CEn | WE     | Œ    | Vpp                      | I/O Pins | Supply Current |  |

|              | Not Selected   | Н   | ×      | X    | VPPLO                    | High-Z   | Standby        |  |

| READ<br>ONLY | Output Disable | L   | н      | Н    | V <sub>PPLO</sub> High-Z |          | Active         |  |

| Civil        | Read           | L   | Н      | L    | VPPLO                    | DOUT     | Active         |  |

|              | Not Selected   | Н   | ×      | X    | VPPH                     | High-Z   | Standby        |  |

| COMMAND      | Output Disable | L   | Н      | н    | VPPIN                    | High-Z   | Active         |  |

| PROGRAM      | Read           | L   | Н      | L    | Vppi-si                  | DOUT     | Active         |  |

|              | Write          | L   | L      | Н    | VPPH                     | DIN      | Active         |  |

30A076-02 REV. A

| RECOMMENDED OPERATING RANGE <sup>1</sup> |                       |       |      |                      |      |  |  |  |  |  |  |

|------------------------------------------|-----------------------|-------|------|----------------------|------|--|--|--|--|--|--|

| Symbol                                   | Characteristic        | Min.  | Тур. | Max.                 | Unit |  |  |  |  |  |  |

| VDD                                      | Supply Voltage        | 4.5   | 5.0  | 5.5                  | V    |  |  |  |  |  |  |

| Vpp                                      | Programming Voltage 2 | 12.0  | 12.5 | 13.0                 | V    |  |  |  |  |  |  |

| VIL                                      | Input LOW Voltage     | -0.33 |      | 0.8                  | V    |  |  |  |  |  |  |

| VH                                       | Input HIGH Voltage    | 2.2   |      | V <sub>DD</sub> +1.0 | V    |  |  |  |  |  |  |

| TA                                       | Operating Temp.       | -55   | +25  | +125                 | °C   |  |  |  |  |  |  |

| С      | CAPACITANCE 5: TA = 25°C, F = 1.0MHz |      |      |           |  |  |  |  |  |  |  |  |

|--------|--------------------------------------|------|------|-----------|--|--|--|--|--|--|--|--|

| Symbol | Parameter                            | Max. | Unit | Condition |  |  |  |  |  |  |  |  |

| CADR   | Address Input                        | 40   |      | †         |  |  |  |  |  |  |  |  |

| CCE    | Chip Enable                          | 10   |      | •         |  |  |  |  |  |  |  |  |

| CwE    | Write Enable                         | 40   | рF   | VIN3 - 0V |  |  |  |  |  |  |  |  |

| COE    | Output Enable                        | 40   |      |           |  |  |  |  |  |  |  |  |

| Ci/o   | Data Input/Output                    | 30   |      | l         |  |  |  |  |  |  |  |  |

|                 | ABSOLUTE MAXIMUM RATINGS 4                           |                           |      |  |  |  |  |  |  |  |  |

|-----------------|------------------------------------------------------|---------------------------|------|--|--|--|--|--|--|--|--|

| Symbol          | Parameler                                            | Value                     | Unit |  |  |  |  |  |  |  |  |

| Tstc            | Storage Temperature                                  | -65 to +150               | •c   |  |  |  |  |  |  |  |  |

| TBIAS           | Temperature Under Bias                               | -55 to +125               | •c   |  |  |  |  |  |  |  |  |

| Vi/O            | Input/Output Voltage 1                               | -0.6 to +7.0 <sup>3</sup> | V    |  |  |  |  |  |  |  |  |

| V <sub>PP</sub> | Vpp Supply Voltage <sup>1</sup> During Erase/Program | -0.6 to +14.0             | V    |  |  |  |  |  |  |  |  |

| VDD             | Supply Voltage <sup>1</sup>                          | -0.6 to +7.0              | V    |  |  |  |  |  |  |  |  |

| DC OUTPUT CHARACTERISTICS |              |             |      |      |      |  |  |  |  |  |  |

|---------------------------|--------------|-------------|------|------|------|--|--|--|--|--|--|

| Symbol                    | Parameter    | Conditions  | Min. | Max. | Unit |  |  |  |  |  |  |

| Vон                       | HIGH Voltage | 1он= -400µА | 2.4  | -    | V    |  |  |  |  |  |  |

| Vol                       | LOW Voltage  | lot=2.1mA   | -    | 0.45 | V    |  |  |  |  |  |  |

|                  |                                       |                                                                                                     |     | TYP. | Lin  | J    |      |  |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------|-----|------|------|------|------|--|

| Symbol           | Characteristics                       | Test Conditions                                                                                     |     |      | Min. | Max. | Unit |  |

| hn               | Input Leakage Current                 | V <sub>IN</sub> = 0V to V <sub>DD</sub>                                                             |     | -    | -8   | +8   | μΛ   |  |

| lout             | Output<br>Leakage Current             | V <sub>I</sub> /O = 0V to V <sub>DD</sub> ,<br>CE or OE = V <sub>IH</sub> , or WE = V <sub>IL</sub> |     | -    | -8   | +8   | μΛ   |  |

| lccı             | Active                                | CEO = VIL, CET = VIH or CET = VIL, CEO = VIH                                                        | ×8  | 10   |      | 20   |      |  |

|                  | Supply Current                        | VIN = VIL OF VIH, LOUT = 0mA, f = 0MHz                                                              | x16 | 15   |      | 35   | mA.  |  |

| kc2              | Operating                             | CEO = VIL, CET = VIH or CET = VIL, CEO = VIH                                                        | ×8  | 20   |      | 55   |      |  |

|                  | Supply Current                        | VIN = VIL or VIH, IQUT = 0mA, f = 8MHz                                                              | x16 | 50   |      | 100  | mA   |  |

| lcc3             | V <sub>DO</sub>                       |                                                                                                     | х8  | 5    |      | 15   |      |  |

|                  | Programming Current                   | Programming in Progress                                                                             | x16 | 6    |      | 25   | m∧   |  |

| lcc4             | V <sub>DD</sub>                       |                                                                                                     | ×8  | 15   |      | 45   |      |  |

|                  | Erase Current                         | Erasure in Progress                                                                                 | x16 | 25   |      | 80   | mA   |  |

| I <sub>SB1</sub> | Standby Current (TTL)                 | CE = V <sub>IH</sub>                                                                                |     | I I  |      | 4    | mΛ   |  |

| lsez             | Full Standby Supply<br>Current (CMOS) | CE = V <sub>DO</sub> -0.2V                                                                          |     |      |      | 80   | μА   |  |

| lees             | Vpp Leakage Current                   | Vpp = Vpplo                                                                                         |     |      |      | 80   | μΛ   |  |

| l <sub>PP1</sub> | Vpp Read Current                      | Vpp = VppHi                                                                                         |     |      |      | 2.5  | mA   |  |

| lpp2             | Vpp                                   | Vpp = Vpp+u,                                                                                        | ×8  | 8    |      | 35   | mA.  |  |

|                  | Programming Current                   | Programming in Progress                                                                             | x16 | 12   |      | 65   | 1    |  |

| lpp3             | Vpp                                   | Vpp = Vpp+a,                                                                                        | ×8  | 40   |      | 85   |      |  |

|                  | Erase Current                         | Erasure in Progress                                                                                 | x16 | 75   |      | 165  | 1 m^ |  |

Typical measurements made at +25°C, Cycle = min., V<sub>00</sub> = 5.0V.

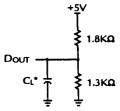

| AC TEST COND                                    | ITIONS        |

|-------------------------------------------------|---------------|

| Input Pulse Levels                              | 0V to 3.0V    |

| Input Pulse Rise and Fall Times                 | 5ns           |

| Input and Output<br>Timing Reference Levels     | 1.5V          |

| Output Timing<br>Reference Levels During Verify | 0.8V and 2.4V |

| OUTPUT LOAD |        |                     |  |  |  |  |  |  |  |  |

|-------------|--------|---------------------|--|--|--|--|--|--|--|--|

| Load        | CL     | Parameters Measured |  |  |  |  |  |  |  |  |

| 1           | 100 pF | except top          |  |  |  |  |  |  |  |  |

| 2           | 30 pF  | tor .               |  |  |  |  |  |  |  |  |

Figure 1. Output Load \*Including Probe and Jig Capacitance.

|     | AC OF      | PERATING CONDITIONS AND CHARAC          | TERISTIC | CS - F | READ | CYC  | CLE: | Over | ope  | rating | g ran    | ges        |      |

|-----|------------|-----------------------------------------|----------|--------|------|------|------|------|------|--------|----------|------------|------|

|     |            | Parameter                               | -12      |        | -150 |      | -170 |      | -200 |        | -250     |            | Unit |

| No. | No. Symbol | Parameter                               | Min.     | Max.   | Min. | Max. | Min. | Max. | Min. | Max.   | Min.     | Max.       |      |

| 1   | <b>LCE</b> | Chip Enable Access Time                 |          | 120    |      | 150  |      | 170  |      | 200    |          | 250        | ns   |

| 2   | LACC       | Address Access Time                     |          | 120    |      | 150  |      | 170  |      | 200    |          | 250        | ns   |

| 3   | to€        | Output Enabe Access Time                |          | 60     |      | 70   |      | 75   |      | 80     | <u> </u> | 90         | ns   |

| 4   | lDF        | Output Disable to Output in HIGH-Z 5, 6 | 0        | 40     | 0    | 50   | 0    | 55   |      | 60     |          | 70         | ns   |

| 5   | lон        | Output Hold from Address Change         | 5        |        | 5    |      | 5    |      | 5    |        | 5        | <u>l</u> . | ns   |

|      | AC OP             | ERATING CONDITIONS AND CHARACTER                       | ISTIC | <u> S - V</u> | VRIT     | E CY |      |          | r ope | ratin    | g ran | ges      |      |

|------|-------------------|--------------------------------------------------------|-------|---------------|----------|------|------|----------|-------|----------|-------|----------|------|

| No.  | Symbol            | Parameter                                              |       | 20            | -1:      |      | -170 |          | -200  |          | -2    |          | Unit |

| 140. | 37111001          |                                                        |       |               |          |      | _    |          | _     | Max.     |       |          |      |

| 6    | lcwc              | Write Cycle Time                                       | 120   |               | 150      |      | 170  |          | 200   |          | 250   |          | ns   |

| 7    | tas               | Address Setup Time                                     | 0     |               | 0        |      | 0    |          | 0     |          | 0     | $\sqcup$ | ns   |

| 8    | <b>L</b> AH       | Address Hold Time                                      | 60    |               | 60       |      | 60   |          | 60    | ļ        | 60    |          | ns   |

| 9    | tos               | Data Setup Time                                        | 50    | L             | 50       |      | 50   | <u> </u> | 50    |          | 50    |          | ns   |

| 10   | tон               | Data Hold Time                                         | 10    |               | 10       |      | 10   |          | 10    |          | 10    |          | ns   |

| 11   | tces              | Chip Enable Setup Time                                 | 0     | <u> </u>      | 0        |      | 0    |          | 0     |          | 0     |          | กร   |

| 12   | <b>ICEH</b>       | Chip Enable Hold Time                                  | 15    | <u> </u>      | 15       |      | 15   |          | 15    |          | 15    |          | ភទ   |

| 13   | tvps              | Vpp Setup Time 7, 8                                    | 100   |               | 100      |      | 100  | <u> </u> | 100   |          | 100   | -        | ns   |

| 14   | €VPH              | Vpp Hold Time 7, 8                                     | 100   |               | 100      |      | 100  |          | 100   | L        | 100   |          | ns   |

| 15   | IWEP              | Write Enable Pulse Width                               | 70    |               | 70       |      | 80   |          | 80    | <u> </u> | 90    |          | ns   |

| 16   | twen              | Write Enable Pulse Width HIGH Time                     | 20    | <u> </u>      | 20       |      | 20   |          | 20    |          | 20    | ļ        | ns   |

| 17   | t <sub>OEWS</sub> | Output Enable Setup Time before<br>Command Programming | 0     |               | 0        |      | 0    |          | 0     |          | 0     |          | ns   |

| 18   | <b>toers</b>      | Output Enable Setup Time before Verify                 | 6     |               | 6        |      | 6    | <u> </u> | 6     | <u> </u> | 6     | _        | μs   |

| 19   | tva               | Verify Access Time                                     |       | 120           | <u> </u> | 150  |      | 170      |       | 200      | -     | 250      | ns   |

| 20   | TOEPS             | Output Enable Setup Time before Status Polling         | 20    | 1             | 20       |      | 20   | ļ        | 20    | <u> </u> | 20    | ļ        | ns   |

| 21   | ISPA              | Status Polling Access Time                             |       | 120           |          | 150  | Ь.   | 170      |       | 200      |       | 250      | ns   |

| 22   | tppw              | Standby Time before Programming                        | 25    |               | 25       |      | 25   | <u> </u> | 25    |          | 25    | ļ        | μs   |

| 23   | ter               | Standby Time in Erase                                  | 11    |               | 11       |      | 11   |          | 11    | 1        | 11    | <b>↓</b> | ms   |

| 24   | LAET              | Total Erase Time in Autoerase 9                        | 0.5   | 30            | 0.5      | 30   | 0.5  | 30       | 0.5   | 30       | 0.5   | 30       | S    |

#### **NOTES:**

- 1. All voltages are with respect to Vss.

- 2. When operating device at temperatures less than 0°C (-55°C to 0°C), Vpp must be 7.4 Vdc above Vpp durring Program/Erase functions.

- 3. -2.0V min. for pulse width less than 20ns (VIL min. = -0.6V at DC level).

- 4. Stresses greater than those under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 5. This parameter is guaranteed and not 100% tested.

- 6. Transition is measured at the point of ±500mV from steady state voltage.

- 7. Vcc must be applied before Vpp and removed after Vpp.

- 8. Vpp must not exceed 14V, including overshoot.

- 9. The total erase times shown are for one (1) 128Kx8 device, to erase the entire module would be 4x the times shown.

30A076-02 REV. A

# Dense-Pac Microsystems, Inc.

7321 Lincoln Way ◆ Garden Grove, California 92641-1428 (714) 898-0007 ◆ (800) 642-4477 (Outside CA) ◆ FAX: (714) 897-1772