# 32-kHz Watch CMOS IC with Motor Regulation (1.5 V)

### **Features**

- 32-kHz oscillator

- 1.3 V to 1.8 V operating-voltage range

- 120 nA typical current consumption

- Motor regulation for minimum current consumption (MCAP)

- Voltage regulator

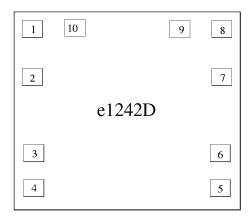

# **Pad Configuration**

Pad size = 112  $\mu$ m × 112  $\mu$ m

13370

Figure 1. Chip size: 1.75 mm x 1.18 mm

- Amplitude controlled oscillator

- Integrated capacitors, mask-selectable

- Mask options for pad designation and adaptation to the motor

- Low resistance outputs for bipolar stepping motor

- Motor fast-test function

# **General Description**

The e1242D is an integrated circuit in CMOS Silicon-Gate Technology for analog watches. It consists of a 32-kHz oscillator, frequency dividers down to 1/2 Hz, output pulse formers and push-pull motor drivers. Capacitors are provided (selectable mask option) for tuning the crystal. Low current consumption and high oscillator stability are achieved by an on-chip voltage regulator.

| Pin       | Symbol      | Function                 |

|-----------|-------------|--------------------------|

| 1 to 6, 8 | $V_{SS}$    | Negative supply voltage  |

| 1 to 5, 8 | $V_{ m DD}$ | Positive supply voltage  |

| 1 to 4    | OSCIN/      | Oscillator input/ output |

|           | OSCOUT      |                          |

| 7         | MOT 1       | Motor drive outputs      |

| 5 and 6   | MOT 2       |                          |

| 1 to 5, 8 | RESET       | Reset input              |

| 1 to 5, 8 | M_TEST      | Motor test input         |

# **Absolute Maximum Ratings**

| g                                         |                  |                                                                     |      |

|-------------------------------------------|------------------|---------------------------------------------------------------------|------|

| Parameters                                | Symbol           | Value                                                               | Unit |

| Supply voltage                            | $V_{ m DD}$      | −0.3 to +5 V                                                        | V    |

| Input voltage range, all inputs           | $V_{\rm IN}$     | $(V_{SS} - 0.3 \text{ V}) \le V_{IN}, \le (V_{DD} + 0.3 \text{ V})$ | V    |

| Output short-circuit duration             |                  | indefinite                                                          |      |

| Power dissipation (DIL package)           | P <sub>tot</sub> | 125 mW                                                              | mW   |

| Operating ambient temperature range       | T <sub>amb</sub> | -20 to +70                                                          | °C   |

| Storage temperature range                 | $T_{stg}$        | -40 to +125                                                         | °C   |

| Lead temperature during soldering at 2 mm | T <sub>sld</sub> | 260                                                                 | °C   |

| distance, 10 seconds                      |                  |                                                                     |      |

Absolute maximum ratings define parameter limits which, if exceeded, may permanently change or damage the device.

All inputs and outputs in TEMIC Semiconductors circuits are protected against electrostatic discharges. However,

precautions to minimize the build-up of electrostatic charges during handling are recommended.

This circuit is protected against supply voltage reversal for typically 5 minutes.

Rev. A1, 06-Jul-99

# **Functional Description**

### **Voltage Regulator**

An integrated voltage regulator provides the oscillator and the leading five divider stages with a well controlled positive supply voltage  $V_{REG}$ . Due to this reduced supply voltage, the frequency stability of the oscillator versus supply voltage variations is significantly improved and the current consumption of the circuit is minimized.

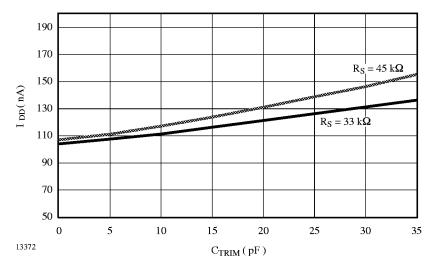

#### **Oscillator**

For generation of the 32768-Hz clock frequency, an amplitude controlled oscillator is used. The amplitude of the oscillator input signal is held constant independent of external load conditions (i.e., trimmer capacitance and quartz characteristics), minimizing the current consumption of the oscillator. For typical supply current versus  $C_{TRIM}$  and quartz  $R_{S}$  variations see figure 3.

A total capacitance of 22 pF is integrated, which can be selected for  $C_{\rm OSCOUT}$  in 1 pF increments by metal mask options.

A trimming capacitor (chip capacitor) for frequency adjustment has to be connected between OSCIN and  $V_{\rm SS}$ .

## **Motor Drive Output**

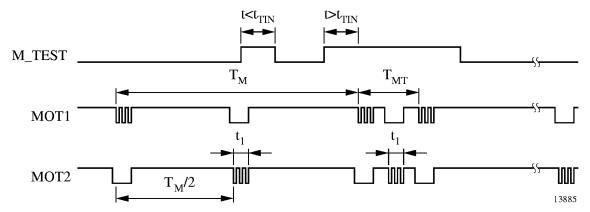

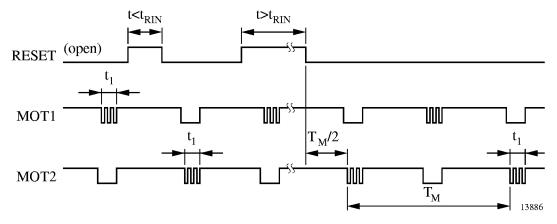

The e1242D contains two push-pull output buffers for driving bipolar stepper motors. During a motor pulse, the n-channel device of one buffer and the p-channel device of the other buffer is activated. Between two pulses, the p-channel devices of both buffers are active (see figure 4). Motor period  $t_M$  is 2 s.

#### Reset

Connecting the RESET input to  $V_{DD}$  for at least 31.2 ms resets the frequency divider, thus disabling further motor pulses. Motor pulses in progress when the reset function is applied will be completed. After releasing the RESET pad from  $V_{DD}$ , the next motor pulse appears with a delay of one half motor period (1 s) on the drive output opposed to the former (see figure 5).

### 4.2.7 Motor Test

Connecting M\_TEST to  $V_{\rm DD}$  for at least 31.2 ms changes the motor period from 2 s to either 62.5 ms or 125 ms ( $t_{\rm MT}$  mask options), while the timing of the motor current regulation remains unchanged (see figure 4).

### MCAP Motor Regulation.

(MCAP = Minimum Current Adaptive Pulse)

In order to reduce the motor current consumption to its absolute minimum for a given mechanical load (i.e., required torque), the motor drive parameters are adapted during **each** motor pulse to the existing load condition.

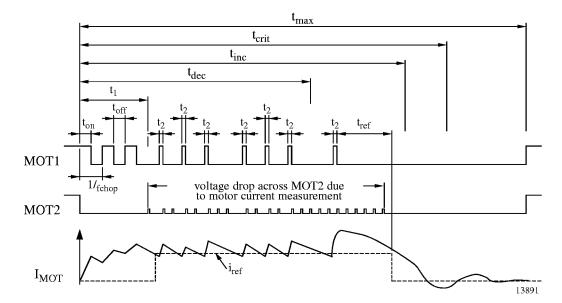

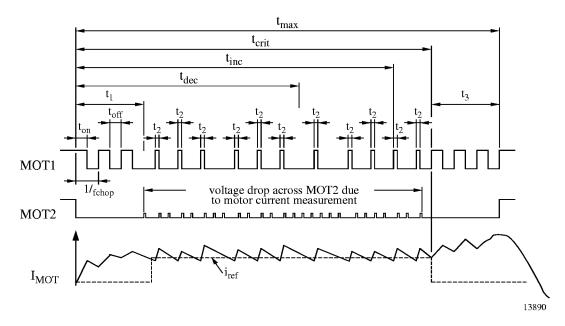

Adaption to a given motor is done by appropriate selection of the parameters  $t_1$ ,  $f_{chop}$ ,  $t_2$ ,  $t_{ref}$ ,  $t_{inc}$ ,  $t_{dec}$ ,  $t_{crit}$ ,  $t_{max}$ ,  $t_3$  and  $i_{ref}$ .

### **Regulation Algorithm**

The regulation is performed in the following way (please refer to figure 6 and 7):

At the end of  $t_1$ , the motor current  $I_{\mbox{MOT}}$  is measured and this measured value is stored.

After measurement of the motor current, a reference current  $i_{ref}$  is generated, which is typically 100% of the previously (at the end of  $t_1$ ) measured motor current and the actual motor current is compared every 61  $\mu s$  with  $i_{ref}$ .

If the motor current is found to be below  $i_{ref}$ , then a drive pulse  $t_2$  is generated (see figure 6). At the end of the first  $t_2$  pulse, the motor current is again compared to  $i_{ref}$  and as soon as the motor current falls again below  $i_{ref}$ , a new drive pulse  $t_2$  is generated (see figure 6).

This is continued as long as the motor current drops below  $i_{ref}$  within a time shorter than  $t_{ref}$  – after the preceding drive pulse  $t_2$ , or until the time  $t_{crit}$  has elapsed.

If the motor current does not drop below  $i_{ref}$  during the time  $t_{ref}$ , then no further motor pulses  $t_2$  are generated (see figure 6).

In addition to the above, the following takes place in order to achieve reliable function over a wide range of mechanical load and power supply voltage (and minimum current consumption for a given load condition).

At power-up or with RESET =  $V_{DD}$ ,  $t_{on}$  is set to its maximum value (duty cycle 50% or 100%).

If the motor pulses  $t_2$  are terminated before  $t_{dec}$  has elapsed, then  $t_{on}$  is decremented, for the following motorpulse.

$t_{on}$  may be decremented repetitively (after each motor pulse), until the  $t_2$  pulses are terminated after  $t_{dec}$  or until a minimum width of  $t_{on}$  is reached.

If the motor pulses  $t_2$  are terminated after  $t_{\rm dec}$  but before  $t_{\rm inc}$  has elapsed (which means that the duty cycle of the chopped pulses  $-t_{\rm on}/t_{\rm off}$  – during  $t_1$  is well adapted to the mechanical load), then  $t_{\rm on}$  remains unchanged.

If the motor pulses  $t_2$  are not terminated at the end of  $t_{\rm inc}$ , then  $t_{\rm on}$  is incremented, for the following motorpulse.

2 (6) Rev. A1, 06-Jul-99

$t_{on}$  may be incremented repetitively (after each motor pulse) until the  $t_2$  pulses are terminated before  $t_{inc}$  – or until a maximum width for  $t_{on}$  of 50% or 100% duty cycle is reached.

If the motor pulses  $t_2$  are not terminated at  $t_{crit}$ , then an additional motorpulse  $t_3$  (duty cycle 50% or 100%) will be generated (see figure 7).

In this case, the following motorpulse  $t_1$  starts again with its maximum duty cycle (i.e., same condition as after power-up or RESET =  $V_{DD}$ ).

# **Operating Characteristics**

$V_{SS} = 0$ ,  $V_{DD} = 1.5$  V,  $T_{amb} = +25$ °C; unless otherwise specified. All voltage levels are measured with reference to  $V_{SS}$ . Test crystal as specified below.

| Parameters                    | Test Conditions / Pins                                    | Symbol            | Min.            | Тур.         | Max. | Unit |

|-------------------------------|-----------------------------------------------------------|-------------------|-----------------|--------------|------|------|

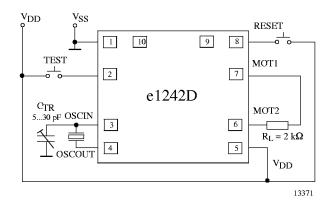

| Operating voltage             | Functional test (figure 2)                                | $V_{ m DD}$       | 1.3             |              | 1.8  | V    |

| Operating current             | $C_{OUT}$ = 16 pF, $C_{TR}$ = 15 pF<br>$R_L$ = $\infty$   | $I_{\mathrm{DD}}$ |                 | 120          | 250  | nA   |

| RESET input current           | $RESET = V_{DD}$                                          | $I_R$             |                 | 8            |      | nA   |

| <b>Motor outputs</b>          |                                                           |                   |                 |              |      |      |

| Motor output current          | $R_L = 2 k\Omega, V_{DD} = 1.55 V$                        | $I_{\mathbf{M}}$  | $\pm 0.7$       |              |      | mA   |

| Motor period                  |                                                           | $t_{\mathbf{M}}$  | 2               |              |      | S    |

| Motor pulse width             |                                                           | t <sub>PW</sub>   | See option list |              |      | ms   |

| Oscillator                    |                                                           |                   |                 |              |      |      |

| Stability vs. supply voltage  | $\Delta V_{SS} = 100 \text{ mV},$ $C_{TR} = 5 \text{ pF}$ | Δf/f              |                 | 0.1          |      | ppm  |

| Start-up voltage              | within 2 sec                                              | V <sub>ST</sub>   | 1.3             |              |      | V    |

| Integrated input capacitance  |                                                           | Coscin            |                 | 2            |      | pF   |

| Integrated output capacitance |                                                           | Coscout           | See op          | tion list 22 |      | pF   |

Note 1: Typical parameters represent the statistical mean values

Figure 2. Functional test

# **Test Crystal Specification**

$\begin{array}{ll} \mbox{Frequency} & \mbox{f} = 32768 \mbox{ Hz} \\ \mbox{Series resistance} & \mbox{R}_S = 30 \mbox{ k} \Omega \\ \mbox{Static capacitance} & \mbox{C}_O = 1.0 \mbox{ pF} \\ \mbox{Dynamic capacitance} & \mbox{C}_1 = 2.5 \mbox{ fF} \\ \mbox{Load capacitance} & \mbox{C}_L = 8 \mbox{ pF} \end{array}$

Note: Maximum series resistance  $R_S = 50 \text{ k}\Omega$

Rev. A1, 06-Jul-99

Figure 3.  $I_{DD} = f(C_{TRIM}, quartz)$

Figure 4. Motor drive outputs in normal mode and motortest

Figure 5. Motor drive outputs and reset

**Note:** For sake of simplicity, only the  $t_1$ -portion of the motorpulse  $t_{PW}$  is shown in figure 4 and figure 5. The complete shape of the motorpulse is shown in figure 6 and figure 7.

4 (6) Rev. A1, 06-Jul-99

Figure 6. Motor pulse shape

Figure 7. Motor pulse shape (no rotation at  $t_{crit}$ )

Rev. A1, 06-Jul-99 5 (6)

Table 3. Option list e1242D-

| Option | Integrated Capacitance *) |               |          |            |        |          |                   |       |       |                 |

|--------|---------------------------|---------------|----------|------------|--------|----------|-------------------|-------|-------|-----------------|

|        | Coscin<br>pF              | Coscout<br>pF | Pad 1    | Pad 2      | Pad 3  | Pad 4    | Pad 5             | Pad 6 | Pad 7 | Pad 8           |

| -C     | 2                         | 16            | $V_{SS}$ | M_<br>TEST | OSCOUT | OSCIN    | $V_{\mathrm{DD}}$ | МОТ2  | MOT1  | RESET           |

| -E     | 2                         | 15            | OSCIN    | OSCOUT     | RESET  | $V_{SS}$ | M_<br>TEST        | MOT2  | MOT1  | V <sub>DD</sub> |

|        |                           |               |          |            |        |          |                   |       |       |                 |

|        |                           |               |          |            |        |          |                   |       |       |                 |

|        |                           |               |          |            |        |          |                   |       |       |                 |

<sup>\*)</sup> on-chip stray capacitance included

### Options for motor control

|                     | Option              | -C    | _E    |       |       |       |      |

|---------------------|---------------------|-------|-------|-------|-------|-------|------|

| Symbol              | Conditions          | Value | Value | Value | Value | Value | Unit |

| $T_{\mathbf{M}}$    |                     | 2     | 2     |       |       |       | s    |

| $t_1$               |                     | 3.9   | 3.4   |       |       |       | ms   |

| $f_{chop}$          |                     | 2048  | 2048  |       |       |       | Hz   |

| t <sub>onmax</sub>  | 100%                | 488   | 488   |       |       |       | μs   |

| $t_{onmin}$         |                     | 305   | 336   |       |       |       | μs   |

| $t_3$               | $t_{on} = 100\%$    | 3.9   | 3.9   |       |       |       | ms   |

| $t_{ m dec}$        |                     | 6.34  | 6.83  |       |       |       | ms   |

| t <sub>inc</sub>    |                     | 7.81  | 7.81  |       |       |       | ms   |

| t <sub>crit</sub>   |                     | 9.27  | 9.27  |       |       |       | ms   |

| $t_{max}$           |                     | 13.18 | 13.18 |       |       |       | ms   |

| $t_2$               |                     | 61    | 61    |       |       |       | μs   |

| $t_{ref}$           |                     | 732   | 732   |       |       |       | μs   |

| $T_{MT}$            | 16 steps per second | 125   | 125   |       |       |       | ms   |

| $TM_{TEST}$         | 64 steps per second | 31.25 | 31.25 |       |       |       | ms   |

| i <sub>ref</sub>    | From I measured     | 80    | 80    |       |       |       | %    |

| i <sub>refmin</sub> |                     | 160   | 64    |       |       |       | μΑ   |

#### We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify TEMIC Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

TEMIC Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2594, Fax number: 49 (0)7131 67 2423

6 (6) Rev. A1, 06-Jul-99