### Features

- High-performance, Low-power AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC Architecture

- 131 Powerful Instructions Most Single-clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

- Non-volatile Program and Data Memories

- 16K Bytes of In-System Self-programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- 512 Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 1K Bytes Internal SRAM

- Up to 64K Bytes Optional External Memory Space

- Programming Lock for Software Security

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- Two 16-bit Timer/Counters with Separate Prescalers, Compare Modes, and

- Capture Modes

- Real Time Counter with Separate Oscillator

- Six PWM Channels

- Dual Programmable Serial USARTs

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Five Sleep Modes: Idle, Power-save, Power-down, Standby, and Extended Standby

- I/O and Packages

- 35 Programmable I/O Lines

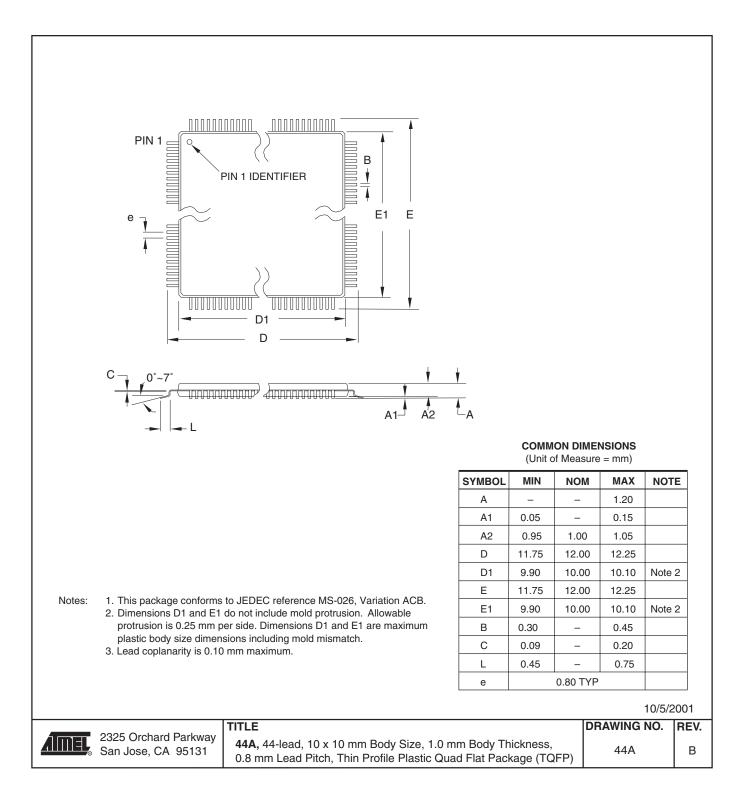

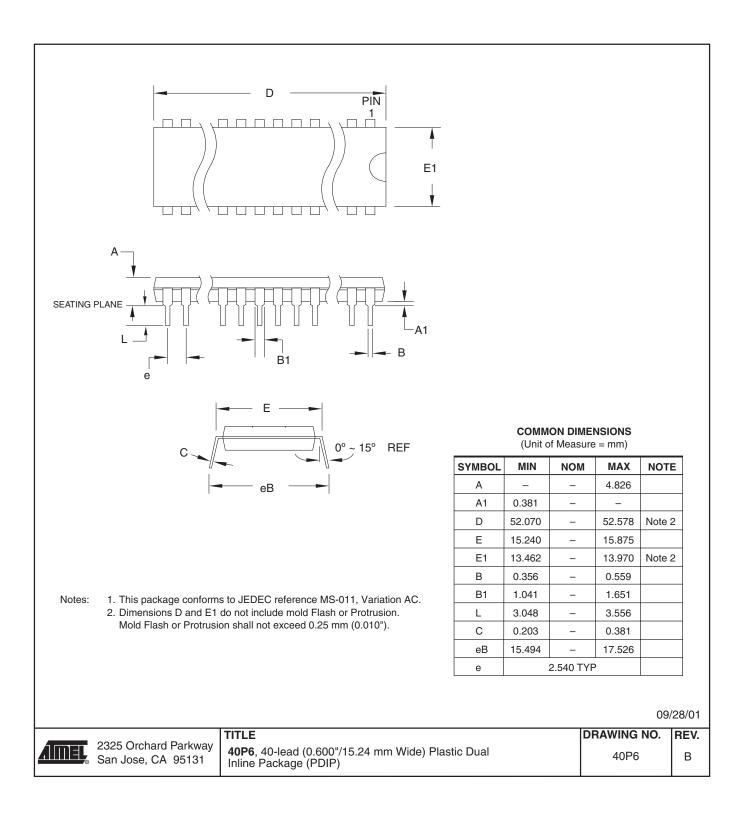

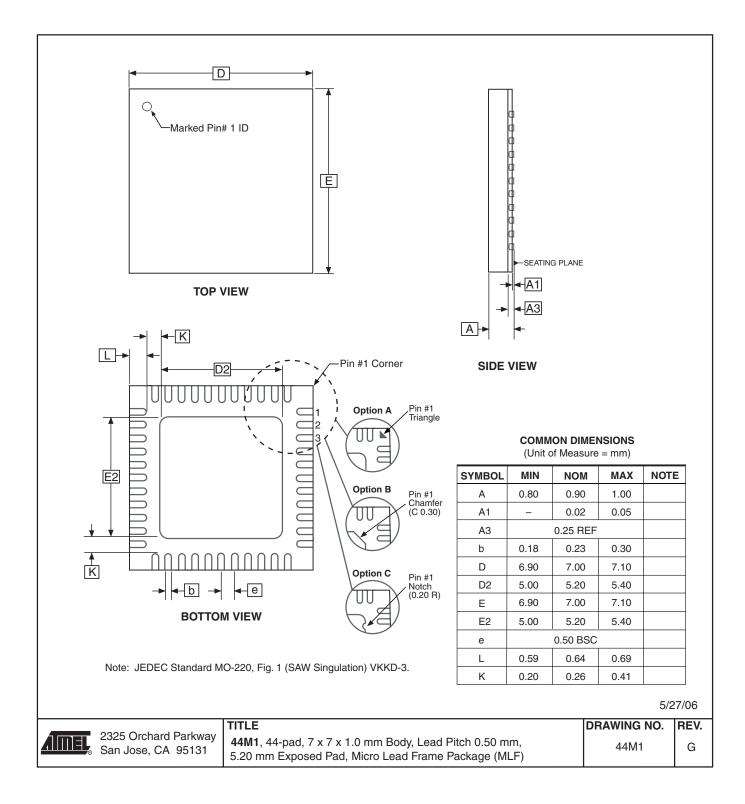

- 40-pin PDIP, 44-lead TQFP, and 44-pad MLF

- Operating Voltages

- 1.8 5.5V for ATmega162V

- 2.7 5.5V for ATmega162

- Speed Grades

- 0 8 MHz for ATmega162V (see Figure 113 on page 265)

- 0 16 MHz for ATmega162 (see Figure 114 on page 265)

8-bit **AVR**<sup>®</sup> Microcontroller with 16K Bytes In-System Programmable Flash

# ATmega162 ATmega162V

## Summary

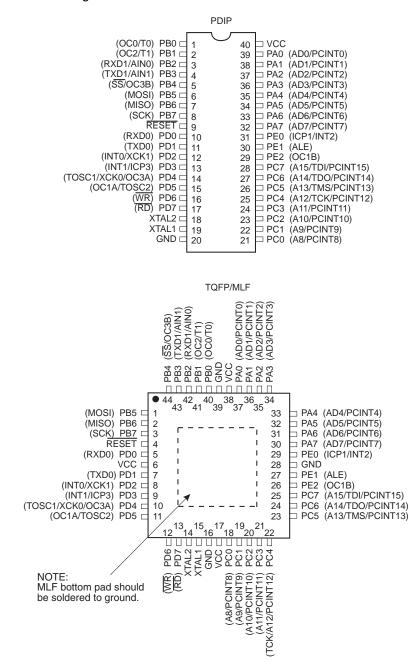

### **Pin Configurations**

Figure 1. Pinout ATmega162

#### Disclaimer

Typical values contained in this datasheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

# <sup>2</sup> ATmega162/V

#### **Overview**

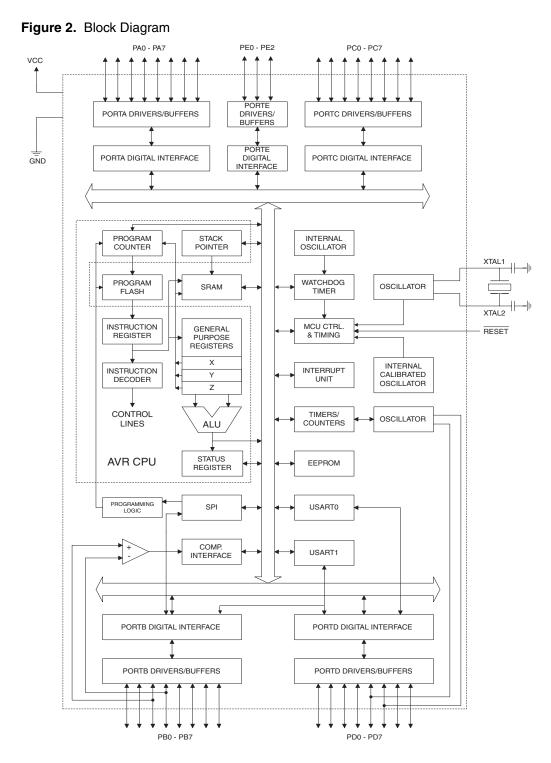

**Block Diagram**

The ATmega162 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega162 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega162 provides the following features: 16K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes EEPROM, 1K bytes SRAM, an external memory interface, 35 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, four flexible Timer/Counters with compare modes, internal and external interrupts, two serial programmable USARTs, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.

The device is manufactured using Atmel's high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot Program running on the AVR core. The Boot Program can use any interface to download the Application Program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega162 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega162 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

The ATmega162 is a highly complex microcontroller where the number of I/O locations supersedes the 64 I/O locations reserved in the AVR instruction set. To ensure backward compatibility with the ATmega161, all I/O locations present in ATmega161 have the same locations in ATmega162. Some additional I/O locations are added in an Extended I/O space starting from 0x60 to 0xFF, (i.e., in the ATmega162 internal RAM space). These locations can be reached by using LD/LDS/LDD and ST/STS/STD instructions only, not by using IN and OUT instructions. The relocation of the internal RAM space may still be a problem for ATmega161 users. Also, the increased number of Interrupt Vectors might be a problem if the code uses absolute addresses. To solve these problems, an ATmega161 compatibility mode can be selected by programming the fuse M161C. In this mode, none of the functions in the Extended I/O space are in use, so the internal RAM is located as in ATmega161. Also, the Extended Interrupt Vectors are removed. The ATmega162 is 100% pin compatible with ATmega161, and can replace the ATmega161 on current Printed Circuit Boards. However, the location of Fuse bits and the electrical characteristics differs between the two devices.

#### ATmega161 and ATmega162 Compatibility

| ATmega161 Compatibility | Programming the M161C will change the following functionality:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mode                    | <ul> <li>The extended I/O map will be configured as internal RAM once the M161C Fuse is<br/>programmed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | <ul> <li>The timed sequence for changing the Watchdog Time-out period is disabled. See<br/>"Timed Sequences for Changing the Configuration of the Watchdog Timer" on page<br/>55 for details.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |

|                         | <ul> <li>The double buffering of the USART Receive Registers is disabled. See "AVR<br/>USART vs. AVR UART – Compatibility" on page 167 for details.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                         | <ul> <li>Pin change interrupts are not supported (Control Registers are located in Extended I/O).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | • One 16 bits Timer/Counter (Timer/Counter1) only. Timer/Counter3 is not accessible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                         | Note that the shared UBRRHI Register in ATmega161 is split into two separate registers in ATmega162, UBRR0H and UBRR1H. The location of these registers will not be affected by the ATmega161 compatibility fuse.                                                                                                                                                                                                                                                                                                                                                                   |

| Pin Descriptions        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC                     | Digital supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| GND                     | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Port A (PA7PA0)         | Port A is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                            |

|                         | Port A also serves the functions of various special features of the ATmega162 as listed on page 71.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Port B (PB7PB0)         | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.                                                                                                                                           |

|                         | Port B also serves the functions of various special features of the ATmega162 as listed on page 71.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Port C (PC7PC0)         | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC7(TDI), PC5(TMS) and PC4(TCK) will be activated even if a Reset occurs. |

|                         | Port C also serves the functions of the JTAG interface and other special features of the ATmega162 as listed on page 74.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port D also serves the functions of various special features of the ATmega162 as listed on page 77.                                                                                                                                                                                                                                                                                                                                       |

| Port E is an 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port E pins that are externally pulled low will source current if the pull-up resistors are activated. The Port E pins are tri-stated when a reset condition becomes active, even if the clock is not running. |

| Port E also serves the functions of various special features of the ATmega162 as listed on page 80.                                                                                                                                                                                                                                                                                                                                       |

| Reset input. A low level on this pin for longer than the minimum pulse length will gener-<br>ate a Reset, even if the clock is not running. The minimum pulse length is given in Table<br>18 on page 47. Shorter pulses are not guaranteed to generate a reset.                                                                                                                                                                           |

| Input to the Inverting Oscillator amplifier and input to the internal clock operating circuit.                                                                                                                                                                                                                                                                                                                                            |

| Output from the Inverting Oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                           |

AIMEL

# 6 ATmega162/V

# ATmega162/V

## **Register Summary**

| Address          | Name                 | Bit 7   | Bit 6   | Bit 5     | Bit 4             | Bit 3                 | Bit 2       | Bit 1  | Bit 0  | Page     |

|------------------|----------------------|---------|---------|-----------|-------------------|-----------------------|-------------|--------|--------|----------|

| (0xFF)           | Reserved             | _       | -       | -         | _                 | _                     | _           | _      | -      | <u> </u> |

|                  | Reserved             | _       |         |           | _                 |                       |             |        |        |          |

| <br>(0x9E)       | Reserved             | _       | _       | _         | _                 | _                     | _           | -      | _      |          |

| (0x9D)           | Reserved             | _       | _       | _         | _                 | _                     | _           | _      | _      |          |

| (0x9C)           | Reserved             | -       | _       | -         | _                 | -                     | _           | -      | -      |          |

| (0x9B)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x9A)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x99)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x98)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x97)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x96)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x95)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x94)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x93)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x92)<br>(0x91) | Reserved<br>Reserved | -       | -       | -         | -                 | -                     | _           | -      | -      |          |

| (0x91)<br>(0x90) | Reserved             | _       | _       | _         | _                 | _                     | _           |        |        |          |

| (0x90)<br>(0x8F) | Reserved             | _       | _       | _         | _                 | _                     |             |        |        |          |

| (0x8F)           | Reserved             | _       | _       |           | _                 | _                     | _           |        |        |          |

| (0x8D)           | Reserved             | _       | _       | _         | _                 | _                     | _           | _      | _      |          |

| (0x8C)           | Reserved             | _       | _       | _         | _                 | _                     | _           | _      | -      | []       |

| (0x8B)           | TCCR3A               | COM3A1  | COM3A0  | COM3B1    | COM3B0            | FOC3A                 | FOC3B       | WGM31  | WGM30  | 130      |

| (0x8A)           | TCCR3B               | ICNC3   | ICES3   | _         | WGM33             | WGM32                 | CS32        | CS31   | CS30   | 127      |

| (0x89)           | TCNT3H               |         |         | Time      | er/Counter3 – Co  | unter Register Hig    | gh Byte     |        |        | 132      |

| (0x88)           | TCNT3L               |         |         | Time      | er/Counter3 – Co  | unter Register Lo     | w Byte      |        |        | 132      |

| (0x87)           | OCR3AH               |         |         | Timer/Cou | unter3 – Output C | ompare Register       | A High Byte |        |        | 132      |

| (0x86)           | OCR3AL               |         |         | Timer/Co  | unter3 – Output 0 | Compare Register      | A Low Byte  |        |        | 132      |

| (0x85)           | OCR3BH               |         |         | Timer/Co  | unter3 – Output C | ompare Register       | B High Byte |        |        | 132      |

| (0x84)           | OCR3BL               |         |         |           |                   | Compare Register      | B Low Byte  |        |        | 132      |

| (0x83)           | Reserved             | -       | -       | -         | -                 | -                     | _           | -      | -      |          |

| (0x82)           | Reserved             | -       | -       |           | -                 | -                     | -           | -      | -      |          |

| (0x81)           | ICR3H                |         |         |           |                   | Capture Register      |             |        |        | 133      |

| (0x80)           | ICR3L<br>Reserved    | _       | _       | –         | _ounter3 – Input  | Capture Register<br>– | Low Byte    | -      | -      | 133      |

| (0x7F)<br>(0x7E) | Reserved             |         |         |           | _                 | _                     | _           |        |        |          |

| (0x7L)           | ETIMSK               | _       |         | TICIE3    | OCIE3A            | OCIE3B                | TOIE3       |        |        | 134      |

| (0x7C)           | ETIFR                | _       | _       | ICF3      | OCF3A             | OCF3B                 | TOV3        | -      | _      | 135      |

| (0x7B)           | Reserved             | _       | _       | -         | _                 | -                     | -           | _      | _      |          |

| (0x7A)           | Reserved             | -       | -       | -         | _                 | -                     | -           | -      | -      |          |

| (0x79)           | Reserved             | -       | _       | -         | _                 | -                     | _           | -      | -      |          |

| (0x78)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x77)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x76)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x75)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x74)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x73)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x72)           | Reserved             | -       | -       | -         | -                 | -                     | _           | -      | -      |          |

| (0x71)           | Reserved<br>Reserved | -       | -       | -         | -                 | -                     | -           | -      | -      | ┟─────┤  |

| (0x70)<br>(0x6F) | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x6F)<br>(0x6E) | Reserved             | _       | _       | _         | _                 | _                     | _           | _      | -      |          |

| (0x6D)           | Reserved             | _       | _       | _         | _                 | _                     | _           |        |        |          |

| (0x6C)           | PCMSK1               | PCINT15 | PCINT14 | PCINT13   | PCINT12           | PCINT11               | PCINT10     | PCINT9 | PCINT8 | 87       |

| (0x6B)           | PCMSK0               | PCINT7  | PCINT6  | PCINT5    | PCINT4            | PCINT3                | PCINT2      | PCINT1 | PCINTO | 87       |

| (0x6A)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x69)           | Reserved             | _       | _       | -         | _                 | _                     | _           | -      | -      |          |

| (0x68)           | Reserved             | _       | _       | _         | _                 | _                     | _           | _      | _      |          |

| (0x67)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x66)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x65)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x64)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x63)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x62)           | Reserved             | -       | -       | -         | -                 | -                     | -           | -      | -      |          |

| (0x61)           | CLKPR                | CLKPCE  | -       | -         | -                 | CLKPS3                | CLKPS2      | CLKPS1 | CLKPS0 | 39       |

| Address                                   | Name           | Bit 7  | Bit 6    | Bit 5  | Bit 4          | Bit 3                               | Bit 2    | Bit 1    | Bit 0  | Page          |

|-------------------------------------------|----------------|--------|----------|--------|----------------|-------------------------------------|----------|----------|--------|---------------|

| (0x60)                                    | Reserved       | -      | -        | -      | -              | -                                   | -        | -        | -      |               |

| 0x3F (0x5F)                               | SREG           | -      | Т        | Н      | S              | V                                   | N        | Z        | С      | 8             |

| 0x3E (0x5E)                               | SPH            | SP15   | SP14     | SP13   | SP12           | SP11                                | SP10     | SP9      | SP8    | 11            |

| 0x3D (0x5D)                               | SPL            | SP7    | SP6      | SP5    | SP4            | SP3                                 | SP2      | SP1      | SP0    | 11            |

| 0x3C <sup>(2)</sup> (0x5C) <sup>(2)</sup> | UBRR1H         | URSEL1 |          |        |                |                                     | UBRF     | R1[11:8] |        | 189           |

| 0,000 (0,00)                              | UCSR1C         | URSEL1 | UMSEL1   | UPM11  | UPM10          | USBS1                               | UCSZ11   | UCSZ10   | UCPOL1 | 188           |

| 0x3B (0x5B)                               | GICR           | INT1   | INT0     | INT2   | PCIE1          | PCIE0                               | -        | IVSEL    | IVCE   | 60, 85        |

| 0x3A (0x5A)                               | GIFR           | INTF1  | INTF0    | INTF2  | PCIF1          | PCIF0                               | -        | -        | -      | 86            |

| 0x39 (0x59)                               | TIMSK          | TOIE1  | OCIE1A   | OCIE1B | OCIE2          | TICIE1                              | TOIE2    | TOIE0    | OCIE0  | 101, 133, 154 |

| 0x38 (0x58)                               | TIFR           | TOV1   | OCF1A    | OCF1B  | OCF2           | ICF1                                | TOV2     | TOV0     | OCF0   | 102, 135, 155 |

| 0x37 (0x57)                               | SPMCR          | SPMIE  | RWWSB    | -      | RWWSRE         | BLBSET                              | PGWRT    | PGERS    | SPMEN  | 220           |

| 0x36 (0x56)                               | EMCUCR         | SM0    | SRL2     | SRL1   | SRL0           | SRW01                               | SRW00    | SRW11    | ISC2   | 28,42,84      |

| 0x35 (0x55)                               | MCUCR          | SRE    | SRW10    | SE     | SM1            | ISC11                               | ISC10    | ISC01    | ISC00  | 28,41,83      |

| 0x34 (0x54)                               | MCUCSR         | JTD    | -        | SM2    | JTRF           | WDRF                                | BORF     | EXTRF    | PORF   | 41,50,206     |

| 0x33 (0x53)                               | TCCR0          | FOC0   | WGM00    | COM01  | COM00          | WGM01                               | CS02     | CS01     | CS00   | 99            |

| 0x32 (0x52)                               | TCNT0          |        |          |        |                | nter0 (8 Bits)                      |          |          |        | 101           |

| 0x31 (0x51)                               | OCR0           |        |          |        |                | put Compare Re                      |          |          |        | 101           |

| 0x30 (0x50)                               | SFIOR          | TSM    | XMBK     | XMM2   | XMM1           | XMM0                                | PUD      | PSR2     | PSR310 | 30,69,104,156 |

| 0x2F (0x4F)                               | TCCR1A         | COM1A1 | COM1A0   | COM1B1 | COM1B0         | FOC1A                               | FOC1B    | WGM11    | WGM10  | 127           |

| 0x2E (0x4E)                               | TCCR1B         | ICNC1  | ICES1    | -      | WGM13          | WGM12                               | CS12     | CS11     | CS10   | 130           |

| 0x2D (0x4D)                               | TCNT1H         |        |          |        |                | unter Register Hig                  |          |          |        | 132           |

| 0x2C (0x4C)                               | TCNT1L         |        |          |        |                | unter Register Lo                   |          |          |        | 132           |

| 0x2B (0x4B)                               | OCR1AH         |        |          |        |                | compare Register                    |          |          |        | 132           |

| 0x2A (0x4A)                               | OCR1AL         |        |          |        |                | Compare Register                    |          |          |        | 132           |

| 0x29 (0x49)                               | OCR1BH         |        |          |        |                | compare Register                    | ÷ /      |          |        | 132           |

| 0x28 (0x48)                               | OCR1BL         | 5000   | 14/01/00 |        |                | Compare Register                    |          | 0001     | 0000   | 132           |

| 0x27 (0x47)                               | TCCR2          | FOC2   | WGM20    | COM21  | COM20          | WGM21                               | CS22     | CS21     | CS20   | 148           |

| 0x26 (0x46)                               | ASSR           | -      | -        |        |                | AS2                                 | TCON2UB  | OCR2UB   | TCR2UB | 152           |

| 0x25 (0x45)                               | ICR1H          |        |          |        |                | Capture Register                    | * *      |          |        | 133           |

| 0x24 (0x44)<br>0x23 (0x43)                | ICR1L<br>TCNT2 |        |          | Timer/ |                | Capture Register<br>Inter2 (8 Bits) | LOW Byle |          |        | 133<br>151    |

| 1 /                                       | OCR2           |        |          | т.     |                | put Compare Re                      | riotor   |          |        | 151           |

| 0x22 (0x42)<br>0x21 (0x41)                | WDTCR          |        |          | 111    | WDCE           | WDE                                 | WDP2     | WDP1     | WDP0   | 52            |

| 0,21 (0,41)                               | UBRR0H         | URSEL0 |          |        | -              | WDL                                 |          | R0[11:8] | WDF0   | 189           |

| 0x20 <sup>(2)</sup> (0x40) <sup>(2)</sup> | UCSR0C         | URSEL0 | UMSEL0   | UPM01  | UPM00          | USBS0                               | UCSZ01   | UCSZ00   | UCPOL0 | 188           |

| 0x1F (0x3F)                               | EEARH          | -      | -        | -      | -              | -                                   | -        | -        | EEAR8  | 18            |

| 0x1E (0x3E)                               | EEARL          |        |          |        | FEPBOM Addres  | s Register Low B                    |          |          | EEXINO | 18            |

| 0x1D (0x3D)                               | EEDR           |        |          |        |                | Data Register                       | ,        |          |        | 19            |

| 0x1C (0x3C)                               | EECR           | _      | _        | -      | _              | EERIE                               | EEMWE    | EEWE     | EERE   | 19            |

| 0x1B (0x3B)                               | PORTA          | PORTA7 | PORTA6   | PORTA5 | PORTA4         | PORTA3                              | PORTA2   | PORTA1   | PORTA0 | 81            |

| 0x1A (0x3A)                               | DDRA           | DDA7   | DDA6     | DDA5   | DDA4           | DDA3                                | DDA2     | DDA1     | DDA0   | 81            |

| 0x19 (0x39)                               | PINA           | PINA7  | PINA6    | PINA5  | PINA4          | PINA3                               | PINA2    | PINA1    | PINA0  | 81            |

| 0x18 (0x38)                               | PORTB          | PORTB7 | PORTB6   | PORTB5 | PORTB4         | PORTB3                              | PORTB2   | PORTB1   | PORTB0 | 81            |

| 0x17 (0x37)                               | DDRB           | DDB7   | DDB6     | DDB5   | DDB4           | DDB3                                | DDB2     | DDB1     | DDB0   | 81            |

| 0x16 (0x36)                               | PINB           | PINB7  | PINB6    | PINB5  | PINB4          | PINB3                               | PINB2    | PINB1    | PINB0  | 81            |

| 0x15 (0x35)                               | PORTC          | PORTC7 | PORTC6   | PORTC5 | PORTC4         | PORTC3                              | PORTC2   | PORTC1   | PORTC0 | 81            |

| 0x14 (0x34)                               | DDRC           | DDC7   | DDC6     | DDC5   | DDC4           | DDC3                                | DDC2     | DDC1     | DDC0   | 81            |

| 0x13 (0x33)                               | PINC           | PINC7  | PINC6    | PINC5  | PINC4          | PINC3                               | PINC2    | PINC1    | PINC0  | 82            |

| 0x12 (0x32)                               | PORTD          | PORTD7 | PORTD6   | PORTD5 | PORTD4         | PORTD3                              | PORTD2   | PORTD1   | PORTD0 | 82            |

| 0x11 (0x31)                               | DDRD           | DDD7   | DDD6     | DDD5   | DDD4           | DDD3                                | DDD2     | DDD1     | DDD0   | 82            |

| 0x10 (0x30)                               | PIND           | PIND7  | PIND6    | PIND5  | PIND4          | PIND3                               | PIND2    | PIND1    | PIND0  | 82            |

| 0x0F (0x2F)                               | SPDR           |        |          |        | SPI Da         | ta Register                         |          |          |        | 163           |

| 0x0E (0x2E)                               | SPSR           | SPIF   | WCOL     | -      | -              | -                                   | -        | -        | SPI2X  | 163           |

| 0x0D (0x2D)                               | SPCR           | SPIE   | SPE      | DORD   | MSTR           | CPOL                                | CPHA     | SPR1     | SPR0   | 161           |

| 0x0C (0x2C)                               | UDR0           |        |          |        | USARTO I/C     | Data Register                       |          |          |        | 185           |

| 0x0B (0x2B)                               | UCSR0A         | RXC0   | TXC0     | UDRE0  | FE0            | DOR0                                | UPE0     | U2X0     | MPCM0  | 185           |

| 0x0A (0x2A)                               | UCSR0B         | RXCIE0 | TXCIE0   | UDRIE0 | RXEN0          | TXEN0                               | UCSZ02   | RXB80    | TXB80  | 186           |

| 0x09 (0x29)                               | UBRR0L         |        | n        | ι      | JSART0 Baud Ra | te Register Low I                   | Byte     |          | 1      | 189           |

| 0x08 (0x28)                               | ACSR           | ACD    | ACBG     | ACO    | ACI            | ACIE                                | ACIC     | ACIS1    | ACIS0  | 194           |

| 0x07 (0x27)                               | PORTE          | _      | -        | _      | -              | -                                   | PORTE2   | PORTE1   | PORTE0 | 82            |

| 0x06 (0x26)                               | DDRE           | -      | -        | -      | -              | -                                   | DDE2     | DDE1     | DDE0   | 82            |

| 0x05 (0x25)                               | PINE           | -      | -        | -      | -              | -                                   | PINE2    | PINE1    | PINE0  | 82            |

| 0x04 <sup>(1)</sup> (0x24) <sup>(1)</sup> | OSCCAL         | -      | CAL6     | CAL5   | CAL4           | CAL3                                | CAL2     | CAL1     | CAL0   | 37            |

| . ,                                       | OCDR           |        |          |        |                | ebug Register                       |          |          |        | 201           |

| 0x03 (0x23)<br>0x02 (0x22)                | UDR1           |        | -        |        |                | Data Register                       |          |          |        | 185           |

|                                           | UCSR1A         | RXC1   | TXC1     | UDRE1  | FE1            | DOR1                                | UPE1     | U2X1     | MPCM1  | 185           |

## ATmega162/V

| Address     | Name   | Bit 7  | Bit 6                              | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Page |

|-------------|--------|--------|------------------------------------|--------|-------|-------|--------|-------|-------|------|

| 0x01 (0x21) | UCSR1B | RXCIE1 | TXCIE1                             | UDRIE1 | RXEN1 | TXEN1 | UCSZ12 | RXB81 | TXB81 | 186  |

| 0x00 (0x20) | UBRR1L |        | USART1 Baud Rate Register Low Byte |        |       |       |        | 189   |       |      |

Notes: 1. When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debugger specific documentation for details on how to use the OCDR Register.

2. Refer to the USART description for details on how to access UBRRH and UCSRC.

3. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

4. Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

## **Instruction Set Summary**

| Mnemonics                                                                                                            | Operands                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Flags                                                                                                                                                                                                                                                                                                           | #Clocks                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARITHMETIC AND                                                                                                       | LOGIC INSTRUCTION                                                                                                                                                                                                                                                                            | Ş                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |

| ADD                                                                                                                  | Rd, Rr                                                                                                                                                                                                                                                                                       | Add two Registers                                                                                                                                                                                                                                                                                                                                                                                                                                  | Rd ← Rd + Rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| ADC                                                                                                                  | Rd, Rr                                                                                                                                                                                                                                                                                       | Add with Carry two Registers                                                                                                                                                                                                                                                                                                                                                                                                                       | $Rd \leftarrow Rd + Rr + C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| ADIW                                                                                                                 | Rdl,K                                                                                                                                                                                                                                                                                        | Add Immediate to Word                                                                                                                                                                                                                                                                                                                                                                                                                              | Rdh:Rdl ← Rdh:Rdl + K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Z,C,N,V,S                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                     |

| SUB                                                                                                                  | Rd, Rr                                                                                                                                                                                                                                                                                       | Subtract two Registers                                                                                                                                                                                                                                                                                                                                                                                                                             | Rd ← Rd - Rr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| SUBI                                                                                                                 | Rd, K                                                                                                                                                                                                                                                                                        | Subtract Constant from Register                                                                                                                                                                                                                                                                                                                                                                                                                    | $Rd \leftarrow Rd - K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| SBC                                                                                                                  | Rd, Rr                                                                                                                                                                                                                                                                                       | Subtract with Carry two Registers                                                                                                                                                                                                                                                                                                                                                                                                                  | Rd ← Rd - Rr - C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| SBCI                                                                                                                 | Rd, K                                                                                                                                                                                                                                                                                        | Subtract with Carry Constant from Reg.                                                                                                                                                                                                                                                                                                                                                                                                             | $Rd \leftarrow Rd - K - C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Z,C,N,V,H                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                     |

| SBIW                                                                                                                 | Rdl,K                                                                                                                                                                                                                                                                                        | Subtract Immediate from Word                                                                                                                                                                                                                                                                                                                                                                                                                       | Rdh:Rdl ← Rdh:Rdl - K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Z,C,N,V,S                                                                                                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                     |

| AND                                                                                                                  | Rd, Rr                                                                                                                                                                                                                                                                                       | Logical AND Registers                                                                                                                                                                                                                                                                                                                                                                                                                              | $Rd \leftarrow Rd \bullet Rr$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z,N,V                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                     |

| ANDI                                                                                                                 | Rd, K                                                                                                                                                                                                                                                                                        | Logical AND Register and Constant                                                                                                                                                                                                                                                                                                                                                                                                                  | $Rd \leftarrow Rd \bullet K$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z,N,V                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                     |