### **INTEGRATED CIRCUITS**

### DATA SHEET

# TDA9885; TDA9886 I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

Product specification Supersedes data of 2002 Mar 05 2003 Oct 02

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

| CONTENT    | rs                                                  | 10   | LIMITING VALUES                                                                |

|------------|-----------------------------------------------------|------|--------------------------------------------------------------------------------|

| 1          | FEATURES                                            | 11   | THERMAL CHARACTERISTICS                                                        |

| 2          | GENERAL DESCRIPTION                                 | 12   | CHARACTERISTICS                                                                |

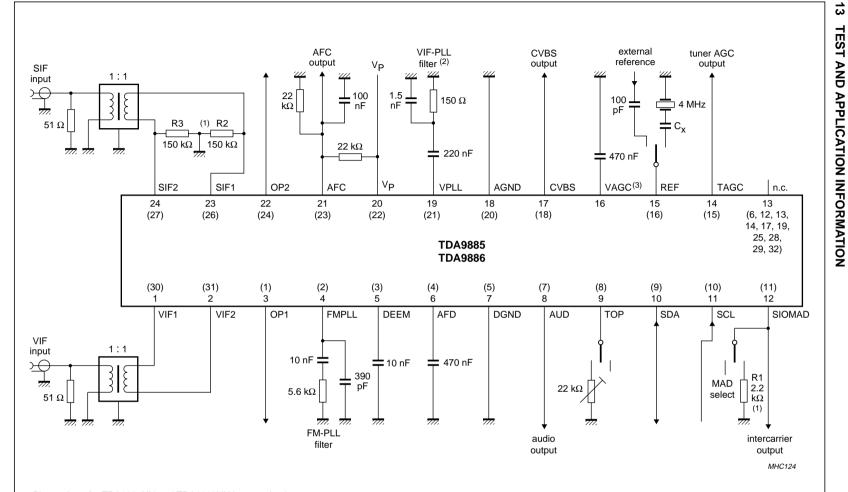

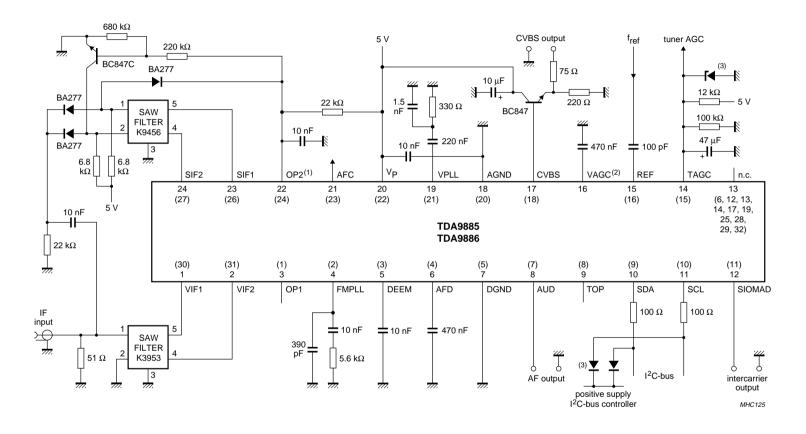

| 3          | APPLICATIONS                                        | 13   | TEST AND APPLICATION INFORMATION                                               |

|            |                                                     | 14   | PACKAGE OUTLINES                                                               |

| 4          | ORDERING INFORMATION                                | 15   | SOLDERING                                                                      |

| 5          | QUICK REFERENCE DATA                                | 15.1 | Introduction to soldering surface mount                                        |

| 6          | BLOCK DIAGRAM                                       | 10.1 | packages                                                                       |

| 7          | PINNING                                             | 15.2 | Reflow soldering                                                               |

| 8          | FUNCTIONAL DESCRIPTION                              | 15.3 | Wave soldering                                                                 |

| 8.1        | VIF amplifier                                       | 15.4 | Manual soldering                                                               |

| 8.2        | Tuner AGC and VIF-AGC                               | 15.5 | Suitability of surface mount IC packages for wave and reflow soldering methods |

| 8.3        | VIF-AGC detector                                    | 4.0  | · ·                                                                            |

| 8.4        | FPLL detector                                       | 16   | DATA SHEET STATUS                                                              |

| 8.5<br>8.6 | VCO and divider AFC and digital acquisition help    | 17   | DEFINITIONS                                                                    |

| 8.7        | Video demodulator and amplifier                     | 18   | DISCLAIMERS                                                                    |

| 8.8        | Sound carrier trap                                  | 19   | PURCHASE OF PHILIPS I2C COMPONENTS                                             |

| 8.9        | SIF amplifier                                       |      |                                                                                |

| 8.10       | SIF-AGC detector                                    |      |                                                                                |

| 8.11       | Single reference QSS mixer                          |      |                                                                                |

| 8.12       | AM demodulator                                      |      |                                                                                |

| 8.13       | FM demodulator and acquisition help                 |      |                                                                                |

| 8.14       | Audio amplifier and mute time constant              |      |                                                                                |

| 8.15       | Internal voltage stabilizer                         |      |                                                                                |

| 8.16       | I <sup>2</sup> C-bus transceiver and module address |      |                                                                                |

| 9          | I <sup>2</sup> C-BUS CONTROL                        |      |                                                                                |

| 9.1        | Read format                                         |      |                                                                                |

| 9.1.1      | Slave address                                       |      |                                                                                |

| 9.1.2      | Data byte                                           |      |                                                                                |

| 9.2        | Write format                                        |      |                                                                                |

| 9.2.1      | Subaddress                                          |      |                                                                                |

| 9.2.2      | Data byte for switching mode                        |      |                                                                                |

| 9.2.3      | Data byte for adjust mode                           |      |                                                                                |

| 9.2.4      | Data byte for data mode                             |      |                                                                                |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 1 FEATURES

- 5 V supply voltage

- Gain controlled wide-band Vision Intermediate Frequency (VIF) amplifier, AC-coupled

- Multistandard true synchronous demodulation with active carrier regeneration: very linear demodulation, good intermodulation figures, reduced harmonics, and excellent pulse response

- · Gated phase detector for L and L-accent standard

- Fully integrated VIF Voltage Controlled Oscillator (VCO), alignment-free, frequencies switchable for all negative and positive modulated standards via I<sup>2</sup>C-bus

- Digital acquisition help, VIF frequencies of 33.4, 33.9, 38.0, 38.9, 45.75, and 58.75 MHz

- 4 MHz reference frequency input: signal from Phase-Locked Loop (PLL) tuning system or operating as crystal oscillator

- VIF Automatic Gain Control (AGC) detector for gain control, operating as peak sync detector for negative modulated signals and as a peak white detector for positive modulated signals

- External AGC setting via pin OP1

- Precise fully digital Automatic Frequency Control (AFC) detector with 4-bit digital-to-analog converter, AFC bits readable via I<sup>2</sup>C-bus

- TakeOver Point (TOP) adjustable via I<sup>2</sup>C-bus or alternatively with potentiometer

- Fully integrated sound carrier trap for 4.5, 5.5,

6.0, and 6.5 MHz, controlled by FM-PLL oscillator

- Sound IF (SIF) input for single reference Quasi Split Sound (QSS) mode, PLL controlled

- SIF-AGC for gain controlled SIF amplifier, single reference QSS mixer able to operate in high performance single reference QSS mode and in intercarrier mode, switchable via I<sup>2</sup>C-bus

- · AM demodulator without extra reference circuit

- Alignment-free selective FM-PLL demodulator with high linearity and low noise

- Four selectable I2C-bus addresses

- I<sup>2</sup>C-bus control for all functions

- I<sup>2</sup>C-bus transceiver with pin programmable Module Address (MAD).

#### 2 GENERAL DESCRIPTION

The TDA9885 is an alignment-free multistandard (PAL and NTSC) vision and sound IF signal PLL demodulator for negative modulation only and FM processing.

The TDA9886 is an alignment-free multistandard (PAL, SECAM and NTSC) vision and sound IF signal PLL demodulator for positive and negative modulation, including sound AM and FM processing.

### 3 APPLICATIONS

• TV, VTR, PC, and STB applications.

#### 4 ORDERING INFORMATION

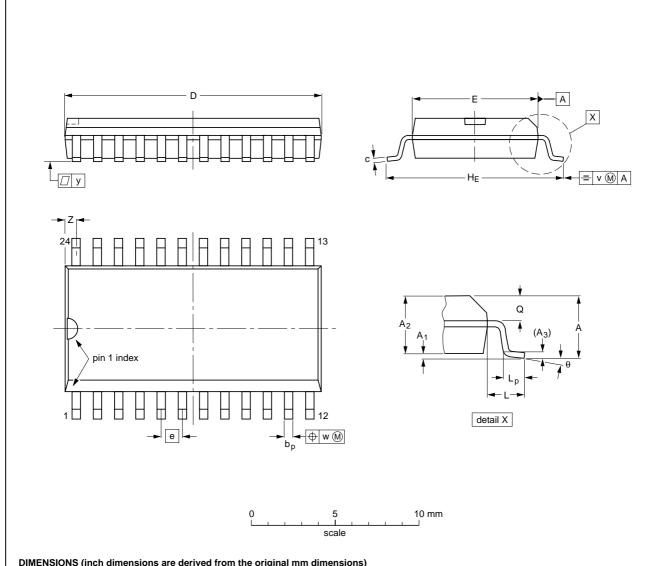

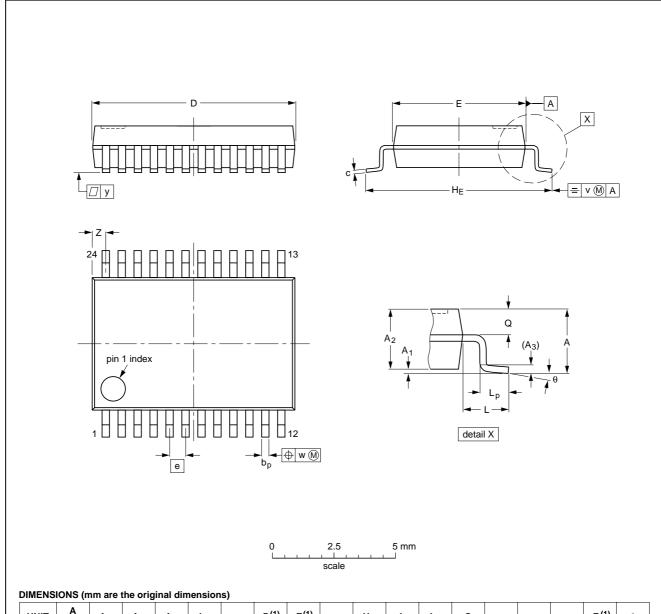

| TYPE NUMBER   |         | PACKAGE                                                                                                    |          |  |  |  |  |  |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|

| I I PE NOMBER | NAME    | NAME DESCRIPTION                                                                                           |          |  |  |  |  |  |  |

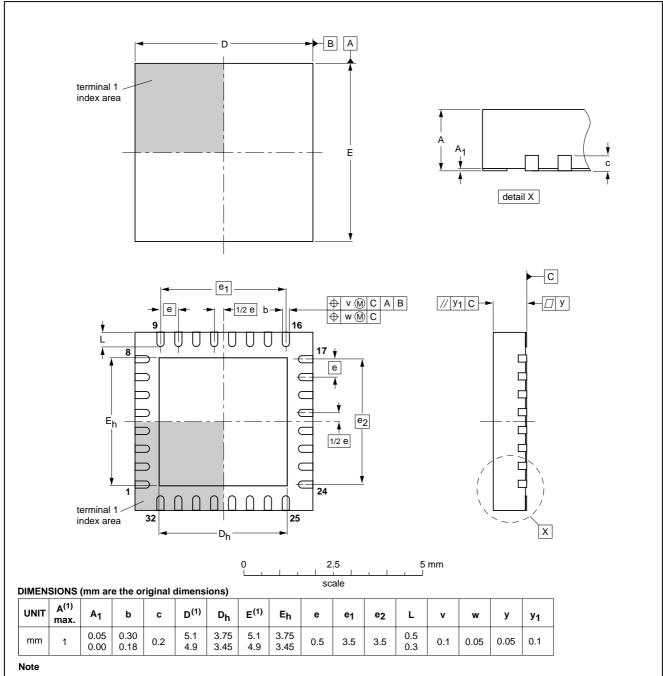

| TDA9885T/V3   | SO24    | plastic small outline package; 24 leads; body width 7.5 mm                                                 | SOT137-1 |  |  |  |  |  |  |

| TDA9885TS/V3  | SSOP24  | plastic shrink small outline package; 24 leads; body width 5.3 mm                                          | SOT340-1 |  |  |  |  |  |  |

| TDA9885HN/V3  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85$ mm | SOT617-3 |  |  |  |  |  |  |

| TDA9886T/V4   | SO24    | plastic small outline package; 24 leads; body width 7.5 mm                                                 | SOT137-1 |  |  |  |  |  |  |

| TDA9886TS/V4  | SSOP24  | plastic shrink small outline package; 24 leads; body width 5.3 mm                                          | SOT340-1 |  |  |  |  |  |  |

| TDA9886HN/V4  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85$ mm | SOT617-3 |  |  |  |  |  |  |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

### 5 QUICK REFERENCE DATA

| SYMBOL                     | PARAMETER                                        | CONDITIONS                                                                                                  | MIN. | TYP.  | MAX. | UNIT   |

|----------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-------|------|--------|

| V <sub>P</sub>             | supply voltage                                   | notes 1 and 2                                                                                               | 4.5  | 5.0   | 5.5  | V      |

| I <sub>P</sub>             | supply current                                   |                                                                                                             | 52   | 63    | 70   | mA     |

| Video part                 |                                                  |                                                                                                             |      |       |      |        |

| V <sub>i(VIF)(rms)</sub>   | VIF input voltage sensitivity (RMS value)        | -1 dB video at output                                                                                       | _    | 60    | 100  | μV     |

| G <sub>VIF(cr)</sub>       | VIF gain control range                           | see Fig.7                                                                                                   | 60   | 66    | _    | dB     |

| f <sub>VIF</sub>           | vision carrier operating frequencies             | see Table 14                                                                                                | _    | 33.4  | _    | MHz    |

|                            |                                                  |                                                                                                             | _    | 33.9  | _    | MHz    |

|                            |                                                  |                                                                                                             | _    | 38.0  | _    | MHz    |

|                            |                                                  |                                                                                                             | _    | 38.9  | _    | MHz    |

|                            |                                                  |                                                                                                             | _    | 45.75 | _    | MHz    |

|                            |                                                  |                                                                                                             | _    | 58.75 | _    | MHz    |

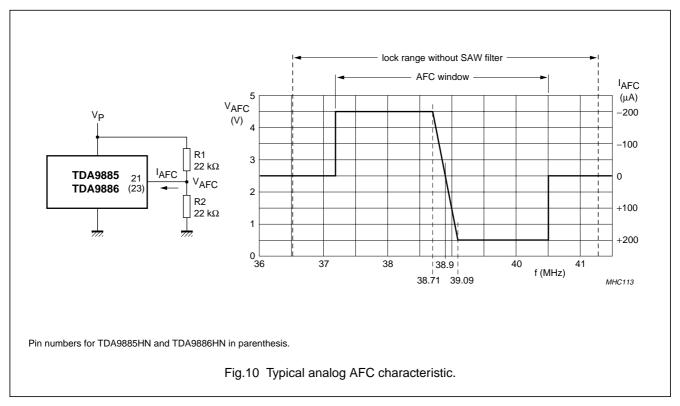

| $\Delta f_{\sf VIF}$       | VIF frequency window of digital acquisition help | related to f <sub>VIF</sub> ; see Fig.10                                                                    | -    | ±2.3  | -    | MHz    |

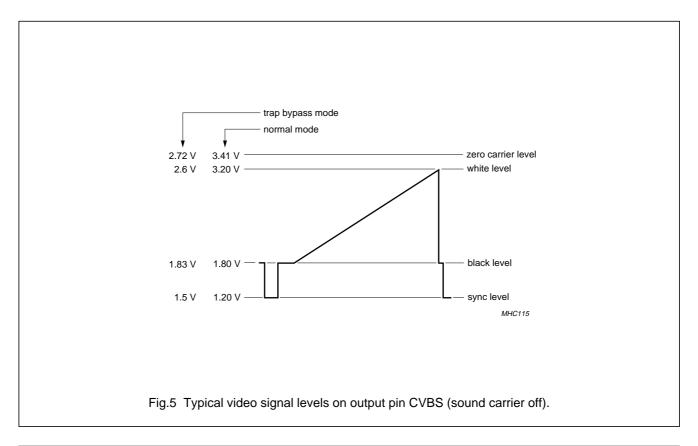

| $V_{o(v)(p-p)}$            | video signal output voltage                      | see Fig.5                                                                                                   |      |       |      |        |

|                            | (peak-to-peak value)                             | normal mode                                                                                                 | 1.7  | 2.0   | 2.3  | V      |

|                            |                                                  | trap bypass mode                                                                                            | 0.95 | 1.10  | 1.25 | V      |

| G <sub>dif</sub>           | differential gain                                | "CCIR 330"; note 3                                                                                          |      |       |      |        |

| <b>u.</b> .                |                                                  | B/G standard                                                                                                | _    | _     | 5    | %      |

|                            |                                                  | L standard                                                                                                  | _    | _     | 7    | %      |

| φ <sub>dif</sub>           | differential phase                               | "CCIR 330"                                                                                                  | _    | 2     | 4    | deg    |

| B <sub>v(-1dB)</sub>       | -1 dB video bandwidth                            | trap bypass mode; AC load; $C_L < 20 \text{ pF}$ ; $R_L > 1 \text{ k}\Omega$                                | 5    | 6     | -    | MHz    |

| B <sub>v(-3dB)(trap)</sub> | -3 dB video bandwidth including                  | note 4                                                                                                      |      |       |      |        |

|                            | sound carrier trap                               | f <sub>trap</sub> = 4.5 MHz                                                                                 | 3.95 | 4.05  | _    | MHz    |

|                            |                                                  | f <sub>trap</sub> = 5.5 MHz                                                                                 | 4.90 | 5.00  | _    | MHz    |

|                            |                                                  | $f_{trap} = 6.0 \text{ MHz}$                                                                                | 5.40 | 5.50  | _    | MHz    |

|                            |                                                  | f <sub>trap</sub> = 6.5 MHz                                                                                 | 5.50 | 5.95  | _    | MHz    |

| α <sub>SC1</sub>           | trap attenuation at first sound                  | M/N standard                                                                                                | 30   | 36    | _    | dB     |

|                            | carrier                                          | B/G standard                                                                                                | 30   | 36    | _    | dB     |

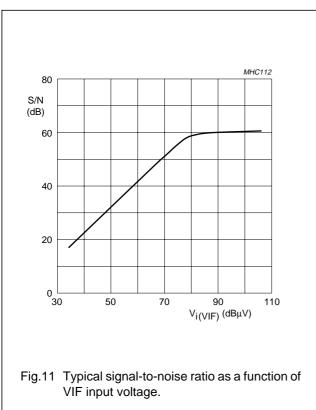

| S/N <sub>W</sub>           | weighted signal-to-noise ratio                   | weighted in accordance with "CCIR 567"; see Fig.11; note 5                                                  | 56   | 59    | _    | dB     |

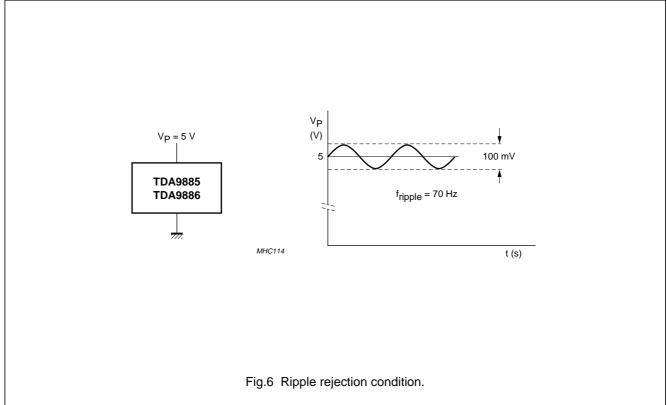

| PSRR <sub>CVBS</sub>       | power supply ripple rejection at pin CVBS        | f <sub>ripple</sub> = 70 Hz; video signal;<br>grey level; positive and<br>negative modulation;<br>see Fig.6 | 20   | 25    | _    | dB     |

| AFC <sub>stps</sub>        | AFC control steepness                            | definition: ΔI <sub>AFC</sub> /Δf <sub>VIF</sub>                                                            | 0.85 | 1.05  | 1.25 | μΑ/kHz |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

| SYMBOL                    | PARAMETER                                      | CONDITIONS                                                                                | MIN. | TYP. | MAX. | UNIT |

|---------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Audio part                |                                                |                                                                                           |      | •    |      |      |

| $V_{o(AF)(rms)}$          | AF output voltage (RMS value)                  | 27 kHz FM deviation;<br>50 μs de-emphasis                                                 | 430  | 540  | 650  | mV   |

| THD                       | total harmonic distortion of audio signal      | FM: 27 kHz FM deviation; 50 μs de-emphasis                                                | -    | 0.15 | 0.50 | %    |

|                           |                                                | AM: m = 54 %                                                                              | Ī-   | 0.5  | 1.0  | %    |

| B <sub>AF(-3dB)</sub>     | -3 dB AF bandwidth                             | without de-emphasis;<br>dependent on FM-PLL filter                                        | 80   | 100  | -    | kHz  |

| S/N <sub>W(AF)</sub>      | weighted signal-to-noise ratio of audio signal | FM: 27 kHz FM deviation;<br>50 μs de-emphasis;<br>vision carrier unmodulated              | 52   | 56   | -    | dB   |

|                           |                                                | AM: m = 54 %                                                                              | 45   | 50   | _    | dB   |

| $\alpha_{\text{AM(sup)}}$ | AM suppression of FM demodulator               | 50 μs de-emphasis;<br>AM: f = 1 kHz and<br>m = 54 %; referenced to<br>27 kHz FM deviation | 40   | 46   | _    | dB   |

| PSRR <sub>AUD</sub>       | power supply ripple rejection on               | f <sub>ripple</sub> = 70 Hz; see Fig.6                                                    |      |      |      |      |

|                           | pin AUD                                        | for AM                                                                                    | 20   | 26   | _    | dB   |

|                           |                                                | for FM                                                                                    | 14   | 20   | _    | dB   |

| V <sub>o(intc)(rms)</sub> | IF intercarrier output level                   | QSS mode; SC <sub>1</sub> ; SC <sub>2</sub> off                                           | 90   | 140  | 180  | mV   |

|                           | (RMS value)                                    | L standard; without modulation                                                            | 90   | 140  | 180  | mV   |

|                           |                                                | intercarrier mode;<br>PC/SC <sub>1</sub> = 20 dB; SC <sub>2</sub> off;<br>note 6          | _    | 75   | _    | mV   |

| Reference fre             | quency                                         |                                                                                           |      |      |      |      |

| f <sub>ref</sub>          | reference signal frequency                     | note 7                                                                                    | _    | 4    | _    | MHz  |

| V <sub>ref(rms)</sub>     | reference signal voltage (RMS value)           | operation as input terminal                                                               | 80   | _    | 400  | mV   |

### Notes

- 1. Values of video and sound parameters can be decreased at  $V_P = 4.5 \text{ V}$ .

- 2. For applications without I<sup>2</sup>C-bus, the time constant (R  $\times$  C) at the supply must be >1.2  $\mu$ s (e.g. 1  $\Omega$  and 2.2  $\mu$ F).

- 3. Condition: luminance range (5 steps) from 0 % to 100 %.

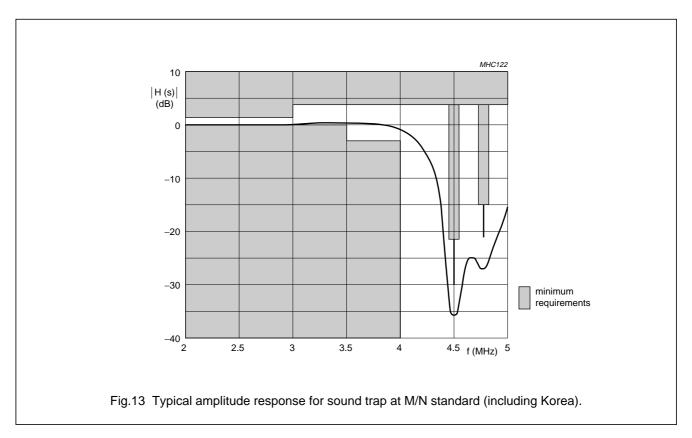

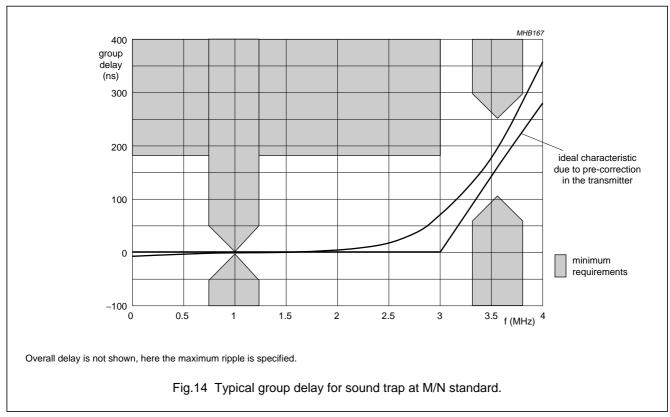

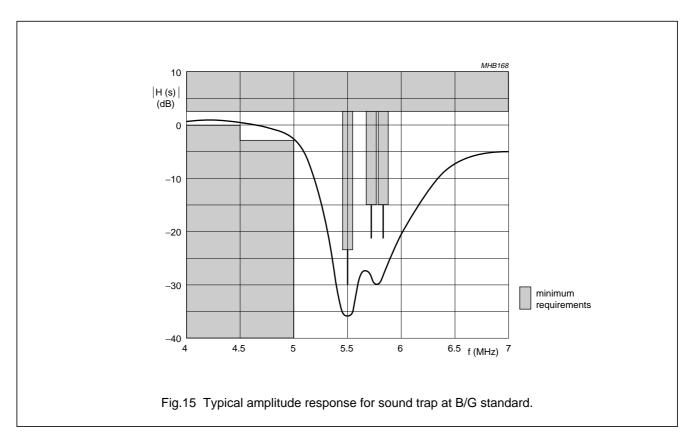

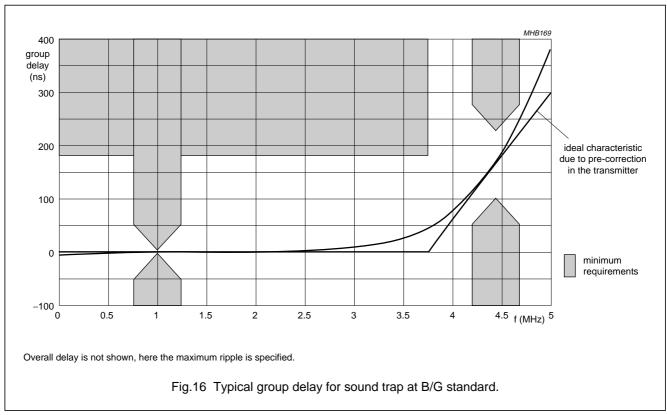

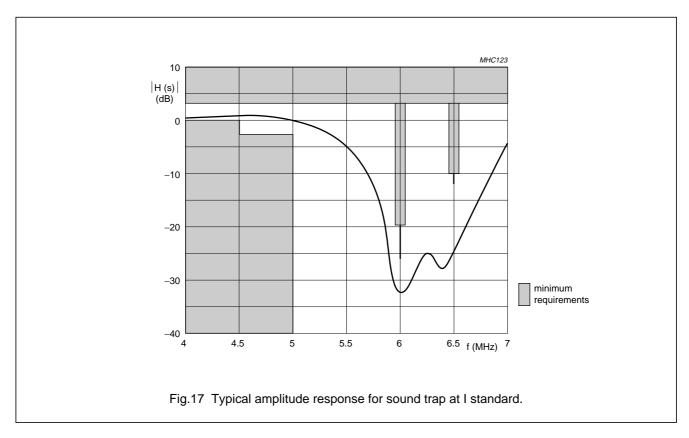

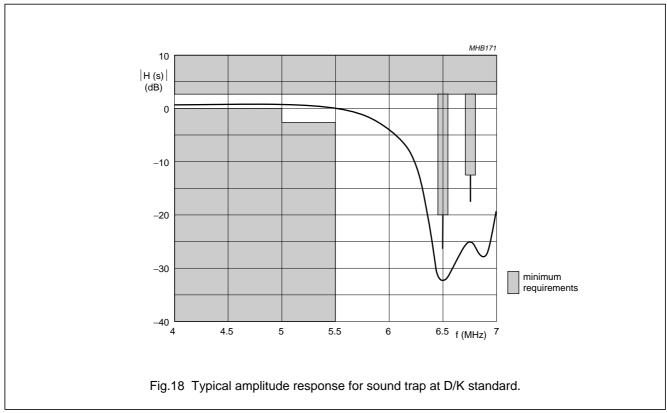

- 4. AC load:  $C_L < 20$  pF and  $R_L > 1$  k $\Omega$ . The sound carrier frequencies (depending on the TV standard) are attenuated by the integrated sound carrier traps (see Figs 13 to 18; |H(s)| is the absolute value of transfer function).

- 5.  $S/N_W$  is the ratio of the black-to-white amplitude to the black level noise voltage (RMS value measured on pin CVBS). B = 5 MHz weighted in accordance with "CCIR 567".

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

6. The intercarrier output signal at pin SIOMAD can be calculated by the following formula taking into account the internal video signal with 1.1 V (p-p) as a reference:

$$V_{o(intc)(rms)} = 1.1 \times \frac{1}{2\sqrt{2}} \times 10^r \text{ V}$$

and

$$r = \frac{1}{20} \times \left( \frac{V_{i(SC)}}{V_{i(PC)}} (dB) + 6 \ dB \pm 3 \ dB \right)$$

where:

$\frac{1}{2\sqrt{2}} \text{ is the correction term for RMS value, } \frac{V_{i(SC)}}{V_{i(PC)}} (dB) \text{ is the sound-to-picture carrier ratio at pins VIF1 and VIF2}$

in dB, 6 dB is the correction term of internal circuitry and  $\pm 3$  dB is the tolerance of video output and intercarrier output  $V_{o(intc)(rms)}$ .

7. Pin REF is able to operate as a 1-pin crystal oscillator input as well as an external reference signal input, e.g. from the tuning system.

7

## alignment-free IF-PLL I<sup>2</sup>C-bus controlled single and multistandard demodulators

6

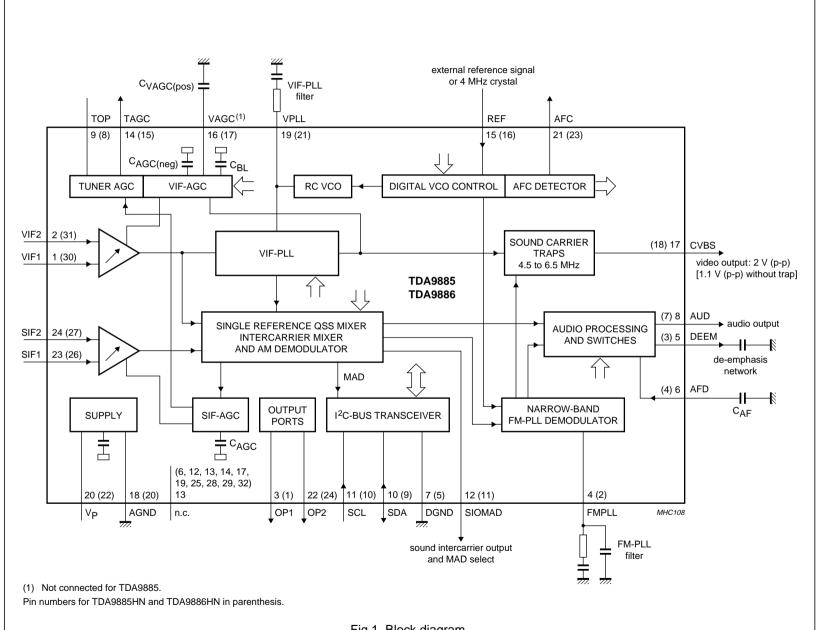

**BLOCK DIAGRAM**

TDA9885; TDA9886

Fig.1 Block diagram.

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

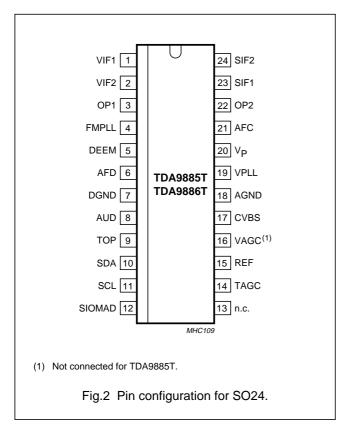

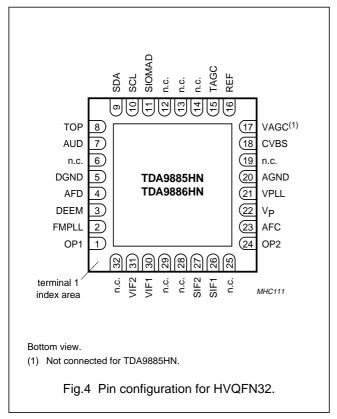

### 7 PINNING

|                |                       | Р                     | IN        |           |                                                        |

|----------------|-----------------------|-----------------------|-----------|-----------|--------------------------------------------------------|

| SYMBOL         | TDA9885T<br>TDA9885TS | TDA9886T<br>TDA9886TS | TDA9885HN | TDA9886HN | DESCRIPTION                                            |

| VIF1           | 1                     | 1                     | 30        | 30        | VIF differential input 1                               |

| VIF2           | 2                     | 2                     | 31        | 31        | VIF differential input 2                               |

| n.c.           | _                     | _                     | 32        | 32        | not connected                                          |

| OP1            | 3                     | 3                     | 1         | 1         | output port 1; open-collector                          |

| FMPLL          | 4                     | 4                     | 2         | 2         | FM-PLL for loop filter                                 |

| DEEM           | 5                     | 5                     | 3         | 3         | de-emphasis output for capacitor                       |

| AFD            | 6                     | 6                     | 4         | 4         | AF decoupling input for capacitor                      |

| DGND           | 7                     | 7                     | 5         | 5         | digital ground                                         |

| n.c.           | _                     | _                     | 6         | 6         | not connected                                          |

| AUD            | 8                     | 8                     | 7         | 7         | audio output                                           |

| TOP            | 9                     | 9                     | 8         | 8         | tuner AGC TakeOver Point (TOP) for resistor adjustment |

| SDA            | 10                    | 10                    | 9         | 9         | I <sup>2</sup> C-bus data input and output             |

| SCL            | 11                    | 11                    | 10        | 10        | I <sup>2</sup> C-bus clock input                       |

| SIOMAD         | 12                    | 12                    | 11        | 11        | sound intercarrier output and MAD select with resistor |

| n.c.           | _                     | _                     | 12        | 12        | not connected                                          |

| n.c.           | 13                    | 13                    | 13        | 13        | not connected                                          |

| n.c.           | _                     | _                     | 14        | 14        | not connected                                          |

| TAGC           | 14                    | 14                    | 15        | 15        | tuner AGC output                                       |

| REF            | 15                    | 15                    | 16        | 16        | 4 MHz crystal or reference signal input                |

| VAGC           | _                     | 16                    | _         | 17        | VIF-AGC for capacitor                                  |

| n.c.           | 16                    | _                     | 17        | _         | not connected                                          |

| CVBS           | 17                    | 17                    | 18        | 18        | composite video output                                 |

| n.c.           | _                     | _                     | 19        | 19        | not connected                                          |

| AGND           | 18                    | 18                    | 20        | 20        | analog ground                                          |

| VPLL           | 19                    | 19                    | 21        | 21        | VIF-PLL for loop filter                                |

| V <sub>P</sub> | 20                    | 20                    | 22        | 22        | supply voltage                                         |

| AFC            | 21                    | 21                    | 23        | 23        | AFC output                                             |

| OP2            | 22                    | 22                    | 24        | 24        | output port 2; open-collector                          |

| n.c.           | _                     | _                     | 25        | 25        | not connected                                          |

| SIF1           | 23                    | 23                    | 26        | 26        | SIF differential input 1 and MAD select with resistor  |

| SIF2           | 24                    | 24                    | 27        | 27        | SIF differential input 2 and MAD select with resistor  |

| n.c.           | _                     | _                     | 28        | 28        | not connected                                          |

| n.c.           | _                     | _                     | 29        | 29        | not connected                                          |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 8 FUNCTIONAL DESCRIPTION

Figure 1 shows the simplified block diagram of the device which comprises the following functional blocks:

- VIF amplifier

- Tuner AGC and VIF-AGC

- VIF-AGC detector

- · Frequency Phase-Locked Loop (FPLL) detector

- VCO and divider

- · AFC and digital acquisition help

- · Video demodulator and amplifier

- · Sound carrier trap

- SIF amplifier

- · SIF-AGC detector

- · Single reference QSS mixer

- · AM demodulator

- · FM demodulator and acquisition help

- · Audio amplifier and mute time constant

- · Internal voltage stabilizer

- I<sup>2</sup>C-bus transceiver and MAD (module address).

### 8.1 VIF amplifier

The VIF amplifier consists of three AC-coupled differential stages. Gain control is performed by emitter degeneration. The total gain control range is typically 66 dB. The differential input impedance is typically 2 k $\Omega$  in parallel with 3 pF.

#### 8.2 Tuner AGC and VIF-AGC

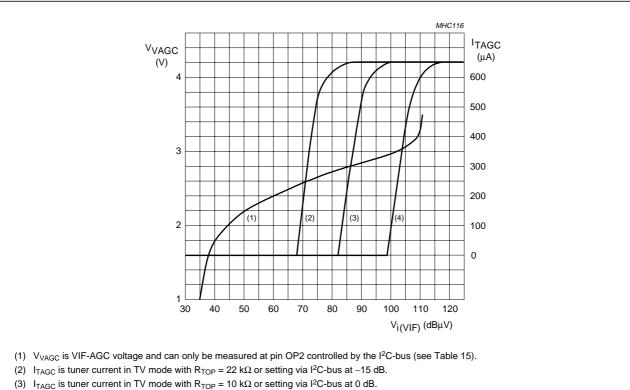

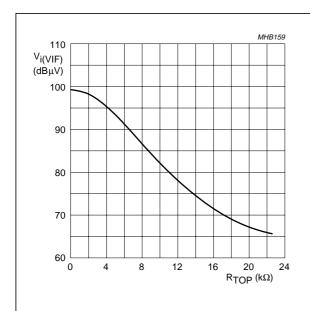

This block adapts the voltages, generated at the VIF-AGC and SIF-AGC detectors, to the internal signal processing at the VIF and SIF amplifiers and performs the tuner AGC control current generation. The onset of the tuner AGC control current generation can be set either via the I<sup>2</sup>C-bus (see Table 13) or optionally by a potentiometer at pin TOP (in case that the I<sup>2</sup>C-bus information cannot be stored, related to the device). The presence of a potentiometer is automatically detected and the I<sup>2</sup>C-bus setting is disabled.

Furthermore, derived from the AGC detector voltage, a comparator is used to test if the corresponding VIF input voltage is higher than 200  $\mu$ V. This information can be read out via the I<sup>2</sup>C-bus (bit VIFLEV = 1).

#### 8.3 VIF-AGC detector

Gain control is performed by sync level detection (negative modulation) or peak white detection (positive modulation).

For negative modulation, the sync level voltage is stored at an integrated capacitor by means of a fast peak detector. This voltage is compared with a reference voltage (nominal sync level) by a comparator which charges or discharges the integrated AGC capacitor for the generation of the required VIF gain. The time constants for decreasing or increasing the gain are nearly equal and the total AGC reaction time is fast to cope with 'aeroplane fluttering'.

For positive modulation, the white peak level voltage is compared with a reference voltage (nominal white level) by a comparator which charges (fast) or discharges (slow) the external AGC capacitor directly for the generation of the required VIF gain. The need of a very long time constant for VIF gain increase is because the peak white level may appear only once in a field. In order to reduce this time constant, an additional level detector increases the discharging current of the AGC capacitor (fast mode) in the event of a decreasing VIF amplitude step controlled by the detected actual black level voltage. The threshold level for fast mode AGC is typically –6 dB video amplitude. The fast mode state is also transferred to the SIF-AGC detector for speed-up. In case of missing peak white pulses, the VIF gain increase is limited to typically +3 dB by comparing the detected actual black level voltage with a corresponding reference voltage.

### 8.4 FPLL detector

The VIF amplifier output signal is fed into a frequency detector and into a phase detector via a limiting amplifier for removing the video AM.

During acquisition the frequency detector produces a current proportional to the frequency difference between the VIF and the VCO signals. After frequency lock-in the phase detector produces a current proportional to the phase difference between the VIF and the VCO signals. The currents from the frequency and phase detectors are charged into the loop filter which controls the VIF VCO and locks it to the frequency and phase of the VIF carrier.

For a positive modulated VIF signal, the charging currents are gated by the composite sync in order to avoid signal distortion in case of overmodulation. The gating depth is switchable via the I<sup>2</sup>C-bus.

2003 Oct 02

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 8.5 VCO and divider

The VCO of the VIF-FPLL operates as an integrated low radiation relaxation oscillator at double the picture carrier frequency. The control voltage, required to tune the VCO to double the picture carrier frequency, is generated at the loop filter by the frequency phase detector. The possible frequency range is 50 to 140 MHz (typical value).

The oscillator frequency is divided-by-two to provide two differential square wave signals with exactly 90 degrees phase difference, independent of the frequency, for use in the FPLL detectors, the video demodulator and the intercarrier mixer.

#### 8.6 AFC and digital acquisition help

Each relaxation oscillator of the VIF-PLL and FM-PLL demodulator has a wide frequency range. To prevent false locking of the PLLs and with respect to the catching range, the digital acquisition help provides an individual control, until the frequency of the VCO is within the preselected standard dependent lock-in window of the PLL.

The in-window and out-window control at the FM-PLL is additionally used to mute the audio stage (if auto mute is selected via the I<sup>2</sup>C-bus).

The working principle of the digital acquisition help is as follows. The PLL VCO output is connected to a down counter which has a predefined start value (standard dependent). The VCO frequency clocks the down counter for a fixed gate time. Thereafter, the down counter stop value is analysed. In case the stop value is higher (lower) than the expected value range, the VCO frequency is lower (higher) than the wanted lock-in window frequency range. A positive (negative) control current is injected into the PLL loop filter and consequently the VCO frequency is increased (decreased) and a new counting cycle starts.

The gate time as well as the control logic of the acquisition help circuit is dependent on the precision of the reference signal at pin REF. Operation as a crystal oscillator is possible as well as connecting this input via a serial capacitor to an external reference frequency, e.g. the tuning system oscillator.

The AFC signal is derived from the corresponding down counter stop value after a counting cycle. The last four bits are latched and can be read out via the I<sup>2</sup>C-bus (see Table 7). Also the digital-to-analog converted value is given as current at pin AFC.

### 8.7 Video demodulator and amplifier

The video demodulator is realized by a multiplier which is designed for low distortion and large bandwidth. The VIF signal is multiplied with the 'in phase' signal of the VIF-PLL VCO.

The demodulator output signal is fed into the video preamplifier via a level shift stage with integrated low-pass filter to achieve carrier harmonics attenuation.

The output signal of the preamplifier is fed to the VIF-AGC detector (see Section 8.3) and in the sound trap mode also fed internally to the integrated sound carrier trap (see Section 8.8). The differential trap output signal is converted and amplified by the following postamplifier. The video output level at pin CVBS is 2 V (p-p).

In the bypass mode the output signal of the preamplifier is fed directly through the postamplifier to pin CVBS. The output video level is 1.1 V (p-p) for using an external sound trap with 10 % overall loss.

Noise clipping is provided in both cases.

#### 8.8 Sound carrier trap

The sound carrier trap consists of a reference filter, a phase detector and the sound trap itself.

A sound carrier reference signal is fed into the reference low-pass filter and is shifted by nominal 90 degrees. The phase detector compares the original reference signal with the signal shifted by the reference filter and produces a DC voltage by charging or discharging an integrated capacitor with a current proportional to the phase difference between both signals, respectively to the frequency error of the integrated filters. The DC voltage controls the frequency position of the reference filter and the sound trap. So the accurate frequency position for the different standards is set by the sound carrier reference signal.

The sound trap itself is constructed of three separate traps to realize sufficient suppression of the first and second sound carriers.

#### 8.9 SIF amplifier

The SIF amplifier consists of three AC-coupled differential stages. Gain control is performed by emitter degeneration. The total gain control range is typically 66 dB. The differential input impedance is typically 2 k $\Omega$  in parallel with 3 pF.

2003 Oct 02

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 8.10 SIF-AGC detector

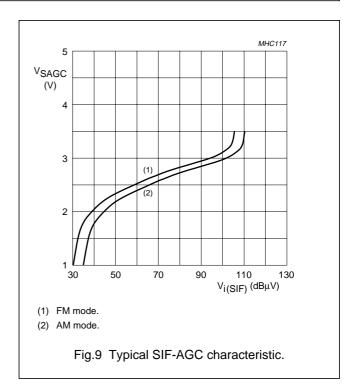

SIF gain control is performed by the detection of the DC component of the AM demodulator output signal. This DC signal corresponds directly to the SIF voltage at the output of the SIF amplifier so that a constant SIF signal is supplied to the AM demodulator and to the single reference QSS mixer.

By switching the gain of the input amplifier of the SIF-AGC detector via the I<sup>2</sup>C-bus, the internal SIF level for FM sound is 5.5 dB lower than for AM sound. This is to adapt the SIF-AGC characteristic to the VIF-AGC characteristic. The adaption is ideal for a picture-to-sound FM carrier ratio of 13 dB.

Via a comparator, the integrated AGC capacitor is charged or discharged for the generation of the required SIF gain. Due to AM sound, the AGC reaction time is slow ( $f_c$  < 20 Hz for the closed AGC loop). For reducing this AM sound time constant in the event of a decreasing IF amplitude step, the load current of the AGC capacitor is increased (fast mode) when the VIF-AGC detector (at positive modulation mode) operates in the fast mode too. An additional circuit (threshold approximately 7 dB) ensures a very fast gain reduction for a large increasing IF amplitude step.

### 8.11 Single reference QSS mixer

With the present system a high performance Hi-Fi stereo sound processing can be achieved. For a simplified application without a SIF SAW filter, the single reference QSS mixer can be switched to the intercarrier mode via the I<sup>2</sup>C-bus.

The single reference QSS mixer generates the 2nd FM TV sound intercarrier signal. It is realized by a linear multiplier which multiplies the SIF amplifier output signal and the VIF-PLL VCO signal (90 degrees output) which is locked to the picture carrier. In this way the QSS mixer operates as a quadrature mixer in the intercarrier mode and provides suppression of the low frequency video signals.

The QSS mixer output signal is fed internally via a high-pass and low-pass combination to the FM demodulator as well as via an operational amplifier to the intercarrier output pin SIOMAD.

#### 8.12 AM demodulator

The amplitude modulated SIF amplifier output signal is fed both to a two-stage limiting amplifier that removes the AM and to a linear multiplier. The result of the multiplication of the SIF signal with the limiter output signal is AM demodulation (passive synchronous demodulator). The demodulator output signal is fed via a low-pass filter that attenuates the carrier harmonics and via the input amplifier of the SIF-AGC detector to the audio amplifier.

### 8.13 FM demodulator and acquisition help

The narrow-band FM-PLL detector consists of:

- · Gain controlled FM amplifier and AGC detector

- Narrow-band PLL.

The intercarrier signal from the intercarrier mixer is fed to the input of an AC-coupled gain controlled amplifier with two stages. The gain controlled output signal is fed to the phase detector of the narrow-band FM-PLL (FM demodulator). For good selectivity and robustness against disturbance caused by the video signal, a high linearity of the gain controlled FM amplifier and of the phase detector as well as a constant signal level are required. The gain control is done by means of an 'in phase' demodulator for the FM carrier (from the output of the FM amplifier). The demodulation output is fed into a comparator for charging or discharging the integrated AGC capacitor. This leads to a mean value AGC loop to control the gain of the FM amplifier.

The FM demodulator is realized as a narrow-band PLL with an external loop filter, which provides the necessary selectivity (bandwidth approximately 100 kHz). To achieve good selectivity, a linear phase detector and a constant input level are required. The gain controlled intercarrier signal from the FM amplifier is fed to the phase detector. The phase detector controls via the loop filter the integrated low radiation relaxation oscillator. The designed frequency range is from 4 to 7 MHz.

The VCO within the FM-PLL is phase-locked to the incoming 2nd SIF signal, which is frequency modulated. As well as this, the VCO control voltage is superimposed by the AF voltage. Therefore, the VCO tracks with the FM of the 2nd SIF signal. So, the AF voltage is present at the loop filter and is typically 5 mV (RMS) for 27 kHz FM deviation. This AF signal is fed via a buffer to the audio amplifier.

The correct locking of the PLL is supported by the digital acquisition help circuit (see Section 8.6).

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 8.14 Audio amplifier and mute time constant

The audio amplifier consists of two parts:

- · AF preamplifier

- · AF output amplifier.

The AF preamplifier used for FM sound is an operational amplifier with internal feedback, high gain and high common mode rejection. The AF voltage from the PLL demodulator is 5 mV (RMS) for a frequency deviation of 27 kHz and is amplified by 30 dB. By the use of a DC operating point control circuit (with external capacitor  $C_{AF}$ ), the AF preamplifier is decoupled from the PLL DC voltage. The low-pass characteristic of the amplifier reduces the harmonics of the sound intercarrier signal at the AF output terminal.

For FM sound a switchable de-emphasis network (with external capacitor) is implemented between the preamplifier and the output amplifier.

The AF output amplifier provides the required AF output level by a rail-to-rail output stage. A preceding stage makes use of an input selector for switching between FM sound, AM sound and mute state. The gain can be switched between 10 dB (normal) and 4 dB (reduced).

Switching to the mute state is controlled automatically, dependent on the digital acquisition help in case the VCO of the FM-PLL is not in the required frequency window. This is done by a time constant: fast for switching to the mute state and slow (typically 40 ms) for switching to the no-mute state.

All switching functions are controlled via the I<sup>2</sup>C-bus:

- · AM sound, FM sound and forced mute

- Auto mute enable or disable

- De-emphasis off or on with 50 or 75 μs

- · Audio gain normal or reduced.

### 8.15 Internal voltage stabilizer

The band gap circuit internally generates a voltage of approximately 2.4 V, independent of supply voltage and temperature. A voltage regulator circuit, connected to this voltage, produces a constant voltage of 3.55 V which is used as an internal reference voltage.

#### 8.16 I<sup>2</sup>C-bus transceiver and module address

The device can be controlled via the 2-wire I<sup>2</sup>C-bus by a microcontroller. Two wires carry serial data (SDA) and serial clock (SCL) information between the devices connected to the I<sup>2</sup>C-bus.

The device has an I<sup>2</sup>C-bus slave transceiver with auto-increment. The circuit operates up to clock frequencies of 400 kHz.

A slave address is sent from the master to the slave receiver. To avoid conflicts in a real application with other devices providing similar or complementing functions, there are four possible slave addresses available. These Module Addresses (MADs) can be selected by connecting resistors on pin SIOMAD and/or pins SIF1 and SIF2 (see Fig.23). Pin SIOMAD relates with bit A0 and pins SIF1 and SIF2 relate with bit A3. The slave addresses of this device are given in Table 1.

The power-on preset value is dependent on the use of pin SIOMAD and can be chosen for 45.75 MHz NTSC as default (pin SIOMAD left open-circuit) or 58.75 MHz NTSC (resistor on pin SIOMAD). In this way the device can be used without the I<sup>2</sup>C-bus as an NTSC only device.

**Remark:** In case of using the device without the  $I^2C$ -bus, then the rise time of the supply voltage after switching on power must be longer than 1.2  $\mu$ s.

2003 Oct 02

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

Table 1 Slave address detection

| SLAVE ADDRESS | SELECTABLE | ADDRESS BIT | RESISTOR ON PIN |        |  |  |

|---------------|------------|-------------|-----------------|--------|--|--|

| SLAVE ADDRESS | А3         | A0          | SIF1 AND SIF2   | SIOMAD |  |  |

| MAD1          | 0          | 1           | no              | no     |  |  |

| MAD2          | 0          | 0           | no              | yes    |  |  |

| MAD3          | 1          | 1           | yes             | no     |  |  |

| MAD4          | 1          | 0           | yes             | yes    |  |  |

#### 9 I2C-BUS CONTROL

#### 9.1 Read format

**Table 2** I<sup>2</sup>C-bus read format (slave transmits data)

| S |               | BYTE 1 |    |    |    |    | Α  |     |  |    | BY | E 2 |    |    |    | AN | Р  |  |  |

|---|---------------|--------|----|----|----|----|----|-----|--|----|----|-----|----|----|----|----|----|--|--|

|   | A6            | A5     | A4 | A3 | A2 | A1 | A0 | R/W |  | D7 | D6 | D5  | D4 | D3 | D2 | D1 | D0 |  |  |

|   | slave address |        |    |    |    | 1  |    |     |  |    | da | ıta |    |    |    |    |    |  |  |

Table 3 Explanation of Table 2

| SYMBOL               | FUNCTION                                                |  |  |  |  |  |

|----------------------|---------------------------------------------------------|--|--|--|--|--|

| S                    | TART condition, generated by the master                 |  |  |  |  |  |

| Slave address        | ee Table 4                                              |  |  |  |  |  |

| $R/\overline{W} = 1$ | ead command, generated by the master                    |  |  |  |  |  |

| Α                    | acknowledge bit, generated by the slave                 |  |  |  |  |  |

| Data                 | 8-bit data word, transmitted by the slave (see Table 5) |  |  |  |  |  |

| AN                   | acknowledge-not bit, generated by the master            |  |  |  |  |  |

| Р                    | STOP condition, generated by the master                 |  |  |  |  |  |

The master generates an acknowledge when it has received the dataword READ. The master next generates an acknowledge, then slave begins transmitting the dataword READ, and so on until the master generates an acknowledge-not bit and transmits a STOP condition.

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 9.1.1 SLAVE ADDRESS

The first module address MAD1 is the standard address (see Table 1).

Table 4 Slave addresses; notes 1 and 2

| SLAV | E ADDRESS   |    | BIT |    |    |    |    |    |  |  |

|------|-------------|----|-----|----|----|----|----|----|--|--|

| NAME | VALUE (HEX) | A6 | A5  | A4 | А3 | A2 | A1 | A0 |  |  |

| MAD1 | 43          | 1  | 0   | 0  | 0  | 0  | 1  | 1  |  |  |

| MAD2 | 42          | 1  | 0   | 0  | 0  | 0  | 1  | 0  |  |  |

| MAD3 | 4B          | 1  | 0   | 0  | 1  | 0  | 1  | 1  |  |  |

| MAD4 | 4A          | 1  | 0   | 0  | 1  | 0  | 1  | 0  |  |  |

#### **Notes**

- 1. For MAD activation via external resistor: see Table 1 and Fig.23.

- 2. For applications without I<sup>2</sup>C-bus: see Tables 17 and 18.

#### 9.1.2 DATA BYTE

Table 5 Data read register (status register)

| MSB    |        |         |      |      |      |      | LSB  |

|--------|--------|---------|------|------|------|------|------|

| D7     | D6     | D5      | D4   | D3   | D2   | D1   | D0   |

| AFCWIN | VIFLEV | CARRDET | AFC4 | AFC3 | AFC2 | AFC1 | PONR |

Table 6 Description of status register bits

| BIT      | VALUE | DESCRIPTION                                       |  |  |  |

|----------|-------|---------------------------------------------------|--|--|--|

| AFCWIN   |       | AFC window                                        |  |  |  |

|          | 1     | VCO in ±1.6 MHz AFC window; note 1                |  |  |  |

|          | 0     | VCO out of ±1.6 MHz AFC window                    |  |  |  |

| VIFLEV   |       | VIF input level                                   |  |  |  |

|          | 1     | high level; VIF input voltage ≥200 μV (typically) |  |  |  |

|          | 0     | low level                                         |  |  |  |

| CARRDET  |       | FM carrier detection                              |  |  |  |

|          | 1     | detection                                         |  |  |  |

|          | 0     | no detection                                      |  |  |  |

| AFC[4:1] |       | Automatic frequency control                       |  |  |  |

|          |       | see Table 7                                       |  |  |  |

| PONR     | ·     | Power-on reset                                    |  |  |  |

|          | 1     | after Power-on reset or after supply breakdown    |  |  |  |

|          | 0     | after a successful reading of the status register |  |  |  |

#### Note

1. If no IF input is applied, then bit AFCWIN = 1 due to the fact that the VCO is forced to the AFC window border for fast lock-in behaviour.

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

Table 7 Automatic frequency control bits; note 1

|      | В    | IT   |      |                                |

|------|------|------|------|--------------------------------|

| AFC4 | AFC3 | AFC2 | AFC1 | fvif                           |

| 0    | 1    | 1    | 1    | ≤ (f <sub>0</sub> – 187.5 kHz) |

| 0    | 1    | 1    | 0    | f <sub>0</sub> – 162.5 kHz     |

| 0    | 1    | 0    | 1    | f <sub>0</sub> – 137.5 kHz     |

| 0    | 1    | 0    | 0    | f <sub>0</sub> – 112.5 kHz     |

| 0    | 0    | 1    | 1    | f <sub>0</sub> – 87.5 kHz      |

| 0    | 0    | 1    | 0    | f <sub>0</sub> – 62.5 kHz      |

| 0    | 0    | 0    | 1    | f <sub>0</sub> – 37.5 kHz      |

| 0    | 0    | 0    | 0    | f <sub>0</sub> – 12.5 kHz      |

| 1    | 1    | 1    | 1    | f <sub>0</sub> + 12.5 kHz      |

| 1    | 1    | 1    | 0    | f <sub>0</sub> + 37.5 kHz      |

| 1    | 1    | 0    | 1    | f <sub>0</sub> + 62.5 kHz      |

| 1    | 1    | 0    | 0    | f <sub>0</sub> + 87.5 kHz      |

| 1    | 0    | 1    | 1    | f <sub>0</sub> + 112.5 kHz     |

| 1    | 0    | 1    | 0    | f <sub>0</sub> + 137.5 kHz     |

| 1    | 0    | 0    | 1    | f <sub>0</sub> + 162.5 kHz     |

| 1    | 0    | 0    | 0    | ≥ (f <sub>0</sub> + 187.5 kHz) |

#### Note

1.  $f_0$  is the nominal frequency of  $f_{VIF}$ .

#### 9.2 Write format

Table 8 I<sup>2</sup>C-bus write format (slave receives data); note 1

| S | BYTE 1        |     | Α | BYTE 2     | Α | BYTE 3      | Α | BYTE n      | Α | Р |

|---|---------------|-----|---|------------|---|-------------|---|-------------|---|---|

|   | A6 to A0      | R/W |   | A7 to A0   |   | bits 7 to 0 |   | bits 7 to 0 |   |   |

|   | slave address | 0   |   | subaddress |   | data 1      |   | data n      |   |   |

### Note

1. The auto-increment of the subaddress stops if the subaddress is 3.

Table 9 Explanation of Table 8

| SYMBOL               | FUNCTION                                                               |

|----------------------|------------------------------------------------------------------------|

| S                    | START condition, generated by the master                               |

| Slave address        | see Table 4                                                            |

| $R/\overline{W} = 0$ | write command, generated by the master                                 |

| Α                    | acknowledge bit, generated by the slave                                |

| Subaddress (SAD)     | see Table 10                                                           |

| Data 1, data n       | 8-bit data words, transmitted by the master (see Tables 11, 12 and 14) |

| Р                    | STOP condition                                                         |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 9.2.1 SUBADDRESS

If more than one data byte is transmitted, then auto-increment is performed: starting from the transmitted subaddress and auto-increment of subaddress in accordance with the order of Table 10.

Table 10 Definition of the subaddress (second byte after slave address); note 1

| REGISTER               | MSB                      |                          |                          |                          |                          |                          |    | LSB |

|------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|----|-----|

| REGISTER               | <b>A7</b> <sup>(2)</sup> | <b>A6</b> <sup>(3)</sup> | <b>A5</b> <sup>(3)</sup> | <b>A4</b> <sup>(3)</sup> | <b>A3</b> <sup>(3)</sup> | <b>A2</b> <sup>(3)</sup> | A1 | A0  |

| SAD for switching mode | 0                        | Х                        | Х                        | Х                        | Х                        | Х                        | 0  | 0   |

| SAD for adjust mode    | 0                        | Х                        | Х                        | Х                        | Х                        | Х                        | 0  | 1   |

| SAD for data mode      | 0                        | Х                        | Х                        | Х                        | Х                        | Х                        | 1  | 0   |

#### **Notes**

- 1. X = don't care.

- 2. Bit A7 = 1 is not allowed.

- 3. Bits A6 to A2 will be ignored by the internal hardware.

### 9.2.2 DATA BYTE FOR SWITCHING MODE

**Table 11** Bit description of SAD register for switching mode (SAD = 00)

| BIT       | VALUE | DESCRIPTION                                       |

|-----------|-------|---------------------------------------------------|

| B7        |       | Output port 2 for SAW switching or monitoring     |

|           | 1     | high-impedance, disabled or HIGH                  |

|           | 0     | low-impedance, active or LOW                      |

| B6        |       | Output port 1 for SAW switching or external input |

|           | 1     | high-impedance, disabled or HIGH                  |

|           | 0     | low-impedance, active or LOW                      |

| B5        |       | Forced audio mute                                 |

|           | 1     | on                                                |

|           | 0     | off                                               |

| B4 and B3 |       | TV standard modulation                            |

|           | 00    | positive AM TV; note 1                            |

|           | 01    | not used                                          |

|           | 10    | negative FM TV                                    |

|           | 11    | not used                                          |

| B2        |       | Carrier mode                                      |

|           | 1     | QSS mode                                          |

|           | 0     | intercarrier mode                                 |

| B1        |       | Auto mute of FM AF output                         |

|           | 1     | active                                            |

|           | 0     | inactive                                          |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

| BIT | VALUE | DESCRIPTION             |  |  |  |  |  |

|-----|-------|-------------------------|--|--|--|--|--|

| В0  |       | Video mode (sound trap) |  |  |  |  |  |

|     | 1     | sound trap bypass       |  |  |  |  |  |

|     | 0     | sound trap active       |  |  |  |  |  |

### Note

1. For positive AM TV choose 6.5 MHz for the second SIF.

### 9.2.3 DATA BYTE FOR ADJUST MODE

Table 12 Bit description of SAD register for adjust mode (SAD = 01)

| BIT      | VALUE | DESCRIPTION                     |

|----------|-------|---------------------------------|

| C7       |       | Audio gain                      |

|          | 1     | −6 dB                           |

|          | 0     | 0 dB                            |

| C6       |       | De-emphasis time constant       |

|          | 1     | 50 μs                           |

|          | 0     | 75 μs                           |

| C5       |       | De-emphasis                     |

|          | 1     | on                              |

|          | 0     | off                             |

| C4 to C0 |       | Tuner takeover point adjustment |

|          |       | see Table 13                    |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

Table 13 Tuner takeover point adjustment bits

|    | TOD AD ILIETMENT (AD) |    |    |    |                     |

|----|-----------------------|----|----|----|---------------------|

| C4 | C3                    | C2 | C1 | CO | TOP ADJUSTMENT (dB) |

| 1  | 1                     | 1  | 1  | 1  | +15                 |

| 1  | 1                     | 1  | 1  | 0  | +14                 |

| 1  | 1                     | 1  | 0  | 1  | +13                 |

| 1  | 1                     | 1  | 0  | 0  | +12                 |

| 1  | 1                     | 0  | 1  | 1  | +11                 |

| 1  | 1                     | 0  | 1  | 0  | +10                 |

| 1  | 1                     | 0  | 0  | 1  | +9                  |

| 1  | 1                     | 0  | 0  | 0  | +8                  |

| 1  | 0                     | 1  | 1  | 1  | +7                  |

| 1  | 0                     | 1  | 1  | 0  | +6                  |

| 1  | 0                     | 1  | 0  | 1  | +5                  |

| 1  | 0                     | 1  | 0  | 0  | +4                  |

| 1  | 0                     | 0  | 1  | 1  | +3                  |

| 1  | 0                     | 0  | 1  | 0  | +2                  |

| 1  | 0                     | 0  | 0  | 1  | +1                  |

| 1  | 0                     | 0  | 0  | 0  | 0(1)                |

| 0  | 1                     | 1  | 1  | 1  | -1                  |

| 0  | 1                     | 1  | 1  | 0  | -2                  |

| 0  | 1                     | 1  | 0  | 1  | -3                  |

| 0  | 1                     | 1  | 0  | 0  | -4                  |

| 0  | 1                     | 0  | 1  | 1  | -5                  |

| 0  | 1                     | 0  | 1  | 0  | -6                  |

| 0  | 1                     | 0  | 0  | 1  | -7                  |

| 0  | 1                     | 0  | 0  | 0  | -8                  |

| 0  | 0                     | 1  | 1  | 1  | -9                  |

| 0  | 0                     | 1  | 1  | 0  | -10                 |

| 0  | 0                     | 1  | 0  | 1  | -11                 |

| 0  | 0                     | 1  | 0  | 0  | -12                 |

| 0  | 0                     | 0  | 1  | 1  | -13                 |

| 0  | 0                     | 0  | 1  | 0  | -14                 |

| 0  | 0                     | 0  | 0  | 1  | -15                 |

| 0  | 0                     | 0  | 0  | 0  | -16                 |

#### Note

1. 0 dB is equal to 17 mV (RMS).

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 9.2.4 DATA BYTE FOR DATA MODE

Table 14 Bit description of SAD register for data mode (SAD = 10)

| BIT       | VALUE | DESCRIPTION                                           |

|-----------|-------|-------------------------------------------------------|

| E7        |       | VIF-AGC and port features                             |

|           |       | dependent on bit E5; see Table 15                     |

| E6        |       | L standard PLL gating                                 |

|           | 1     | gating in case of 36 % positive modulation            |

|           | 0     | gating in case of 0 % positive modulation             |

| E5        |       | VIF, SIF and tuner minimum gain                       |

|           |       | dependent on bit E7; see Table 15                     |

| E4 to E2  |       | Vision intermediate frequency selection               |

|           |       | see Table 16                                          |

| E1 and E0 |       | Sound intercarrier frequency selection (sound 2nd IF) |

|           | 00    | $f_{FM} = 4.5 \text{ MHz}$                            |

|           | 01    | $f_{FM} = 5.5 \text{ MHz}$                            |

|           | 10    | $f_{FM} = 6.0 \text{ MHz}$                            |

|           | 11    | f <sub>FM</sub> = 6.5 MHz; note 1                     |

#### Note

1. For positive modulation choose 6.5 MHz.

Table 15 Options in extended TV mode; bit B3 = 0 of SAD 00 register

| FUNCTION | BIT E         | E7 = 0        | BIT E7 = 1                    |                                       |  |  |

|----------|---------------|---------------|-------------------------------|---------------------------------------|--|--|

| FUNCTION | BIT E5 = 0    | BIT E5 = 1    | BIT E5 = 0                    | BIT E5 = 1                            |  |  |

| Pin OP1  | port function | port function | port function                 | VIF-AGC external input <sup>(1)</sup> |  |  |

| Pin OP2  | port function | port function | VIF-AGC output <sup>(1)</sup> | port function                         |  |  |

| Gain     | normal gain   | minimum gain  | normal gain                   | external gain                         |  |  |

#### Note

1. The corresponding port function has to be disabled (set to 'high-impedance'); see Table 11 and Chapter 12, Table of Characteristics, note 12.

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

Table 16 TV standard selection for VIF

|    | VIDEO IF SELECT B | £ (MILL) |                        |

|----|-------------------|----------|------------------------|

| E4 | E3                | E2       | f <sub>VIF</sub> (MHz) |

| 0  | 0                 | 0        | 58.75 <sup>(1)</sup>   |

| 0  | 0                 | 1        | 45.75 <sup>(1)</sup>   |

| 0  | 1                 | 0        | 38.9                   |

| 0  | 1                 | 1        | 38.0                   |

| 1  | 0                 | 0        | 33.9                   |

| 1  | 0                 | 1        | 33.4                   |

| 1  | 1                 | 0        | not applicable         |

| 1  | 1                 | 1        | not applicable         |

#### Note

Table 17 Data setting after power-on reset (default setting with a resistor on pin SIOMAD)

| REGISTER       | MSB |    |    |    |    |    |    | LSB |

|----------------|-----|----|----|----|----|----|----|-----|

| REGISTER       | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| Switching mode | 1   | 1  | 0  | 1  | 0  | 1  | 1  | 0   |

| Adjust mode    | 0   | 0  | 1  | 1  | 0  | 0  | 0  | 0   |

| Data mode      | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0   |

Table 18 Data setting after power-on reset (default setting without a resistor on pin SIOMAD)

| REGISTER       | MSB |    |    |    |    |    |    | LSB |

|----------------|-----|----|----|----|----|----|----|-----|

| REGISTER       | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

| Switching mode | 1   | 1  | 0  | 1  | 0  | 1  | 1  | 0   |

| Adjust mode    | 0   | 0  | 1  | 1  | 0  | 0  | 0  | 0   |

| Data mode      | 0   | 0  | 0  | 0  | 0  | 1  | 0  | 0   |

<sup>1.</sup> Pin SIOMAD can be used for the selection of the different NTSC standards without I<sup>2</sup>C-bus. With a resistor on pin SIOMAD,  $f_{VIF} = 58.75$  MHz; without a resistor on pin SIOMAD,  $f_{VIF} = 45.75$  MHz (NTSC-M).

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### **10 LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL           | PARAMETER                                                                      | CONDITIONS | MIN.  | MAX.  | UNIT |

|------------------|--------------------------------------------------------------------------------|------------|-------|-------|------|

| V <sub>P</sub>   | supply voltage                                                                 |            | _     | 5.5   | V    |

| V <sub>n</sub>   | voltage on                                                                     |            |       |       |      |

|                  | pins VIF1, VIF2, SIF1, SIF2, OP1, OP2, V <sub>P</sub> , and FMPLL              |            | 0     | $V_P$ | V    |

|                  | pin TAGC                                                                       |            | 0     | 8.8   | V    |

| t <sub>sc</sub>  | short-circuit time to ground or V <sub>P</sub>                                 |            | _     | 10    | s    |

| T <sub>stg</sub> | storage temperature                                                            |            | -25   | +150  | °C   |

| T <sub>amb</sub> | ambient temperature                                                            |            |       |       |      |

|                  | TDA9885T (SO24), TDA9885TS (SSOP24),<br>TDA9886T (SO24) and TDA9886TS (SSOP24) |            | -20   | +70   | °C   |

|                  | TDA9885HN (HVQFN32)<br>and TDA9886HN (HVQFN32)                                 |            | -20   | +85   | °C   |

| V <sub>es</sub>  | electrostatic discharge voltage on all pins                                    | note 1     | -400  | +400  | V    |

|                  |                                                                                | note 2     | -4000 | +3500 | V    |

#### **Notes**

- 1. Machine model in accordance with SNW-FQ-302B: class C, discharging a 200 pF capacitor via a 0.75  $\mu$ H series inductance.

- 2. Human body model in accordance with SNW-FQ-302A: class 2, discharging a 100 pF capacitor via a 1.5 k $\Omega$  series resistor.

### 11 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS  | VALUE | UNIT |

|----------------------|---------------------------------------------|-------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air |       |      |

|                      | TDA9885T (SO24)                             |             | 76    | K/W  |

|                      | TDA9885TS (SSOP24)                          |             | 118   | K/W  |

|                      | TDA9885HN (HVQFN32)                         |             | 40    | K/W  |

|                      | TDA9886T (SO24)                             |             | 76    | K/W  |

|                      | TDA9886TS (SSOP24)                          |             | 118   | K/W  |

|                      | TDA9886HN (HVQFN32)                         |             | 40    | K/W  |

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

TDA9885; TDA9886

#### 12 CHARACTERISTICS

$V_P = 5$  V;  $T_{amb} = 25$  °C; see Table 20 for input frequencies; B/G standard is used for the specification ( $f_{PC} = 38.9$  MHz;  $f_{SC} = 33.4$  MHz; PC/SC = 13 dB;  $f_{mod} = 400$  Hz); input level  $V_{i(VIF)} = 10$  mV (RMS) (sync level for B/G; peak white level for L); IF input from 50  $\Omega$  via broadband transformer 1 : 1; video modulation DSB; residual carrier for B/G is 10 % and for L is 3 %; video signal in accordance with "CCIR line 17 and line 330" or "NTC-7 Composite"; measurements taken in test circuit of Fig.23; unless otherwise specified.

| SYMBOL                       | PARAMETER                                                                | CONDITIONS                                                                | MIN. | TYP.  | MAX. | UNIT |

|------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-------|------|------|

| Supply (pin V <sub>P</sub> ) | )                                                                        |                                                                           | •    | 1     | 1    | 1    |

| V <sub>P</sub>               | supply voltage                                                           | note 1                                                                    | 4.5  | 5.0   | 5.5  | V    |

| I <sub>P</sub>               | supply current                                                           |                                                                           | 52   | 63    | 70   | mA   |

| P <sub>tot</sub>             | total power dissipation                                                  |                                                                           | _    | 305   | 385  | mW   |

| Power-on rese                | T :T                                                                     |                                                                           | •    | •     | '    | '    |

| V <sub>P(start)</sub>        | supply voltage for start of reset                                        | decreasing supply voltage                                                 | 2.5  | 3.0   | 3.5  | V    |

| V <sub>P(stop)</sub>         | supply voltage for end of reset                                          | increasing supply<br>voltage; I <sup>2</sup> C-bus<br>transmission enable | _    | _     | 4.4  | V    |

| τρ                           | time constant (R $\times$ C) for network at pin V <sub>P</sub>           | for applications without I <sup>2</sup> C-bus                             | 1.2  | _     | _    | μs   |

| VIF amplifier (p             | pins VIF1 and VIF2)                                                      |                                                                           |      |       |      |      |

| $V_{i(VIF)(rms)}$            | VIF input voltage sensitivity (RMS value)                                | -1 dB video at output                                                     | _    | 60    | 100  | μV   |

| V <sub>i(max)(rms)</sub>     | maximum input voltage (RMS value)                                        | +1 dB video at output                                                     | 150  | 190   | -    | mV   |

| V <sub>i(ovI)(rms)</sub>     | overload input voltage<br>(RMS value)                                    | note 2                                                                    | _    | -     | 440  | mV   |

| $\Delta V_{IF(int)}$         | internal IF amplitude difference<br>between picture and sound<br>carrier | within AGC range;<br>Δf = 5.5 MHz                                         | _    | 0.7   | _    | dB   |

| G <sub>VIF(cr)</sub>         | VIF gain control range                                                   | see Fig.7                                                                 | 60   | 66    | _    | dB   |

| B <sub>VIF(-3dB)(II)</sub>   | lower limit –3 dB VIF bandwidth                                          |                                                                           | _    | 15    | _    | MHz  |

| B <sub>VIF(-3dB)(ul)</sub>   | upper limit -3 dB VIF bandwidth                                          |                                                                           | _    | 80    | _    | MHz  |

| R <sub>i(dif)</sub>          | differential input resistance                                            | note 3                                                                    | _    | 2     | _    | kΩ   |

| C <sub>i(dif)</sub>          | differential input capacitance                                           | note 3                                                                    | _    | 3     | _    | pF   |

| VI                           | DC input voltage                                                         |                                                                           | _    | 1.93  | _    | V    |

| FPLL and true                | synchronous video demodulator;                                           | note 4                                                                    |      | •     | •    |      |

| f <sub>VCO(max)</sub>        | maximum oscillator frequency for carrier regeneration                    | f = 2f <sub>PC</sub>                                                      | 120  | 140   | _    | MHz  |

| f <sub>VIF</sub>             | vision carrier operating                                                 | see Table 14                                                              | _    | 33.4  | _    | MHz  |

|                              | frequencies                                                              |                                                                           | _    | 33.9  | _    | MHz  |

|                              |                                                                          |                                                                           | _    | 38.0  | _    | MHz  |

|                              |                                                                          |                                                                           | _    | 38.9  | _    | MHz  |

|                              |                                                                          |                                                                           | _    | 45.75 | _    | MHz  |

|                              |                                                                          |                                                                           | _    | 58.75 | _    | MHz  |

TDA9885; TDA9886

### I<sup>2</sup>C-bus controlled single and multistandard alignment-free IF-PLL demodulators

| SYMBOL                      | PARAMETER                                                  | CONDITIONS                                                 | MIN.                 | TYP.               | MAX. | UNIT   |

|-----------------------------|------------------------------------------------------------|------------------------------------------------------------|----------------------|--------------------|------|--------|

| $\Delta f_{VIF}$            | VIF frequency window of digital acquisition help           | related to f <sub>VIF</sub> ;<br>see Fig.10                | _                    | ±2.3               | -    | MHz    |

| t <sub>acq</sub>            | acquisition time                                           | BL = 70 kHz; note 5                                        | _                    | _                  | 30   | ms     |

| Vi(lock)(rms)               | input voltage sensitivity for PLL to be locked (RMS value) | measured on pins VIF1<br>and VIF2;<br>maximum IF gain      | _                    | 30                 | 70   | μV     |