SAPI DAUGHTERBOARD

# **PM5945**

# SONET ATM PHYSICAL INTERFACE BOARD

#### SAPI DAUGHTERBOARD

# **CONTENTS**

| OVERVIEW                                        | 1  |

|-------------------------------------------------|----|

| FUNCTIONAL DESCRIPTION                          | 2  |

| DAUGHTERBOARD REGISTERS                         | 8  |

| INTERFACE DESCRIPTION                           | 9  |

| SUNI REGISTER ADDRESS MAP                       | 16 |

| RECEIVE DROP SIDE TIMING                        | 18 |

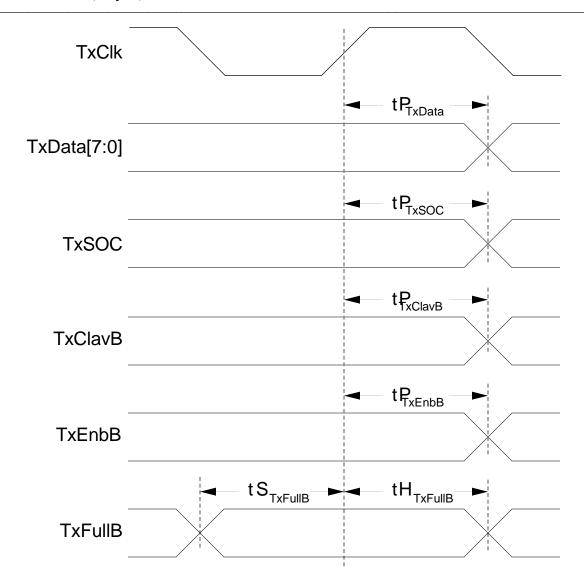

| TRANSMIT DROP SIDE TIMING                       | 20 |

| CHARACTERISTICS                                 | 22 |

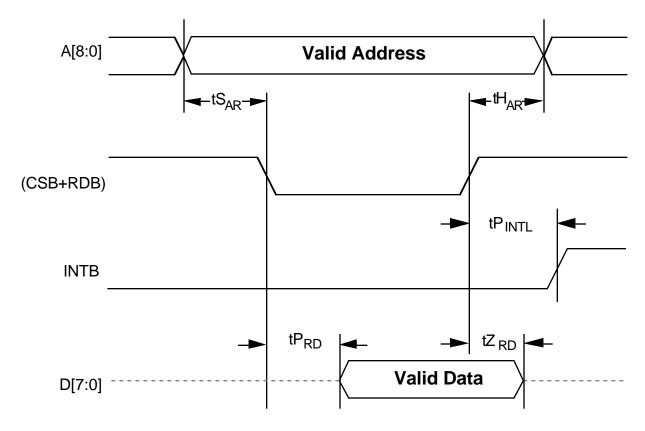

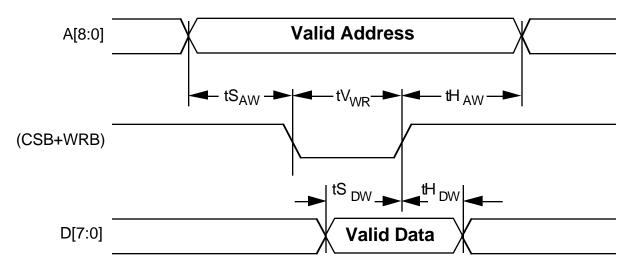

| MICROPROCESSOR INTERFACE TIMING CHARACTERISTICS | 22 |

| APPENDIX A: PAL EQUATIONS                       | A1 |

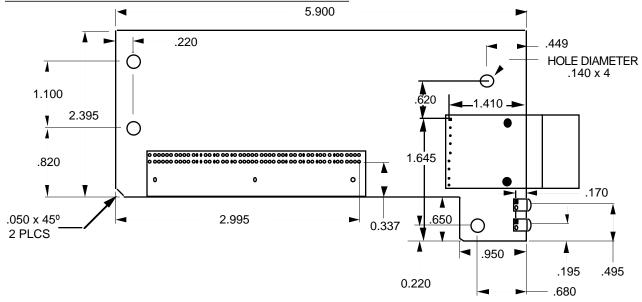

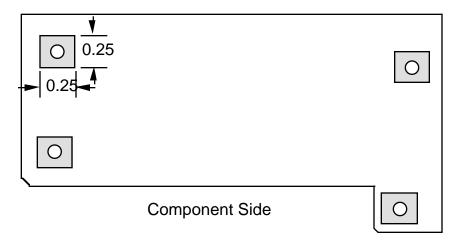

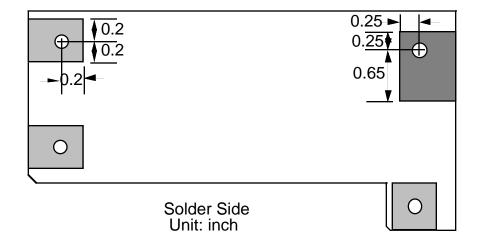

| APPENDIX B: MECHANICAL DRAWINGS                 | B1 |

| APPENDIX C: MATERIAL LIST                       |    |

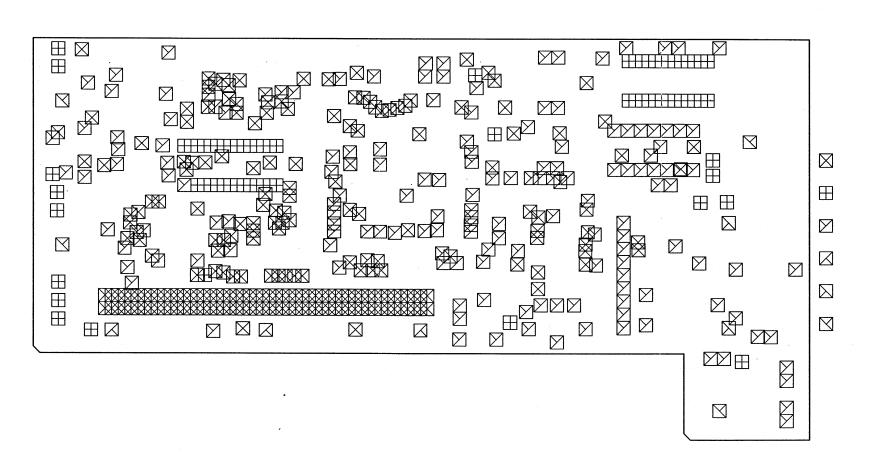

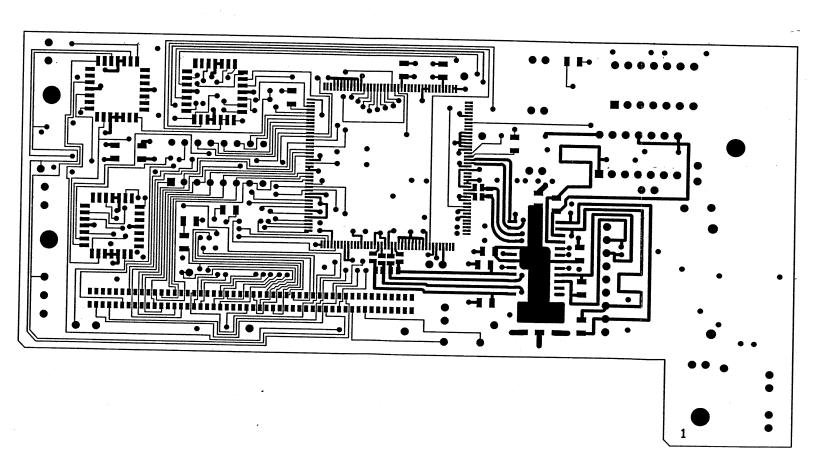

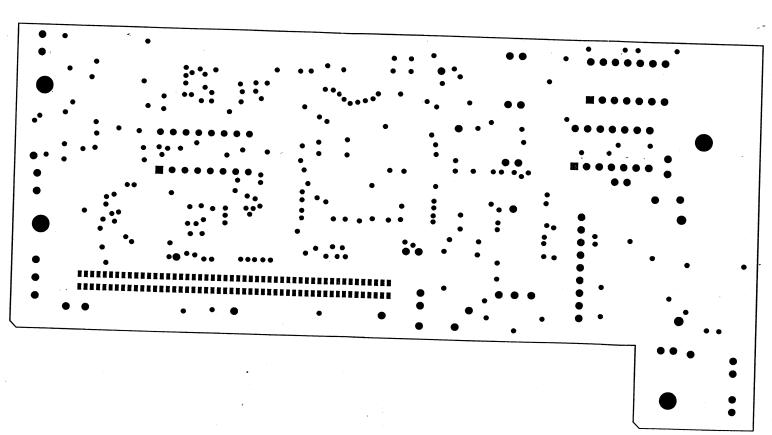

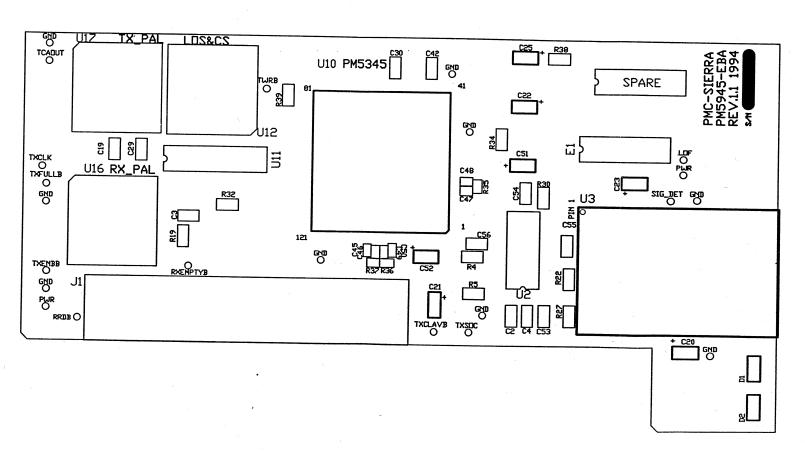

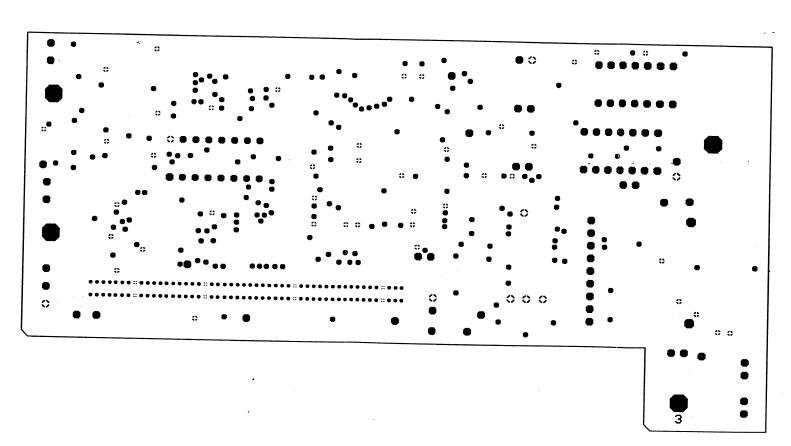

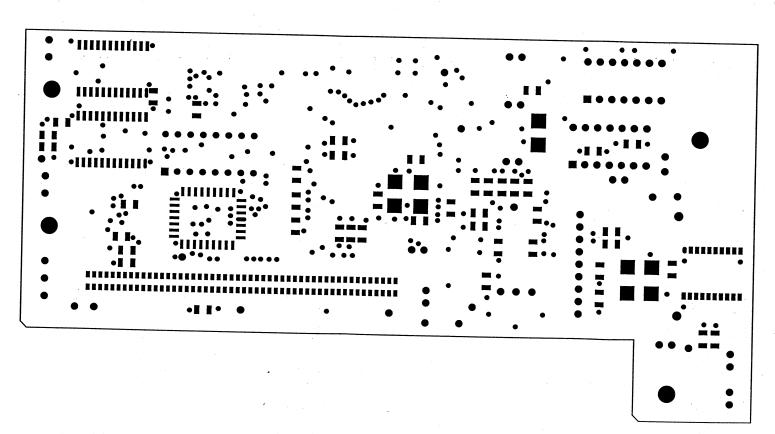

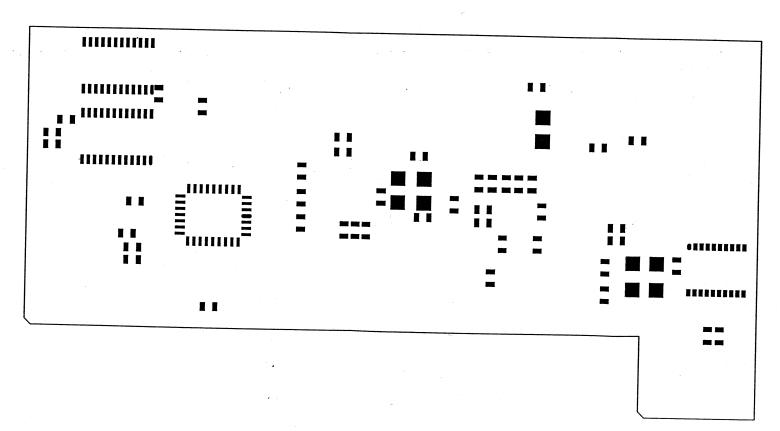

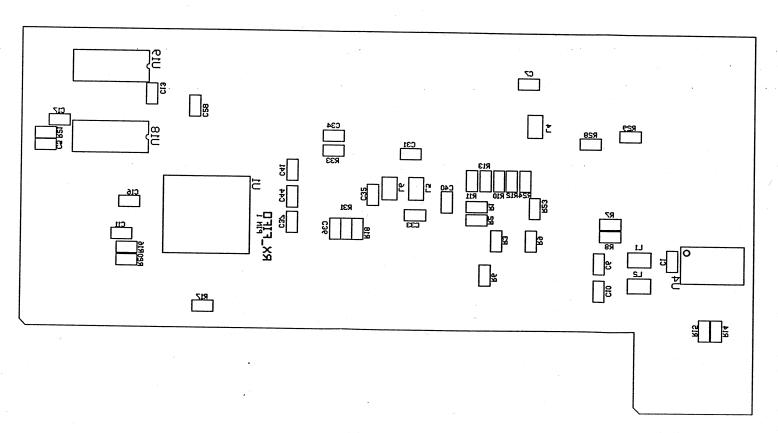

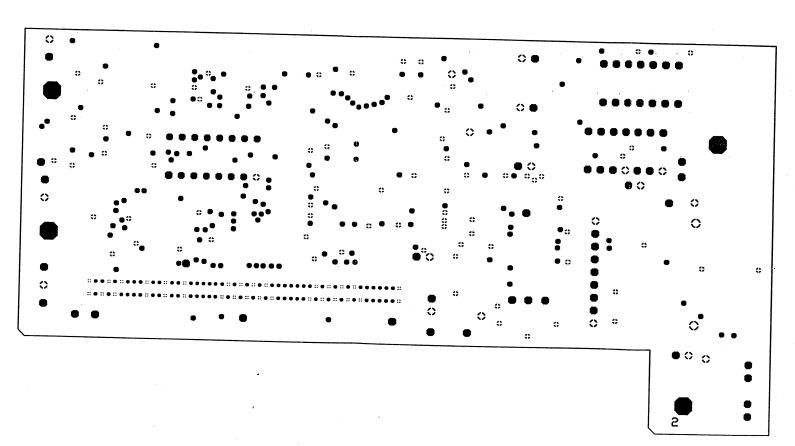

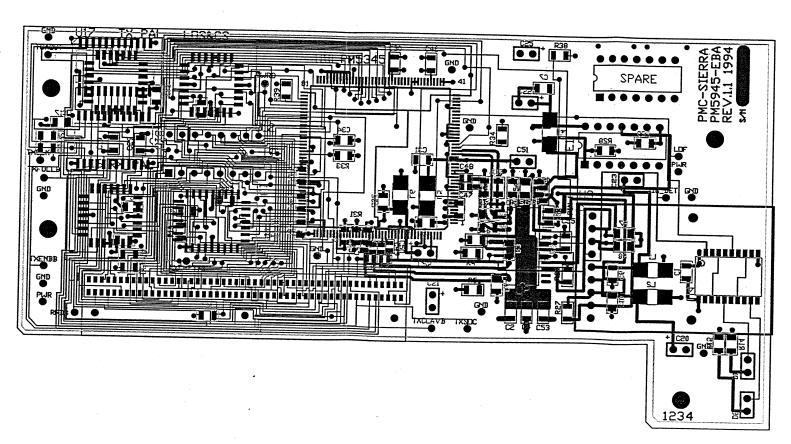

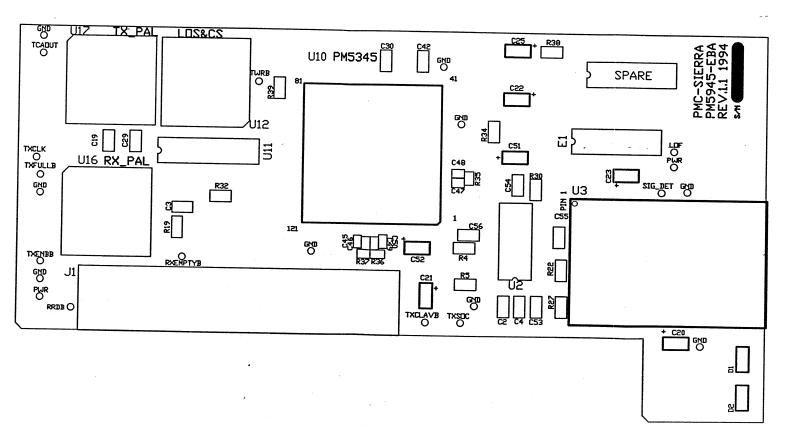

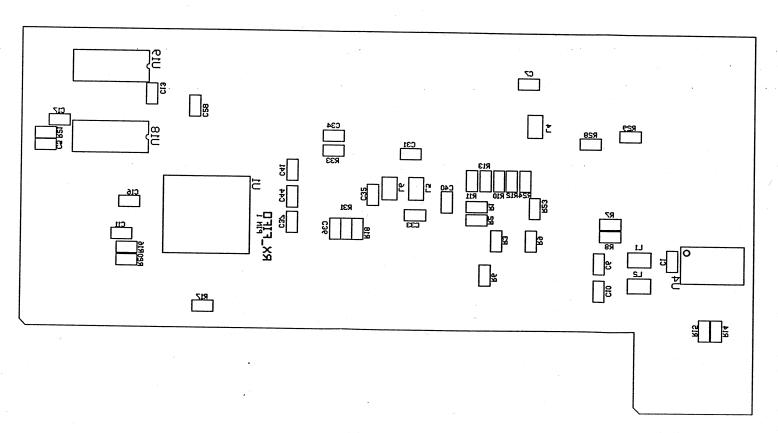

| APPENDIX D: COMPONENT PLACEMENT                 | D1 |

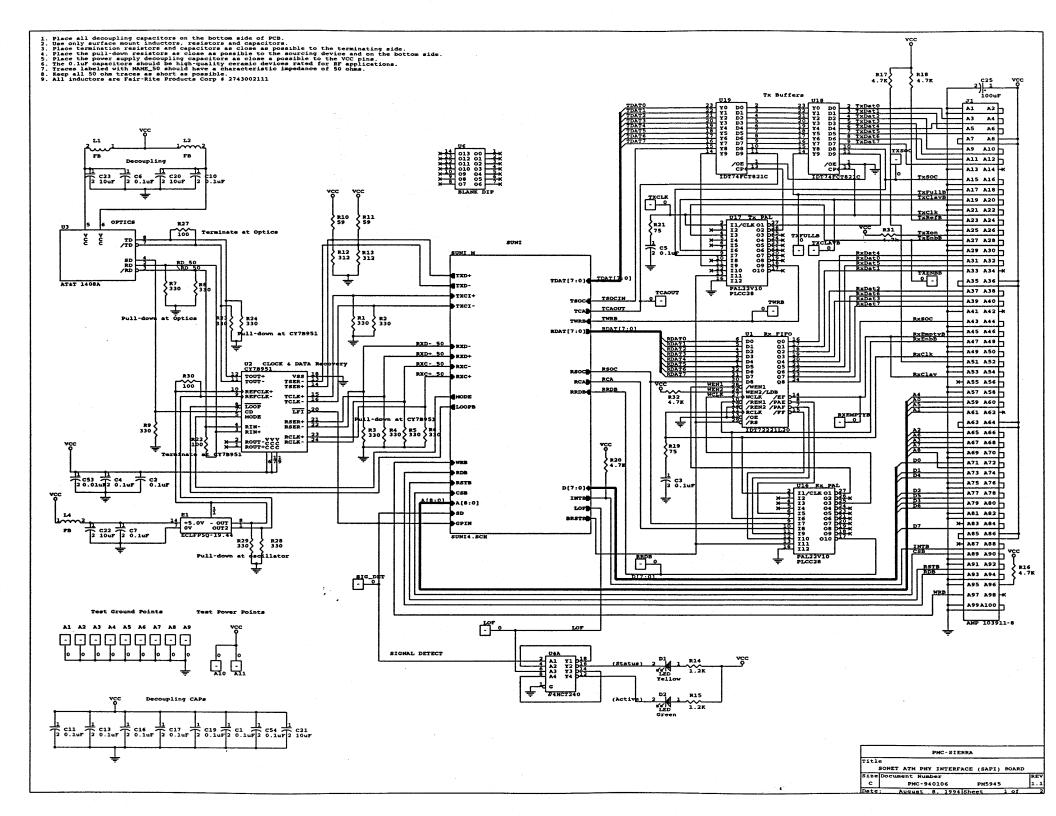

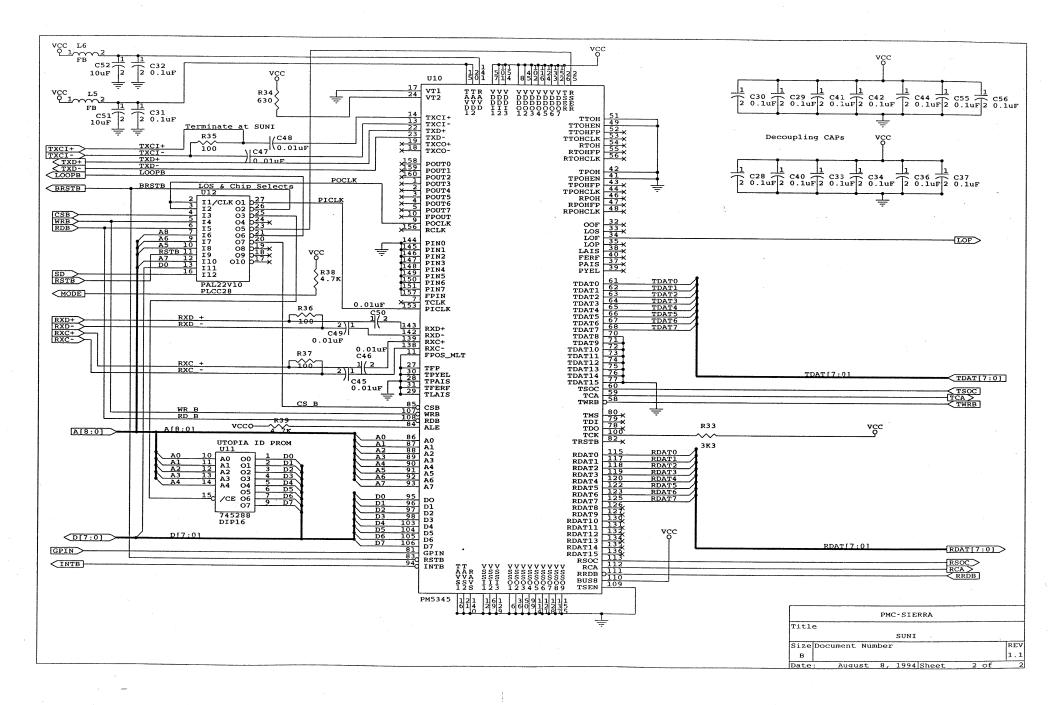

| APPENDIX E: SCHEMATICS                          | E1 |

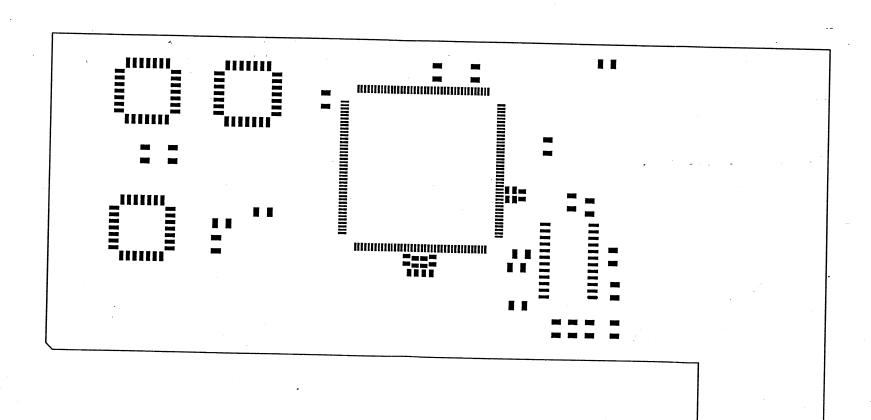

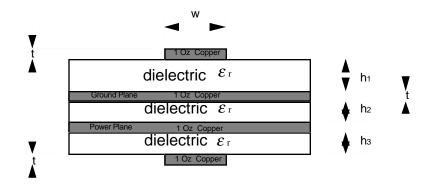

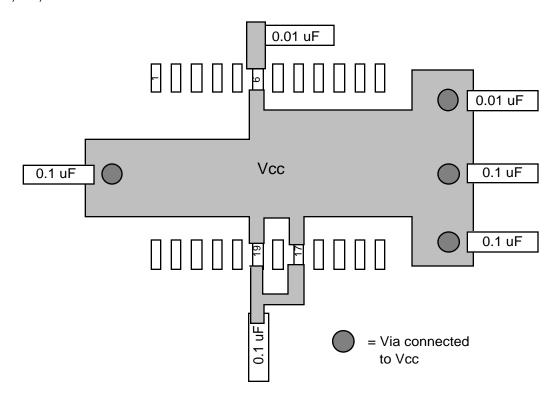

| APPENDIX F: LAYOUT NOTES                        | F1 |

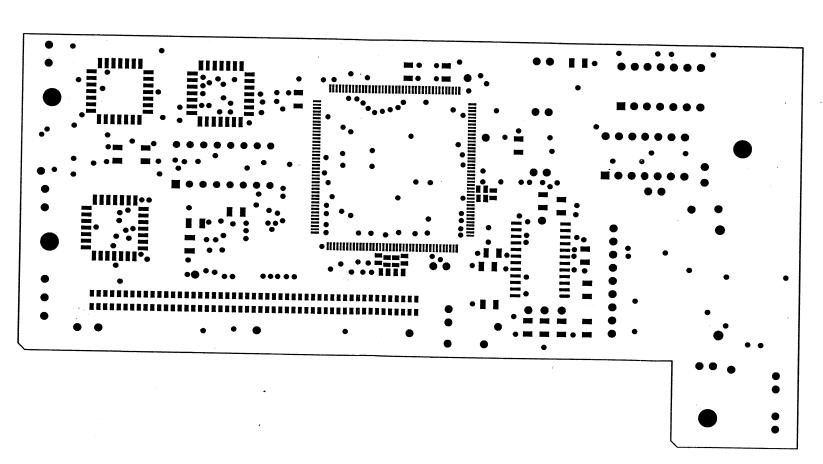

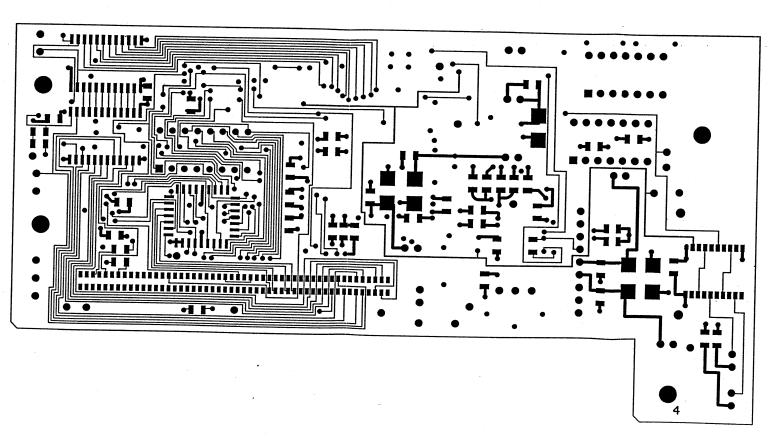

| APPENDIX G: LAYOUT                              | G′ |

SAPI DAUGHTERBOARD

#### **OVERVIEW**

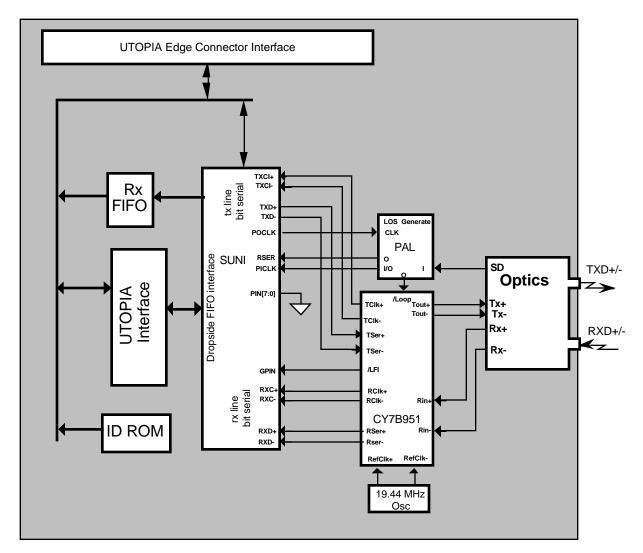

The PM5945 SAPI daughter board contains the PMC PM5345 SUNI-155 (SATURN User Network Interface), the Cypress CY7B951 SONET/SDH Serial Transceiver (a clock and data recovery and clock synthesis unit), and optical PMD in a complete optical ATM (Asynchronous Transfer Mode) physical interface. The SUNI is an ATM physical layer processor for a SONET STS-3C transmission system. This daughter board has been designed to mate with National Semiconductor Corporation's Vicksburg EISA adapter motherboard to form a complete evaluation system. The SAPI daughter board is configured, monitored, and powered through a 100 pin edge connector that mates with the Vicksburg motherboard. The motherboard provides all of the software and decoding logic necessary to directly access all of the registers on the SAPI board.

The SAPI line side interface uses any 9-pin duplex SC receptacle. The optical Transceiver PMD device runs at 155.52 MHz. On the receive side, the receive optical PMD connects to the clock and data recovery section of the Cypress SONET/SDH Serial Transceiver (CY7B951). The output of the CY7B951 is accoupled to the SUNI's bit serial input. On the transmit side, the SUNI's PECL data outputs connect directly to the Cypress CY7B951 serial input which buffers the data and outputs the data directly to the transmit optics. The CY7B951 can mux the output data to the input of the PLL and transfer back the recovered clock and data to the input of the SUNI for diagnostic purposes.

The SAPI drop side interface uses a 100 pin edge connector. The 22V10 PLDs transform the SUNI drop side signals to comply with the UTOPIA like signals of the Vicksburg motherboard. The receive drop side also incorporates an additional FIFO, as the internal 4 cell FIFO of the SUNI device is insufficient to handle the latency time between burst cell reads by the R-FRED device on the Vicksburg motherboard.

SAPI DAUGHTERBOARD

### **FUNCTIONAL DESCRIPTION**

### **Block Diagram**

### **SUNI**

The SUNI is a monolithic integrated circuit that implements the SONET/SDH processing and ATM mapping functions of a 155 Mbit/s SONET STS-3c User Network Interface. It is the heart of the SAPI board; all traffic goes through the SUNI. On the line side, the SUNI transmits SONET frames through the line interface and receives frames from the line interface. On the drop side, the SUNI sinks cells provided by the buffer interface and sources cells to the buffer interface. Below, the SUNI is briefly described.

SAPI DAUGHTERBOARD

The SUNI receives SONET/SDH frames via a bit serial interface, and processes section, line, and path overhead. It performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (FEBE) are also accumulated. The SUNI interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload.

The SUNI frames to the ATM payload using cell delineation. Header check sequence (HCS) error correction is provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon detection of an Uncorrectable HCS error. The ATM cell payloads are descrambled. The ATM cells that are passed are written to a four cell FIFO buffer. The received cells are read from the FIFO using a generic 8-bit wide datapath interface. Counts of received ATM cell headers that are erred and uncorrectable, and also those that are erred and correctable, are accumulated independently for performance monitoring purposes.

The SUNI transmits SONET/SDH frames via a bit serial interface, and formats section, line, and path overhead bytes appropriately. It performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and inserts section, line, and path bit interleaved parity (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path far end block error indications (FEBE) are also inserted. The SUNI generates the payload pointer (H1, H2) and inserts the synchronous payload envelope which carries the ATM cell payload. The SUNI also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors, and illegal pointers, which are useful for system diagnostics and tester applications.

Transmit ATM cells are written to an internal four cell FIFO using a generic 8-bit wide datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one cell. The SUNI provides generation of the header check sequence and scrambles the payload of the ATM cells. Each of these transmit ATM cell processing functions can be enabled or bypassed.

The SUNI is configured, controlled and monitored via the UTOPIA interface to the Vicksburg motherboard.

For a complete description of the SUNI, please refer to PMC-Sierra's PM5345 datasheet.

SAPI DAUGHTERBOARD

#### CY7B951

The Cypress SONET/SDH Serial Transceiver is an integrated SONET clock and data recovery/clock synthesis device. The internal receive PLL recovers a 155.52 MHz clock from a incoming NRZ or NRZI data and re-times the data. The receive PLL uses the reference clock (19.44 MHz) to provide a 155.52 MHz clock in the absence of input data. The reference clock is also used to improve PLL lock time. The differential input data is re-timed by the recovered clock and presented as the PECL differential output data.

The transmit section of the SONET/SDH Serial Transceiver contains a PLL that takes a reference clock and multiplies it by 8 to produce a 155.52 MHz PECL differential output clock. The transmit PECL differential input pair are used to buffer the transmit PECL output of the SUNI. This input can also be muxed into the receive side PLL for clock and data recovery (used for diagnostic purposes).

#### Line Interface

The receive line interface consists of receive optics connected to a clock and data recovery unit. To ensure that there is a clock in the absence of incoming light, the signal detect (SD) output of the optics is used to select between the serial and parallel mode of operation on the receive side of the SUNI device. In normal operation (good incoming signal) the SUNI device is in the serial mode and accepts clock and data from the high speed interface (RSER is high). In loss of signal condition, the SUNI device is switched to the parallel mode and accepts data from the PICLK and PIN[7:0] inputs. The POCLK is switched in to generate the 19.44 MHz PICLK. This technique also guarantees that the SUNI will generate a LOS indication when the optics loses incoming light. This is done due to the CY7B951 not squelching the data in a loss of signal condition.

The transmit line interface consists of the SUNI PECL transmit outputs which are buffered by the Cypress CY7B951 and then fed directly to the transmit optics.

Optical transceivers having a standard 9-pin duplex SC receptacle are used.

The SUNI is configured for bit serial operation. The 155.52 MHz transmit clock source is synthesized by the CY7B951 from a 19.44 MHz oscillator. The receive clock and data recovery is supplied by the Cypress CY7B951 device.

If the loop back select is enabled on the CY7B951 the transmit data is muxed in to the receive PLL and the recovered clock and data are fed back to the SUNI device.

The SUNI can also be configured for loop time operation. When configured for loop time operation, only the receive clock and data are required.

SAPI DAUGHTERBOARD

### **UTOPIA Identification ROM**

The upper 32 bytes of the address space is used by the UTOPIA indentification ROM to hold the interface configuration information.

| Address     | Function      | Address     | Function                 |

|-------------|---------------|-------------|--------------------------|

| 0x1C0-0x1DF | Reserved      | 0x1E4-0x1EB | 64 or 48-bit Address     |

| 0x1E0       | Protocol Type | 0x1EC-0x1EF | Reserved                 |

| 0x1E1       | Media Type    | 0x1F0-0x1FF | Manufacturer ID, Version |

| 0x1E2-0x1E3 | Capability    |             |                          |

### **Protocol Type:**

Contains an identifier for the type of framing/protocol used on this PHY interface. The SAPI board has 0x0C programmed into this location which specifies 155.52 Mbps (SONET/OC-3) ATM Forum standard. The following values are defined:

| Value     | Framing Type                                           |

|-----------|--------------------------------------------------------|

| 0x00-0x03 | Reserved                                               |

| 0x04      | 44.736 Mbps (DS-3) ATM Forum Standard                  |

| 0x05-0x07 | Reserved                                               |

| 0x08      | 100 Mbps (4B/5B block coded) ATM Forum Standard        |

| 0x09-0x0B | Reserved                                               |

| 0x0C      | 155.52 Mbps (SONET/OC-3) ATM Forum Standard            |

| 0x0D      | 155.52 Mbps (8B/10B block coded) ATM Forum<br>Standard |

| 0x0E-0xFE | Reserved                                               |

| 0xFF      | Undefined/Unidentified Protocol Type                   |

SAPI DAUGHTERBOARD

### Media Type:

Contains an identifier for the type of media used on this PHY interface. The SAPI board has 0x05 programmed into this location which specifies a low cost Multimode fiber (LCMF, 500m). The following values are defined:

| Value     | Media Type                                    |

|-----------|-----------------------------------------------|

| 0x00      | Category 3 Unshielded Twisted Pair (CAT3-UTP) |

| 0x01      | Category 5 Unshielded Twisted Pair (CAT5-UTP) |

| 0x02      | Shielded Twisted Pair (STP)                   |

| 0x03      | Reserved                                      |

| 0x04      | Very Low-Cost Multimode Fiber (VLCMF, 150 m)  |

| 0x05      | Low-Cost Multimode Fiber (LCMF, 500 m)        |

| 0x06      | Multimode Fiber (MF, 2km)                     |

| 0x07      | Reserved                                      |

| 0x08      | Single Mode Fiber (SMF)                       |

| 0x09-0x0B | Reserved                                      |

| 0x0C      | Coaxial Cable (COAX)                          |

| 0x0D      | Reserved                                      |

| 0x0F      | Undefined/Unidentified Media Type             |

### Capability:

Contains two octets which define the capability of the PHY interface. The SAPI board has 0x21 & 0x0C programmed into octets 1 & 2 respectively. The capabilities include:

- 1. TxRef, =1 when this interface supports the TxRefB UTOPIA signal.

- 2. RxRef, =1 when this interface supports the RxRefB UTOPIA signal.

- 3. TxClav, =1 when this interface supports the TxClav UTOPIA signal.

- 4. RxClav, =1 when this interface supports the RxClav UTOPIA signal.

SAPI DAUGHTERBOARD

- 5. TxXon, =1 when this interface supports the TxXon UTOPIA signal.

- 6. Ver[3:0], 4 bits UTOPIA version number, value for this specification =1.

- 7. D16, =1 to indicate 16-bit datapath, 0 = 8-bit datapath.

- 8. HEC, =1 to indicate the HEC is carried in the UDF(1) field.

- 9. HCS, =1 to indicate HCS is carried in the UDF(2) field, for 16-bit mode only.

- 10. NOTE "rsvd" stands for Reserved.

### Assignments of fields are shown below.

| r | svd | HCS  | HEC  | D16   | Ver[3] | Ver[2] | Ver[1] | Ver[0] | octet 1 |

|---|-----|------|------|-------|--------|--------|--------|--------|---------|

| r | svd | rsvd | rsvd | TxXon | RxClav | TxClav | RxRef  | TxRef  | octet 2 |

#### 64 or 48-bit Address:

Contains eight octets which define the 64 or 48-bit address of the PHY interface. If a 48-bit address is used, the 2 most significant octets are zero filled. The address is stored in Big-Endian format (MSB is in the LS address). The SAPI board has 0x00 programmed into this location.

#### Reserved:

Reserved for future expansion.

#### Manufacturer ID, etc.:

Contains sixteen octets which identify the manufacturer of the PHY interface. Using the ASCII character set (7-bit code) is encouraged. Three octets of ASCII representing the manufacture ID and 13 octets of part number.

| M.S | 0   | 1   | 2  | 3 | 4 | 5 | 6 | 7 |

|-----|-----|-----|----|---|---|---|---|---|

| L.S |     |     |    |   |   |   |   |   |

| 0   | NUL | DLE | SP | 0 | @ | Р | \ | р |

| 1   | SOH | DC1 | !  | 1 | А | Q | а | q |

| 2   | STX | DC2 | "  | 2 | В | R | b | r |

| 3   | ETX | DC3 | #  | 3 | С | S | С | s |

| 4   | EOT | DC4 | \$ | 4 | D | Т | d | t |

| 5   | ENQ | NAK | %  | 5 | E | U | е | u |

SAPI DAUGHTERBOARD

| 6 | ACK | SYN | & | 6      | F | V  | f             | v   |

|---|-----|-----|---|--------|---|----|---------------|-----|

| 7 | BEL | ETB | 1 | 7      | G | W  | g             | W   |

| 8 | BS  | CAN | 1 | 8      | Н | X  | h             | z   |

| 9 | HT  | EM  | ) | 9      |   | Y  | i             | V   |

| A | LF  | SUM | * | :      | J | Z  | <u>'</u><br>i | Z   |

| В | VT  | ESC | + |        | K |    | k             |     |

| С | FF  | FS  |   | ,<br>< | L | \  | ı             | ı   |

| D | CR  | GS  | - | =      | M | 1  | m             |     |

| E | SO  | RS  |   | >      | N |    | n             | ~   |

| F | SI  | μS  |   | ?      | 0 | <- | 0             | DEL |

| Р  | М  | С  | _  | Р  | М  | 5  | 9  | 4  | 5  | -  | S  | Α  | Р  | I  |    |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 50 | 4d | 43 | 2d | 50 | 4d | 35 | 39 | 34 | 35 | 2d | 53 | 41 | 50 | 49 | 20 |

#### DAUGHTERBOARD REGISTERS

The SAPI daughterboard has two write only register bits. One bit is a software reset bit and the other is a transmit loopbacd enable bit.

#### **Software Reset**

The software reset bit is at binary address 1110xxxxx (the most significant bit is at the far left and the least significant is at the far right). The least significant 5 bits of the address are don't cares. Writing a binary xxxxxxx1 to this address will hold the SUNI, the FIFO, and the PALs reset. Writing a binary xxxxxxx0 to this address will remove the reset. The most significant 7 bits of data are don't cares. This is a write only bit. A hardware reset removes the software reset.

### **Transmit Loopback Enable**

The transmit loopback enable bit is at binary address 1111xxxxx (the most significant bit is at the far left and the least significant is at the far right). The least significant 5 bits of the address are don't cares. Writing a binary xxxxxxxx1 to this address will mux the transmit output data going to the optics, into the inputs of the clock and data recovery PLL. This is all done inside the Cypress CY7B951 device.

SAPI DAUGHTERBOARD

This allows a diagnostic loopback to be done at the Cypress part which will verify the connections and functionality between the Cypress device and the SUNI device. done. Writing a binary xxxxxxx0 to this address will disable transmit diagnostic loopback. The most significant 7 bits of data are don't cares. This is a write only bit. A hardware reset removes the transmit loopback enable (if it was set).

### INTERFACE DESCRIPTION

#### **UTOPIA** Interface

The UTOPIA Interface makes the SUNI drop side receive and transmit signals compatible with the UTOPIA 1.04 interface specification. It consists of two high speed 22V10 PALs, two high speed IDT74FCT377C buffers, and a receive IDT72201 clocked FIFO. The 22V10 PALs can be replaced with faster versions if you must run at a higher than 20 MHz TxClk and RxClk clock signals.

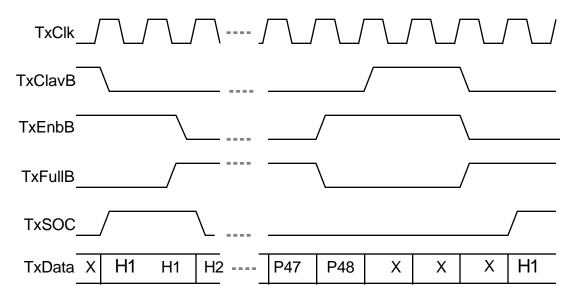

The Transmit drop side interface is controlled by the ATM layer through the edge connector. All the transmit signals from the ATM layer change with respect to the TxClk. All the input signals to the ATM layer are sampled on the rising edge of the TxClk.

The SUNI device asserts the TCA signal when it has a complete empty cell available. This signal goes to the PAL (U17) and causes the TxFullB signal to the ATM layer to be de-asserted (high). The ATM layer asserts the TxClavB signal (low) when it has a complete Cell of data to transfer to the PHY device. The TxEnbB signal from the ATM layer (Vicksburg card) is the output of the TxFullB signal from the PHY layer gated with the TxClavB signal from the ATM layer. The way the TxEnbB signal goes active (low) depends on whether the ATM layer is ready to send a cell of data before the PHY layer becomes available to accept the data, or whether the PHY layer is ready to send data.

The case where the ATM layer has a cell available for transmission before the PHY layer is ready to accept the cell is handled as follows; The Vicksburg card drives the TSOC signal active (high) and the TxData bus with valid octet byte zero coincident with the assertion of the TxClavB signal, and waits for the TxFullB signal from the PHY layer to go inactive (high). When the PHY device has a cell available, the TxFullB signal goes inactive (high) and then the TxEnbB signal is immediately asserted (low) (after a delay through a gate). On the next rising edge of the TxClk signal, the second byte of data is driven onto the TxData bus and the TSOC signal is de-asserted (low).

The case where the PHY layer is ready to accept a cell of data before the ATM layer is ready to transmit the cell is handled as follows; The PHY layer de-asserts the TxFullB signal (high) and waits for the TxEnbB signal to go active (low). When the

SAPI DAUGHTERBOARD

ATM layer has a cell available for transmission, the TxClavB is set active (low) on the rising edge of the TxClk signal, and drives the TSOC signal active (high) and the TxData bus with valid octet byte zero . The TxClavB signal sets the TxEnbB signal active (low) through a gate delay.

In either case, the TxData bus is continually clocked into the first buffer (U18) by the rising edges of the TxClk signal. The assertion of the TxEnbB signal enables the TWRB signal to the SUNI device. On the falling edge of the TWRB signal (rising edge of TxClk) the data from U18 is clocked into the second buffer (U19). The clock signal to U19 is generated by the PAL (inverted TxClk). The ATM layer updates the TxData with new data on the rising edge of each TxClk signal while TxEnbB is asserted and the TxFullB signal is de-asserted (high). If at the end of the current cell transfer, another cell is available (TCA remains active), the TxFullB will still be asserted (low) on the 51'st byte transferred. This is to accomodate the propagation delay of TCA going inactive (low) at the end of a cell transfer and then being sampled by the PAL (TCA must be sampled as it can go active at any time). This will incur an extra clock delay per cell transfer. The TxClavB signal goes inactive (high) for a minimum of two cycles per cell trasfer. There will be a 3 clock cycle delay per cell transfer as the TxFullB and the TxClavB overlap.

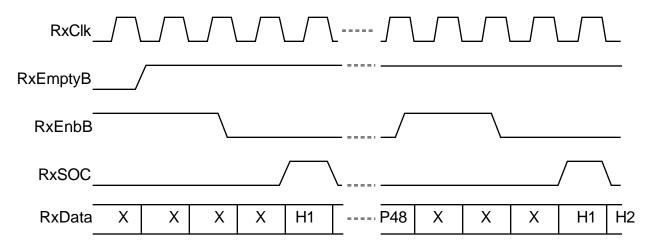

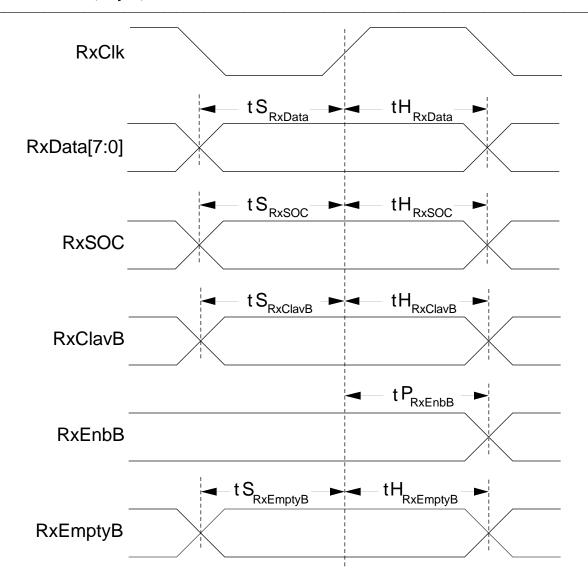

The Receive drop side interface is controlled by the ATM layer through the edge connector. All the receive signals from the ATM layer change with respect to the RxClk. All the input signals to the ATM layer are sampled on the rising edge of the RxClk. The receive side incorporates a external FIFO so that the SUNI device does not overrun due to the latency times between burst cell reads of the ATM layer (Vicksburg mother board).

The SUNI device asserts the RCA signal when it has a complete cell to transfer to the FIFO. The RCA signal goes to the Receive PAL (U16) and the PAL asserts the write enables to the receive FIFO. If the receive FIFO is not full (/FF high), the receive PAL will start clocking the data from the SUNI into the FIFO by generating the RRDB clock signal. The RSOC signal from the SUNI is inserted into bit 9 of the FIFO data inputs. The FIFO enables the /FF (active low FIFO Full) signal when it is full which disables further transfer of data from the SUNI to the FIFO. If the FIFO gets full, the SUNI will have transferred an indeterminate portion of a cell. The rest of the cell will get transferred as soon as the FIFO de-activates the /FF signal. The Receive PAL uses the RxCLK signal from the ATM layer to generate the WClk signal going to the FIFO and the RRDB clock signal to the SUNI. The WEN going to the FIFO is disabled while the /FF is active (low). While the FIFO write enable is disabled, the clock going to the FIFO is the same as the RxCLK. This is done because the FIFO /FF signal will not be disabled (high) untill it gets a rising edge on the WCLK input.

The RxEmptyB signal comes from the Receive FIFO /EF (active low Empty FIFO) signal. The Receive FIFO de-asserts the the RxEmptyB signal (high) upon reception of a single byte of data. On the next rising edge of the RxClk clock signal, the ATM layer samples the RxEmptyB signal and on the following RxClk clock signal, the ATM layer activates the RxEnbB signal (low) if it has an empty cell available. The

SAPI DAUGHTERBOARD

RxEnbB signal from the ATM layer goes to the Receive PAL (U16) and to the read enable (/RDEN1) input of the receive FIFO. On the next rising edge of the RxCLK signal after the RxEnbB signal goes active (low) the first byte of data is clocked out of the FIFO along with the RSOC signal. The receive ATM layer ignores the data until it sees a valid RSOC signal. Once cell transfer has commenced, the ATM layer expects a complete cell transfer. If the FIFO is empty (RxEmptyB is active) and then the SUNI starts to transfer data to the FIFO, there might only be one byte in the FIFO before the RxEmptyB signal could go inactive (high). For the FIFO to become empty, the SUNI must not have had any cells to transfer and therefore the first byte in the FIFO would be the first byte of the Cell along with the valid RSOC signal. Since the RxClk clock signal is generating the write and read clock signals to the FIFO as well as the read clock signal to the SUNI, the ATM layer cannot read the data out of the FIFO faster than the SUNI can write the data into the FIFO.

### SAPI Board Edge Connector Interface

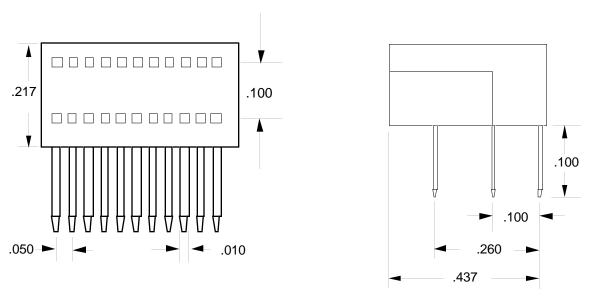

The SAPI UTOPIA Edge Connector Interface includes all the signals required to connect the SAPI board to a high layer protocol entity (i.e. a AAL processor). Cells can be written to the SUNI transmit FIFO and read from the SUNI receive FIFO using this interface. The edge connector is made up of a 100 pin dual line female connector is shown in table below. It consists of signals appropriate to read and write to the registers of the devices on the daughter board, and it provides the necessary power and ground. TTL signal levels are used on this interface.

| Signal<br>Name                                                          | Туре  | PIN                               | Function                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|-------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                                                     | Power | 1                                 | Ground                                                                                                                                                                                                     |

| GND                                                                     | Power | 2                                 | Ground                                                                                                                                                                                                     |

| TxDat[0] TxDat[1] TxDat[2] TxDat[3] TxDat[4] TxDat[5] TxDat[6] TxDat[7] |       | 3<br>5<br>9<br>11<br>4<br>6<br>10 | The SUNI is configured for the 8 bit FIFO interface, TxDat[7:0] corresponds to a cell byte.  TxDat[7] corresponds to bit 1, the first bit received.  TxDat[0] corresponds to bit 8, the last bit received. |

| VCC                                                                     | Power | 7                                 | +5 Volts                                                                                                                                                                                                   |

| vcc                                                                     | Power | 8                                 | +5 Volts                                                                                                                                                                                                   |

| GND                                                                     | Power | 13                                | Ground                                                                                                                                                                                                     |

| TxPrty                                                                  | l     | 14                                | Transmit data bus (TxDat[7:0]) odd parity. Not Used                                                                                                                                                        |

| TxSOC   | I     | 15 | Transmit start of cell indication. Identifies the first byte (word) of a cell on inputs TxDAT[7:0]                                                                                                                                             |

|---------|-------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND     | Power | 16 | Ground                                                                                                                                                                                                                                         |

| GND     | Power | 17 | Ground                                                                                                                                                                                                                                         |

| TxFullB | 0     | 18 | Active low signal from the PHY to ATM layer, asserted by the PHY layer 4 cycles before it is no longer able to accept transmit data.                                                                                                           |

| TxClavB | _     | 19 | Active low signal from the ATM layer to the PHY layer, asserted by the ATM layer when it has a full cell to transmit.                                                                                                                          |

| GND     | Power | 20 | Ground                                                                                                                                                                                                                                         |

| GND     | Power | 21 | Ground                                                                                                                                                                                                                                         |

| TxCLK   | I     | 22 | The transmit transfer/synchronization clock provided by the ATM to the PHY layer for synchronizing transfers on the TxDATA bus. (nominally at 20 MHz).                                                                                         |

| TxRefB  | ı     | 23 | Transmit Reference. Input for the purposes of synchronization (e.g. 8 KHz frame marker or SONET frame indicator). Not Used                                                                                                                     |

| GND     | Power | 24 | Ground                                                                                                                                                                                                                                         |

| GND     | Power | 25 | Ground                                                                                                                                                                                                                                         |

| TxXon   | 0     | 26 | PHY layer flow control. 1= Xon, 0= Xoff. Asserted by the PHY layer for normal transmission.  Deasserted by the PHY layer when the ATM link is experiencing congestion. The response of the ATM layer to this signal is user defined. Not Used. |

| TxEnbB  |       | 27 | Active low transmit signal asserted by the ATM layer during cycles when the TxDat contains valid cell data.                                                                                                                                    |

| GND     | Power | 28 | Ground                                                                                                                                                                                                                                         |

| GND     | Power | 29 | Ground                                                                                                                                                                                                                                         |

| RxDat[0]<br>RxDat[1]<br>RxDat[2]<br>RxDat[3]<br>RxDat[4]<br>RxDat[5]<br>RxDat[6]<br>RxDat[7] | 00000000 | 31<br>33<br>37<br>39<br>30<br>32<br>38<br>40 | RxDat[7:0] corresponds to a cell byte. Please refer to the SUNI datasheet for the byte cell data structure.  RxDat[7] corresponds to bit 1, the first bit received.  RxDat[0] corresponds to bit 8, the last bit received. |

|----------------------------------------------------------------------------------------------|----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxPrty                                                                                       | 0        | 34                                           | Receive data bus (RxDat[7:0]) odd parity. Not Used                                                                                                                                                                         |

| VCC                                                                                          | Power    | 35                                           | +5 Volts                                                                                                                                                                                                                   |

| VCC                                                                                          | Power    | 36                                           | +5 Volts                                                                                                                                                                                                                   |

| GND                                                                                          | Power    | 41                                           | Ground                                                                                                                                                                                                                     |

| Undefined                                                                                    |          | 42                                           |                                                                                                                                                                                                                            |

| RxSOC                                                                                        | 0        | 43                                           | Receive start of cell indication. Identifies the first byte (word) of a cell on outputs RxDat[7:0]                                                                                                                         |

| GND                                                                                          | Power    | 44                                           | Ground                                                                                                                                                                                                                     |

| GND                                                                                          | Power    | 45                                           | Ground                                                                                                                                                                                                                     |

| RxEmptyB                                                                                     | 0        | 46                                           | Active low empty signal to indicate that in the current cycle there is no valid data for delivery to the ATM layer.                                                                                                        |

| RxEnbB                                                                                       | I        | 47                                           | Active low signal asserted by the ATM layer to indicate that the RxDat[7:0] will be sampled at the start of the next cycle. Sampling occurs on cycles following those with RxENB asserted and RxEmptyB Deasserted.         |

| GND                                                                                          | Power    | 48                                           | Ground                                                                                                                                                                                                                     |

| GND                                                                                          | Power    | 49                                           | Ground                                                                                                                                                                                                                     |

| RxClk                                                                                        | I        | 50                                           | Transfer/synchronization clock provide by the ATM layer for synchronizing transfers on RxDat (nominally 20 MHz).                                                                                                           |

| RxRefB                                                                                       | 0        | 51                                           | Receive Reference. Output for the purposes of synchronization (e.g. 8 KHz frame marker or SONET frame indicator). Not Used.                                                                                                |

| GND                                                                                          | Power    | 52                                           | Ground                                                                                                                                                                                                                     |

| GND                                                                                          | Power    | 53                                           | Ground                                                                                                                                                                                                                     |

| RxClav    | 0     | 54 | Receive Cell Available Signal. Active high signal from the PHY layer to the ATM layer, asserted to indicate that there is a complete cell available for transfer to the ATM layer. |

|-----------|-------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxFlush   |       | 55 | Not Used                                                                                                                                                                           |

| GND       | Power | 56 | Ground                                                                                                                                                                             |

| GND       | Power | 57 | Ground                                                                                                                                                                             |

| A[4]      | I     | 58 | Address bus bit 7.                                                                                                                                                                 |

| A[0]      | I     | 59 | Address bus bit 6.                                                                                                                                                                 |

| A[5]      | I     | 60 | Address bus bit 5.                                                                                                                                                                 |

| A[1]      | I     | 61 | Address bus bit 4.                                                                                                                                                                 |

| Undefined |       | 62 |                                                                                                                                                                                    |

| VCC       | Power | 63 | +5 Volts                                                                                                                                                                           |

| VCC       | Power | 64 | +5 Volts                                                                                                                                                                           |

| A[2]      | I     | 65 | Address bus bit 3.                                                                                                                                                                 |

| A[6]      | I     | 66 | Address bus bit 2.                                                                                                                                                                 |

| A[3]      | I     | 67 | Address bus bit 1.                                                                                                                                                                 |

| A[7]      | I     | 68 | Address bus bit 0.                                                                                                                                                                 |

| GND       | Power | 69 | Ground                                                                                                                                                                             |

| GND       | Power | 70 | Ground                                                                                                                                                                             |

| D[0]      | I/O   | 71 | Data bus bit 0.                                                                                                                                                                    |

| A[8]      | I     | 72 | Address bit used to read the Standard PHY registers.                                                                                                                               |

| D[1]      | I/O   | 73 | Data bus bit 1.                                                                                                                                                                    |

| D[4]      | I/O   | 74 | Data bus bit 4.                                                                                                                                                                    |

| GND       | Power | 75 | Ground                                                                                                                                                                             |

| GND       | Power | 76 | Ground                                                                                                                                                                             |

| D[2]      | I/O   | 77 | Data bus bit 2.                                                                                                                                                                    |

| D[5]      | I/O   | 78 | Data bus bit 5.                                                                                                                                                                    |

| D[3]      | I/O   | 79 | Data bus bit 3.                                                                                                                                                                    |

| D[6]      | I/O   | 80 | Data bus bit 6.                                                                                                                                                                    |

# STANDARD PRODUCT

### PMC-940106 ISSUE 3, May 16, 1994

| GND       | Power | 81  | Ground                                                                                          |

|-----------|-------|-----|-------------------------------------------------------------------------------------------------|

| GND       | Power | 82  | Ground                                                                                          |

| Prty      | I/O   | 83  | Data bus D[7:0] odd parity. Not Used.                                                           |

| D[7]      | I/O   | 84  | Data bus bit 7.                                                                                 |

| VCC       | Power | 85  | +5 Volts                                                                                        |

| VCC       | Power | 86  | +5 Volts                                                                                        |

| Undefined |       | 87  |                                                                                                 |

| INTB      | 0     | 88  | Active low, open-drain interrupt signal.                                                        |

| CSB       | I     | 89  | The SUNI active low chip select signal.                                                         |

| GND       | Power | 90  | Ground                                                                                          |

| GND       | Power | 91  | Ground                                                                                          |

| RSTB      | I     | 92  | Active low H/W reset.                                                                           |

| RDB       | I     | 93  | Active low read signal asserted to enable data from the addressed location onto the D[7:0] bus. |

| GND       | Power | 94  | Ground                                                                                          |

| GND       | Power | 95  | Ground                                                                                          |

| RDY       |       | 96  | Not Used                                                                                        |

| WRB       | I     | 97  | Active low write signal asserted to write data to the addressed location from the D[7:0] bus.   |

| ALE       | I     | 98  | Address latch enable. When high, identifies that address is valid on D[7:0]. Not Used.          |

| GND       | Power | 99  | Ground                                                                                          |

| GND       | Power | 100 | Ground                                                                                          |

SAPI DAUGHTERBOARD

### SUNI REGISTER ADDRESS MAP

The microprocessor interface provides access to the SUNI device registers via the 100 pin UTOPIA connector. The SUNI address space extends from 00H to FFH. Address bit 8 (A8 being the most significant bit and A0 being the least significant bit) is set low to access the SUNI register space. Below is a list of the SUNI device registers. For further details, please refer to the "Saturn User Network Interface Device Datasheet".

| Address   | Register                       |

|-----------|--------------------------------|

| 0x00      | SUNI Master Reset and Identity |

| 0x01      | SUNI Master Configuration      |

| 0x02      | SUNI Master Interrupt Status   |

| 0x04      | SUNI Master Clock Monitor      |

| 0x05      | SUNI Master Control            |

| 0x06-0x07 | Reserved                       |

| 0x08-0x0B | Reserved                       |

| 0x0C-0x0F | Reserved                       |

| 0x10      | RSOP Control/Interrupt Enable  |

| 0x11      | RSOP Status/Interrupt Status   |

| 0x12      | RSOP Section BIP-8 LSB         |

| 0x13      | RSOP Section BIP-8 MSB         |

| 0x14      | TSOP Control                   |

| 0x15      | TSOP Diagnostic                |

| 0x16-0x17 | TSOP Reserved                  |

| 0x18      | RLOP Control/Status            |

| 0x19      | RLOP Interrupt Enable/Status   |

| 0x1A      | RLOP Line BIP-24 LSB           |

| 0x1B      | RLOP Line BIP-24               |

| 0x1C      | RLOP Line BIP-24 MSB           |

| 0x1D      | RLOP Line FEBE LSB             |

| 0x1E      | RLOP Line FEBE                 |

| 0x1F      | RLOP Line FEBE MSB             |

| 0x20      | TLOP Control                   |

| 0x21      | TLOP Diagnostic                |

| 0x22-0x23 | TLOP Reserved                  |

| 0x24-0x27 | Reserved                       |

| 0x28-0x2B | Reserved                       |

| 0x2C-0x2F | Reserved                       |

| 0x30      | RPOP Status/Control            |

| 0x31      | RPOP Interrupt Status          |

| 0x32      | RPOP Reserved                  |

| 0x33      | RPOP Interrupt Enable          |

| 0x35 RPOP Reserved 0x36 RPOP Reserved 0x37 RPOP Path Signal Label 0x38 RPOP Path BIP-8 LSB / Load Meters 0x39 RPOP Path BIP-8 MSB 0x3A RPOP Path FEBE LSB 0x3BH RPOP Path FEBE MSB 0x3C-0x3F RPOP Reserved 0x40 TPOP Control/Diagnostic 0x41 TPOP Pointer Control 0x42 TPOP Source Control 0x43 TPOP Reserved 0x44 TPOP Reserved 0x44 TPOP Reserved 0x45 TPOP Arbitrary Pointer LSB 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Arbitrary Pointer MSB 0x47 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4A TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x63-0x67 Reserved 0x80 SUNI Master Test 0x81-0xFF Reserved for Test | 0x34      | RPOP Reserved                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------|

| 0x36RPOP Reserved0x37RPOP Path Signal Label0x38RPOP Path BIP-8 LSB / Load Meters0x39RPOP Path BIP-8 MSB0x3ARPOP Path FEBE LSB0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x44TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x60SUNI Master Test                                             |           |                                                 |

| 0x37RPOP Path Signal Label0x38RPOP Path BIP-8 LSB / Load Meters0x39RPOP Path BIP-8 MSB0x3ARPOP Path FEBE LSB0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x44TPOP Arbitrary Pointer LSB0x45TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x60SUNI Master Test                                             |           |                                                 |

| 0x38RPOP Path BIP-8 LSB / Load Meters0x39RPOP Path BIP-8 MSB0x3ARPOP Path FEBE LSB0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x44TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Control/Status0x61TACP Control/Status0x62TACP Idle/Unassigned Cell Header Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x60SUNI Master Test                                                                            |           |                                                 |

| 0x39RPOP Path BIP-8 MSB0x3ARPOP Path FEBE LSB0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Control/Status0x62TACP Idle/Unassigned Cell Header Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                              |           |                                                 |

| 0x3ARPOP Path FEBE LSB0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Natch Header Mask0x56-0x5FRACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                |           |                                                 |

| 0x3BHRPOP Path FEBE MSB0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Colle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                        |           |                                                 |

| 0x3C-0x3FRPOP Reserved0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Reserved0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                                                                                           |           |                                                 |

| 0x40TPOP Control/Diagnostic0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x55RACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                                                      |           |                                                 |

| 0x41TPOP Pointer Control0x42TPOP Source Control0x43TPOP Reserved0x44TPOP Reserved0x45TPOP Arbitrary Pointer LSB0x46TPOP Arbitrary Pointer MSB0x47TPOP Reserved0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x56-0x5FRACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                                                                            | 0x3C-0x3F | RPOP Reserved                                   |

| 0x42 TPOP Source Control 0x43 TPOP Reserved 0x44 TPOP Reserved 0x45 TPOP Arbitrary Pointer LSB 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                 | 0x40      |                                                 |

| 0x44 TPOP Reserved 0x45 TPOP Arbitrary Pointer LSB 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                    | 0x41      | TPOP Pointer Control                            |

| 0x44 TPOP Reserved 0x45 TPOP Arbitrary Pointer LSB 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x68-0x7F Reserved 0x60 SUNI Master Test                                                                                                                                                                                                                                                                                                                 | 0x42      |                                                 |

| 0x45 TPOP Arbitrary Pointer LSB 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                           | 0x43      | TPOP Reserved                                   |

| 0x46 TPOP Arbitrary Pointer MSB 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                           | 0x44      | TPOP Reserved                                   |

| 0x47 TPOP Reserved 0x48 TPOP Path Signal Label 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                | 0x45      |                                                 |

| 0x48TPOP Path Signal Label0x49TPOP Path Status0x4ATPOP Reserved0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x56-0x5FRACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x80SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                           | 0x46      | TPOP Arbitrary Pointer MSB                      |

| 0x49 TPOP Path Status 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x47      | TPOP Reserved                                   |

| 0x4A TPOP Reserved 0x4B-0x4F TPOP Reserved 0x50 RACP Control/Status 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x48      | TPOP Path Signal Label                          |

| 0x4B-0x4FTPOP Reserved0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x56-0x5FRACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x49      | TPOP Path Status                                |

| 0x50RACP Control/Status0x51RACP Interrupt Enable/Status0x52RACP Match Header Pattern0x53RACP Match Header Mask0x54RACP Correctable HCS Error Count0x55RACP Uncorrectable HCS Error Count0x56-0x5FRACP Reserved0x60TACP Control/Status0x61TACP Idle/Unassigned Cell Header Pattern0x62TACP Idle/Unassigned Cell Payload Octet Pattern0x63-0x67TACP Reserved0x68-0x7FReserved0x80SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x4A      | TPOP Reserved                                   |

| 0x51 RACP Interrupt Enable/Status 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x4B-0x4F | TPOP Reserved                                   |

| 0x52 RACP Match Header Pattern 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x50      | RACP Control/Status                             |

| 0x53 RACP Match Header Mask 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x51      | RACP Interrupt Enable/Status                    |

| 0x54 RACP Correctable HCS Error Count 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x52      | RACP Match Header Pattern                       |

| 0x55 RACP Uncorrectable HCS Error Count 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x53      | RACP Match Header Mask                          |

| 0x56-0x5F RACP Reserved 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x54      | RACP Correctable HCS Error Count                |

| 0x60 TACP Control/Status 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x55      | RACP Uncorrectable HCS Error Count              |

| 0x61 TACP Idle/Unassigned Cell Header Pattern 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x56-0x5F | RACP Reserved                                   |

| 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x60      | TACP Control/Status                             |

| 0x62 TACP Idle/Unassigned Cell Payload Octet Pattern 0x63-0x67 TACP Reserved 0x68-0x7F Reserved 0x80 SUNI Master Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x61      | TACP Idle/Unassigned Cell Header Pattern        |