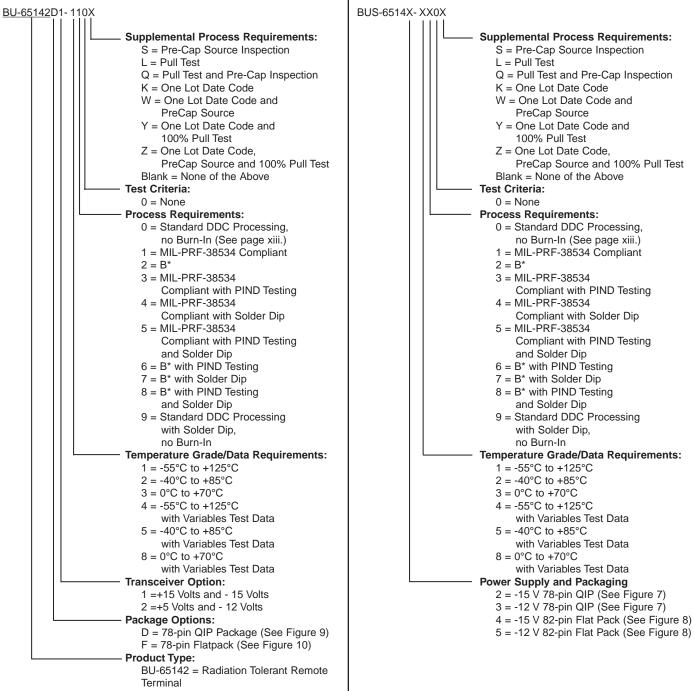

# MIL-STD-1553 DUAL REDUNDANT REMOTE TERMINAL HYBRID

# DESCRIPTION

The BUS-65142 Series is a complete dual redundant MIL-STD-1553 Remote Terminal Unit (RTU) packaged in a small 1.9" x 2.1" hybrid. The device is based upon two DDC custom ICs, which includes two monolithic bi-polar low power transceivers and one CMOS protocol containing data buffers and timing control logic. It supports all 13 mode codes for dual redundant operation, any combinaion of which can be illegalized.

Parallel data transfers are accomplished with a DMA type handshaking, compatible with most CPU types. Data transfers to/from memory are simplified by the latched command word and word count outputs. Error detection and recovery are enhanced by BUS-65142 Series special features. A 14-bit built-intest word register stores RTU information, and sends it to the Bus Controller in response to the Mode Command Transmit Bit Word. The BUS-65142 Series performs continuous on-line wraparound self-test, and provides four error flags to the host CPU. Inputs are provided for host CPU control of 6 bits of the RTU Status Word.

Its small hermetic package, -55°C to +125°C operating temperature range, and complete RTU operation make the BUS-65142 ideal for most MIL-STD-1553 applications requiring hardware or microprocessor subsystems.

# **FEATURES**

- Complete Intergrated Remote Terminal Including: -Dual Low-Power Transceivers -Complete RT Protocol

- Direct Interface to Systems With No Processor

- Radiation Tolerant Version

Available

- Space Qualified Version Available

- High Reliability Screening

Available

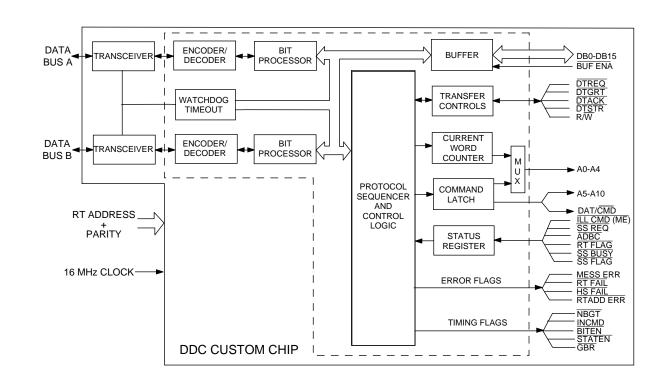

FIGURE 1. BUS-65142 SERIES BLOCK DIAGRAM

| TABLE 1. BU-65142 and BUS-6514                                                                                                                                                                                                              | 42/44 SI | PECIFIC | ATIONS            | ;              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-------------------|----------------|

| PARAMETER                                                                                                                                                                                                                                   | MIN      | TYP     | MAX               | UNITS          |

| RECEIVER<br>Differential Input Impedance                                                                                                                                                                                                    | 4.0      |         |                   | kohm           |

| (DC to 1 MHz)<br>Differential Input Voltage                                                                                                                                                                                                 |          |         | 40                | Vp-р           |

| Input Threshold Level<br>(Direct Coupled)                                                                                                                                                                                                   | 0.70     |         | 1.20              | Vp-p           |

| CMRR (DC to 2 MHz)                                                                                                                                                                                                                          | 40       |         |                   | dB             |

| CMV (DC to 2 MHz)                                                                                                                                                                                                                           | ±10      |         |                   | V              |

| TRANSMITTER<br>Differential Output Voltage                                                                                                                                                                                                  |          |         |                   |                |

| Direct Coupled Across 35 Ω,                                                                                                                                                                                                                 | 6        | 7       | 9                 | Vp-р           |

| Measured on Bus<br>Transformer Coupled Across 70 Ω,<br>Measured on Stub:                                                                                                                                                                    | 18       | 21      | 27                | Vp-р           |

| Output Noise, Differential (Direct<br>Coupled)                                                                                                                                                                                              |          |         | 10                | mVp-p,<br>diff |

| Output Offset Voltage, (Transformer<br>Coupled Across 70 ohms)                                                                                                                                                                              | -250     |         | +250              | mVp-p,<br>diff |

| Rise/Fall Time                                                                                                                                                                                                                              | 100      | 150     | 300               | nsec           |

| LOGIC                                                                                                                                                                                                                                       |          |         |                   |                |

| ViH                                                                                                                                                                                                                                         | 2.4      |         |                   | V              |

| VIL                                                                                                                                                                                                                                         |          |         | 0.7               | V              |

| IIH ( <sup>V</sup> IH=2.7V)<br>■ BRO ENA,                                                                                                                                                                                                   | 0.04     |         | 0.2               | mA             |

| ADDRE-ADDRA(RTAD4-RTAD0),<br>ADDRP (connect to 30kΩ pull-up )                                                                                                                                                                               |          |         |                   |                |

| ■ ( <sup>V</sup> IH=2.7V) DB15 - DB0                                                                                                                                                                                                        | 0.04     |         | 0.2               | mA             |

| (connect to a 45kΩ pull-up )<br>■ (VIH≥2.4V) All Other Inputs                                                                                                                                                                               |          |         | ±20               | μA             |

| I <sub>IL</sub> ( <sup>V</sup> IL=0.4V)<br>■ BRO ENA,<br>ADDRE-ADDRA(RTAD4-RTAD0),<br>ADDRP (connect to 30kΩ pull-up)<br>■ ( <sup>V</sup> IL=0.4V) DB15 - DB0<br>(connect to a 45kΩ pull-up)<br>■ ( <sup>V</sup> IL=≥0.7V) All Other Inputs |          |         | 0.4<br>0.4<br>±20 | mA<br>mA<br>μA |

|                                                                                                                                                                                                                                             |          |         |                   |                |

| VOH<br>■( <sup>I</sup> OH=-0.4mA)<br>A9-A5(SA4-SA0), RTADERR,<br>HSFAIL, DAT/CMD, RTFAIL, BITEN,<br>NBGT, GBR, ME, STATEN                                                                                                                   | 2.4      |         |                   | V              |

| V <sub>OH</sub><br>■ ( <sup>I</sup> OH=-0.4mA) All Other Inputs                                                                                                                                                                             | 2.4      |         |                   | V              |

| <sup>V</sup> OH<br>■ ( <sup>I</sup> OH=-0.4mA) DB15 - DB0<br>(connect to a 45kΩ pull-up )                                                                                                                                                   | 2.4      |         |                   | V              |

| VOL<br>■( <sup>I</sup> OH=-2mA)<br>A9-A5(SA4-SA0), RTADERR,<br>HSFAIL, DAT/CMD, RTFAIL, BITEN,<br>NBGT, GBR, ME, STATEN                                                                                                                     |          |         | 0.4               | V              |

| V <sub>OH</sub><br>■ <sup>(I</sup> OL=2 mA) All Other Inputs                                                                                                                                                                                |          |         | 0.4               | V              |

| TABLE 1. BU-65142 and BUS-65142/44 SPECIFICATIONS (continued)                       |        |                |                |          |  |  |

|-------------------------------------------------------------------------------------|--------|----------------|----------------|----------|--|--|

| PARAMETER                                                                           | MIN    | TYP            | MAX            | UNITS    |  |  |

| LOGIC (continued)<br>VOH                                                            |        |                |                |          |  |  |

| ■ ( <sup>I</sup> OH=-2mA) DB15 - DB0<br>(connect to a 45kΩ pull-up )                |        |                | 0.4            | V        |  |  |

| $C_1$ (f = 1 MHz)                                                                   |        |                | 50             | pF       |  |  |

| $C_0$ (f = 1 MHz)                                                                   |        | 10             |                | pF       |  |  |

| $C_{10}$ ((f = 1 MHz)                                                               |        |                | 50             | pF       |  |  |

| <ul> <li>DB15 - DB0<br/>(connect to a 45kΩ pull-up )</li> </ul>                     |        |                |                |          |  |  |

| POWER SUPPLY REQUIREMENTS<br>+5V (BU-65142X1/2,<br>BUS-65142/43/44/45)              | 4.5    |                | 5.5            | V        |  |  |

| Current Drain                                                                       |        | 50             | 115            | mA       |  |  |

| -15V (BU-65142X1, BUS-65142/44)<br>Current Drain                                    | -15.75 |                | -14.25         | V        |  |  |

| <ul> <li>Idle</li> <li>25% Transmitter Duty Cycle</li> </ul>                        |        | 30<br>68       | 60<br>108      | mA<br>mA |  |  |

| 50% Transmitter Duty Cycle                                                          |        | 105            | 160            | mA       |  |  |

| <ul> <li>100% Transmitter Duty Cycle</li> </ul>                                     |        | 180            | 255            | mA       |  |  |

| -12V (BU-65142X2, BUS-65143/45)<br>Current Drain                                    | -12.6  |                | -11.4          | V        |  |  |

| • Idle                                                                              |        | 30             | 60             | mA       |  |  |

| <ul> <li>25% Transmitter Duty Cycle</li> <li>50% Transmitter Duty Cycle</li> </ul>  |        | 80<br>130      | 120<br>185     | mA<br>mA |  |  |

| 100% Transmitter Duty Cycle                                                         |        | 230            | 305            | mA       |  |  |

| POWER DISSIPATION (See Note)                                                        |        |                |                |          |  |  |

| Total Hybrid<br>■ BU-65142X1/BUS-65142/44                                           |        |                |                |          |  |  |

| • Idle                                                                              |        | 0.700          | 1.475          | W        |  |  |

| 25% Transmitter Duty Cycle                                                          |        | 0.912          |                | W        |  |  |

| <ul> <li>50% Transmitter Duty Cycle</li> <li>100% Transmitter Duty Cycle</li> </ul> |        | 1.125          | 2.238<br>3.000 | W<br>W   |  |  |

| ■ BU-65142X2/BUS-65143/45                                                           |        | 1.550          | 0.000          | ~~       |  |  |

| • Idle                                                                              |        | 0.610          |                | W        |  |  |

| <ul> <li>25% Transmitter Duty Cycle</li> <li>50% Transmitter Duty Cycle</li> </ul>  |        | 0.860          | 1.680<br>2.065 | W<br>W   |  |  |

| 100% Transmitter Duty Cycle                                                         |        | 1.160          | 2.895          | Ŵ        |  |  |

| Hottest Die<br>■ BU-65142X1/BUS-65142/44                                            |        |                |                |          |  |  |

| • Idle                                                                              |        | 0.335          | 0.680          | W        |  |  |

| <ul> <li>25% Transmitter Duty Cycle</li> <li>50% Transmitter Duty Cycle</li> </ul>  |        | 0.550<br>0.760 | 1.010<br>1.350 | W<br>W   |  |  |

| 100% Transmitter Duty Cycle                                                         |        | 1.185          | 2.030          | Ŵ        |  |  |

| <ul> <li>BU-65142X2/BUS-65143/45</li> <li>Idle</li> </ul>                           |        | 0.290          | 0.590          | W        |  |  |

| <ul> <li>25% Transmitter Duty Cycle</li> </ul>                                      |        | 0.540          | 0.870          | W        |  |  |

| <ul> <li>50% Transmitter Duty Cycle</li> <li>100% Transmitter Duty Cycle</li> </ul> |        | 0.790<br>1.290 | 1.260<br>1.960 | W<br>W   |  |  |

|                                                                                     |        | 1.290          | 1.900          | ٧V       |  |  |

| TABLE 1. BU-65142 and BUS-65142/44 SPECIFICATIONS (continued)                                                                             |                                            |                    |                    |            |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|--------------------|------------|--|--|

| <ul> <li>THERMAL</li> <li>Thermal Resistance, Junction-to-<br/>Case, Hottest Die (θJC)</li> <li>Operating Junction Temperature</li> </ul> | -55                                        |                    | 20<br>150          | °C/W<br>°C |  |  |

| <ul> <li>Storage Temperature</li> <li>Lead Temperature<br/>(soldering, 10 sec.)</li> </ul>                                                | -65                                        |                    | 150<br>150<br>+300 | ပံ ပံ      |  |  |

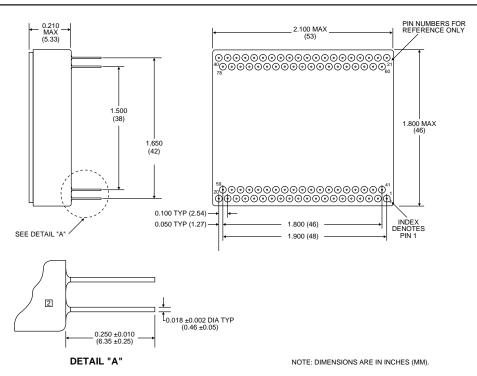

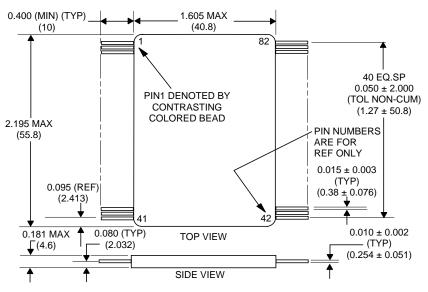

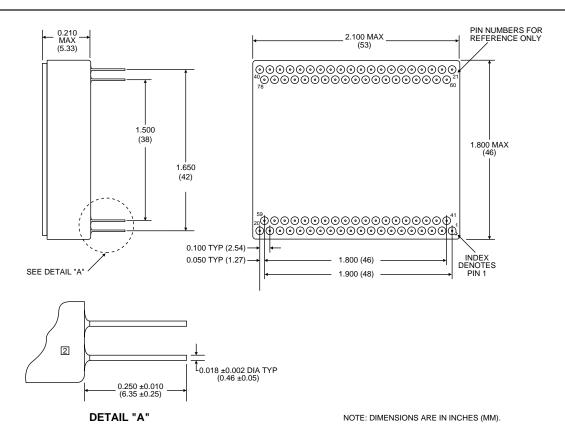

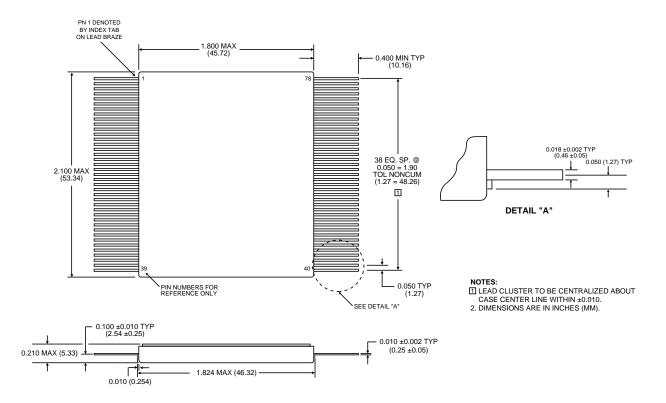

| PHYSICAL CHARACTERISTICS                                                                                                                  |                                            |                    |                    |            |  |  |

| Size<br>78-pin Kovar (BUS-65142/43)                                                                                                       |                                            | x 53.3             |                    | in<br>(mm) |  |  |

| 82-pin Kovar Flat Pack<br>(BUS-65142/43)                                                                                                  | 1.61 x 2.20 x 0.181<br>(40.8 x 55.8 x 4.6) |                    |                    | in<br>(mm) |  |  |

| 78-pin Ceramic QIP (BU-65142D)                                                                                                            | 1.80 x 2.10 x 0.21<br>(45.7 x 53.3 x 5.3)  |                    |                    | in<br>(mm) |  |  |

| 78-pin Ceramic Flat Pack<br>(BU-65142F)                                                                                                   |                                            | x 2.10 x<br>x 53.3 |                    | in<br>(mm) |  |  |

| Weight                                                                                                                                    |                                            | 1.7<br>(4.1)       |                    | oz<br>(g)  |  |  |

#### Note:

Power dissipation specifications assume a transformer coupled configuration, with external disipation (while transmitting) of 0.14 watts for the active isolation transformer, 0.8 watts for the active coupling transformer, 0.45 watts for each of the two bus isolation resistors, and 0.15 watts for each of the two bus termination resistors.

| TABLE 2. BU-65142 SERIES RADIATION SPECIFICATIONS |                                                                                             |                                                                                                  |        |  |  |

|---------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|--|--|

| PART<br>NUMBER                                    | TOTAL         SINGLE EVENT         SINGLE EVEN           DOSE         UPSET         LATCHUP |                                                                                                  |        |  |  |

| BU-65142<br>X1/X2                                 | 300K<br>Rad                                                                                 | 5.3 x 10 <sup>-6</sup><br>errors/device-day,<br>(LET Threshold of<br>59 MeV/mg/cm <sup>2</sup> ) | Immune |  |  |

### **INTRODUCTION**

The BUS-65142 is a complete dual redundant Remote Terminal Unit (RTU) packaged in a small 1.9 x 2.1 hybrid. It is fully compliant with MIL-STD=1553B and supports all message formats. As shown in FIGURE 1, it includes 2 transceivers and a custom chip containing 2 encoders, 2 bit processors, an RTU protocol sequencer and control logic, output latches, and buffers. With the addition of 2 data bus transformers, the BUS-65142 is ready for connection to a MIL-STD-1553 data bus.

Data is transferred to and from the subsystem host CPU over a 16-bit parallel highway, which is isolated by a set of bi-directional buffers. All transfers are made with a DMA type handshake sequence of request, grant and acknowledge. Read/write and data strobes are provided to simplify interfacing to external RAM. Also simplifying the RAM interface is the availability of latched command word and auto-incrementing word counter. These signals may be used as an address to map the data directly to and from RAM.

The BUS-65142 allows the subsystem host CPU to control 6 of the bits in the RTU status word. Of particular interest is the Illegal Command input which may be used to set the message error bit and illegalize any command word. The BUS-65142 provides four error flags to the subsystem host CPU for evaluating its condition. In addition a continuous on-line self-test is performed by the BUS-65142 on every transmission. The last Transmitted Word of every message is wrapped around the decoder and compared with the Actual Word. Any discrepancy is flagged as an error.

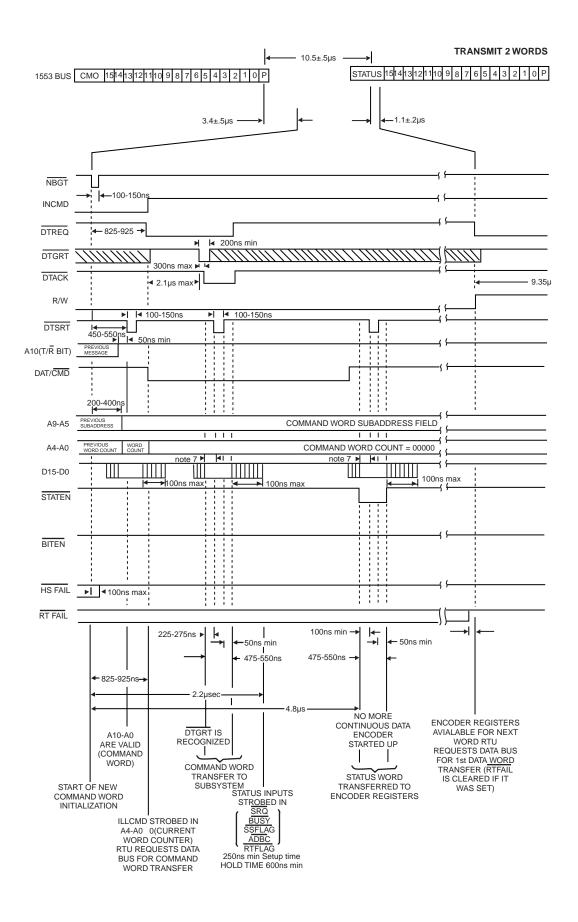

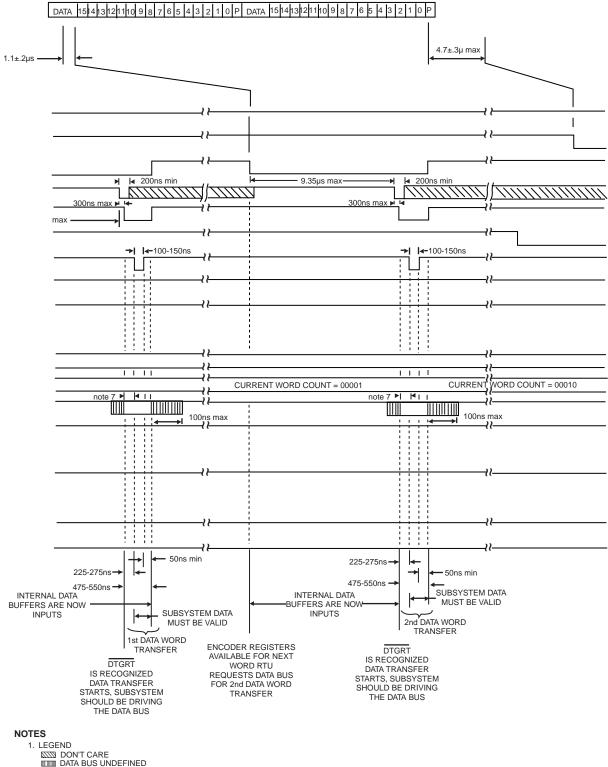

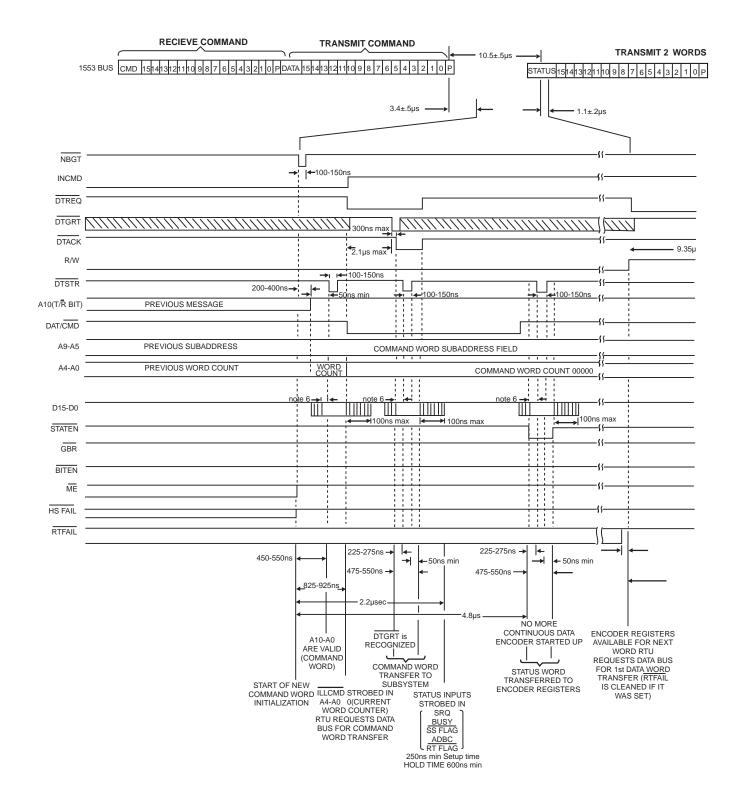

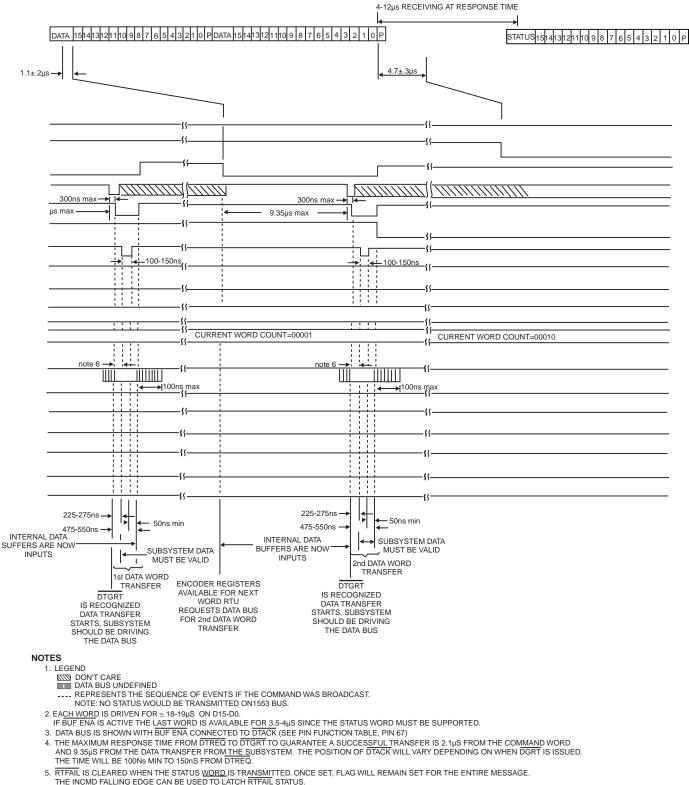

# TIMING

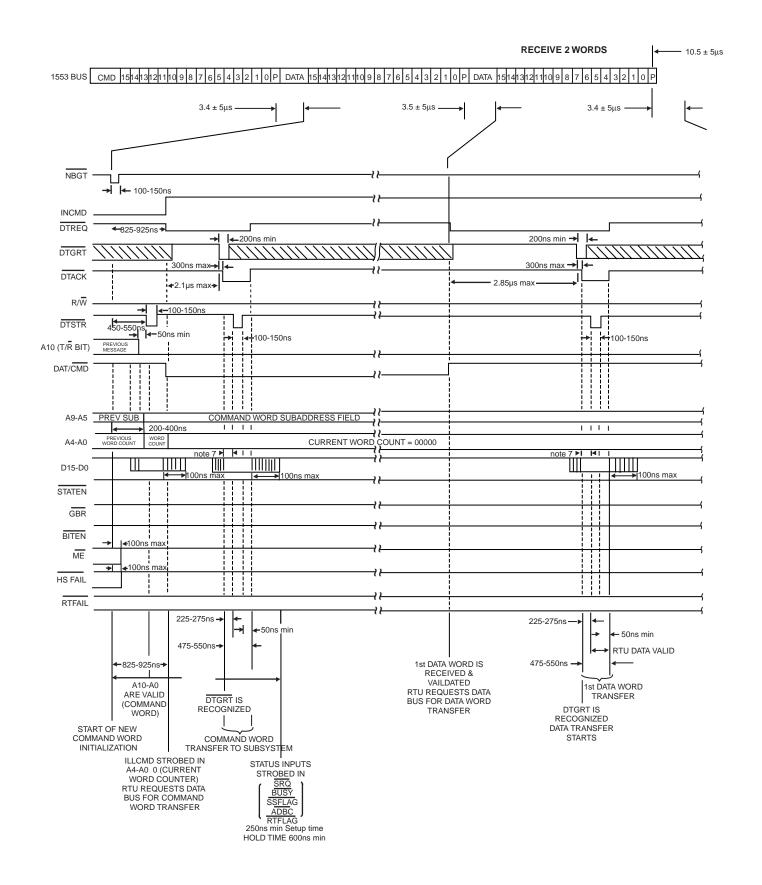

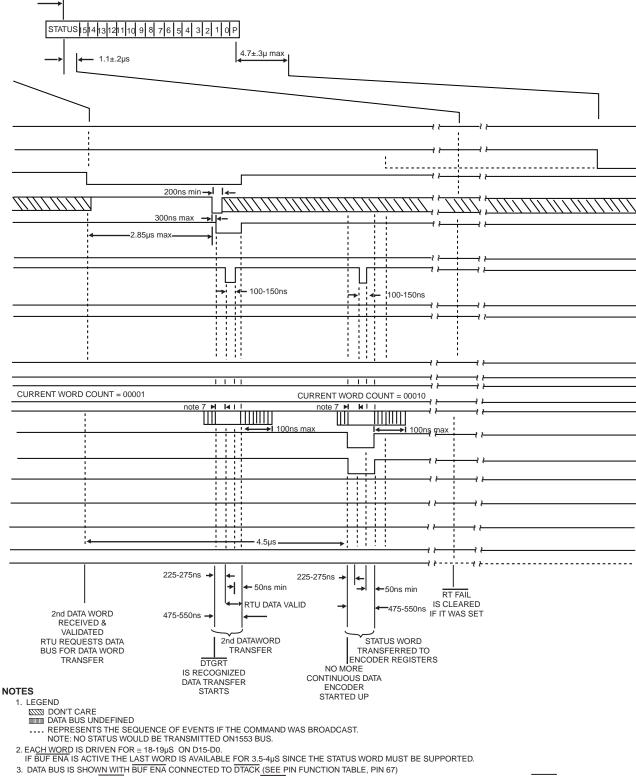

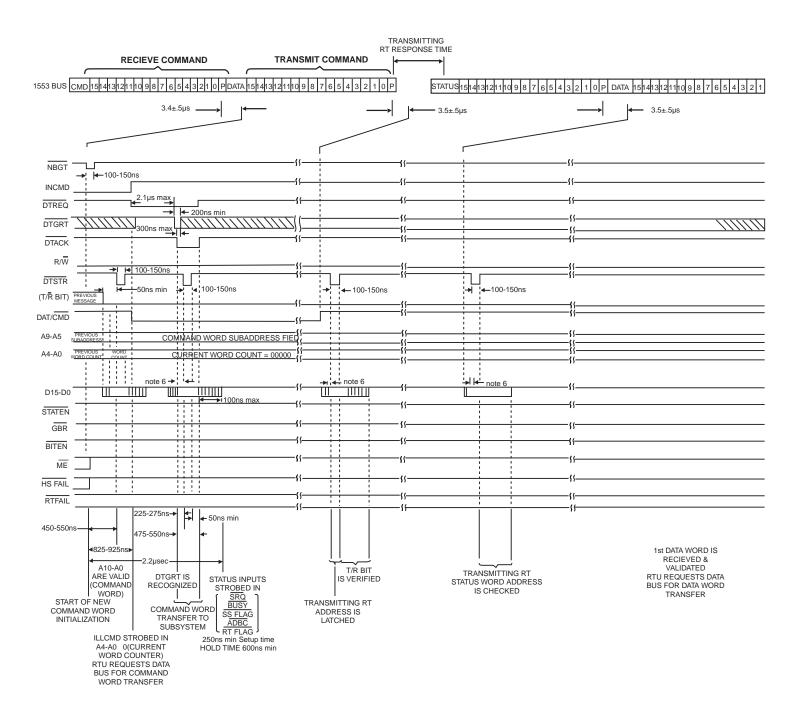

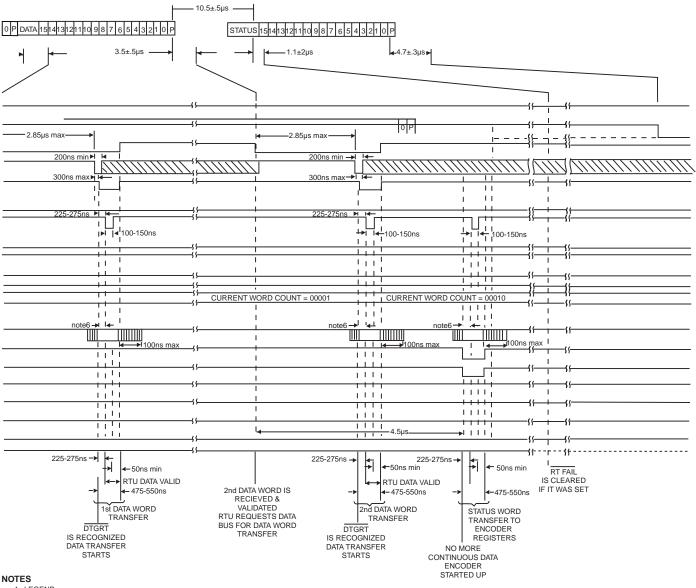

Interfacing the subsystem host CPU to the BUS-65142 is simple and compatible with most microprocessors. FIGURE 3 and 4 illustrate typical MIL-STD-1553 messages for Transmit data and Receive data. FIGURES 5 and 6 illustrate RT to RT transfers. In each case NBGT identifies the start of the message, and INCMD identifies that a command is being processed. The handshake sequence DTREQ, DTGRT, and DTACK is used to transfeer each word over the parallel data highway. DTSRB and RD/WR are used to control transfers to RAM memory. GBR identifies a "good block received", when a received message has passed all validation checks and has the correct word count. BUFENA (Buffer Enable) must be applied to enable the internal tri-state buffers.

# ERROR FLAGS

Four error flags are ouput to the subsystem to provide information on the condition of the BUS-65142.

The ME (Message Error) line goes LOW if any of the following error conditions exist: format error word count error invalid word sync error RT to RT address error T/R bit error.

The RTFAIL (Remote Terminal Failure) line goes LOW whenever the results of a continuous wraparound self-test shows a discrepancy, or a transmitter watchdog timeout has occurred.

The HSFAIL (Handshake Failure) line goes LOW whenever the system dows not issue a DTGRT in response to a DTREQ before timing-out.

The RTADR ERR (RT Address Error) line goes LOW whenever the sum of the 5 address lines and parity lines show a parity error (the terminal will not respond to commands while this error condition exists).

### **STATUS REGISTER**

Six inputs to the BUS-65142 allow the subsystem host CPU to control bits in the RTU status word. The Illegal Command input may be used to set the Message Error bit in the Status Word and suppress the transmission of data to the bus controller. This line allows illegalization of any combination of commands. The latched Command Word may be connected to the address pins of an optional external PROM, which would drive the Illegal Command line LOW when it identifies a command programmed as illegal.

# STATUS REGISTER BIT ASSIGNMENTS

The SRQ (Subsystem Request) line is used to set the Status Word service request bit.

The ADBC (Accept Dynamic Bus Control) line is used to set the Status Word bus control bit.

The RTFLAG (RT Flag Line) is used to set the Status Word terminal flag bit.

The BUSY (Busy) line is used to set the Status Word busy bit, and inhibit subsystem requests for data.

The SSFLAG (SubSystem Flag) line is used to set the Status Word subsytem (fault) flag.

# **BUILT-IN-TEST**

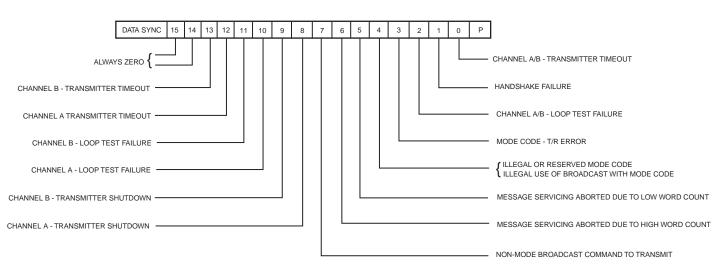

The BUS-65142 contains a 14-bit Built-In-Test (BIT) word register which stores information about the condition of the RTU. When a mode code is received to transmit the BIT word, the con-

tents of the BIT register is transmitted over the 1553 bus. FIGURE 2 shows the fault assigned to each bit in the BIT word. Conditions monitored are; transmitter timeouts, loop test failures, transmitter shutdown, subsystem handshake failure, and the results of individual message validations.

### NOTES

1. BITS 3-7 ARE CLEARED IN THE BEGINNING OF EACH NEW MESSAGE AND UPDATED AT THE END OF THE MESSAGE. THEY ONLY REFLECT THE PRESENT COMMAND WORD.

2. BITS 0-2 AND 10-13 ARE LATCHED AND ONLY CLEARED BY A MODE RESET COMMAND OR A MASTER RESET (RESET).

3. BITS 8 AND 9 ARE SET ONLY BY THE MODE COMMAND FOR "TRANSMITTER SHUTDOWN" AND ARE CLEARED BY THE MODE COMMAND FOR "OVERRIDE TRANSMITTER SHUTDOWN" OR "RESET REMOTE TERMINAL". BITS 8 AND 9 ARE ALSO CLEARED BY RESET.

FIGURE 2. BUILT-IN-TEST (BIT) WORD REGISTER

# FIGURE 3. TRANSMIT TIMING DIAGRAM

- 2. EACH WORD IS DRIVEN FOR ≅ 18-19µS ON D15-D05.

- IF BUF ENA IS ACTIVE THE LAST WORD IS AVAILABLE FOR 3.5-4µS SINCE THE STATUS WORD MUST BE SUPPORTED.

- 3. DATA BUS IS SHOWN WITH BUF ENA CONNECTED TO DTACK (SEE PIN FUNCTION TABLE, PIN 67)

- 4. THE POSITION OF DTACK WILL VARY DEPENDING ON WHEN DTGRT IS ISSUED; THE TIME WILL BE 100nS MIN to 150ns MAX FROM DTGRT. 5. HSFAIL IS ASSERTED UPON EXCESS DTGRT RESPONSE TIME.

- INCMD WILL SUBSEQUENTLY GO LOW, AND NO FURTHER DATA TRANSFERS WILL OCCUR.

- RTFAIL IS CLEARED WHEN THE STATUS WORD IS TRANSMITTED. ONCE SET, FLAG WILL REMAIN SET FOR THE ENTIRE MESSAGE. THE INCMD FALLING EDGE CAN BE USED TO LATCH RTFAIL STATUS. 6.

- 7. 100nS MIN REPRESENTS SETUP TIME FOR VALID DATA BEFORE DTSTR GOES LOW FOR A WRITE CYCLE. A READ CYCLE REQUIRES VALID DATA 160 nS MAX AFTER DTACK GOES LOW

### FIGURE 4. RECEIVE TIMING DIAGRAM

4. THE POSITION OF DTACK WILL VARY DEPENDING ON WHEN DTGRT IS ISSUED; THE TIME WILL BE 100NS MIN TO 150ns MAX FROM DTREQ

5. HSFAIL IS ASSERTED UPON EXCESS DTGRT RESPONSE TIME. GBR WILL NOT BE SET.

6. RTFAIL IS CLEARED WHEN THE STATUS WORD IS TRANSMITTED. ONCE SET, FLAG WILL REMAIN SET FOR THE ENTIRE MESSAGE.

THE INCMD FALLING EDGE CAN BE USED TO LATCH RTFAIL STATUS.

7. 100nS MIN REPRESENTS SETUP TIME FOR VALID DATA BEFORE DTSTR GOES LOW.

# FIGURE 5. RT TO RT (RECEIVE) TIMING DIAGRAM

1. LEGEND DON'T CARE

DATA BUS UNDEFINED

.... REPRESENTS THE SEQUENCE OF EVENTS IF THE COMMAND WAS BROADCAST.

NOTE: NO STATUS WOULD BE TRANSMITTED ON1553 BUS. 2. EACH WORD IS DRIVEN FOR  $\cong$  18-19µS ON D15-D0.

IF BUF ENA IS ACTIVE THE LAST WORD IS AVAILABLE FOR 3.5-4µS SINCE THE STATUS WORD MUST BE SUPPORTED.

DATA BUS IS SHOWN WITH BUF ENA CONNECTED TO DTACK (SEE PIN FUNCTION TABLE, PIN 67)

THE TIMING DIAGRAM REPRESENTS A <u>DTGRT RESPONSE</u> TIME OF 0.92µS FOR COMMAND TRANSFER AND 2.1µS FOR DATA. THE MAXIMUM RESPONSE TIME FROM DTREQ TO DTGRT TO GUARANTEE A <u>SUCCESSFUL</u> TRANSFER IS 1.5µS FOR THE COMMAND TRANSFER AND 2.3µS FOR DATA TRANSFER TO THE SUBSYSTEM. THE POSITION OF DTACK WILL VARY DEPENDING ON WHEN DGRT IS ISSUED 5. RTFAIL IS CLEARED WHEN THE STATUS WORD IS TRANSMITTED. ONCE SET, FLAG WILL REMAIN SET FOR THE ENTIRE MESSAGE. THE INCMD FALLING EDGE CAN BE USED TO LATCH RTFAIL STATUS.

6. 100nS MIN REPRESENTS SETUP TIME FOR VALID DATA BEFORE DTSTR GOES LOW.

# FIGURE 6. RT TO RT (TRANSMIT) TIMING DIAGRAM

6. 100nS MIN REPRESENTS SETUP TIME FOR VALID DATA BEFORE DTSTR GOES LOW FOR A WRITE CYCLE.

A READ CYCLE REQUIRES VALID DATA 150nS MAX AFTER DTACK GOES LOW.

# MODE CODES

The BUS-65142 implements all mode codes applicable to dualredundant systems. Mode codes can also be illegalized using the appropriate I/O signals. Mode command illegalization and handling are detailed below in TABLE 2.

# **TABLE 2. MODE CODES IMPLEMENTED** DYNAMIC BUS CONTROL (00000) **MESSAGE SEQUENCE = DBC \* STATUS** The RT responds with status. If the subsystem wants control of the bus, it must set DBACC in the Configuration Register. ERROR CONDITIONS 1. Invalid Command. No response, command ignored. 2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word). 3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error (BIT Word). 4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error (BIT Word). 5. Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code (BIT Word). SYNCHRONIZE WITHOUT DATA WORD (00001) **MESSAGE SEQUENCE = SYNC \* STATUS** The RT responds with status. If sent as a broadcast, the broadcast receive bit will be set and status response suppressed. **ERROR CONDITIONS** 1. Invalid Command. No response, command ignored. 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word) 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word). 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error (BIT Word). STATUS WORD (00010) MESSAGE SEQUENCE = TRANSMIT WORD \* STATUS The status and BIT word registers are not altered by this command and contain the status from the previous command. **ERROR CONDITIONS** 1. Invalid Command. No response, command ignored. 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word) 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word). 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error (BIT Word). 5. Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word). INITIATE SELF-TEST (00011)

### MESSAGE SEQUENCE = SELF TEST \* STATUS

The RT responds with a status word. If the command was broadcast, the broadcast received bit is set and status transmission suppressed. Short-loop test is initiated on the status word transmitted. If the test fails, an RT fail flag is set.

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. **T/R** bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word).

- 5. Faulty Test. Bits set: terminal flag (S/W), A/B Loop Test Fail, Current 1553 Bus (A or B) Loop Test Fail (BIT Word)

#### TRANSMITTER SHUTDOWN (00100)

#### **MESSAGE SEQUENCE = SHUTDOWN \* STATUS**

This command is only used with dual redundant bus systems. The RT responds with status. At the end of the status transmission, the RT inhibits any further transmission from the dual redundant channel. Once shutdown, the transmitter can only be reactivated by OVERRIDE TRANSMITTER SHUTDOWN or RESET RT commands.

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error (BIT Word).

#### TABLE 2. MODE CODES IMPLEMENTED (continued)

# OVERRIDE TRANSMITTER SHUTDOWN (00101)

MESSAGE SEQUENCE = OVERRIDE SHUTDOWN \* STATUS

This command is only used with dual redundant bus systems. The RTU responds with status. At the end of the status transmission, the RTU reenables the transmitter of the redundant bus. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. T/R bit Set to Zero. No statue response. Bits set: message error, broadcast received (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error (BIT Word).

#### INHIBIT TERMINAL FLAG BIT (00110)

#### MESSAGE SEQUENCE = INHIBIT TERMINAL FLAG \* STATUS

The RTU responds with status and inhibits further internal or external setting of the terminal flag bit in the status register. Once the terminal flag has been inhibited, it can only be reactivated by an Override Inhibit Terminal Flag or Reset RT command. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word).

#### OVERRIDE INHIBIT TERMINAL FLAG BIT (00111)

#### MESSAGE SEQUENCE = OVERRIDE INHIBIT TERMINAL FLAG \* STATUS

The RTU responds with status and reactivates the terminal flag bit in the status register. If the command was broadcast, the broadcast received bit is set and and status transmission is suppressed.

ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), T/R Error (BIT Word).

#### **RESET REMOTE TERMINAL (01000)**

#### MESSAGE SEQUENCE = RESET REMOTE TERMINAL \* STATUS

The RTU responds with status and internally reseets. Transmitter shutdown, mode commands, BIT Word, and inhibit terminal flag commands will be reseet. If the command was broadcast, the broadcast received bit is set and the status word is suppressed. **ERROR CONDITIONS**

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No statue response. Bits Set: message error (S/W), T/R Error (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response.. Bits set: message error, broadcast received (S/W), T/R Error (BIT Word).

#### RESERVED MODE COMMAND (01001-01111)

#### MESSAGE SEQUENCE = RESERVED MODE COMMAND \* STATUS

The RTU responds with clear status and no data. If the command is illegalized through an optional PROM, the message error bit is set and only the ststus word is transmitted.

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No statue response. Bits Set: message error (SW), High Word Count (BIT Word).

- 3. T/R bit Set to Zero. No statue response. Bits set: message error (S/W), Illegal Mode Code (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No statue response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code (BIT Word).

#### TABLE 2. MODE CODES IMPLEMENTED (continued)

#### TRANSMIT VECTOR WORD (10000)

#### MESSAGE SEQUENCE = TRANSMIT VECTOR WORD \* STATUS VECTOR WORD

The RTU transmits a status word followed by a vector word.

ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

- 3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), Low Word Count (BIT Word).

- Zero T/R bit and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code, T/R Error, Low Word Count (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (S/W), Illegal Mode Code, (BIT Word).

#### SYNCHRONIZE WITH DATA WORD (10001)

#### MESSAGE SEQUENCE = SYNCHRONIZE WITH DATA WORD \* STATUS

The data word received fo;;owing the command word is transferred to RAM. The status word is then transmitted. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed.

ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Not Followed by Data Word. No status response. Bits Set: message error (SW), Low Word Count (BIT Word)

- 3. Command Followed by too many Data Words. No status response. Bits Set: message error (SW), High Word Count (BIT Word)

- 4. Command T/R bit Set to One. No status response. Bits set: message error (S/W), T/R Error, High Word Count (BIT Word).

5. Command T/R bit Set to Zero and Broadcast Address. No status response. Bits set: message error, broadcast received (S/W), High Word Count, T/R Erro (BIT Word).

#### TRANSMIT LAST COMMAND (10010)

#### MESSAGE SEQUENCE = TRANSMIT LAST COMMAND \* STATUS

The status and BIT word registers are not altered by this command. The SW contains the status from the previous command. The data word transmitted contains the previous valid command (providing it was not another TRANSMIT LAST COMMAND).

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits Set: message error (SW)

- 3. T/R bit Set to Zero. No status response. Bits set: message error (S/W), T/R Error, Low Word Count (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response. Bits Set: message error (S/W), Illegal Mode Code, T/R Error (BIT Word).

- 5. Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W), Illegal Mode Code (BIT Word).

#### TRANSMIT BIT WORD (10011)

#### MESSAGE SEQUENCE = TRANSMIT BIT WORD \* STATUS

The RTU responds with status followed by the BIT word. The BIT word is not altered by this command; however, the next SW will reflect errors in this trnsmission.

#### ERROR CONDITIONS

- 1. Invalid Command. No response, command ignored.

- 2. Command Followed by Data Word. No status response. Bits Set: message error (SW).

- 3. T/R bit Set to Zero. No status response. Bits Set: message error (S/W), T/R Error, Low Word Count (BIT Word).

- 4. Zero T/R bit and Broadcast Address. No status response.. Bits set: message error (S/W), Illegal Mode Code, T/R Error, Low Word Count (BIT Word).

- 5. Broadcast Address. No status response. Bits set: message error, broadcast received (S/W), Illegal Mode Code (BIT Word)

| TABLE 2. MODE CODES IMPLEMENTED (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>SELECTED TRANSMITER SHUTDOWN (10100)<br/>MESSAGE SEQUENCE = SELECTED TRANSMITER SHUTDOWN * STATUS VECTOR WORD<br/>The data word received is transmitted to the subsystem and status is transmitted. No other action is taken by the RTU. If the command was<br/>broadcast, the broadcast received bit is set and status transmission suppressed. Intended for use with RT's with more than one dual redundant<br/>channel.</li> <li>ERROR CONDITIONS <ol> <li>Invalid Command. No response, command ignored.</li> <li>Command Not Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count, Illegal Mode Code (BIT Word)</li> <li>Command Followed by too many Data Word. No status response. Bits Set: message error (SW), Low Word Count,<br/>Illegal Mode Code (BIT Word)</li> </ol> </li> <li>Command T/R bit Set to One. No status response. Bits set: message error (S/W), Illegal Mode Code, High Word Count (BIT Word).</li> <li>Command T/R bit Set to One and Broadcast Address. No status response. Bits Set: message error, broadcast received (S/W),<br/>Illegal Mode Code, High Word Count (BIT Word).</li> </ul> |

| <ul> <li>OVVERRIDE SELECTED TRANSMITTER SHUTDOWN (10101)<br/>MESSAGE SEQUENCE = OVVERRIDE SELECTED TRANSMITTER SHUTDOWN * STATUS<br/>The data word received after the command is transferred to the subsystem. No other action is taken by the RTU. If the command was broadcast, the broadcast received bit is set and status transmission suppressed.</li> <li>ERROR CONDITIONS <ol> <li>Invalid Command. No response, command ignored.</li> <li>Command Not Followed by Data Word. No status response. Bits Set: message error (SW), Low Word Count, Illegal Mode Code (BIT Word)</li> <li>Command Followed by too many Data Words. No status response. Bits Set: message error (SW), High Word Count, Illegal Mode Code (BIT Word)</li> <li>Command T/R bit Set to One. No status response. Bits set: message error (S/W), Illegal Mode Code, High Word Count (BIT Word).</li> </ol> </li> <li>Command T/R bit Set to One and Broadcast Address. No status response. Bits set: message error, broadcast received (S/W), Illegal Mode Code, High Word Count, T/R Erro (BIT Word).</li> </ul>                                                                          |

| <ul> <li>RESERVED MODE CODES (10110-11111)<br/>MESSAGE SEQUENCE = RESERVED MODE CODE (T/R = 1) * STATUS<br/>RESERVED MODE CODE (T/R = 0) * STATUS<br/>If Valid (T/R = 0)<br/>The RTU responds with status. If the command was broadcast, the broadcast received bit is set and status transmission is suppressed. If the command is illegalized through an optional PROM, the message error bit is set and only the status word is transmitted.<br/>If Valid (T/R = 1)<br/>Respond with status and one data word.<br/>ERROR CONDITIONS (T/R = 1)</li> <li>Invalid Command. No response, command ignored.</li> <li>Command Followed by Data Word. No status response. Bits Set: message error (SW), High Word Count, Illegal Mode Code (BIT Word).<br/>ERROR CONDITIONS (T/R = 0)</li> <li>Invalid Command. No response, command ignored.</li> <li>Command not followed by Contiguous Data Word. No status response. Bits set: message error (S/W), Low Word Count,<br/>Illegal Mode Code (BIT Word).</li> <li>Command followed by to many Data Words. No status response. Bits Set: message error (S/W), High Word Count,<br/>Illegal Mode Code (BIT Word).</li> </ul>   |

UNDEFINED MODE CODES (T/R = 0, MODE CODES 00000 TO 01111) No Response, set message error bit.

|                   | PIN FUNCTION TABLE          |                             |                      |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-------------------|-----------------------------|-----------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PAC               | AGE                         | & PIN                       |                      |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 78-<br>Pin<br>QIP | 82-<br>Pin<br>Flat-<br>Pack | 78-<br>Pin<br>Flat-<br>Pack | FUNCTION             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 1                 | 2                           | 1                           | A9<br>(SA4)          | Latched output of the most significant bit<br>(MSB) in the subaddress field of the<br>command word.                                                                                                                                                                                                                                                         |  |  |  |

| 2                 | 4                           | 3                           | A7<br>(SA2)          | Latched output of the third most signifi-<br>cant bit in the subaddress field of the<br>command word.                                                                                                                                                                                                                                                       |  |  |  |

| 3                 | 6                           | 5                           | A5<br>(SA0)          | Latched output of the least significant bit (LSB) in the subaddress field of the command word.                                                                                                                                                                                                                                                              |  |  |  |

| 4                 | 8                           | 7                           | DB1                  | Bi-directional parallel data bus Bit 1                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 5                 | 10                          | 9                           | DB3                  | Bi-directional parallel data bus Bit 3                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 6                 | 12                          | 11                          | DB5                  | Bi-directional parallel data bus Bit 5                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 7                 | 14                          | 13                          | DB7                  | Bi-directional parallel data bus Bit 7                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 8                 | 16                          | 15                          | DB9                  | Bi-directional parallel data bus Bit 9                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 9                 | 18                          | 17                          | DB11                 | Bi-directional parallel data bus Bit 11                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 10                | 20                          | 19                          | DB13                 | Bi-directional parallel data bus Bit 13                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 11                | 22                          | 21                          | DB15                 | Bi-directional parallel data bus Bit 15<br>(MSB)                                                                                                                                                                                                                                                                                                            |  |  |  |

| 12                | 24                          | 23                          | BRO ENA              | Broadcast enable - when HIGH, this<br>input allows recognition of an RT address<br>of all ones in the command word as a<br>broadcast message. When LOW, it pre-<br>vents response to RT address 31 unless<br>it has the assigned<br>terminal address.                                                                                                       |  |  |  |

| 13                | 26                          | 25                          | ADDRE<br>(RTAD4)     | Input of the MSB of the assigned termi-<br>nal address.                                                                                                                                                                                                                                                                                                     |  |  |  |

| 14                | 28                          | 27                          | ADDRC<br>(RTAD2)     | Input of the 3rd MSB of the assigned terminal address.                                                                                                                                                                                                                                                                                                      |  |  |  |

| 15                | 30                          | 29                          | ADDRA<br>(RTAD0)     | Input of the LSB of the assigned terminal address.                                                                                                                                                                                                                                                                                                          |  |  |  |

| 16                | 32                          | 31                          | RTADERR              | Output signal used to inform subsystem<br>of an address parity error. If LOW, indi-<br>cates parity error and the RT will not<br>respond to any command address to a<br>single terminal. It will respond to broad-<br>cast commands if BRO ENA is HIGH.                                                                                                     |  |  |  |

| 17                | 34                          | 33                          | TXDATA B             | LOW output to the primary side of the<br>coupling transformer that connects B<br>channel of the 1553 bus.                                                                                                                                                                                                                                                   |  |  |  |

| 18                | 36                          | 35                          | NC                   |                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 19                | 38                          | 37                          | GND B                | Power Supply return connection for the B channel transceiver.                                                                                                                                                                                                                                                                                               |  |  |  |

| 20                | 40                          | 39                          | RXDATA B             | Input from the HIGH side of the primary side of the coupling transformer that connects to the B channel of the 1553 Bus.                                                                                                                                                                                                                                    |  |  |  |

| 21                | 81                          | 78                          | A3<br>(WC3/<br>CWC3) | Multiplexed address line output. When<br>INCMD is LOW or A5 thru A9 are all<br>zeroes or all ones (Mode Command), it<br>represents the latched output of the 2nd<br>MSB in the word count field of the com-<br>mand word. When INCMD is HIGH and<br>A5 thru A9 are not all zeroes or all ones,<br>it represents the 2nd MSB of the current<br>word counter. |  |  |  |

| 22                | 79                          | 76                          | A1<br>(WC1/<br>CWC1) | Multiplexed address line output. When<br>INCMD is LOW or A5 thru A9 are all<br>zeroes or all ones (Mode Command), it<br>represents the latched output of the 2nd<br>LSB in the word count field of the com-<br>mand word. When INCMD is HIGH and<br>A5 thru A9 are not all zeroes or all ones,<br>it represents the 2nd LSB of the current<br>word counter. |  |  |  |

|                           |                                    |                                      | FUNCTION  | TABLE (continued)                                                                                                                                                                                                                                                                                                                        |

|---------------------------|------------------------------------|--------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PACH<br>78-<br>Pin<br>QIP | AGE<br>82-<br>Pin<br>Flat-<br>Pack | & PIN<br>78-<br>Pin<br>Flat-<br>Pack | FUNCTION  | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

| 23                        | 77                                 | 74                                   | DTGRT     | Data transfer grant active LOW input<br>signal from the subsystem that informs<br>the RT, when DTREQ is asserted, to start<br>the transfer. Once transfer is started,<br>DTGRT can be removed.                                                                                                                                           |

| 24                        | 75                                 | 72                                   | INCMD     | In-Command HIGH level output signal used to inform the subsystem that the RT is presently servicing a command.                                                                                                                                                                                                                           |

| 25                        | 73                                 | 70                                   | HSFAIL    | Handshake Fail output signal that goes<br>LOW and stays LOW whenever the sub-<br>system fails to supply DTGRT in time to<br>do a <u>succe</u> ssful transfer. Cleared by the<br>next NBGT.                                                                                                                                               |

| 26                        | 71                                 | 68                                   | DTSTR     | A LOW level output pulse (166ns) present<br>in the middle of every data word transfer<br>over the parallel data bus. Used to latch<br>or strobe the data into memory, FIFOs,<br>registers, etc. Recommended using the<br>rising edge to clock data in.                                                                                   |

| 27                        | 69                                 | 66                                   | (DAT/CMD) | Address line output that is LOW whenever<br>the command word is being transferred to<br>the subsystem over the parallel data bus,<br>and is HIGH whenever data words are<br>being transfered.                                                                                                                                            |

| 28                        | 67                                 | 64                                   | RTFAIL    | Remote Terminal Failure latched active<br>LOW output signal to the subsystem to<br>flag detection of a remote terminal contin-<br>uous self-test failure. Also set if the<br>Watchdog Timeout circuit is activated.<br>Cleared by the start of the next message<br>transmission (status word) and set if prob-<br>lem is again detected. |

| 29                        | 65                                 | 62                                   | DTREQ     | Data Transfer Requestactive LOW out-<br>put signal to the subsystem indicating that<br>the RT has data for or needs data from<br>the subsystem and requests a data trans-<br>fer over the parallel data bus. Will stay<br>LOW until transfer is completed or transfer<br>timeout has ocurred.                                            |

| 30                        | 63                                 | 60                                   | ADBC      | Accept Dynamic Bus Control active<br>LOW input signal from the subsystem<br>used to set the Dynamic Bus Control<br>Acceptance bit in the status register if the<br>command word was a valid, legal mode<br>command for dynamic bus control.                                                                                              |

| 31                        | 61                                 | 58                                   | TEST 2    | Factory test point output-DO NOT USE (see note 1)*                                                                                                                                                                                                                                                                                       |

| 32                        | 59                                 | 56                                   | A10 (T/R) | Latched output of the T/R bit in the com-<br>mand word.                                                                                                                                                                                                                                                                                  |

| 33                        | 57                                 | 54                                   | ILLCMD    | Illegal Commandactive LOW input signal<br>from the subsystem, strobed in on the ris-<br>ing edge of INCMD. Used to define the<br>command word as illegal and to set the<br>message error bit in the status register.                                                                                                                     |

| 34                        | 55                                 | 52                                   | SS REQ    | Subsystem Service Request Input from<br>the subsystem used to control the Service<br>Request Bit in the status register. If LOW<br>when the status word is updated, the<br>Service Request Bit will be set; if HIGH, it<br>will be cleared.                                                                                              |

| 35                        | 53                                 | 50                                   | BITEN     | Built-in-Test Word EnableLOW level output<br>pulse (.5µs), present when the built-in-test<br>word is enabled on the parallel data bus.                                                                                                                                                                                                   |

| 36                        | 51                                 | 48                                   | RXDATA A  | Input from the LOW side of the primary side of the coupling transformer that connects to the A channel of the 1553 Bus.                                                                                                                                                                                                                  |

|                   | PIN FUNCTION TABLE (continued) |                             |                      |                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-------------------|--------------------------------|-----------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PACK              | AGE                            | & PIN                       |                      |                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 78-<br>Pin<br>QIP | 82-<br>Pin<br>Flat-<br>Pack    | 78-<br>Pin<br>Flat-<br>Pack | FUNCTION             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                 |  |  |

| _                 | 49                             | 46                          | +5VA                 | +5V input power supply connection for the A channel transceiver.                                                                                                                                                                                                                                                                                            |  |  |

| 38                | 47                             | 44                          | -VA                  | -15V/-12V input power supply connection for the A Channel transceiver (Note 5).                                                                                                                                                                                                                                                                             |  |  |

| 39                | 45                             | 42                          | TXDATA A             | HIGH output to the primary side of the coupling transformer that connects to the A channel of the 1553 Bus.                                                                                                                                                                                                                                                 |  |  |

| 40                | 43                             | 40                          | NBGT                 | New Bus Grant LOW level output pulse<br>(166ns) used to indicate the start of a<br>new protocol sequence in response to the<br>command word just received.                                                                                                                                                                                                  |  |  |

| 41                | 3                              | 2                           | A8<br>(SA3)          | Latched output of the 2nd MSB in the subaddress field of the command word.                                                                                                                                                                                                                                                                                  |  |  |

| 42                | 5                              | 4                           | A6<br>(SA1)          | Latched output of the 2nd LSB in the sub-<br>address field of the command word.                                                                                                                                                                                                                                                                             |  |  |

| 43                | 7                              | 6                           | DB0                  | Bi-directional parallel data bus Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                |  |  |

| 44                | 9                              | 8                           | DB2                  | Bi-directional parallel data bus Bit 2                                                                                                                                                                                                                                                                                                                      |  |  |

| 45                | 11                             | 10                          | DB4                  | Bi-directional parallel data bus Bit 4                                                                                                                                                                                                                                                                                                                      |  |  |

| 46                | 13                             | 12                          | DB6                  | Bi-directional parallel data bus Bit 6                                                                                                                                                                                                                                                                                                                      |  |  |

| 47                | 15                             | 14                          | DB8                  | Bi-directional parallel data bus Bit 8                                                                                                                                                                                                                                                                                                                      |  |  |

| 48                | 17                             | 16                          | DB10                 | Bi-directional parallel data bus Bit 10                                                                                                                                                                                                                                                                                                                     |  |  |

| 49                | 19                             | 18                          | DB10<br>DB12         | Bi-directional parallel data bus Bit 12                                                                                                                                                                                                                                                                                                                     |  |  |

| -                 | 21                             | -                           | DB12<br>DB14         |                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 50                | 21                             | 20                          | DB14                 | Bi-directional parallel data bus Bit 14                                                                                                                                                                                                                                                                                                                     |  |  |

| 51                | 23                             | 22                          | +5V                  | +5V input power supply connection for<br>RTU digital logic section.                                                                                                                                                                                                                                                                                         |  |  |

| 52                | 25                             | 24                          | GND                  | Power supply return for RTU digital logic section.                                                                                                                                                                                                                                                                                                          |  |  |

| 53                | 27                             | 26                          | ADDRD                | Input of the 2nd MSB of the assigned ter-<br>minal address.                                                                                                                                                                                                                                                                                                 |  |  |

| 54                | 29                             | 28                          | ADDRB                | Input of the 2nd LSB of the assigned ter-<br>minal address.                                                                                                                                                                                                                                                                                                 |  |  |

| 55                | 31                             | 30                          | ADDRP                | Input of Address Parity Bit. The combina-<br>tion of assigned terminal address and<br>ADDRP must be odd parity for the RT to<br>work.                                                                                                                                                                                                                       |  |  |

| 56                | 33                             | 32                          | TXDATA B             | HIGH, output to the primary side of the coupling transformer that connects to the B channel transceiver.                                                                                                                                                                                                                                                    |  |  |

|                   | 35                             | 34                          | -VB                  | -15V/-12V input power supply connection for the B channel transceiver (Note 5).                                                                                                                                                                                                                                                                             |  |  |

| 58                | 37                             | 36                          | +5VB                 | +5 V input power supply connection for<br>the B channel transceiver.                                                                                                                                                                                                                                                                                        |  |  |

| 59                | 39                             | 38                          | RXDATA B             | Input from the LOW side of the primary<br>side of the coupling transformer that con-<br>nects to the B channel of the 1553 Bus.                                                                                                                                                                                                                             |  |  |

| 60                | 80                             | 77                          | A2<br>(WC2/<br>CSW2) | Multiplexed address line output. When<br>INCMD is LOW or A5 thru A9 are all<br>zeroes or all ones (Mode Command), it<br>represents the latched output of the 3rd<br>MSB in the word count field of the com-<br>mand word. When INCMD is HIGH and<br>A5 thru A9 are not all zeroes or all ones,<br>it represents the 3rd MSB of the current<br>word counter. |  |  |

| 61                | 78                             | 75                          | A0<br>(WCO/<br>CSWO) | Multiplexed address line output. When<br>INCMD is LOW or A5 thru A9 are all<br>zeroes or all ones (Mode Command), it<br>represents the latched output of the LSB<br>in the word count field of the command<br>word. When INCMD is HIGH and A5 thru<br>A9 are not all zeroes or all ones, it repre-<br>sents the LSB of the current word counter.            |  |  |

|                           | PIN FUNCTION TABLE (continued)     |                                      |                      |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |