# Am100415

1024 x 1 IMOX™ II ECL Bipolar RAM

#### DISTINCTIVE CHARACTERISTICS

- Fast access time (8 ns typ.) improves system cycle

- Enhanced output voltage level compensation providing 6X (improvement in) VOL and VOH stability over supply and temperature ranges

- Internally voltage and temperature compensated providing flat AC performance

- Outputs preconditioned during write cycle eliminating write recovery glitch

- Emitter follower outputs -- easy wire-ORing

- Power dissipation decreases with increasing temperatura

#### GENERAL DESCRIPTION

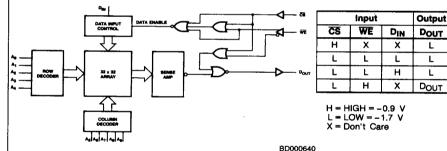

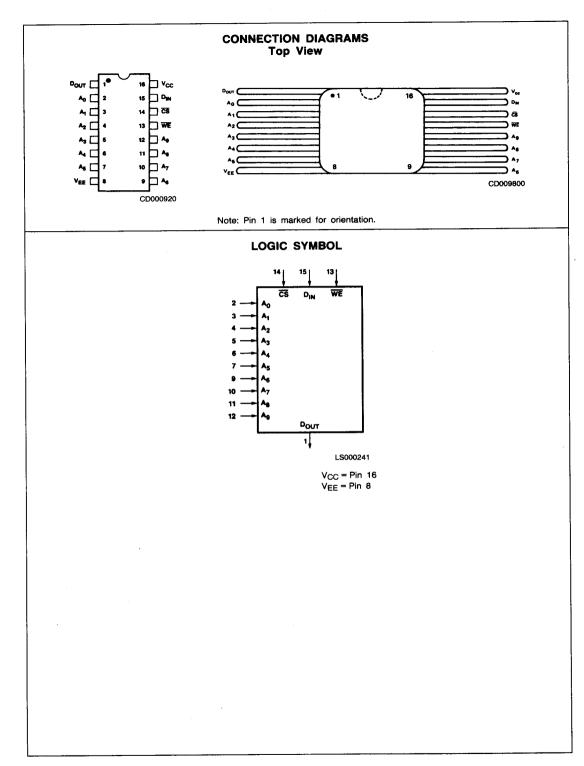

The Am100415 is a fully decoded 1024-bit ECL RAM organized 1024 words by one bit. Bit selection is achieved by means of a 10-bit address, Ao through Ag. Easy memory expansion is provided by an active-LOW chip select (CS) input and an unterminated OR-tieable emitter follower output.

An active-LOW write line (WE) controls the write/read operation of the memory. When the chip select and write lines are LOW, the data input (DIN) is written into the addressed memory word simultaneously preconditioning

the output so true data is present when the write cycle is complete. This preconditioning operation insures minimum write recovery times by eliminating the "write recovery alitch."

Reading is performed with the chip select line LOW and the write line HIGH. The information stored in the addressed word is read out on the noninverting output (DOUT).

During the writing operation or when the chip select line is HIGH, the output of the memory goes to a LOW state.

## MODE SELECT TABLE

L

L

Mode

Not Selected

Write "0"

Write "1"

Read

#### PRODUCT SELECTOR GUIDE

#### Highlights of Key Performance Parameters (Commercial)

| Part Number                                                           | Am100415-10 | Am100415A | Am100415 |

|-----------------------------------------------------------------------|-------------|-----------|----------|

| Address Access Time (tAA)                                             | 10 ns       | 15 ns     | 20 ns    |

| Write Pulse Width (tw)                                                | 10 ns       | 10 ns     | 12 ns    |

| Write Recovery (twR)                                                  | 10 ns       | 12 ns     | 15 ns    |

| Chip Select Access/<br>Recovery (t <sub>ACS</sub> /t <sub>RCS</sub> ) | 8 ns        | 8 ns      | 8 ns     |

| Write Disable (tws)                                                   | 10 ns       | 10 ns     | 10 ns    |

| Power Supply (I <sub>EE</sub> )                                       | 150 mA      | 150 mA    | 150 mA   |

IMOX is a trademark of Advanced Micro Devices, Inc.

Publication # Amendment Issue Date: May 1986

3-1

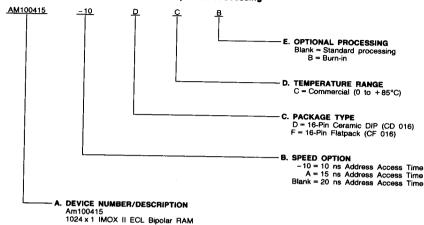

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

B. Speed Option (if applicable)

C. Package Type

D. Temperature Range

E. Optional Processing

| Valid Combinations |                    |  |  |  |  |  |

|--------------------|--------------------|--|--|--|--|--|

| AM100415-10        |                    |  |  |  |  |  |

| AM100415A          | DC, DCB<br>FC, FCB |  |  |  |  |  |

| Am100415           | FC, FCB            |  |  |  |  |  |

#### **Valid Combinations**

B = Burn-in

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to +150°C                 |

|-------------------------------------------------|

| Case Temperature with                           |

| Power Applied55 to +125°C                       |

| VFF Pin Potential to                            |

| GND Pin7.0 V to +0.5 V                          |

| Input Voltage (DC)VEE to +0.5 V                 |

| Output Current (DC Output HIGH)30 mA to +0.1 mA |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices |    |        |

|------------------------|----|--------|

| Temperature0           | to | +85°C  |

| Supply Voltage5.7 V    | to | -4.2 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS V<sub>EE</sub> = -4.5 V, V<sub>CC</sub> = GND (Note 2)

| Parameter<br>Symbol | Parameter<br>Description                            | Test Co                            | B(Note<br>3)                | <b>Typ.</b> (Note 1) | A<br>(Note 3) | Units  |    |

|---------------------|-----------------------------------------------------|------------------------------------|-----------------------------|----------------------|---------------|--------|----|

| VoH                 | Output Voltage HIGH                                 | VIN = VIHA OF VILB                 |                             | - 1025               | -955          | -880   | mV |

| Vol                 | Output Voltage LOW                                  | - VIN VIAX S. VILE                 | Loading is                  | -1810                | -1715         | - 1620 | mV |

| VOHC                | Output Voltage HIGH                                 | VIN = VIHB OF VILA                 | 50 Ω to -2.0 V              | - 1035               |               |        | mV |

| Volc                | Output Voltage LOW                                  | T VIN TIME OF TICK                 |                             |                      |               | -1610  | mV |

| ViH                 | Input Voltage HIGH                                  | Guaranteed Input Voltage<br>4)     | -1165                       |                      | -880          | m∨     |    |

| V <sub>IL</sub>     | Input Voltage LOW                                   | Guaranteed Input Voltage<br>4)     | -1810                       |                      | -1475         | mV     |    |

| l <sub>IH</sub>     | Input Current HIGH                                  | V <sub>IN</sub> = V <sub>IHA</sub> |                             |                      | 220           | μΑ     |    |

| hL                  | Input Current LOW Chip Select (CS) All Other Inputs | V <sub>IN</sub> = V <sub>ILB</sub> |                             | 0.5<br>-50           |               | 170    | μΑ |

| IEE                 | Power Supply Current<br>(Pin 8)                     | All Inputs and Outputs O           | All Inputs and Outputs Open |                      |               |        | mA |

Notes: 1. Typical values are at VEE = -4.5 V, T = 25°C and maximum loading.

2. Output load = 50  $\Omega$  and 30 pF to -2.0 V

T = T<sub>A</sub> = 0 to +85°C for Ceramic DIPs.

Guaranteed with transverse air flow exceeding 400 linear F.P.M. and 2-minute warm-up period. Approximate resistance values of the package are:

$\theta_{\rm JA}$  (Junction to Ambient) = 90°C/Watt (still air)

$\theta_{\rm JA}$  (Junction to Ambient) = 50°C/Watt (at 400 F.P.M. air flow) T = T<sub>C</sub> = 0 to +85°C for Flatpacks and Leadless Chip Carriers

$\theta_{\rm JC}$  (Junction to Case) = 25°C/Watt

3. Definition of symbols and terms used in this product specification: The relative values of the specified conditions and limits will be referenced to an algebraic scale. The extremities of the scale are: "A" the value closest to positive infinity, "B" the value closest to negative infinity.

4. These are absolute voltages with respect to device ground pin and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

C<sub>L</sub> = 30 pF (including stray jig capacitance)

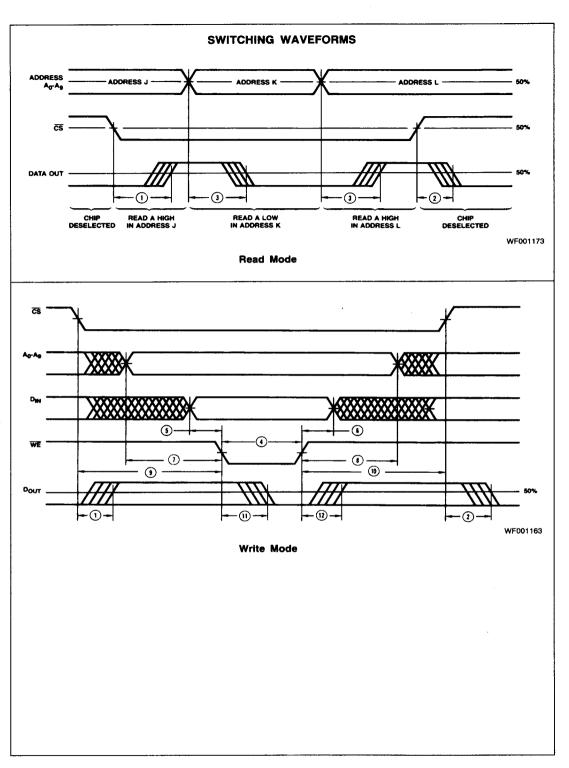

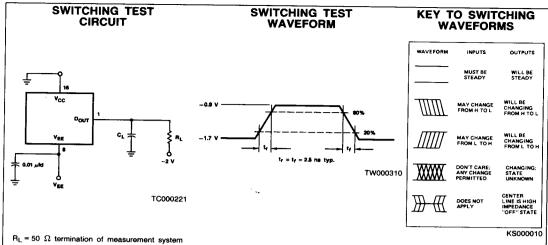

# **SWITCHING CHARACTERISTICS** $V_{EE} = -4.27$ to -4.73 V (Note 2)

| No.     | Parameter<br>Symbol     | Parameter<br>Description                 | Test<br>Conditions                           | Am100415A-10 |                  |      | Am100415A |      |      | Am 100415     |           |           |       |

|---------|-------------------------|------------------------------------------|----------------------------------------------|--------------|------------------|------|-----------|------|------|---------------|-----------|-----------|-------|

|         |                         |                                          |                                              | Min.         | Typ.<br>(Note 1) | Max. | Min.      | Typ. | Max. | Min.          | Typ.      | Max.      | Units |

| REAL    | MODE                    |                                          |                                              |              |                  |      |           |      |      |               | (110.0 1) | I WILLIAM | Oille |

| 1       | tacs                    | Chip Select Access<br>Time               | Measured at 50% of input to valid            |              | 5                | 8    |           | 5    | 8    |               | 5         | 8         |       |

| 2       | trics                   | Chip Select Recovery<br>Time             | output (VILA for<br>VOL or VIHB for<br>VOH)  |              | 5                | 8    |           | 5    | 8    |               | 5         | 8         | ns    |

| 3       | tAA                     | Address Access Time                      |                                              |              | 8                | 10   | -         | 10   | 15   | -             | 12        | 20        |       |

| WRIT    | E MODE                  |                                          |                                              |              |                  |      |           |      |      |               |           |           |       |

| 4       | tw                      | Write Pulse Width (to Guarantee Writing) | twsa = twsa(Min.)                            | 10           | 6                |      | 10        | 6    |      | 12            | 9         |           | ns    |

| 5       | twsp                    | Data Setup Time<br>Prior to Write        |                                              | 1            | 0                |      | 2         | 0    |      | 4             | 0         |           | ns    |

| 6       | twho                    | Data Hold Time<br>After Write            |                                              | 1            | 0                |      | 2         | 0    |      | 4             | 0         |           | ns    |

| 7       | twsa                    | Address Setup Time<br>Prior to Write     | tw = tw(Min.)                                | 1            | 0                |      | 3         | 3    |      | 5             | 3         |           | ns    |

| 8       | twha                    | Address Hold Time<br>After Write         |                                              | 1            | 0                |      | 2         | 0    |      | 3             | 0         |           | ns    |

| ľ       |                         |                                          | Measured at 50%                              | 1            | 0                |      | 2         | ō    |      | 4             | 0         | -         | ns    |

| 9 twscs | Chip Select Setup of in | of input to valid<br>output (VILA for    | 1                                            | 0            |                  | 2    | 0         |      | 4    | 0             |           | ns        |       |

| ĺ       | • wscs                  | Prior to Write                           | VOL or VIHB for                              |              | 5                | 10   |           | 5    | 10   |               | 5         | 10        | ns    |

|         |                         |                                          | VOH)                                         |              | 6                | 10   |           | 6    | 12   |               | 7         | 15        | ns    |

| RISE    | TIME AND F              | ALL TIME                                 |                                              | _            |                  |      |           |      |      |               |           |           |       |

|         | tr                      | Output Rise Time                         | Measured<br>between<br>20% and 80%<br>points |              | 2.5              |      |           | 2.5  |      |               | 2.5       |           |       |

|         | t <sub>f</sub>          | Output Fall Time                         |                                              |              | 2.5              |      |           | 2.5  |      |               | 2.5       |           | ns    |

| CAPA    | CITANCE                 |                                          | ·                                            |              |                  |      |           |      |      |               |           |           |       |

| - 1     | CIN                     | Input Pin Capacitance                    | Management with a                            | T            | 4                | 5    |           | 4    | 5    | $\overline{}$ | 4         | 5         | рF    |

|         | COUT                    | Output Pin<br>Capacitance                | Measure with a<br>Pulse Technique            |              | 7                | 8    |           | 7    | 8    |               | 7         | 8         | pF    |