# Low Cost, Low Power Stereo Audio Analog Front End

# **Preliminary Technical Data**

AD74322

#### **FEATURES**

2.5V Stereo Audio Codec with 3.3 V Tolerant Digital Interface

Supports 96 kHz Sample Rates

Supports 16/18 /20/24-Bit Word Lengths

Multibit Sigma Delta Modulators with

"Perfect Differential Linearity Restoration" for

Reduced Idle Tones and Noise Floor

Data Directed Scrambling DACs - Least Sensitive to Jitter Performance (20 Hz to 20 kHz)

90 dB ADC and DAC SNR

Digitally Programmable Input/Output Gain

On-chip Volume Controls Per Output Channel

Hardware and Software Controllable Clickless Mute

Supports 256xFs, 512xFs and 768xFs Master Mode Clocks Master Clock Pre-Scaler for use with DSP master clocks

Flexible Serial Data Port with Right-Justified, Left-

Justified, I<sup>2</sup>S-Compatible and DSP Serial Port Modes

Supports Packed Data Mode ("TDM") for cascading devices.

**On-Chip Reference**

16, 20 and 24-Lead SOIC, SSOP and TSSOP Package options.

#### **APPLICATIONS**

**Digital Video Camcorders (DVC)**

Portable Audio Devices (Walkman etc)

**Audio Processing**

**Voice Processing**

**Conference Phones**

General Purpose Analog I/O

#### **GENERAL DESCRIPTION**

The AD74322 is a front-end processor for general purpose audio and voice applications. It features two multi-bit  $\Sigma\Delta$  A/D conversion channels and two multi-bit  $\Sigma\Delta$  D/A conversion channels. Each ADC channel provides >85 dB signal-to-noise ratio while each DAC channel provides >90 dB, both over an audio signal bandwidth.

The AD74322 is particularly suitable for a variety of applications where stereo input and output channels are required, including audio sections of Digital Video Camcorder, portable personal audio devices and the analog front ends of conference phones . Its high quality performance also make it suitable for speech and telephony applications such as speech recognition and synthesis and modern feature phones.

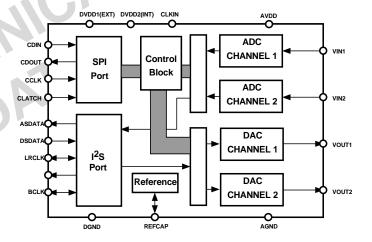

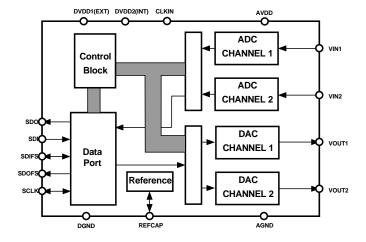

#### FUNCTIONALBLOCKDIAGRAM DVDD1(EXT) DVDD2(INT) CLKIN ADC CDIN **CHANNEL 1** Control SPI CDOUT VIN1N Block Port CCL ADC CLATCH **CHANNEL 2** DAC VOUT1P **CHANNEL 1** ı<sup>2</sup>s VOUT1N Port SDOF DAC VOUT2P Reference BCLK/SCLK CHANNEL 2 VOUT2N AGND REFCAP

#### REV. Pr D 03/00

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 Analog Devices, Inc., 1998

## AD74322

## PRELIMINARY TECHNICAL DATA

An on-chip reference voltage is included but can be bypassed if required for use with an external reference source.

The AD74322 offers sampling rates which, depending on MCLK selection and MCLK divider ratio, range from 8 kHz in the voiceband range to 96 kHz in the audio range.

The digital interface to the AD74322 is configured as two separate ports which allow separation of device control and data streams. Control and status are monitored using an SPI® compatible serial port while the input and output data streams are controlled using an  $\rm I^2S^{\circledast}$  port. The two  $\rm I^2S$  streams are controlled by a common Bit-Clock and Left/Right Clock pins. There is also a DSP mode available on the audio data port which will also allow both control and data to be streamed through the same interface where controller resources are limited.

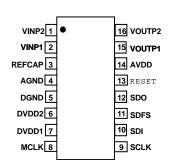

The AD74322 is available in various lead count package options. These range from a 16-pin variant with single-ended inputs/outputs and no SPI port through a 20-pin variant with single-ended inputs/outputs and an SPI port to a 24-pin variant with differential inputs/outputs and an SPI port. These devices will be available in SOIC, SSOP and TSSOP package options and are specified for the industrial temperature range of -40°C to +85°C.

-2- Pr D 03/00

|                                               |        | AD74322A    |         |           |                 |

|-----------------------------------------------|--------|-------------|---------|-----------|-----------------|

| PARAMETER                                     | Min    | Тур         | Max     | Units     | Test Conditions |

| ANALOG-TO-DIGITAL CONVERTERS                  |        |             |         |           |                 |

| ADC Resolution (all ADCs)                     |        | 24          |         | Bits      |                 |

| Dynamic Range (20 Hz to 20 kHz, -60 dB Input) |        | ~ 1         |         | Ditts     |                 |

| No Filter                                     |        | 90          |         | dB        |                 |

| With A-Weighted Filter                        |        | 92          |         | dB        |                 |

| Total Harmonic Distortion + Noise             |        | -85(0.0056) |         | dB(%)     |                 |

| Interchannel Isolation                        |        | TBD         |         | dB        |                 |

| Interchannel Gain Mismatch                    |        | TBD         |         | dB        |                 |

| Programmable Input Gain                       |        | 12          |         | dB        |                 |

| GainStepSize                                  |        | 3           |         | dB        |                 |

| Offset Error                                  |        |             | 0       | LSB       |                 |

| Full Scale Input Voltage At Each Pin          |        | 0.5 (1.414) |         | rms (Vpp) | Single Ended    |

| Automatic Level Control                       |        | ()          |         | (, pp)    |                 |

| Attack Time Resolution                        |        | TBD         |         | Bits      |                 |

| Attack Time                                   |        | TBD         |         | μs/Bit    |                 |

| Decay Time Resolution                         |        | TBD         |         | Bits      |                 |

| Decay Time                                    |        | TBD         |         | μs/Bit    |                 |

| GainDrift                                     |        | TBD         |         | ppm/°C    |                 |

| Input Resistance                              | 10     | 1111        |         | kΩ        |                 |

| Input Capacitance                             | 10     |             | 15      | pF        |                 |

| Common Mode Input Volts                       |        | 1.1V        | 10      | V         |                 |

|                                               |        | 1.11        |         | •         |                 |

| DIGITAL-TO-ANALOG CONVERTERS                  |        |             |         |           |                 |

| Dynamic Range (20 Hz to 20 kHz, -60 dB Input) |        |             |         | _         |                 |

| No Filter                                     |        | 90          |         | dΒ        |                 |

| With A-Weighted Filter                        |        | 92          |         | dB        |                 |

| Total Harmonic Distortion + Noise             |        | -85(0.0056) |         | dB(%)     |                 |

| Interchannel Isolation                        |        | TBD         |         | dB        |                 |

| Interchannel Gain Mismatch                    |        | TBD         |         | dB(%)     |                 |

| DCAccuracy                                    |        |             |         |           |                 |

| Gain Error                                    |        | TBD         |         | %         |                 |

| Interchannel Gain Mismatch                    |        | TBD         |         | ppm/°C    |                 |

| Gain Drift                                    |        | TBD         |         | dB        |                 |

| Interchannel Crosstalk (EIAJ method)          |        | TBD         |         | dB        |                 |

| Interchannel Phase Deviation                  |        | TBD         |         | Degrees   |                 |

| Volume Control Step Size (1023 Linear Steps)  |        | 0.098       |         | %         |                 |

| Volume Control Range (Max Attenuation)        |        | 60          |         | dB        |                 |

| MuteAttenuation                               |        | -100        |         | dB        |                 |

| De-emphasis Gain Error                        |        |             | +/-0.1  | dB        |                 |

| Full Scale Output Voltage At Each Pin         |        | 0.5 (1.414) |         | rms(Vpp)  | Single Ended    |

| Output Resistance At Each Pin                 |        | ??          | ??      | Ω         |                 |

| Common Mode Output Volts                      |        | 2.25        |         | V         |                 |

| REFERENCE (Internal)                          |        |             |         |           |                 |

| Absolute Voltage, V <sub>REF</sub>            |        | 1.1         |         | V         |                 |

| V <sub>REF</sub> TC                           |        | TBD         |         | ppm/°C    |                 |

|                                               |        |             |         | rr °      |                 |

| ADCDECIMATIONFILTER                           |        |             |         |           |                 |

| Pass Band                                     |        |             | 0.xxxFs | Hz        |                 |

| Pass Band Ripple                              | c =    |             | ±0.00xx | dB        |                 |

| TransitionBand                                | 0.xxFs |             | 0.xxFs  | Hz        |                 |

| StopBand                                      | 0.xxFs |             |         | Hz        |                 |

| Stop Band Attenuation                         | 70     | -           | _       | dB        |                 |

| Group Delay Group Delay                       | lll/Fs | nnn/Fs      | mmm/Fs  | ms        |                 |

| DACINTERPOLATIONFILTER                        |        |             |         |           |                 |

| Pass Band                                     |        |             | 0.xxxFs | Hz        |                 |

| Pass Band Ripple                              |        |             | ±0.00xx | dB        |                 |

| Transition Band                               | 0.xxFs |             | 0.xxFs  | Hz        |                 |

| Stop Band                                     | 0.xxFs |             | J       | Hz        |                 |

| Stop Band Attenuation                         | 70     |             |         | dB        |                 |

| Group Delay                                   | III/Fs | nnn/Fs      | mmm/Fs  | ms        |                 |

| PR D 03/00                                    |        |             |         |           |                 |

PR D 03/00

|                                       |           | AD74322       | A     |       |                 |

|---------------------------------------|-----------|---------------|-------|-------|-----------------|

| ARAMETER                              | Min       | Тур           | Max   | Units | Test Conditions |

| OGICINPUT                             |           |               |       |       |                 |

| V <sub>INH</sub> , Input High Voltage | DVDD1-0.8 |               | DVDD1 | V     |                 |

| V <sub>INL</sub> , Input Low Voltage  | 0         |               | 0.8   | V     |                 |

| Input Current                         | -10       |               | +10   | μA    |                 |

| Input Capacitance                     |           |               | 10    | pF    |                 |

| OGICOUTPUT                            |           |               |       |       |                 |

| V <sub>OH</sub> , Output High Voltage | DVDD1-0.4 |               | DVDD1 | V     |                 |

| V <sub>OL</sub> , Output Low Voltage  | 0         |               | 0.4   | V     |                 |

| Three-State Leakage Current           | -10       |               | +10   | μA    |                 |

| OWERSUPPLIES                          |           |               |       |       |                 |

| AVDD,DVDD2                            | 2.25      | 2.5           | 2.75  | V     |                 |

| DVDD1                                 | 2.7       | 3.0           | 3.3   | V     |                 |

| OWERCONSUMPTION                       |           |               |       |       |                 |

| AllSectionsOn                         |           |               | TBD   | mA    |                 |

| ADCsOnOnly                            |           |               | TBD   | mA    |                 |

| DACsOnOnly                            |           |               | TBD   | mA    |                 |

| Reference On Only                     |           |               | TBD   | mA 🔨  |                 |

| PowerdownMode                         |           | $\Lambda M A$ | TBD   | μΑ    |                 |

| P                                     | REL       | 14,           | MC    | ,r    |                 |

Pr D 03/00 -4-

#### ORDERING GUIDE

| Model       | Range          | Package |

|-------------|----------------|---------|

| AD74322DAR  | -40 C to +85 C | R-16    |

| AD74322DARU | -40 C to +85 C | RU-16   |

| AD74322AAR  | -40 C to +85 C | R-20    |

| AD74322AARU | -40 C to +85 C | RU-20   |

| AD74322AAR  | -40 C to +85 C | R-24    |

| AD74322AARU | -40 C to +85 C | RU-24   |

#### **CAUTION** -

MARY ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the XX0000 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

|          |   | 1         |

|----------|---|-----------|

| VINN1 1  | • | 24 VOUTN1 |

| VINN2 2  |   | 23 VOUTN2 |

| VINN1 3  |   | 22 VOUTN1 |

| VINP1 4  |   | 21 VOUTP1 |

| REFCAP 5 |   | 20 AVDD   |

| AGND 6   |   | 19 RESET  |

| DGND 7   |   | 18 SDO    |

| DVDD2 8  |   | 17 SDFS   |

| DVDD1 9  |   | 16 SDI    |

| MCLK 10  |   | 15 SCLK   |

| CCLK 11  |   | 14 соит   |

| CIN 12   |   | 13 CLATCH |

|          |   |           |

## PIN FUNCTION DESCRIPTION (SINGLE-ENDED I/O; NO SPI PORT)

| Mnemonic                                                       | I/O | Function                                                                      |

|----------------------------------------------------------------|-----|-------------------------------------------------------------------------------|

| VIN1                                                           | I   | Analog Input - Channel 1                                                      |

| VIN2                                                           | I   | Analog Input - Channel 2                                                      |

| VOUT1                                                          | О   | Analog Output - Channel 1                                                     |

| VOUT2                                                          | О   | Analog Output - Channel 2                                                     |

| REFCAP                                                         | I/O | Internal Reference - Can also be used for connection of an external reference |

| AVDD                                                           |     | Analog Power Supply Connection                                                |

| AGND                                                           |     | Analog Ground/Substrate Connection                                            |

| DVDD1                                                          |     | Digital Power Supply Connection (Interface)                                   |

| DVDD2                                                          |     | Digital Power Supply Connection (Core)                                        |

| DGND                                                           |     | Digital Ground/Substrate Connection                                           |

| MCLK                                                           | I   | External Clock Connection                                                     |

| SDO                                                            | О   | ADC Serial Data Out - DSP Mode                                                |

| SDI                                                            | I   | DAC Serial Data In - DSP Mode                                                 |

| SDFS                                                           | I/O | Serial Data Input Frame Sync - DSP Mode                                       |

| $\overline{R}\overline{E}\overline{S}\overline{E}\overline{T}$ | I   | Powerdown/Reset Input                                                         |

| SCLK                                                           | I/O | Serial Clock - DSP Mode                                                       |

## PIN FUNCTION DESCRIPTION (SINGLE-ENDED I/O WITH SPI PORT)

| Mnemonic | I/O | Function                                                                      |

|----------|-----|-------------------------------------------------------------------------------|

| VIN1     | I   | Analog Input - Channel 1                                                      |

| VIN2     | I   | Analog Input - Channel 2                                                      |

| VOUT1    | О   | Analog Output - Channel 1                                                     |

| VOUT2    | О   | Analog Output - Channel 2                                                     |

| REFCAP   | I/O | Internal Reference - Can also be used for connection of an external reference |

| AVDD     |     | Analog Power Supply Connection                                                |

| AGND     |     | Analog Ground/Substrate Connection                                            |

| DVDD1    |     | Digital Power Supply Connection (Interface)                                   |

| DVDD2    |     | Digital Power Supply Connection (Core)                                        |

| DGND     |     | Digital Ground/Substrate Connection                                           |

| MCLK     | I   | External Clock Connection                                                     |

| CDIN     | I   | Serial Data In on SPI Control Port                                            |

| CDOUT    | О   | Serial Data Out on SPI Control Port                                           |

| CCLK     | I   | Serial Clock on SPI Control Port                                              |

| CLATCH   | I   | Serial Data Latch on SPI Control Port                                         |

| ASDATA   | О   | ADC Serial Data Out - I <sup>2</sup> S                                        |

| DSDATA   | I   | DAC Serial Data In - I <sup>2</sup> S                                         |

| LRCLK/   | I/O | Left/Right Channel Select - I <sup>2</sup> S                                  |

| BCLK     | I/O | Bit Clock - I <sup>2</sup> S                                                  |

| RESET    | I   | Powerdown/Reset Input                                                         |

-6-

### PIN FUNCTION DESCRIPTION (DIFFERENTIAL I/O WITH SPI PORT)

| Mnemonic | I/O | Function                                                                      |  |  |  |  |  |  |  |

|----------|-----|-------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VINP1    | I   | Analog Input - Channel 1 Positive                                             |  |  |  |  |  |  |  |

| VINN1    | I   | Analog Input - Channel 1 Negative                                             |  |  |  |  |  |  |  |

| VINP2    | I   | Analog Input - Channel 2 Positive                                             |  |  |  |  |  |  |  |

| VINN2    | I   | Analog Input - Channel 2 Negative                                             |  |  |  |  |  |  |  |

| VOUTP1   | O   | Analog Output - Channel 1 Positive                                            |  |  |  |  |  |  |  |

| VOUTN1   | O   | Analog Output - Channel 1 Negative                                            |  |  |  |  |  |  |  |

| VOUTP2   | O   | Analog Output - Channel 2 Positive                                            |  |  |  |  |  |  |  |

| VOUTN2   | O   | Analog Output - Channel 2 Negative                                            |  |  |  |  |  |  |  |

| REFCAP   | I/O | Internal Reference - Can also be used for connection of an external reference |  |  |  |  |  |  |  |

| AVDD     |     | Analog Power Supply Connection                                                |  |  |  |  |  |  |  |

| AGND     |     | Analog Ground/Substrate Connection                                            |  |  |  |  |  |  |  |

| DVDD1    |     | Digital Power Supply Connection (Interface)                                   |  |  |  |  |  |  |  |

| DVDD2    |     | Digital Power Supply Connection (Core)                                        |  |  |  |  |  |  |  |

| DGND     |     | Digital Ground/Substrate Connection                                           |  |  |  |  |  |  |  |

| MCLK     | I   | External Clock Connection                                                     |  |  |  |  |  |  |  |

| CDIN     | I   | Serial Data In on SPI Control Port                                            |  |  |  |  |  |  |  |

| CDOUT    | О   | Serial Data Out on SPI Control Port                                           |  |  |  |  |  |  |  |

| CCLK     | I   | Serial Clock on SPI Control Port                                              |  |  |  |  |  |  |  |

| CLATCH   | I   | Serial Data Latch on SPI Control Port                                         |  |  |  |  |  |  |  |

| ASDATA   | O   | ADC Serial Data Out - I <sup>2</sup> S                                        |  |  |  |  |  |  |  |

| DSDATA   | I   | DAC Serial Data In - I <sup>2</sup> S                                         |  |  |  |  |  |  |  |

| LRCLK/   | I/O | Left/Right Channel Select - I <sup>2</sup> S                                  |  |  |  |  |  |  |  |

| BCLK     | I/O | Bit Clock - I <sup>2</sup> S                                                  |  |  |  |  |  |  |  |

| RESET    | I   | Powerdown/Reset Input                                                         |  |  |  |  |  |  |  |

|          |     |                                                                               |  |  |  |  |  |  |  |

Pr D 03/00 -7-

## AD74322

#### **FUNCTIONAL DESCRIPTION**

#### **ADCSection**

There are two ADC channels in the AD74322, configured as a stereo pair. Each ADC channel can be independently muted. The input pins are switched between differential inputs or four single ended inputs accordingly. The gain block can be programmed for independent left and right gains, in steps of +3dB, from 0dB to +12dB. The ADC operates at an oversampling ratio of 128 and the decimation filter reduces the output to the standard sample rates. The output maximum sample rate is 96 kHz at ASDATA.

#### Automatic Level Control

#### Analog Sigma Delta Modulator

#### **Decimator Section**

The digital decimation filter has a passband ripple of  $\pm 0.01 dB$  and a stopband attenuation of 70dB. The filter is an FIR type with a linear phase response. The group delay at 48kHz is ??us. Output sample rates up to 96 kHz are supported.

#### InputSignalswing

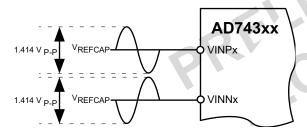

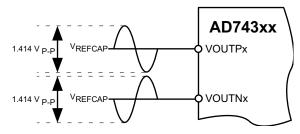

Each ADC input has an input range of  $0.5\,V_{RMS}/1.414\,V_{P-P}$  (Single-Ended) about a bias point equal to  $V_{REFCAP}$  (See Figure <Input\_Swing>)

Figure < Input\_Swing>

#### **DACSection**

The AD74322 has two DAC channels arranged as a stereo pair, with two, fully differential voltage, analog outputs for improved noise and distortion performance. Each channel has it's own independently programmable attenuator with a maximum attenuation of 63dB, adjustable in 1dB steps. Digital inputs are via a serial data input pin and a common frame (DLRCLK) and bit (DBLCK) clock or using a 'packed data' mode, both channels can be input using a single data pin.

#### Interpolator Section

#### DigitalSigmaDeltaModulator

#### DAC

#### Analog Output Filter

#### **Output Signalswing**

Each ADC input has an output range of  $0.5\,V_{RMS}/1.414\,V_{P-P}$  (Single-Ended) about a bias point equal to  $V_{REFCAP}$  (See Figure <Output\_Swing>)

Figure < Output\_Swing>

## PRELIMINARY TECHNICAL DATA

#### Reference

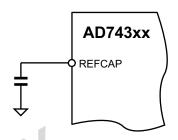

The AD74322 features an on-chip reference whose nominal value is 1.125 V.A \_\_ nF capacitor applied at the REFCAP pin is necessary to stabilise the reference. (See Figure <REFCAP\_Int>)

Figure < REFCAP\_Int>

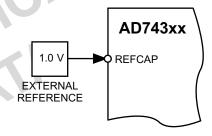

If it is required to use an external reference, because of its value or its reference tempco, the internal reference can be disabled via Control Register \_\_and the external reference applied at the REFCAP pin (See Figure < REFCAP\_Ext>).

Figure < REFCAP\_Ext>

#### **Master Clocking Scheme**

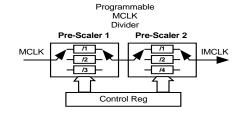

The update rate of the AD74322's ADC and DAC channels require an internal master clock (IMCLK) which is 256 times that sample update rate (IMCLK =  $256 * F_S$ ). In order to provide some flexibility in selecting sample rates, the device has a series of three master clock pre-scalers which are programmable and allow the user to choose a range of convenient sample rates from a single external master clock. The master clock signal to the AD74322 is applied at the MCLK pin. The MCLK signal is passed through a series of two programmable MCLK pre-scalers (divider) circuits which can be selected to reduce the resulting Internal MCLK (IMCLK) frequency if required. The first MCLK prescaler provides divider ratios of /1 (pass through), /2, /3 while the second pre-scaler provides divider ratios of ./1 (pass through), /2, /4 and the third pre-scaler provides ratios of /1 (pass through), /2 and /5...

Figure < PSU\_Connection:

#### Figure < MCLK\_Divider >

The divider ratios will allow more convenient sample rate selection from a common MCLK which may be required in many voice related applications.

## Example 1: $f_{SAMP} = 48 \text{ kHz}$ and 8 kHz required

MCLK =  $48*10^3 * 256 = 12.288$  MHz to cater for 48 kHz  $f_{SAMP}$

For  $f_{SAMP}=8$  kHz, it is necessary to use the /3 setting in Pre-Scaler 1, the /2 setting in Pre-Scaler 2 and pass through in Pre-Scaler 3. This results in an IMCLK =  $8*10^3*256=2.048$  MHz (= 12.288 MHz/6).

## Example 2: $f_{SAMP} = 48$ kHz and 32 kHz required

MCLK = 24.576 MHz

For  $f_{SAMP}=48$  kHz, it is necessary to use the /2 setting in Pre-Scaler 1 and the /1 (pass-through) setting in Pre-Scaler 2 and pass through in Pre-Scaler 3. This results in an IMCLK =  $48*10^3*256=12.288$  MHz.

For  $f_{SAMP}=32$  kHz, it is necessary to use the /3 setting in Pre-Scaler 1 and the /1 (pass-through) setting in Pre-Scaler 2 and pass through in Pre-Scaler 3. This results in an IMCLK =  $32*10^3*256=8.192$  MHz.

#### Example 3: fSAMP = 44.1 kHz and 11.025 kHz required

MCLK =  $44.1*10^3 * 256 = 11.2896$  MHz to cater for 44.1 kHz  $f_{SAMP}$

For  $f_{SAMP}$  = 11.025 kHz, it is necessary to use the /1 setting in Pre-Scaler 1 and the /4 setting in Pre-Scaler 2 and pass through in Pre-Scaler 3. This results in an IMCLK =  $11.025*10^3*256 = 2.8224$  MHz (= 11.2896 MHz/4).

#### **Sample Rates**

For all applications the sampling rate is defined by the internal master clock frequency (IMCLK) where IMCLK =  $256*f_{SAMP}$ .

#### Power-On Reset

The AD74322 features a power-on reset circuit which  $^{-9}$  ensures that all internal circuitry is reset and initialised to

a known state following the power-up of the device. There is also a software reset capability available by setting the RESET bit in Control Register \_. This control register is accessed through the Control Port.

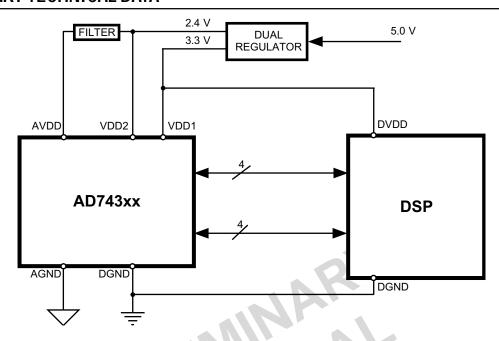

#### **Power Supplies and Grounds**

The AD74322 features three separate supplies: AVDD, DVDD1 and DVDD2.

AVDD is the supply to the analog section of the device and must therefore be of sufficient quality to preserve the AD74322's performance characteristics. It is nominally a 2.4 V supply.

DVDD1 is the supply for the digital interface section of the device. It is fed from the digital supply voltage of the DSP or controller to which the device is interfaced and allows the AD74322 to interface with devices operating at supplies of between 2.4~V -5% to 3.3~V + 10%.

DVDD2 is the supply for the digital core of the AD74322. It is nominally a 2.4 V supply.

| MCLK   |                                     | Sampling Rates (kHz) using Scalar (Divider) Ratios (assumes 256fs) |    |    |   |    |    |   |    |    |    |  |  |  |  |  |

|--------|-------------------------------------|--------------------------------------------------------------------|----|----|---|----|----|---|----|----|----|--|--|--|--|--|

| (MHz)  | 1                                   | 2                                                                  | 3  | 4  | 5 | 6  | 8  | 9 | 10 | 12 | 15 |  |  |  |  |  |

| 2.048  | 8                                   | 4                                                                  | -  | 2  | - | -  | 1  | - | -  | -  | -  |  |  |  |  |  |

| 12.288 | 48                                  | 24                                                                 | -  | 12 | - | -  | 6  | - | -  | -  | -  |  |  |  |  |  |

| 16.384 | 64                                  | 32                                                                 | -  | 16 | - | -  | 8  |   | -  | -  | -  |  |  |  |  |  |

| 24.576 | 96                                  | 48                                                                 | -  | 24 | - | -  | 12 |   | -  | -  | -  |  |  |  |  |  |

| 36.864 | -                                   | -                                                                  | 48 | -  | - | 24 |    | 1 | -  | 12 | -  |  |  |  |  |  |

|        | Table <mclk_divider></mclk_divider> |                                                                    |    |    |   |    |    |   |    |    |    |  |  |  |  |  |

| Sampling Rate        | Interpolator<br>Mode       | MCLK (MHz)               |                   |                          |  |  |  |  |

|----------------------|----------------------------|--------------------------|-------------------|--------------------------|--|--|--|--|

| f <sub>s</sub> (kHz) |                            | <b>256f</b> <sub>s</sub> | 512f <sub>s</sub> | <b>768f</b> <sub>s</sub> |  |  |  |  |

| 8<br>16              | 8x (Normal)<br>4x (Double) | 2.048                    | 4.096             | 6.144                    |  |  |  |  |

| 11.1<br>22.2         | 8x (Normal)<br>4x (Double) | 2.8224                   | 5.6448            | 8.4672                   |  |  |  |  |

| 32<br>64             | 8x (Normal)<br>4x (Double) | 8.192                    | 16.384            | 24.576                   |  |  |  |  |

| 44.1<br>88.2         | 8x (Normal)<br>4x (Double) | 11.2896                  | 22.5792           | 33.8688                  |  |  |  |  |

| 48<br>96             | 8x (Normal)<br>4x (Double) | 12.288                   | 24.576            | 36.864                   |  |  |  |  |

Table <MCLK\_Select>

#### INTERFACING

The AD74322 features two separate interfaces, Control and Data, which are used to program control settings and send/receive sample data respectively. The Control interface is implemented using an SPI® type protocol but transfers 16-bits per frame. The Data interface uses either a DSP or  $1^2 S$ ® protocol to transfer stereo data samples between controller and codec. The DSP compatible interface mode allows data samples to be transferred in a protocol that is supported by the serial interfaces of most fixed-and floating-point DSPs.

In order to reduce peripheral requirements when interfacing the AD74322 with the host DSP, the DSP mode allows the DSP to send both data and control information to the device via the data interface. This is the default mode and requires users to only use a single DSP SPORT to both control the device and service it with data samples.

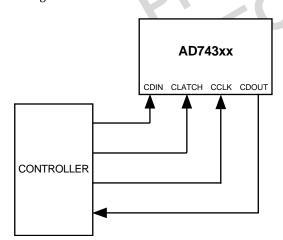

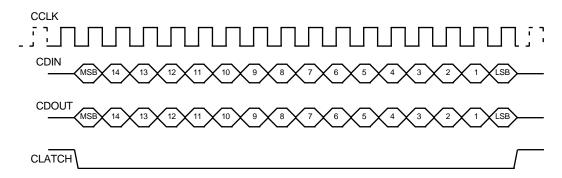

#### **ControlInterface**

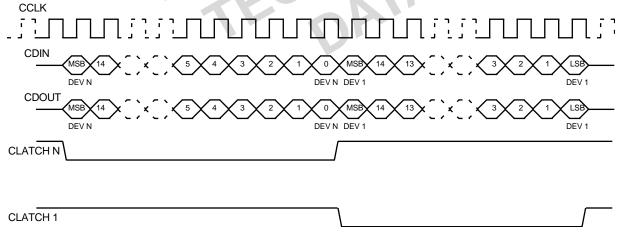

$Control \ of the \ AD74322 \ operation is \ via a set of 16 \ Control \ Registers \ which are programmed through the \ Control \ Port. The \ Control \ Port \ protocol is similar to the \ SPIO \ protocol \ with the exception that 16-bits of data are transferred per frame. The \ Control \ Port \ consists of the following pins: \ CCLK-Control \ Port \ Serial \ Clock, \ CLATCH-Control \ Port \ Latch or \ Frame \ signal, \ CDIN-Control \ Port \ Serial \ Data \ In \ and \ CDOUT-Control \ Port \ Data \ Out. \ CLATCH \ is a framing \ signal \ that \ is \ active \ low. \ When \ asserted, \ it \ gates \ the \ other \ interface \ lines \ as \ being \ active. \ CCLK \ is used \ to \ clock \ input \ data \ on \ CDIN \ and \ clock \ output \ (readback) \ data \ on \ CDOUT. \ Figure < Control\_Interface > \ details \ the \ connectivity \ of \ the \ Control \ Port \ to \ a \ controller \ and \ Figure < Control\_Timing > \ details \ the \ interface \ timing.$

Figure < Control\_Interface>

Data in and out of the Control Port go through a 16-bit shift register whose contents are mapped to the internal registers using the mapping scheme of Figure <ContPortMap>. A 16-bit word received by the Control Port is decoded as a read or write to a register address set by bits 15 - 12. This 4-bit register address selects 1 of 16 registers as shown in Table <ContRegMap>. Bit 11 selects whether a register read or write is requested - Write = 0, Read = 1. Bit-10 is reserved. Bits 9 through 0 contain register data. Each Control register's contents are detailed below.

#### **DataInterface**

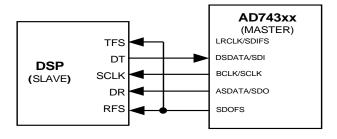

There are two modes of operation of the data interface: DSP mode and I2S mode. The default mode of the data interface is a DSP mode which combines control and data functions in a single protocol. This is to reduce the peripheral overhead required on the DSP when interfacing to the AD74322. This mode operates in a standard DSP serial format. In I2S mode the data interface streams audio data samples being sent to or received from the DACs and ADCs respectively, using the I2S serial protocol.

In either mode it can be configured as either a master or slave device ensuring connectivity to the largest number of host processors.

#### **DSPMode**

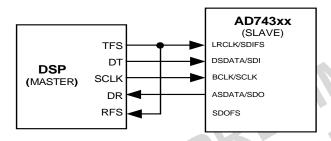

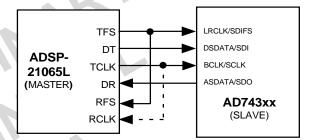

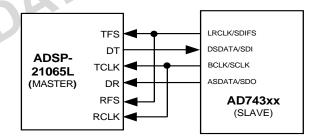

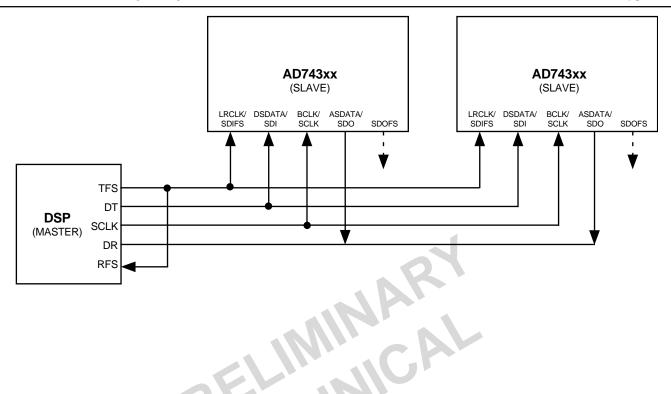

The DSP mode allows interfacing to most fixed- and floating-point DSPs as well as other processors such as RISCs etc that having serial ports that support synchronous communications. The key feature of synchronous DSP communications is that the serial data is framed by a separate Frame Syncsignal. Figures < Data\_DSP\_Slave > and < Data\_DSP\_Master > detail connectivity in Master Mode (codec is master) and Slave Mode (codec is slave) respectively.

Figure < Data\_DSP\_Slave >

Figure < Control\_Timing>

Figure < DSP\_Protocol>

Figure < Data\_DSP\_Master>

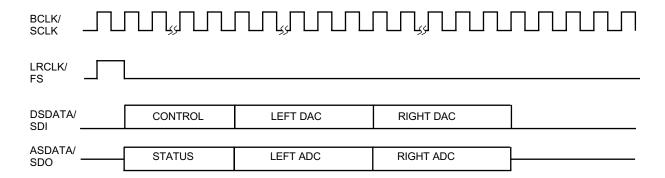

The serial protocol uses a fixed position for data being sent to or received from the Left and Right DACs and ADCs respectively and the control words being sent to and the status words being received from the device respectively. Figure <DSP\_Protocol> details the arrangement of both audio and control/status information in the serial transfer.

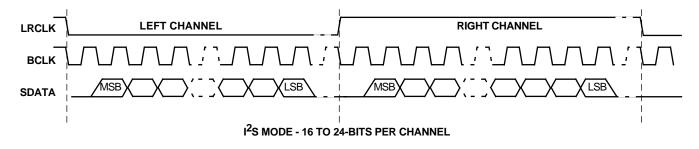

#### **FS® (InterICSoundBus) Mode**

The I2S bus is a three line serial bus which features a serial data line carrying both left and right (stereo) channels. The Left and Right channel information are selected by the status of the Left/Right Clock (Word Select) line. Serial data is clocked by the Bit Clock line. Figures < Data\_I2S\_DSP\_Master> and < Data\_I2S\_DSP\_Slave> detail the interface configuration between controller and codec in  $\rm I^2S$  mode with controller as master and slave respectively. Figure < > details  $\rm I^2S$  timing. The interface allows easy transfer of arbitrary length serial data samples sent MSB first. Toggling of the Left/Right Clock line indicates that the end of the current word will occur after the following Bit Clock cycle and the start of the alternate channel word will occur on the subsequent Bit Clock cycle

Figure < Data\_I2S\_DSP\_Master>

Figure < Data\_I2S\_DSP\_Slave >

Figure < I2S\_Timing>

Figure < Control\_Cascade\_Daisy\_Chain>

Figure < Control\_Cascade\_Timing\_Daisy\_Chain>

#### INTERFACING MULTIPLE DEVICES

Many applications require multiple channels of input and output. The AD743xx series of devices are designed to cater for extending the number of I/O channels by cascading devices together while interfacing to a single control or data port. This reduces the overhead requirement on the controller in terms of serial ports.

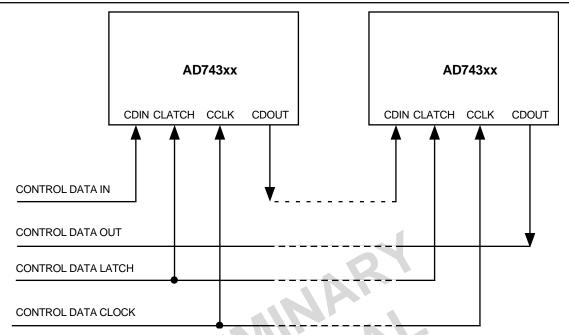

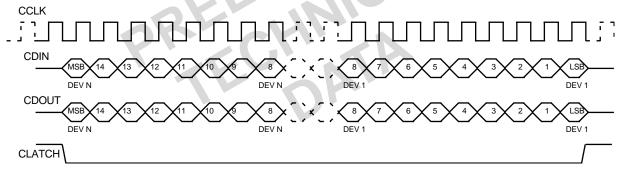

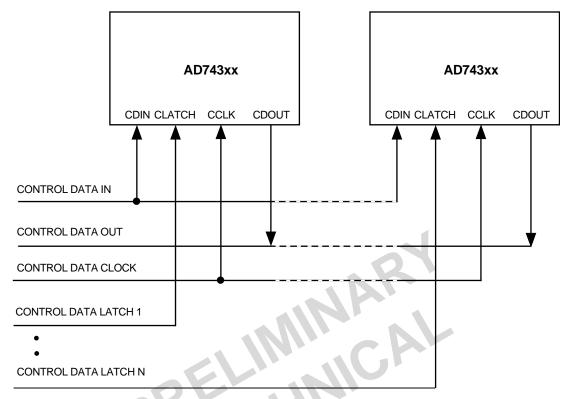

### **ControlPortCascading**

There are two methods of cascading the Control Ports of multiple AD743xx devices together so that all devices can be controlled from a single controller serial port. One method is to configure the multiple devices as a daisy chain of Control Ports each 16-bits wide with common

Pr D 03/00 -13-

Figure < Control\_Cascade\_TDM>

Figure < Control\_Cascade\_Timing\_TDM>

Clock and Latch signals. The other method involves creating a common Data In and Data Out buses where each device has a common Clock but has separate Latch signals which enable the devices on the bus at different times - either as a Time Division Multiplex (TDM) or software control.

#### **DaisyChainMode**

In Daisy Chain Mode, the serial registers (16-bit) of each device are cascaded together by connecting the controller's Data Out to CDIN of the first device and the CDOUT of the first device to CDIN of the next device (see Figure

<Control\_Cascade\_Daisy\_Chain>). The CDOUT of the final device is connected to the controller's Data In. The effective cascade length becomes 16 \* N (where N is the number of devices in cascade) and each control word write to each device requires 16 \* N CCLK cycles. Please note that the CLATCH pin of each device is driven from a common controller output signal which must be active during the entire 16 \* N CCLK cycles as shown in Figure <Control\_Cascade\_Timing\_Daisy\_Chain>.

#### **TDMMode**

$In TDM Mode, each device's CDIN and CDOUT are commoned to the controller's Data Out and Data In respectively (see Figure < Control\_Cascade\_TDM>). Each device's CLATCH pin is separately controlled. When CLATCH is disasserted activity on CDIN and CCLK is not recognised and the CDOUT pin is tri-stated. Figure < Control\_Cascade\_Timing\_TDM> shows TDM Mode Control timing.}$

#### **Data Port Cascading**

The Data Port of the AD74322 is designed to allow multiple single or dual channel devices to be cascaded from a single DSP or controller serial port (SPORT). There is also a mode which allows stereo ADCs and

DACs (with I2S interfaces) to be interfaced to a cascade of AD743xx devices. This allows extra flexibility in choosing the number of input and out channels in the cascade. The various (potential) modes for interfacing the data ports of multiple devices are listed below:

#### DSP Mode - Daisy Chaining

In this mode, sample data is passed along a daisychain of I/O registers in a similar manner that used in the present AD733xx devices. At the sample event each ADC result is placed in the I/O register and is subsequently shifted towards the DSP's Rx register. This achieved by a common SDIFS pulse which samples each device (enables each device's sample). {Drawback: as the device is stereo, we would need to send 32 bits (or perhaps more) to the I/O register at each sample event.}

#### *TDMMode*

In multiplexed mode, each device is programmed with its cascade position. This allows devices to be enabled to the data buses only in their appropriate time-slot as defined by the initial frame-sync signal.

Pr D 03/00 -15-

## PRELIMINARY TECHNICAL DATA

| REG | ISTER | ADDR | RESS | R/W | RES | DATA FIELD |   |   |   |   |   |   |   |   |   |

|-----|-------|------|------|-----|-----|------------|---|---|---|---|---|---|---|---|---|

| 15  | 14    | 13   | 12   | 11  | 10  | 9          | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Note: Bit 15 = MSB

Figure < ContPortMap>

| REG | ISTER | ADDI | RESS | R/W | RES |                            |                     |   |    | DATA     | FIELD    | )    |   |   |   |  |

|-----|-------|------|------|-----|-----|----------------------------|---------------------|---|----|----------|----------|------|---|---|---|--|

| 15  | 14    | 13   | 12   | 11  | 10  | 9                          | 8                   | 7 | 6  | 5        | 4        | 3    | 2 | 1 | 0 |  |

| 0   | 0     | 0    | 0    |     |     |                            |                     |   | ]  | Power    | Setting  | S    |   |   |   |  |

| 0   | 0     | 0    | 1    |     |     |                            |                     |   | (  | Clock    | Divider  | s    |   |   |   |  |

| 0   | 0     | 1    | 0    |     |     |                            | Serial Port Control |   |    |          |          |      |   |   |   |  |

| 0   | 0     | 1    | 1    |     |     | Mute Control               |                     |   |    |          |          |      |   |   |   |  |

| 0   | 1     | 0    | 0    |     |     | Input/Output Configuration |                     |   |    |          |          |      |   |   |   |  |

| 0   | 1     | 0    | 1    | 0   |     |                            | ADC0 Gain Setting   |   |    |          |          |      |   |   |   |  |

| 0   | 1     | 0    | 1    | 1   |     |                            | ADC0 Peak Level     |   |    |          |          |      |   |   |   |  |

| 0   | 1     | 1    | 0    | 0   |     | ADC1 Gain Setting          |                     |   |    |          |          |      |   |   |   |  |

| 0   | 1     | 1    | 0    | 1   |     |                            |                     |   | Al | DC1 P    | eak Le   | vel  |   |   |   |  |

| 0   | 1     | 1    | 1    |     | 1   |                            |                     |   |    | Rese     | erved    |      |   |   |   |  |

| 1   | 0     | 0    | 0    |     |     |                            |                     | V |    | Rese     | erved    |      |   |   |   |  |

| 1   | 0     | 0    | 1    |     |     |                            |                     |   | I  | /O Filte | er Selec | ct   |   |   |   |  |

| 1   | 0     | 1    | 0    |     |     |                            |                     |   | DA | AC0 G    | ain Sett | ting |   |   |   |  |

| 1   | 0     | 1    | 1    |     |     |                            |                     |   | DA | AC1 G    | ain Sett | ting |   |   |   |  |

| 1   | 1     | 0    | 0    |     |     |                            |                     |   |    | Rese     | erved    |      |   |   |   |  |

| 1   | 1     | 0    | 1    |     |     |                            | Reserved            |   |    |          |          |      |   |   |   |  |

| 1   | 1     | 1    | 0    |     |     |                            | REF Trim Control    |   |    |          |          |      |   |   |   |  |

| 1   | 1     | 1    | 1    |     |     |                            |                     |   | Те | st Mod   | le Con   | trol |   |   |   |  |

Figure < ContRegMap >

-16-

| REG<br>ADDRESS | R/W  | RES | Power Control     |                                                 |                               |                     |                     |                     |                     |                     |                     |                       |  |

|----------------|------|-----|-------------------|-------------------------------------------------|-------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-----------------------|--|

|                | N/ W |     | RESET             | PURA                                            | PUR                           | PUD1                | PUD0                | PUA3                | PUA2                | PUA1                | PUA0                | PU                    |  |

| 15 - 12        | 11   | 10  | 9                 | 8                                               | 7                             | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                     |  |

| 0000           |      |     | Software<br>Reset | Power<br>Up<br>Referen-<br>ce<br>Amplifi-<br>er | Power<br>Up<br>Referen-<br>ce | Power<br>Up<br>DAC1 | Power<br>Up<br>DAC0 | Power<br>Up<br>ADC3 | Power<br>Up<br>ADC2 | Power<br>Up<br>ADC1 | Power<br>Up<br>ADC0 | Global<br>Power<br>Up |  |

### Table < MCLK\_Divider >

| REG     | R/W    | RES | Clock Dividers |      |       |   |   |               |     |        |              |       |  |

|---------|--------|-----|----------------|------|-------|---|---|---------------|-----|--------|--------------|-------|--|

| ADDRESS | I K/ W | KES |                | Rese | erved |   |   | BCD2-0        |     | MCD2-0 |              |       |  |

| 15 - 12 | 11     | 10  | 9              | 8    | 7     | 6 | 5 | 4             | 3   | 2      | 1            | 0     |  |

| 0000    |        |     |                | 25   |       |   | В | it Clock Divi | der | Mas    | ter Clock Di | vider |  |

|         |        |     | 8              | 1    | EG.   | 0 | M | P             |     |        |              |       |  |

| REG DAY |     |     |                       |                              |                              | Ser                          | ial Inter               | face Con                | trol                    |                         |                         |                          |

|---------|-----|-----|-----------------------|------------------------------|------------------------------|------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|

| ADDRESS | R/W | RES | DSTD-<br>ME           | TPOS2                        | TPOS1                        | TPOS0                        | DDF1                    | DDF0                    | ADF1                    | ADF0                    | DSMM                    | DSMS                     |

| 15 - 12 | 11  | 10  | 9                     | 8                            | 7                            | 6                            | 5                       | 4                       | 3                       | 2                       | 1                       | 0                        |

| 0000    |     |     | TDM<br>Mode<br>Enable | TDM<br>Mode<br>Position<br>2 | TDM<br>Mode<br>Position<br>1 | TDM<br>Mode<br>Position<br>0 | DAC<br>Data<br>Format 2 | DAC<br>Data<br>Format 2 | ADC<br>Data<br>Format 2 | ADC<br>Data<br>Format 1 | Mixed<br>Mode<br>Enable | Master/<br>Slave<br>Mode |

| REG P/W | DEC |     | Mute Control           |                        |                        |                        |               |               |          |          |               |               |  |  |

|---------|-----|-----|------------------------|------------------------|------------------------|------------------------|---------------|---------------|----------|----------|---------------|---------------|--|--|

| ADDRESS | R/W | RES | DWW1                   | DWW0                   | AWW1                   | AWW0                   | DMU-<br>TE1   | DMU-<br>TE0   | -        | 1        | AMU-<br>TE1   | AMU-<br>TE0   |  |  |

| 15 - 12 | 11  | 10  | 9                      | 8                      | 7                      | 6                      | 5             | 4             | 3        | 2        | 1             | 0             |  |  |

| 0000    |     |     | DAC<br>Word<br>Width 1 | DAC<br>Word<br>Width 0 | ADC<br>Word<br>Width 1 | ADC<br>Word<br>Width 0 | Mute<br>DAC 1 | Mute<br>DAC 0 | Reserved | Reserved | Mute<br>ADC 1 | Mute<br>ADC 0 |  |  |

Pr D 03/00 -17-

| DEG     | REG DAY | DEG |                                 |          |                     | A                         | ADC Cor                   | nfiguration               |                          |                          |                                    |                                    |

|---------|---------|-----|---------------------------------|----------|---------------------|---------------------------|---------------------------|---------------------------|--------------------------|--------------------------|------------------------------------|------------------------------------|

| ADDRESS | R/W     | RES | PEA-<br>KE                      | RES      | DLB                 | DSLB                      | ALB1                      | ALB0                      | INV1                     | INV0                     | SEE1                               | SEE0                               |

| 15 - 12 | 11      | 10  | 9                               | 8        | 7                   | 6                         | 5                         | 4                         | 3                        | 2                        | 1                                  | 0                                  |

| 0111    |         |     | ADC<br>Peak<br>Level<br>Reading | Reserved | Digital<br>Loopback | Data<br>SPORT<br>Loopback | Analog<br>Loopback<br>Ch1 | Analog<br>Loopback<br>Ch0 | Invert<br>ADC1<br>Inputs | Invert<br>ADC0<br>Inputs | ADC1 in<br>Single<br>Ended<br>Mode | ADC0 in<br>Single<br>Ended<br>Mode |

| REG     | R/W | RES |      | ADC0 Gain Setting/Peak Readback |  |  |  |  |  |  |  |  |  |  |  |

|---------|-----|-----|------|---------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| ADDRESS | K/W | KES |      | A0G9-0                          |  |  |  |  |  |  |  |  |  |  |  |

| 15 - 12 | 11  | 10  | 9    | 8 7 6 5 4 3 2 1 0               |  |  |  |  |  |  |  |  |  |  |  |

| 0001    | 0   |     |      | Reserved A0G1 A0G0              |  |  |  |  |  |  |  |  |  |  |  |

|         | 1   |     | A0P9 | ADC0 Peak Readback A0P0         |  |  |  |  |  |  |  |  |  |  |  |

| REG     | R/W | RES |      | ADC1 Gain Setting/Peak Readback |  |  |  |  |  |  |  |  |  |  |  |

|---------|-----|-----|------|---------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| ADDRESS | K/W | KES |      | A1G9-0                          |  |  |  |  |  |  |  |  |  |  |  |

| 15 - 12 | 11  | 10  | 9    | 8 7 6 5 4 3 2 1 0               |  |  |  |  |  |  |  |  |  |  |  |

| 0001    | 0   |     |      | Reserved A1G1 A1G0              |  |  |  |  |  |  |  |  |  |  |  |

|         | 1   |     | A1P9 | 9 ADC1 Peak Readback A0P0       |  |  |  |  |  |  |  |  |  |  |  |

| REG<br>ADDRESS | R/W   | RES |      |                           |   | D | AC0 Ga | in Settir | ng |   |   |   |  |  |

|----------------|-------|-----|------|---------------------------|---|---|--------|-----------|----|---|---|---|--|--|

| ADDRESS        | IN/ W | KES |      | D0G9-0                    |   |   |        |           |    |   |   |   |  |  |

| 15 - 12        | 11    | 10  | 9    | 8                         | 7 | 6 | 5      | 4         | 3  | 2 | 1 | 0 |  |  |

| 0101           |       |     | D0G9 | G9 DAC0 Gain Setting D0G0 |   |   |        |           |    |   |   |   |  |  |

## PRELIMINARY TECHNICAL DATA

AD74322

| REG<br>ADDRESS | R/W   | RES |      |                           |   | Г | AC1 Ga | in Settin | ng |   |   |   |  |  |

|----------------|-------|-----|------|---------------------------|---|---|--------|-----------|----|---|---|---|--|--|

| ADDRESS        | IV. W | KES |      | D1G9-0                    |   |   |        |           |    |   |   |   |  |  |

| 15 - 12        | 11    | 10  | 9    | 8                         | 7 | 6 | 5      | 4         | 3  | 2 | 1 | 0 |  |  |

| 0110           |       |     | D1G9 | G9 DAC1 Gain Setting D1G0 |   |   |        |           |    |   |   |   |  |  |

| REG     | R/W  | RES |                        | Trim Control           |   |      |        |         |       |   |   |   |  |

|---------|------|-----|------------------------|------------------------|---|------|--------|---------|-------|---|---|---|--|

| ADDRESS | N/ W | KES | BMF                    | LTE                    |   | LT:  | 3-0    |         | ST3-0 |   |   |   |  |

| 15 - 12 | 11   | 10  | 9                      | 8                      | 7 | 6    | 5      | 4       | 3     | 2 | 1 | 0 |  |

| 0000    |      |     | Blow<br>Master<br>Fuse | Link<br>Trim<br>Enable |   | Link | Softwa | re Trim |       |   |   |   |  |

|         |      |     | P                      | 7                      | C | HIN  | N      | A       |       |   |   |   |  |

| REG<br>ADDRESS | R/W  | RES |          | Test Mode Control                                          |  |  |  |  |  |  |  |   |  |

|----------------|------|-----|----------|------------------------------------------------------------|--|--|--|--|--|--|--|---|--|

| ADDRESS        | IV W | KES | TMI      | TME1-0 DI3-0 AI3-0                                         |  |  |  |  |  |  |  |   |  |

| 15 - 12        | 11   | 10  | 9        | 8 7 6 5 4 3 2 1 0                                          |  |  |  |  |  |  |  | 0 |  |

| 0000           |      |     | Test Mod | est Mode Control DAC Current Settings ADC Current Settings |  |  |  |  |  |  |  |   |  |

Pr D 03/00 -19-

PRINTED IN U.S.A.

#### **OUTLINE DIMENSIONS (STYLE: outline hd)**

Dimensions shown in inches and (mm). (STYLE: outline sub)

-20-