# μPD485505 Line Buffer for Communications Systems

# **Preliminary Information**

August 1992

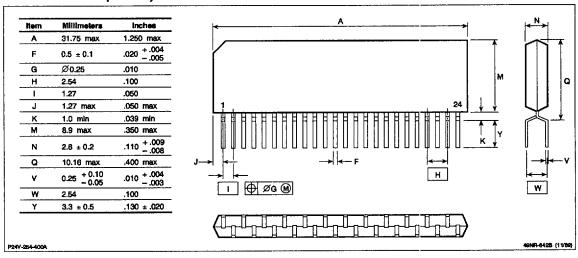

# N E C ELECTRONICS INC Pin Configurations

PSE D

#### Description

The  $\mu$ PD485505 is a 5048-word by 8-bit dual-port line buffer fabricated with a silicon-gate CMOS process. The device is capable of asynchronous read and write operation at high speed and can be used as a time axis converter or a digital delay line of up to 5048 bits (21 bits minimum at maximum frequency).

Applications include image processing in facsimile machines, plain paper copiers, video systems, and other optical scanners; time base correction in video playback systems; and data communication buffering in multiprocessor systems and local area networks.

#### **Features**

- □ 5048-word x 8-bit organization

- Fully static operation

- □ Dual-port operation

- Image processing and data communications applications

- Asynchronous and simultaneous reading/writing

- □ 1H (5048-bit) delay line capability

- TTL-compatible inputs and outputs

- □ Three-state outputs

- □ Single +5-volt power supply

- 24-pin plastic SOP and 24-pin plastic ZIP packaging

#### **Ordering Information**

| Part No.       | Cycle Time<br>(min) |       |                |  |

|----------------|---------------------|-------|----------------|--|

| μPD485505GU-25 | 25 ns               | 18 ns | 24-pin plastic |  |

| GU-35          | 35 ns               | 25 ns | SOP            |  |

| μPD485505V-25  | 25 ns               | 18 ns | 24-pin plastic |  |

| V-35           | 35 ns               | 25 ns | ZIP            |  |

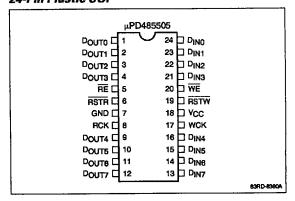

#### 24-Pin Plastic SOP

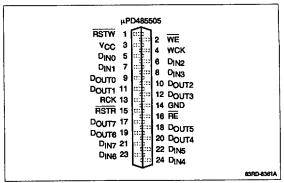

#### 24-Pin Plastic ZIP

#### Pin Identification

| Symbol                              | Function                  |  |  |  |  |

|-------------------------------------|---------------------------|--|--|--|--|

| D <sub>INO</sub> - D <sub>IN7</sub> | Write data inputs         |  |  |  |  |

| Doute - Doute                       | Read data outputs         |  |  |  |  |

| RCK                                 | Read clock input          |  |  |  |  |

| RE                                  | Read enable input         |  |  |  |  |

| RSTR                                | Read address reset input  |  |  |  |  |

| RSTW                                | Write address reset input |  |  |  |  |

| WCK                                 | Write clock input         |  |  |  |  |

| WE                                  | Write enable input        |  |  |  |  |

| GND                                 | Ground                    |  |  |  |  |

| Vcc                                 | +5-volt power supply      |  |  |  |  |

#### **µPD485505**

# NEC

#### N E C ELECTRONICS INC

P5E D

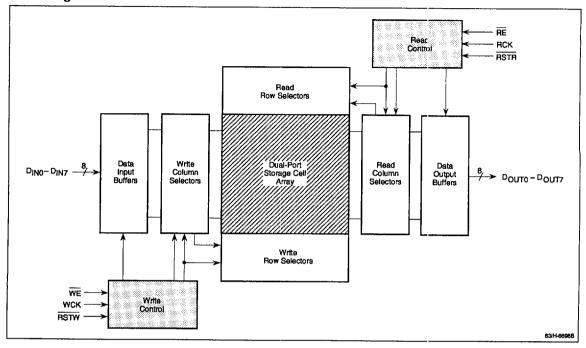

#### **Block Diagram**

#### Pin Functions

$\textbf{D}_{\textbf{IN0}}$  -  $\textbf{D}_{\textbf{IN7}}$  (Data Inputs). New data is entered on these pins.

**D**<sub>OUTO</sub> - **D**<sub>OUT7</sub> (**Data Outputs**). These three-state outputs are used to access stored information. In a simple digital delay line application, a minimum delay of 21 clock cycles is required to move data from the input pins to the output pins.

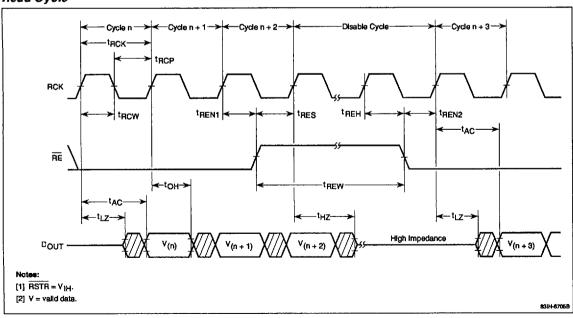

RCK (Read Clock Input). All read cycle are executed synchronously with RCK. The states of both RSTR and RE are latched by the rising edge of RCK at the beginning of a cycle. This same edge of RCK starts internal read operation, and access time is referenced to this edge.

The internal read address increments with each RCK cycle unless  $\overline{\text{RE}}$  is high to hold the read address constant. Unless inhibited by  $\overline{\text{RE}}$ , the internal read address will automatically wrap around from 5047 to 0 and begin incrementing again.

RE (Read Enable Input). This signal controls read operation. If RE is low, all read cycles proceed. If RE is at a high level, the data outputs remain valid for that

address and the internal read address stops incrementing. The state of  $\overline{\text{RE}}$  is strobed by the rising edge of RCK.

RSTR (Read Address Reset Input). This signal is strobed by the rising edge of RCK and resets the internal read address to 0.

RSTW (Write Address Reset Input). Bringing this signal low resets the internal write address to 0. The state of this input is strobed by the rising edge of WCK.

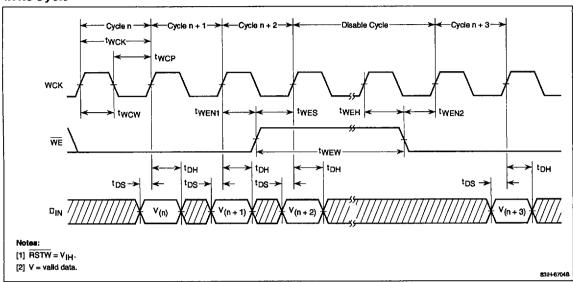

WCK (Write Clock Input). All write cycles are executed synchronously with WCK. The states of both RSTW and WE are strobed by the rising edge of WCK at the beginning of a cycle, and the data inputs are strobed by the rising edge of WCK at the end of a cycle.

The internal write address increments with each WCK cycle unless  $\overline{\text{WE}}$  is at a high level to hold the write address constant. Unless inhibited by  $\overline{\text{WE}}$ , the internal write address will automatically wrap around from 5047 to 0 and begin incrementing again.

WE (Write Enable Input) This input is similar to RE but controls write operation. If WE is at a high level, no data is written to storage cells and the write address does not increment. The state of WE is strobed by the rising edge of WCK.

#### Operation

Reset Cycle. The  $\mu$ PD485505 requires the initialization of internal circuits using the  $\overline{\text{RSTW}}/\overline{\text{RSTR}}$  reset signals before starting operation as a time axis converter or a digital delay line.

A reset cycle can be executed at any time and does not depend on the state of  $\overline{\text{RE}}$  or  $\overline{\text{WE}}$ . However,  $\overline{\text{RSTW}}$  and  $\overline{\text{RSTR}}$  must satisfy required setup and hold times as measured from the rising edges of WCK and RCK.

Write/Read Cycles. Write and read cycles are synchronized to their respective WCK/RCK inputs and executed individually when WCK or RCK is high and  $\overline{\text{WE}}$  or RE is low. Write data must satisfy setup and hold times as specified from the rising edge of WCK. New data written to a particular address is available for reading after one-half write cycle plus 500 ns (maximum).

The access time of a read cycle is measured from the rising edge of RCK by t<sub>AC</sub>. Stored data is read nondestructively; data can be read repeatedly because data hold time is infinite.

Time Axis Conversion. To use the  $\mu$ PD485505 as a time axis converter, write and read cycles must be controlled independently. Write and read ports must be initialized separately using the reset signals. Write cycles can then be executed in synchronization with WCK and write data can be stored sequentially from address 0 of this device. Afterward, when a read cycle is executed in synchronization with RCK, stored data can be read sequentially from address 0.

Since write and read cycles can be executed independently, data loaded at one arbitrary drive frequency can be read at another arbitrary drive frequency. In this sense, the  $\mu$ PD485505 functions as a time axis converter.

Digital Delay Line. The µPD485505 can be easily used as a digital delay line of 5048 bits or less. After the internal circuits are initialized using simultaneous RSTW/RSTR signals, write/read cycles also may be executed simultaneously by supplying the same pulse to the write (WCK) and read (RCK) clocks. Write data is always read after the full 5048-bit delay if neither write nor read operation has been inhibited. This is the essential delay line function.

If either WE or RE is set at a nonselected (high) level for several cycles while the other is maintained in a selected (low) level, the delay line length can differ from 5048 bits.

For example, if only  $\overline{WE}$  is a set to a high level (write disable) for a small number of cycles, read cycles are executed continuously and the delay line length is large. Alternatively, if only  $\overline{RE}$  is set to a high level (read disable) for a small number of cycles, write cycles are executed continuously and the delay line length is small. Note that the minimum delay line length is 21 bits (for maximum frequency operation) and the maximum is 5048 bits.

A data delay of 5048 bits or less can also be obtained by applying the RSTW and RSTR signals at different times. For example, data loaded for "m" cycles after RSTW can then be read after supplying RSTR. In this case, since write data can be read from the beginning after a delay of "m" cycles, the device can be used as an m-bit digital delay line.

The RSTW/RSTR reset signals can also be simultaneously loaded at every 1H (horizontal line) period. In this case, write data loaded in the previous line cycle is read out from the beginning as read data after the reset. Therefore, a delay line length ranging from 21 to 5048 bits (depending on cycle time) can be obtained according to the length of the reset signals supplied. Refer to the timing waveform for an "n-Bit Delay Line."

PSE D

#### **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>           | -0.5 to +7.0 V                  |

|-------------------------------------------|---------------------------------|

| Voltage on any input pin, V <sub>I</sub>  | -0.5 to V <sub>CC</sub> + 0.5 V |

| Voltage on any output pin, V <sub>O</sub> | -0.5 to V <sub>CC</sub> + 0.5 V |

| Short-circuit output current, IOS         | 20 mA                           |

| Operating temperature, TOPR               | 0 to +70°C                      |

| Storage temperature, T <sub>STG</sub>     | -55 to +125°C                   |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

# **Recommended Operating Conditions**

| Parameter           | Symbol          | Min  | Тур | Max                   | Unit |

|---------------------|-----------------|------|-----|-----------------------|------|

| Supply voltage      | Vcc             | 4.5  | 5.0 | 5.5                   | ٧    |

| Input voltage, high | V <sub>IH</sub> | 2.4  |     | V <sub>CC</sub> + 0.5 | ٧    |

| Input voltage, low  | VIL             | -0.3 |     | 0.8                   | ٧    |

| Ambient temperature | TA              | 0    |     | 70                    | °C   |

#### Capacitance

$T_A = 25^{\circ}C; V_{CC} = +5.0 \text{ V} \pm 10\%; f = 1 \text{ MHz}$

| Parameter *          | Symbol | Max | Unit | Pins Under Test                                                      |

|----------------------|--------|-----|------|----------------------------------------------------------------------|

| Input<br>capacitance | CI     | 5   | рF   | WE, RE, WCK, RCK,<br>RSTW, RSTR, D <sub>INO</sub> - D <sub>IN7</sub> |

| Output capacitance   | co     | 7   | рF   | D <sub>OUT0</sub> - D <sub>OUT7</sub>                                |

<sup>\*</sup> These parameters are sampled and not 100% tested.

#### **DC Characteristics**

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%$

| Parameter                          | Symbol         | Min | Тур | Max | Unit | Test Conditions                                                               |

|------------------------------------|----------------|-----|-----|-----|------|-------------------------------------------------------------------------------|

| Write/read cycle operating current | loc            |     |     | 80  | mA   |                                                                               |

| Input leakage current              | l <sub>l</sub> | -10 |     | 10  | μΑ   | V <sub>I</sub> = 0 V to V <sub>CC</sub> ; all other pins not under test = 0 V |

| Output leakage current             | lo             | -10 |     | 10  | μΑ   | D <sub>OUT</sub> disabled; V <sub>O</sub> = 0 to 5.5 V                        |

| Output voltage, high               | Voн            | 2.4 |     |     | ٧    | I <sub>OH</sub> = -1 mA                                                       |

| Output voltage, low                | VoL            |     |     | 0.4 | ٧    | I <sub>OL</sub> = 2 mA                                                        |

#### HSE D

# **µPD485505**

#### AC Characteristics

$T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V } \pm 10\%$

| Parameter                        |                   | μPD485505-25 |     | μPD485505-35 |     |      |                        |

|----------------------------------|-------------------|--------------|-----|--------------|-----|------|------------------------|

|                                  | Symbol            | Min          | Max | Min          | Max | Unit | <b>Test Conditions</b> |

| Access time                      | <sup>t</sup> AC   |              | 18  |              | 25  | กร   |                        |

| Data-in hold time                | t <sub>DH</sub>   | 3            |     | 3            |     | ns   |                        |

| Data-in setup time               | tos               | 7            |     | 10           |     | пѕ   |                        |

| Output disable time              | t <sub>HZ</sub>   | 5            | 18  | 5            | 25  | ns   | (Note 4)               |

| Output active time               | tLZ               | 5            | 18  | 5            | 25  | ns   | (Note 4)               |

| Output hold time                 | tон               | 5            |     | 5            |     | ns   |                        |

| Read clock cycle time            | tRCK              | 25           |     | 35           |     | ns   |                        |

| RCK precharge time               | tRCP              | 9            |     | 12           |     | ns   |                        |

| RCK pulse width                  | tRCW              | 9            |     | 12           |     | ns   |                        |

| Read enable hold time            | t <sub>REH</sub>  | 3            |     | 3            |     | ns   | (Note 8)               |

| Read enable high delay from RCK  | t <sub>REN1</sub> | 3            |     | 3            |     | ns   | (Note 9)               |

| Read enable low delay to RCK     | t <sub>REN2</sub> | 7            |     | 10           |     | ns   | (Note 9)               |

| Read enable setup time           | tRES              | 7            |     | 10           |     | ns   | (Note 8)               |

| Read disable pulse width         | t <sub>REW</sub>  | 0            |     | 0            |     | ns   |                        |

| Reset active hold time           | t <sub>RH</sub>   | 3            |     | 3            |     | ns   | (Note 6)               |

| Reset inactive hold time         | t <sub>RN1</sub>  | 3            |     | 3            |     | ns   | (Note 7)               |

| Reset inactive setup time        | t <sub>RN2</sub>  | 7            |     | 10           |     | ns   | (Note 7)               |

| Reset active setup time          | t <sub>RS</sub>   | 7            |     | 10           |     | ns   | (Note 6)               |

| Read reset time                  | <sup>t</sup> rstr | 0            |     | 0            |     | ns   |                        |

| Write reset time                 | <sup>t</sup> rstw | 0            |     | 0            |     | ns   |                        |

| Transition time                  | t <sub>T</sub>    | 3            | 35  | 3            | 35  | ns   |                        |

| Write clock cycle time           | twck              | 25           |     | 35           |     | ns   |                        |

| WCK precharge time               | twcp              | 9            |     | 12           |     | ns   |                        |

| WCK pulse width                  | twcw              | 9            |     | 12           |     | ns   |                        |

| Write enable hold time           | tweh              | 3            |     | 3            |     | ns   | (Note 8)               |

| Write enable high delay from WCK | twen1             | 3            |     | 3            |     | ns   | (Note 9)               |

| Write enable low delay to WCK    | twen2             | 7            |     | 10           |     | ns   | (Note 9)               |

| Write enable setup time          | twes              | 7            |     | 10           |     | пѕ   | (Note 8)               |

| Write disable pulse width        | twew              | 0            |     | 0            |     | ns   |                        |

#### Notes:

- (1) All voltages are referenced to ground.

- (2) Input pulse rise and fall times assume  $t_T = 5$  ns.

- (3) Input pulse levels = GND to 3 V. Transition times are measured between 3 V and 0 V.

- (4) This delay is measured at  $\pm 200$  mV from the steady-state voltage with the load specified in figure 1. Under any conditions,  $t_{LZ} \ge$

- (5) Input timing reference levels = 1.5 V.

- (6) If either  $t_{RS}$  or  $t_{RH}$  is less than the specified value, reset operations are not guaranteed.

- (7) If either  $t_{\mbox{\scriptsize RN1}}$  or  $t_{\mbox{\scriptsize RN2}}$  is less than the specified value, internal reset operations may extend to cycles immediately preceding or following the period of desired reset operations.

- (8) If either  $t_{WES}$  or  $t_{WEH}$  ( $t_{RES}$  or  $t_{REH}$ ) is less than the specified value, write (read) output disable operations are not guaranteed.

- (9) If either twen1 or twen2 (tren1 or tren2) is less than the specified value, internal write (read) output disable operations may extend to cycles immediately preceding or following the period of desired disable operations.

65E D -

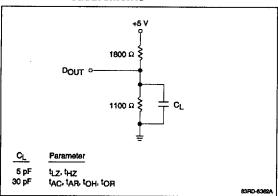

Figure 1. Output Loads for Timing Measurements

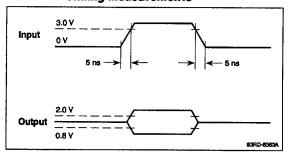

Figure 2. Voltage Thresholds for Timing Measurements

PSE D

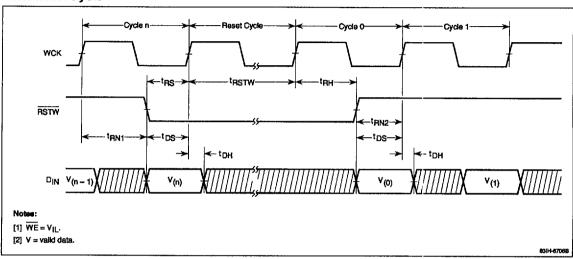

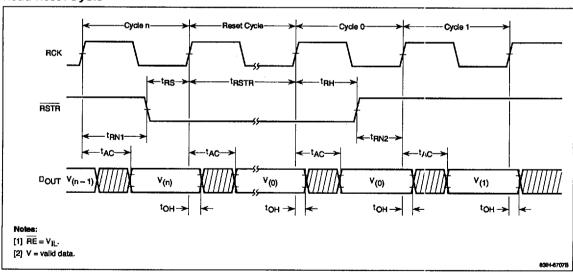

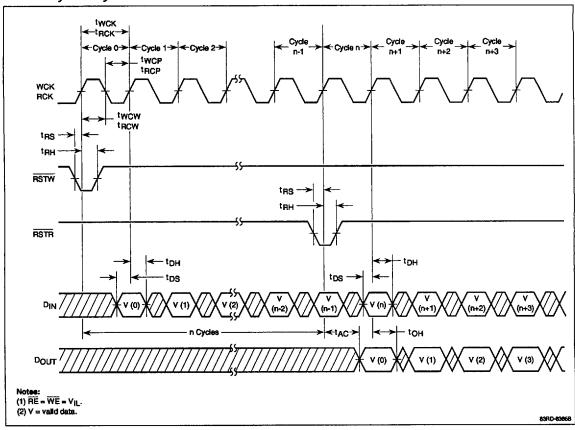

### **Timing Waveforms**

### Write Cycle

### Read Cycle

# N E C ELECTRONICS INC

**Timing Waveforms (cont)**

#### Write Reset Cycle

### Read Reset Cycle

■ 6427525 0035742 314 ■ NECE

μPD485505

N E C ELECTRONICS INC

PSE D

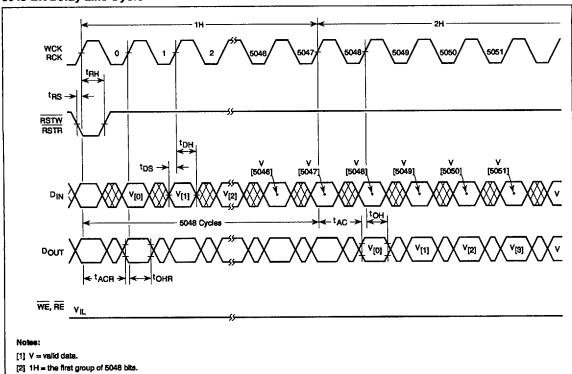

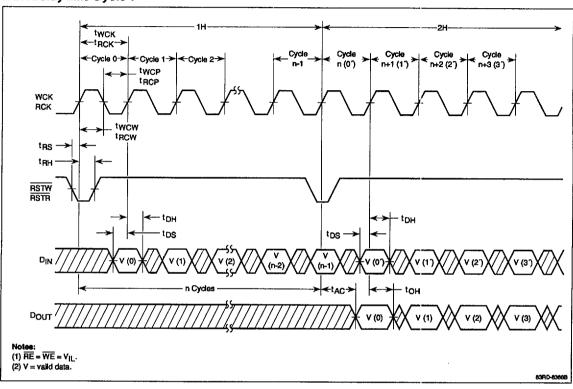

# **Timing Waveforms (cont)**

#### 5048-Bit Delay Line Cycle

[2] 1H = the first group of 5048 bits.2H = the second group of 5048 bits.

89/G-71788

# NEC

- N E C ELECTRONICS INC

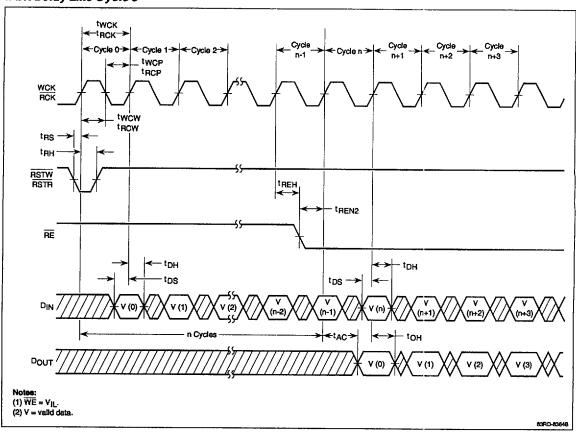

Timing Waveforms (cont)

### n-Bit Delay Line Cycle 3

**μPD485505**

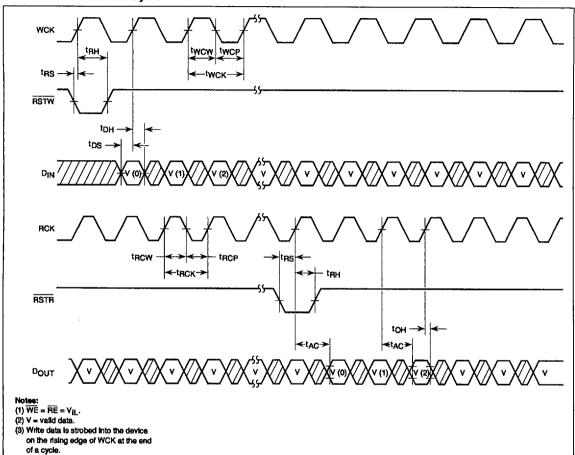

# Timing Waveforms (cont)

### n-Bit Delay Line Cycle 2

### - N E C ELECTRONICS INC

Timing Waveforms (cont)

#### n-Bit Delay Line Cycle 1

μPD485505

PSE D \_

# Timing Waveforms (cont)

# Time Axis Conversion Cycle

83RD-8367B

# - N E C ELECTRONICS INC

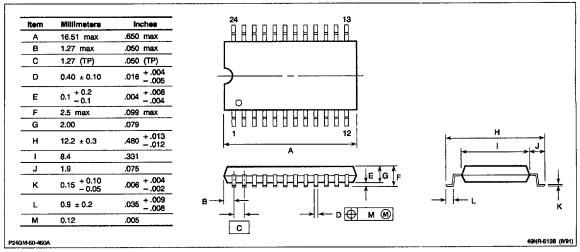

#### **Package Drawings**

#### 24-Pin Plastic SOP (450-mil)

#### 24-Pin Plastic ZIP (400-mil)