#### INTEGRATED CIRCUITS

# DATA SHEET

# PNX3000 Analog front end for digital video processors

Preliminary specification Supersedes data of 2004 Jun 24 2004 Oct 04

PNX3000

| CONTENT                | rs                                                             | 9            | LIMITING VALUES                                                                |

|------------------------|----------------------------------------------------------------|--------------|--------------------------------------------------------------------------------|

| 1                      | FEATURES                                                       | 10           | THERMAL CHARACTERISTICS                                                        |

| 2                      | GENERAL DESCRIPTION                                            | 11           | QUALITY SPECIFICATION                                                          |

| 3                      | ORDERING INFORMATION                                           | 11.1         | Latch-up performance                                                           |

| 4                      | QUICK REFERENCE DATA                                           | 12           | CHARACTERISTICS                                                                |

| 5                      | BLOCK DIAGRAM                                                  | 13           | TEST AND APPLICATION INFORMATION                                               |

| 6                      | PINNING                                                        | 13.1<br>13.2 | Power supply decoupling Application diagram                                    |

| 7                      | FUNCTIONAL DESCRIPTION                                         | 14           | PACKAGE OUTLINE                                                                |

| 7.1<br>7.2             | Vision IF<br>DTV IF                                            | 15           | SOLDERING                                                                      |

| 7.3<br>7.4             | Sound IF CVBS/YC source selector                               | 15.1         | Introduction to soldering surface mount packages                               |

| 7. <del>4</del><br>7.5 | RGB/YPbPr source selector                                      | 15.2         | Reflow soldering                                                               |

| 7.6                    | Video ADCs and anti-alias filters                              | 15.3         | Wave soldering                                                                 |

| 7.7                    | Audio source selectors and A to D converters                   | 15.4         | Manual soldering                                                               |

| 7.8<br>7.9             | Microphone inputs Clock generation, timing circuitry and black | 15.5         | Suitability of surface mount IC packages for wave and reflow soldering methods |

|                        | level clamping                                                 | 16           | DATA SHEET STATUS                                                              |

| 7.10                   | Data link transmitters                                         | 17           | DEFINITIONS                                                                    |

| 7.11<br>7.12           | I <sup>2</sup> C-bus transceiver Power supply circuit          | 18           | DISCLAIMERS                                                                    |

| 7.12                   | East-west interface                                            | 19           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                                |

| 8                      | I <sup>2</sup> C-BUS SPECIFICATION                             |              |                                                                                |

| 8.1<br>8.2             | Input control registers Output status registers                |              |                                                                                |

### Analog front end for digital video processors

PNX3000

#### 1 FEATURES

- Multi-standard vision IF circuit with alignment-free PLL demodulator without external components

- Internal (switchable) time-constant for the IF AGC circuit

- DTV IF circuit for gain control of digital broadcast TV signals

- Sound IF amplifier with separate AGC circuit for quasi-split sound

- IF circuit can also be used for intercarrier sound

- · Analog demodulator for AM sound

- · Integrated sound trap and group delay correction

- Video ident function detects the presence of a video signal

- Video source selector with four external CVBS or YC inputs and two analog CVBS outputs with independent source selection for each output

- Two linear inputs for 1f<sub>H</sub> or 2f<sub>H</sub> RGB signals with source selector; the RGB signals are converted to YUV before A to D conversion; both inputs can also be used as YPbPr input for DVD or set top box

- Integrated anti-alias filters for video Analog to Digital Converters (ADCs)

- Four 10-bit video ADCs for the conversion of CVBS, YC, YUV and down-mixed sound IF signals

- Up to three different A to D converted video channels are available simultaneously (e.g. CVBS, YC and YUV)

- Audio source selector with five stereo inputs for analog audio and two microphone inputs

- Three analog audio outputs for SCART and line out with independent source selection for each output

- Four 1-bit audio sigma delta ADCs for the conversion of audio and microphone signals

- Three serial data link transmitters for interfacing with the digital video processor at a bit rate of 594 Mbit/s per data link

- Voltage to current converter for driving external east-west power amplifier

- I<sup>2</sup>C-bus transceiver with selectable slave address and maskable interrupt output.

#### 2 GENERAL DESCRIPTION

The PNX3000 is an analog front end for digital video processors. It contains an IF circuit for both analog and digital broadcast signals, input selectors and ADCs for analog video and audio signals. The digital output signals are made available via three serial data links.

The IC has a supply voltage of 5 V. The supply voltage of the analog audio part can be 5 V or 8 V, depending on the maximum signal amplitudes that are required.

#### 3 ORDERING INFORMATION

| TYPE NUMBER  |         | PACKAGE                                                                             |          |  |  |  |  |  |

|--------------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| THE NUMBER   | NAME    | DESCRIPTION                                                                         |          |  |  |  |  |  |

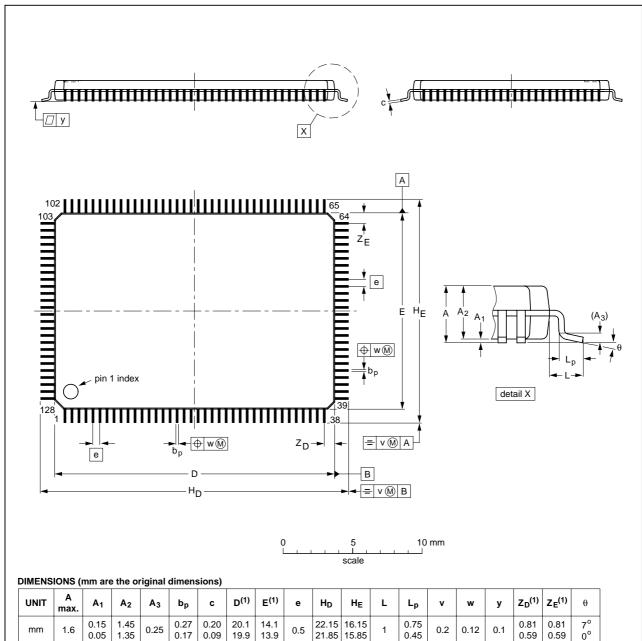

| PNX3000HL/N3 | LQFP128 | plastic low profile quad flat package; 128 leads; body $14 \times 20 \times 1.4$ mm | SOT425-1 |  |  |  |  |  |

3

2004 Oct 04

# Analog front end for digital video processors

PNX3000

#### 4 QUICK REFERENCE DATA

| SYMBOL                                        | PARAMETER                                                    | CONDITIONS           | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------|--------------------------------------------------------------|----------------------|------|------|------|------|

| Supply                                        |                                                              |                      | •    | •    | •    |      |

| $V_{P}$                                       | main supply voltage                                          |                      | 4.75 | 5.0  | 5.25 | V    |

| I <sub>P</sub>                                | main supply current                                          |                      | _    | 285  | 320  | mA   |

| V <sub>CC(1ASW)</sub> , V <sub>CC(2ASW)</sub> | audio supply voltage                                         | note 1               | 4.75 | 8.0  | 8.4  | V    |

| I <sub>CC(ASW)</sub>                          | audio supply current                                         | note 1               | _    | 3.5  | 5.0  | mA   |

| Input signals                                 |                                                              | •                    |      |      |      |      |

| V <sub>i(VIF)(dif)(rms)</sub>                 | video IF amplifier sensitivity (differential; RMS value)     |                      | _    | 75   | 150  | μV   |

| V <sub>i(DTVIF)(dif)(rms)</sub>               | video DTV IF amplifier sensitivity (differential; RMS value) |                      | _    | 75   | 150  | μV   |

| V <sub>i(SIF)(rms)</sub>                      | sound IF amplifier sensitivity (RMS value)                   | −3 dB                | _    | 45   | tbf  | dΒμV |

| V <sub>i(CVBS/Y)(p-p)</sub>                   | CVBS or Y input voltage (peak-to-peak value)                 |                      | _    | 1.0  | 1.76 | ٧    |

| V <sub>i(RGB)(b-w)</sub>                      | RGB inputs (black-to-white value)                            | note 2               | _    | 0.7  | 1.0  | V    |

| $V_{i(Y)(p-p)}$                               | luminance input signal (peak-to-peak value)                  | note 2               | _    | 1.0  | 1.43 | V    |

| $V_{i(Pb)(p-p)}$                              | Pb input signal (peak-to-peak value)                         | note 2               | _    | 0.7  | 1.0  | V    |

| V <sub>i(Pr)(p-p)</sub>                       | Pr input signal (peak-to-peak value)                         | note 2               | _    | 0.7  | 1.0  | V    |

| Video ADCs                                    |                                                              |                      |      |      |      |      |

| B <sub>v(-3dB)</sub>                          | -3 dB signal bandwidth                                       | 1f <sub>H</sub> mode | _    | 9    | _    | MHz  |

| f <sub>sample</sub>                           | sample frequency                                             | 1f <sub>H</sub> mode | _    | 27   | _    | MHz  |

| RES                                           | resolution                                                   |                      | _    | 10   | _    | bit  |

| Analog output signa                           | ls                                                           |                      |      | •    |      |      |

| V <sub>o(CVBS)(p-p)</sub>                     | analog CVBS output voltage (peak-to-peak value)              |                      | _    | 2.0  | _    | V    |

| I <sub>o(TUNERAGC)</sub>                      | tuner AGC output current range                               |                      | 0    | _    | 1    | mA   |

|                                               |                                                              |                      |      |      |      |      |

#### **Notes**

- 1. The supply voltage for the analog audio part of the IC can be 5 V or 8 V. For a supply voltage of 5 V the maximum signal amplitudes at in- and outputs are 1 V (RMS). For a supply voltage of 8 V the maximum amplitudes are 2 V (RMS).

- 2. The RGB inputs can also be used as YPbPr input. The selection is made via the I<sup>2</sup>C-bus. The YPbPr input sensitivity is in accordance with the DVD player specification.

PNX3000

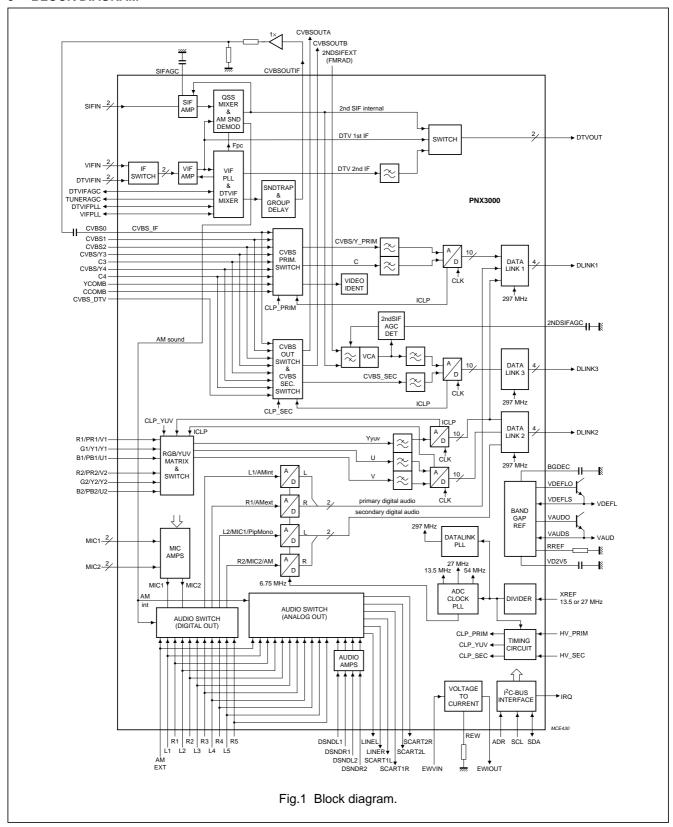

#### 5 BLOCK DIAGRAM

PNX3000

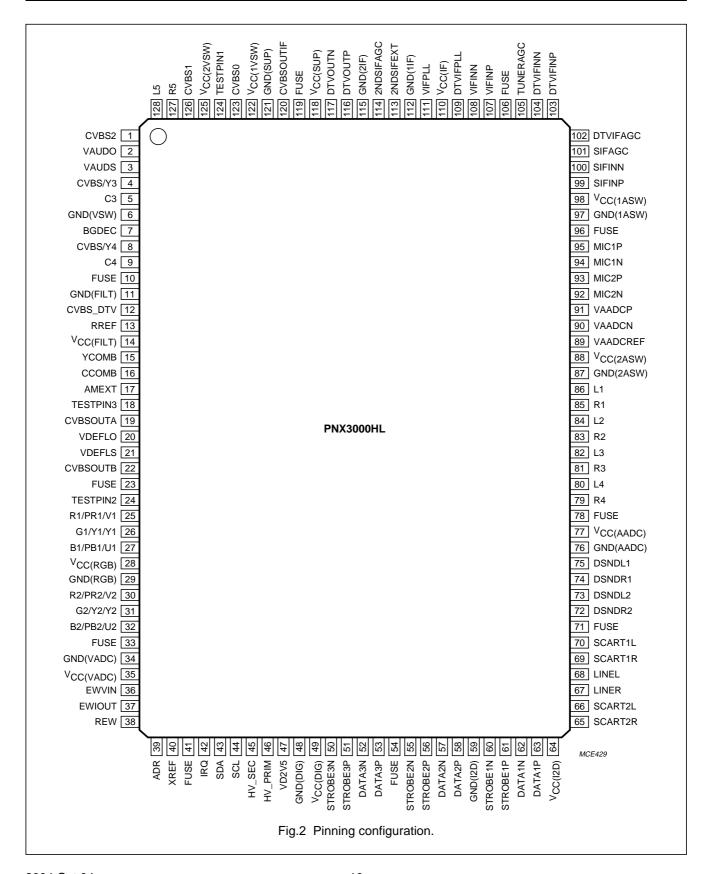

#### 6 PINNING

| SYMBOL                | PIN | DESCRIPTION                                                                     |

|-----------------------|-----|---------------------------------------------------------------------------------|

| CVBS2                 | 1   | CVBS2 input                                                                     |

| VAUDO                 | 2   | DC output voltage for supply of audio DACs in digital decoder                   |

| VAUDS                 | 3   | sense voltage input for audio DACs supply                                       |

| CVBS/Y3               | 4   | external CVBS/Y3 input                                                          |

| C3                    | 5   | external CHROMA3 input                                                          |

| GND(VSW)              | 6   | ground video switch                                                             |

| BGDEC                 | 7   | bandgap decoupling                                                              |

| CVBS/Y4               | 8   | external CVBS/Y4 input                                                          |

| C4                    | 9   | external CHROMA4 input                                                          |

| FUSE                  | 10  | fused lead                                                                      |

| GND(FILT)             | 11  | ground filters                                                                  |

| CVBS_DTV              | 12  | input for CVBS encoded signal from DTV decoder                                  |

| RREF                  | 13  | reference current input                                                         |

| V <sub>CC(FILT)</sub> | 14  | supply voltage filters (5 V)                                                    |

| YCOMB                 | 15  | Y signal input from 3D Comb filter                                              |

| ССОМВ                 | 16  | C signal input from 3D Comb filter                                              |

| AMEXT                 | 17  | external AM mono input                                                          |

| TESTPIN3              | 18  | test pin 3; must be left open                                                   |

| CVBSOUTA              | 19  | CVBS or Y+CHROMA output A                                                       |

| VDEFLO                | 20  | DC output voltage for supply of deflection DACs in digital decoder              |

| VDEFLS                | 21  | sense input voltage for deflection DACs supply                                  |

| CVBSOUTB              | 22  | CVBS or Y+CHROMA output B                                                       |

| FUSE                  | 23  | fused lead                                                                      |

| TESTPIN2              | 24  | test pin 2; connect to ground                                                   |

| R1/PR1/V1             | 25  | R input 1 of RGB signal Pr input 1 of YPbPr signal or V input 1 of YUV signal   |

| G1/Y1/Y1              | 26  | G input 1 of RGB signal or Y input 1 of YPbPr signal or Y input 1 of YUV signal |

| B1/PB1/U1             | 27  | B input 1 of RGB signal Pb input 1 of YPbPr signal or U input 1 of YUV signal   |

| V <sub>CC(RGB)</sub>  | 28  | supply voltage RGB matrix (5 V)                                                 |

| GND(RGB)              | 29  | ground RGB matrix                                                               |

| R2/PR2/V2             | 30  | R input 2 of RGB signal Pr input 2 of YPbPr signal or V input 2 of YUV signal   |

| G2/Y2/Y2              | 31  | G input 2 of RGB signal or Y input 2 of YPbPr signal or Y input 2 of YUV signal |

| B2/PB2/U2             | 32  | B input 2 of RGB signal Pb input 2 of YPbPr signal or U input 2 of YUV signal   |

| FUSE                  | 33  | fused lead                                                                      |

| GND(VADC)             | 34  | ground video ADCs                                                               |

| V <sub>CC(VADC)</sub> | 35  | supply voltage video ADCs (5 V)                                                 |

| EWVIN                 | 36  | east-west input voltage                                                         |

| EWIOUT                | 37  | east-west output current                                                        |

| REW                   | 38  | east-west voltage to current conversion resistor                                |

| ADR                   | 39  | I <sup>2</sup> C-bus address selection input                                    |

| XREF                  | 40  | XTAL reference frequency input                                                  |

PNX3000

| SYMBOL                | PIN | DESCRIPTION                                                    |

|-----------------------|-----|----------------------------------------------------------------|

| FUSE                  | 41  | fused lead                                                     |

| IRQ                   | 42  | interrupt request output                                       |

| SDA                   | 43  | I <sup>2</sup> C-bus serial data input and output              |

| SCL                   | 44  | I <sup>2</sup> C-bus serial clock input                        |

| HV_SEC                | 45  | horizontal and vertical sync input for secondary video channel |

| HV_PRIM               | 46  | horizontal and vertical sync input for primary video channel   |

| VD2V5                 | 47  | decoupling of internal digital supply voltage                  |

| GND(DIG)              | 48  | digital ground                                                 |

| V <sub>CC(DIG)</sub>  | 49  | digital supply voltage (5 V)                                   |

| STROBE3N              | 50  | strobe negative data link 3                                    |

| STROBE3P              | 51  | strobe positive data link 3                                    |

| DATA3N                | 52  | data negative data link 3                                      |

| DATA3P                | 53  | data positive data link 3                                      |

| FUSE                  | 54  | fused lead                                                     |

| STROBE2N              | 55  | strobe negative data link 2                                    |

| STROBE2P              | 56  | strobe positive data link 2                                    |

| DATA2N                | 57  | data negative data link 2                                      |

| DATA2P                | 58  | data positive data link 2                                      |

| GND(I2D)              | 59  | ground data links                                              |

| STROBE1N              | 60  | strobe negative data link 1                                    |

| STROBE1P              | 61  | strobe positive data link 1                                    |

| DATA1N                | 62  | data negative data link 1                                      |

| DATA1P                | 63  | data positive data link 1                                      |

| V <sub>CC(I2D)</sub>  | 64  | supply voltage data links (5 V)                                |

| SCART2R               | 65  | audio output for SCART2 right                                  |

| SCART2L               | 66  | audio output for SCART2 left                                   |

| LINER                 | 67  | audio line output right                                        |

| LINEL                 | 68  | audio line output left                                         |

| SCART1R               | 69  | audio output for SCART1 right                                  |

| SCART1L               | 70  | audio output for SCART1 left                                   |

| FUSE                  | 71  | fused lead                                                     |

| DSNDR2                | 72  | audio signal input from digital decoder right 2                |

| DSNDL2                | 73  | audio signal input from digital decoder left 2                 |

| DSNDR1                | 74  | audio signal input from digital decoder right 1                |

| DSNDL1                | 75  | audio signal input from digital decoder left 1                 |

| GND(AADC)             | 76  | ground audio ADCs                                              |

| V <sub>CC(AADC)</sub> | 77  | supply voltage audio ADCs (5 V)                                |

| FUSE                  | 78  | fused lead                                                     |

| R4                    | 79  | right input audio 4                                            |

| L4                    | 80  | left input audio 4                                             |

| R3                    | 81  | right input audio 3                                            |

PNX3000

| SYMBOL                | PIN | DESCRIPTION                                                    |

|-----------------------|-----|----------------------------------------------------------------|

| L3                    | 82  | left input audio 3                                             |

| R2                    | 83  | right input audio 2                                            |

| L2                    | 84  | left input audio 2                                             |

| R1                    | 85  | right input audio 1                                            |

| L1                    | 86  | left input audio 1                                             |

| GND(2ASW)             | 87  | ground 2 audio switch                                          |

| V <sub>CC(2ASW)</sub> | 88  | supply voltage 2 audio switch (audio output buffers; 5 or 8 V) |

| VAADCREF              | 89  | decoupling of reference voltage for audio ADCs                 |

| VAADCN                | 90  | 0 V reference voltage for audio ADCs (GND)                     |

| VAADCP                | 91  | full scale reference voltage for audio ADCs (5 V)              |

| MIC2N                 | 92  | microphone input 2, negative                                   |

| MIC2P                 | 93  | microphone input 2, positive                                   |

| MIC1N                 | 94  | microphone input 1, negative                                   |

| MIC1P                 | 95  | microphone input 1, positive                                   |

| FUSE                  | 96  | fused lead                                                     |

| GND(1ASW)             | 97  | ground 1 audio switch                                          |

| V <sub>CC(1ASW)</sub> | 98  | supply voltage 1 audio switch (audio input buffers; 5 or 8 V)  |

| SIFINP                | 99  | sound IF input, positive                                       |

| SIFINN                | 100 | sound IF input, negative                                       |

| SIFAGC                | 101 | control voltage for sound IF AGC                               |

| DTVIFAGC              | 102 | control voltage for DTV IF AGC                                 |

| DTVIFINP              | 103 | DTV IF input, positive                                         |

| DTVIFINN              | 104 | DTV IF input, negative                                         |

| TUNERAGC              | 105 | tuner AGC output                                               |

| FUSE                  | 106 | fused lead                                                     |

| VIFINP                | 107 | vision IF input, positive                                      |

| VIFINN                | 108 | vision IF input, negative                                      |

| DTVIFPLL              | 109 | output loop filter DTV IF PLL demodulator                      |

| V <sub>CC(IF)</sub>   | 110 | supply voltage IF circuit (5 V)                                |

| VIFPLL                | 111 | output loop filter VIF PLL demodulator                         |

| GND(1IF)              | 112 | ground 1 IF circuit                                            |

| 2NDSIFEXT             | 113 | second sound IF input                                          |

| 2NDSIFAGC             | 114 | second sound IF AGC capacitor                                  |

| GND(2IF)              | 115 | ground 2 IF circuit                                            |

| DTVOUTP               | 116 | DTV output, positive                                           |

| DTVOUTN               | 117 | DTV output, negative                                           |

| V <sub>CC(SUP)</sub>  | 118 | supply voltage of supply circuit (5 V)                         |

| FUSE                  | 119 | fused lead                                                     |

| CVBSOUTIF             | 120 | CVBS output of IF circuit                                      |

| GND(SUP)              | 121 | ground of supply circuit                                       |

| V <sub>CC(1VSW)</sub> | 122 | supply voltage 1 of video switch (5 V)                         |

PNX3000

| SYMBOL                | PIN | DESCRIPTION                            |  |

|-----------------------|-----|----------------------------------------|--|

| CVBS0                 | 123 | CVBS0 input for CVBS from IF part      |  |

| TESTPIN1              | 124 | test pin 1; connect to ground          |  |

| V <sub>CC(2VSW)</sub> | 125 | supply voltage 2 of video switch (5 V) |  |

| CVBS1                 | 126 | CVBS1 input                            |  |

| R5                    | 127 | right input audio 5                    |  |

| L5                    | 128 | eft input audio 5                      |  |

PNX3000

### Analog front end for digital video processors

PNX3000

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Vision IF

The IF amplifier contains 3 AC-coupled control stages which have a total gain control range of more than 66 dB.

The video signal is demodulated by means of an alignment-free PLL carrier regenerator with an internal VCO. This VCO is calibrated by means of a digital control circuit which uses the external crystal frequency as a reference. The frequency setting for the various standards (33.4 MHz, 33.9 MHz, 38 MHz, 38.9 MHz, 45.75 MHz and 58.75 MHz) is realised via the I<sup>2</sup>C-bus. To improve performance for phase modulated carrier signals the control speed of the PLL can be increased by setting bit FFI.

The AFC output is generated by the digital control circuit of the IF PLL demodulator and can be read via the I<sup>2</sup>C-bus. For fast search tuning systems the window of the AFC can be increased with a factor of three with bus bit AFW.

The AGC-detector operates on top sync or top white level. The demodulation polarity is switched via the  $I^2C$ -bus. The AGC detector capacitor is integrated. The time-constant can be chosen via  $I^2C$ -bus bits AGC1 and AGC0. The AGC has also an external mode which is activated by bit AGCM. In this mode the IF gain is determined by an external voltage on pin DTVIFAGC.

The IC has an integrated sound trap filter. The filter is constructed as a cascade of three separate traps, to realize sufficient suppression of the first and second sound carriers. The trap frequencies are selected via the I<sup>2</sup>C-bus.

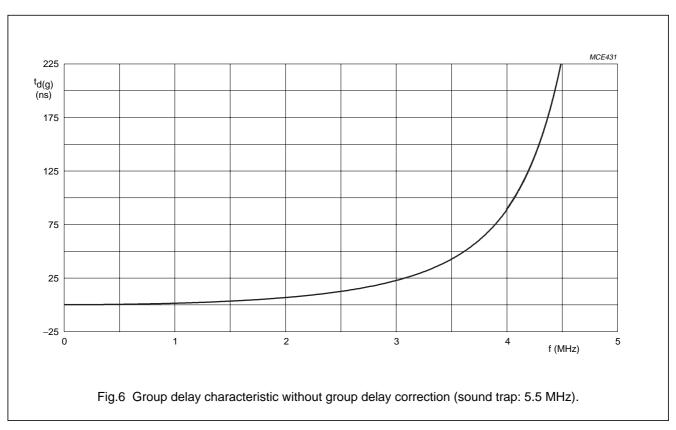

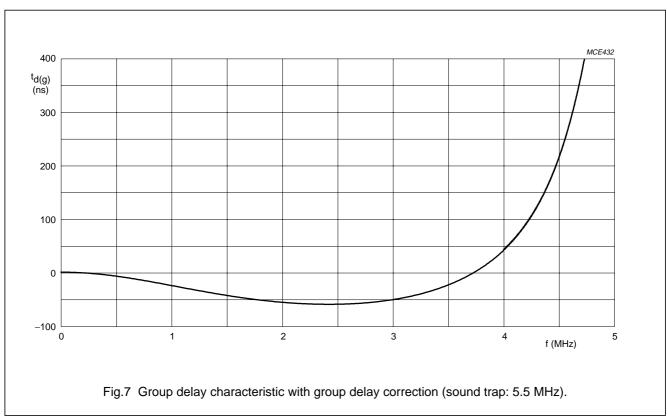

The IC has an integrated group delay correction filter. The filter can be switched between the PAL BG curve and a flat group delay response characteristic. This has the advantage that in multi-standard receivers the video SAW filter does not need to be switchable.

#### 7.2 DTV IF

Apart from processing analog TV signals, the IF circuit can also be used to preprocess digital TV signals before they are sent to a DTV channel decoder. For this application the two modes of operation are DTV 1st IF and DTV 2nd IF. For both operating modes the IF PLL must be set to synthesizer mode.

In DTV 1st IF mode only the AGC function of the IF circuit is used, so the DTV channel decoder must be able to handle the 1st IF frequency. Because the AGC detector operates on the down-mixed 2nd IF signal, it is still important to program a valid frequency for the IF VCO. It is recommended to set the frequency of the VCO to a value

that is approximately 4 MHz higher than the incoming 1st IF centre frequency.

In DTV 2nd IF mode the 2nd IF signal is obtained by down-mixing the incoming DTV IF signal with the IF VCO signal. The low-pass filtered DTV 2nd IF signal is available as a differential signal at the DTV output. This signal may have a maximum bandwidth of 10 MHz. The VCO frequency is programmed via the I<sup>2</sup>C-bus in steps of 250 kHz.

In DTV mode the AGC time constant is determined by a capacitor on pin DTVIFAGC. There are two AGC modes: internal and external. In the internal AGC mode the gain is controlled by an internal AGC detector. The external AGC mode is activated by bit AGCM. In this mode the appropriate AGC pin is used as input, so that the IF gain can be controlled by the DTV channel decoder.

The IF PLL has two pins for connection of the PLL loop filters, one for analog TV and one for DTV. This allows each loop filter to be optimized for its application.

#### 7.3 Sound IF

The PNX3000 has a separate sound IF input to enable quasi-split sound applications. The sound IF amplifier is similar to the vision IF amplifier and has a gain control range of about 55 dB. The AGC detector measures the average level of the AM or FM SIF carrier and ensures a constant signal amplitude for the AM demodulator and Quasi-Split Sound (QSS) mixer.

The single reference QSS mixer is realised by a multiplier. In this multiplier the SIF signal is converted to the intercarrier frequency by mixing it with the regenerated picture carrier from the video IF VCO. With this system a high performance stereo sound processing can be achieved.

For applications without a SIF SAW filter the IC can also be used in intercarrier mode. In this mode the composite video signal from the VIF amplifier is fed to the QSS mixer and converted to the intercarrier frequency.

AM sound demodulation is realised in the analog domain by the QSS mixer. The modulated SIF signal is multiplied in phase with the limited SIF signal. The demodulator output signal is low-pass filtered for suppression of the carrier harmonics. The demodulated AM signal can be digitized by one of the audio ADCs.

The QSS mixer can also be used for down-mixing an FM radio IF signal to an intercarrier frequency, so that it can be demodulated by the digital decoder. The IF PLL must be set to synthesizer mode in this case. The preferred solution is to supply the FM radio signal via a

### Analog front end for digital video processors

PNX3000

separate SAW or ceramic filter to the DTV input of the PNX3000. The reason is that the selectivity of a SAW filter for TV sound is not sufficient for FM radio and, if the SIF input is used, no tuner AGC information is available.

For high performance FM radio it is recommended that a 10.7 MHz FM radio IF signal is supplied to the external 2nd SIF input. In this case the IF signal must be filtered by an external bandpass filter, that also functions as an anti-alias filter. The low-pass filter before the 2nd SIF ADC must be bypassed by setting bus bit SLPM.

The IC includes a separate AGC circuit for the 2nd SIF signal. This AGC is needed for intercarrier sound applications and when an external sound IF signal is supplied to the 2nd SIF input. The AGC amplifier is preceded by a second order high-pass filter for suppression of video signal components. The AGC time constant is determined by an external capacitor.

#### 7.4 CVBS/YC source selector

The video input selector consists of four independent source selectors, that can select between the CVBS signal coming from the IF part and four external CVBS signals. Two of the external CVBS inputs can also be used as YC input. One selector is used to select the signal for of the primary video channel. A second selector selects the CVBS or YC signal for the secondary channel. The third and fourth selectors are used to select analog outputs CVBS A and B, which can be used for SCART or line output.

The primary channel can be a CVBS or YC signal. If a YC signal is selected for the secondary channel or for the external CVBS outputs A or B, the luminance and chrominance signals are added to obtain a CVBS signal.

The IC has an extra YC input for connection of a 3D comb filter. The comb signal can only be selected for the primary video channel. The input pin CVBS\_DTV allows an analog CVBS signal derived from a digital broadcast (MPEG) signal to be recorded with an analog VCR. This signal cannot be selected for the primary video channel.

The video identification circuit detects the presence of a video signal on the CVBS\_IF input (pin CVBS0). The identification output is normally used to detect transmitters during search tuning and can be read via the I<sup>2</sup>C-bus. The circuit can also be used to monitor the selected primary CVBS or YC signal. Either mode is selected by bit VIM.

#### 7.5 RGB/YPbPr source selector

The IC has two RGB inputs. Both inputs can also be used as YPbPr input for connecting video sources with an YPbPr output like a DVD player. The RGB inputs can also be used for fast insertion of RGB signals (for instance on screen display menus) in the primary CVBS signal. The fast insertion switch is located in the digital video processor.

The RGB signals are converted to YUV before further processing. The YUV output signal is digitized by two ADCs. The U and V components have half the bandwidth of the Y signal, therefore the U and V signals are multiplexed and digitized by one ADC.

#### 7.6 Video ADCs and anti-alias filters

The PNX3000 contains four video ADCs for analog and digital video broadcast signals. The clock frequency for the ADCs is either 27 MHz or 54 MHz. Two analog signals can be multiplexed at the input of one ADC. Then the clock frequency of the ADC is 54 MHz and the sample frequency of each channel is 27 MHz.

The video ADCs are 10-bit folding ADCs. The sample frequency for standard 1f<sub>H</sub> video signals is 27 MHz. For the YUV channel the sample frequency of the U and V components is half the sample frequency of the Y signal.

For  $2f_H$  YPbPr or RGB input signals (for instance 480p or 1080i ATSC signals), the frequency that is used to sample the YUV signals is twice as high as for  $1f_H$  signals. The sample frequency is 54 MHz for Y and 27 MHz for U and V. The high sample frequency requires two data links to transport the video data to the digital video processor.

The anti-alias filters before the ADCs limit the signal bandwidth to prevent aliasing effects. The filters for YUV can be bypassed by means of two separate bits: bit BPY for the Y filter and bit BPUV for the U and V filters. This enables the use of external anti-alias filters with increased bandwidth for  $2f_H$ , RGB or YPbPr input signals.

Table 1 shows the signal bandwidths and sample rates for the various types of video signals. Table 2 shows which video signals are sent to the digital video processor for both data link modes.

### Analog front end for digital video processors

PNX3000

Table 1 Overview of anti-alias filter bandwidths and video signal sample rates.

| SIGNAL TYPE         | SIGNAL<br>COMPONENT | SIGNAL BAND<br>-1.0 dB (MHz) | SIGNAL BAND<br>-3.0 dB (MHz) | SAMPLE<br>FREQUENCY (MHz) |

|---------------------|---------------------|------------------------------|------------------------------|---------------------------|

| CVBS                |                     | 8                            | 9                            | 27                        |

| YC                  | Y                   | 8                            | 9                            | 27                        |

|                     | С                   | 8                            | 9                            | 27                        |

| YUV 1f <sub>H</sub> | Y                   | 8                            | 9                            | 27                        |

|                     | U                   | 4                            | 4.5                          | 13.5                      |

|                     | V                   | 4                            | 4.5                          | 13.5                      |

| YUV 2f <sub>H</sub> | Y                   | 16                           | 18                           | 54                        |

|                     | U                   | 8                            | 9                            | 27                        |

|                     | V                   | 8                            | 9                            | 27                        |

| DTV                 | _                   | 10                           | 12                           | -                         |

| 2nd SIF             | _                   | 8                            | 9                            | 27                        |

#### 7.7 Audio source selectors and A to D converters

The PNX3000 contains two different audio source selectors. The first selector selects which audio signals are routed to the audio ADCs for further processing in the digital domain. The two microphone inputs are also connected to this selector. The selector has two outputs, a primary channel and a secondary channel. The primary audio channel is used for one stereo signal. The secondary audio channel can carry a second stereo signal, or two microphone signals, or one mono signal and one microphone signal or one mono signal and one AM sound signal.

The second selector selects which audio signals are fed to the analog audio outputs for SCART and line out. This selector also has two stereo inputs for demodulated sound signals coming from the digital video processor.

The gain from an external audio input to an analog output is 1. A supply voltage of 5 V allows input and output amplitudes of 1 V (RMS) full scale. The PNX3000 has separate supply voltage pins for the audio selector circuit. To allow for input and output amplitudes of 2 V (RMS) full scale, as required for compliance with the SCART specification, an audio supply voltage of 8 V must be used.

The audio ADCs are 1-bit sigma-delta converters that operate at a clock frequency of 6.75 MHz. The audio A to D clock is synchronous with the video A to D clock, so that audio and video data can be sent over the same data links. The effective audio sample rate is

$$\frac{f_{clk}}{128} = 52.7$$

ksample/s.

#### 7.8 Microphone inputs

The IC has two microphone inputs. One microphone input can be used for voice control of the TV set with the help of an intelligent voice command decoder. The second input can be used for connection of a microphone for Karaoke.

To allow the use of microphones with different sensitivities the gain of each microphone amplifier is switchable between two values via the  $I^2C$ -bus.

#### 7.9 Clock generation, timing circuitry and black level clamping

The IC contains two PLL circuits that derive the sample clock for the ADCs and the bit and word clocks for the data links from an external reference frequency. The reference frequency must be a stable frequency of either 13.5 MHz or 27 MHz from a crystal oscillator. The internal reference frequency is always 13.5 MHz. If the external frequency is 27 MHz a prescaler must be activated by bus bit FXT.

One PLL is used to multiply the 13.5 MHz reference frequency to the 27 MHz and 54 MHz clock frequencies that are needed for the video ADCs. A second PLL is used to obtain the 297 MHz bit clock for the data link transmitters.

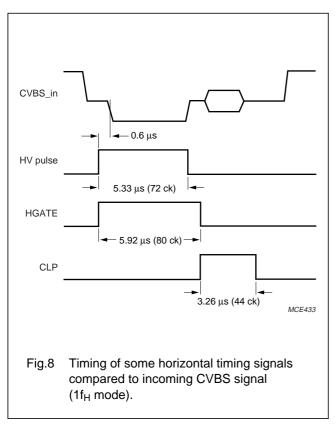

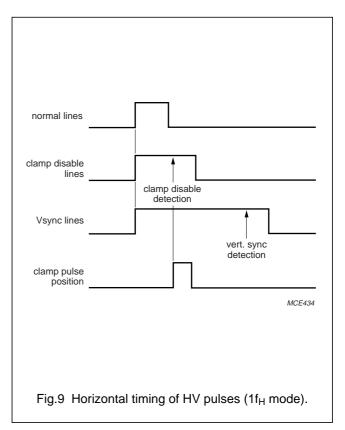

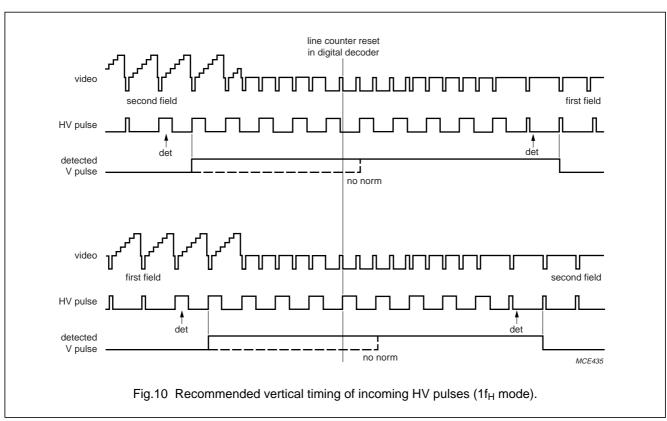

A special timing circuit is used to generate the horizontal and vertical timing pulses that are needed in the IF part, and also for clamping the black level of the selected video signals to a defined value at the output of the video ADCs. The horizontal and vertical timing information of the primary and secondary video channels must be supplied by the digital video processor on pins HV\_PRIM and HV\_SEC. The signal on these pins must consist of a

### Analog front end for digital video processors

PNX3000

horizontal timing pulse that starts just before and ends just after the horizontal sync pulse of the selected video signal. To enable detection of the vertical blanking period, the horizontal pulses must be wider during a number of lines in the vertical blanking interval.

The clamp signal inside the IC is generated with the help of the external horizontal timing pulse and the 13.5 MHz clock. The vertical timing information is used to disable the black level clamp, so that the black level is not disturbed by the vertical sync pulse on the video signal. The clamp pulse for the YUV channel can be derived from the primary or the secondary HV pulse, and is selected by bus bit CLPS.

To avoid signal disturbance, it is possible to disable the black clamps when the horizontal PLL in the digital video processor is not locked to the selected video signal. This is done by bus bit CMP for the primary CVBS channel and bus bit CMS for the secondary CVBS channel.

Special attention is required when the same CVBS input is selected for primary and secondary CVBS channels. In this case the black level clamp loop is only closed for the primary CVBS input. Due to internal offsets this will normally result in a deviation on the black level of the digitized secondary CVBS output.

#### 7.10 Data link transmitters

Three serial data links are used for transportation of the digital video and audio data coming from the ADCs in the PNX3000 to the digital video processor. The use of serial data connections results in a considerable reduction in pin count and the number of connection wires that are needed between both ICs.

The communication between data link transmitter and data link receiver consists of two signals, a data signal and a strobe signal. The two signals together contain the data, bit-sync and word-sync information. For optimal EMC performance both data and strobe are low voltage differential signals. The voltage swing on each wire is 300 mV.

Each data word sent over a data link consists of 44 bits: 4 video samples of 10 bits each, 2 audio bits and 2 word-sync bits. The word clock is 13.5 MHz. The data rate on each of the three data links is 594 Mbit/s.

Table 2 shows which video signals are sent to the digital video processor for both data link modes. In the standard mode up to three video channels plus one sound IF signal are digitized and transferred simultaneously over the data links.

The distance between both ICs that are connected via the data link must not be larger than about 10 centimetres. The two wires for each differential signal should be paired in the layout of the printed-circuit board.

#### 7.11 I<sup>2</sup>C-bus transceiver

The slave address of the I<sup>2</sup>C-bus transceiver in the PNX3000 has two possible values, selected via the ADR pin. The maximum bus clock frequency is 400 kHz, and the voltage swing of SCL and SDA can be 3.3 V or 5 V. The I<sup>2</sup>C-bus transceiver also has a hardwired IRQ output (open drain and LOW-active) for interruption of the microprocessor when the value of an important status bit in status byte 0 changes. The IRQ signal is maskable with register 0FH.

#### 7.12 Power supply circuit

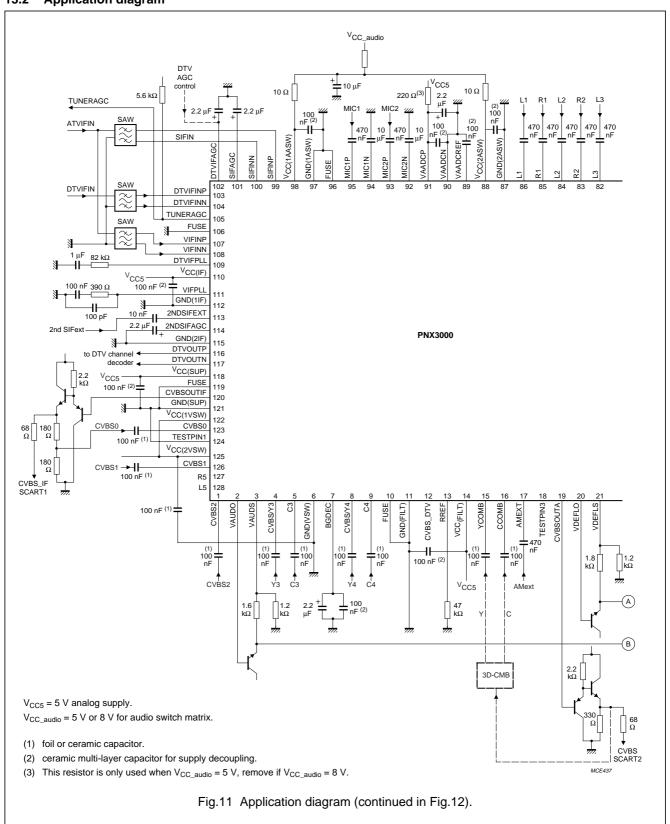

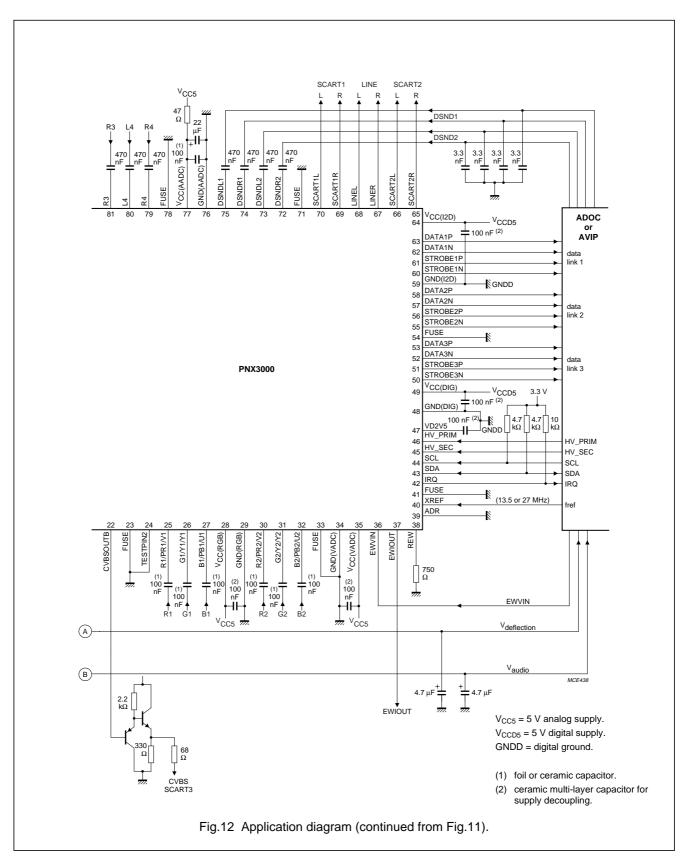

An internal bandgap circuit generates a stable voltage of 1.25 V. This voltage is multiplied to a reference voltage of 2.3 V, and a digital supply voltage of 2.5 V. These two voltages must be decoupled by external capacitors. A  $^{1}/_{2}$ Vp reference voltage for the audio ADCs also requires an external decoupling capacitor. The PNX3000 contains two voltage regulators to supply the SDACs that are used in the digital video processor. Each regulator requires a few external components (one transistor, two resistors and a decoupling capacitor). The output voltage is adjustable between 1.25 V and 3.3 V by selection of external resistors values.

#### 7.13 East-west interface

The PNX3000 contains a voltage to current converter that serves as the interface between the voltage output of the digital video processor and the current input of the east-west stage of the vertical deflection amplifier (TDA8358). The transconductance is determined by the value of an external resistor.

### Analog front end for digital video processors

PNX3000

Table 2 Overview of data link modes

| MODE APPLICATION |                           | DATA LINK 1            |   |               | DATA LINK 2 |                  |        | !  | DATA LINK 3 |                     |         |      |      |

|------------------|---------------------------|------------------------|---|---------------|-------------|------------------|--------|----|-------------|---------------------|---------|------|------|

| INIODE           | APPLICATION               | VIDEO1                 |   | AUDIO1 VIDEO2 |             | EO2              | AUDIO2 |    | VIDEO3      |                     | TEST    |      |      |

| 0                | standard                  | CVBS/Y <sub>prim</sub> | С | L1            | R1          | Y <sub>yuv</sub> | U,V    | L2 | R2          | CVBS <sub>sec</sub> | 2nd SIF | HV_P | HV_S |

| 1                | YUV 2f <sub>H</sub> input | Y <sub>yuv</sub>       |   | L1            | R1          | U                | V      | L2 | R2          | CVBS <sub>sec</sub> | 2nd SIF | HV_P | HV_S |

#### 8 I2C-BUS SPECIFICATION

The slave addresses of the IC are given in Table 3. The circuit operates at clock frequencies of up to 400 kHz.

Table 3 Slave addresses (9A or 9E)

| A6 | A5 | A4 | А3 | A2 | <b>A</b> 1 | A0 | R/W |

|----|----|----|----|----|------------|----|-----|

| 1  | 0  | 0  | 1  | 1  | A1         | 1  | 1/0 |

Bit A1 is controlled via the ADR pin, when the pin is connected to ground A1 = 0 and when connected to the positive supply line A1 = 1. When this pin is left open it is connected to ground via an internal resistor.

#### 8.1 Input control registers

Table 4 Input control registers; valid subaddresses: 00 to 0F; auto-increment mode available for subaddresses

|                                 | SUB  |                  |      |      | DATA | BYTE  |      |      |      | POR            |

|---------------------------------|------|------------------|------|------|------|-------|------|------|------|----------------|

| FUNCTION                        | ADDR | D7               | D6   | D5   | D4   | D3    | D2   | D1   | D0   | VALUE<br>(HEX) |

| Vision IF 0                     | 00   | AFN              | AFW  | IFS  | AGCM | FFI   | PMOD | AGC1 | AGC0 | 00             |

| Vision IF 1                     | 01   | IFON             | DSIF | DFIF | DTV  | IFLH  | SYNT | SSIF | QSS  | 00             |

| IF PLL offset                   | 02   | IFGT             | VAI  | IFO5 | IFO4 | IFO3  | IFO2 | IFO1 | IFO0 | 20             |

| IF tuner take over              | 03   | VA1              | VA0  | TTO5 | TTO4 | TTO3  | TTO2 | TTO1 | TTO0 | 20             |

| IF PLL frequency                | 04   | FXT              | IFA  | IFB  | IFC  | 0     | 0    | 0    | 0    | 80             |

| IF synthesizer frequency        | 05   | SF7              | SF6  | SF5  | SF4  | SF3   | SF2  | SF1  | SF0  | 00             |

| Filters                         | 06   | BPUV             | BPY  | BPP  | GD   | SLPM  | BPS  | ST1  | ST0  | 00             |

| Data link mode                  | 07   | DRND             | 0    | 0    | HDTV | 0     | 0    | 0    | DM   | 00             |

| Video switches 0                | 08   | SEC3             | SEC2 | SEC1 | SEC0 | PRI3  | PRI2 | PRI1 | PRI0 | 00             |

| Video switches 1                | 09   | VIM              | VSW  | CMS  | CMP  | CVA3  | CVA2 | CVA1 | CVA0 | 36             |

| Video switches 2 and audio mute | 0A   | 0                | MA2  | MA1  | MA0  | CVB3  | CVB2 | CVB1 | CVB0 | 76             |

| RGB switches                    | 0B   | 0                | RSEL | MAT  | DVD  | 0     | 0    | CMR  | CLPS | 00             |

| Audio switches ADC              | 0C   | MONO             | SEA2 | SEA1 | SEA0 | MNM1  | PRA2 | PRA1 | PRA0 | 00             |

| Audio switches 0                | 0D   | DSG              | A1S2 | A1S1 | A1S0 | MNM0  | A0S2 | A0S1 | A0S0 | 00             |

| Audio switches 1                | 0E   | 0                | M2G  | AMX  | M1G  | MICON | A2S2 | A2S1 | A2S0 | 00             |

| IRQ mask status byte 0          | 0F   | 1 <sup>(1)</sup> | IM6  | IM5  | IM4  | IM3   | IM2  | IM1  | IMO  | 80             |

#### Note

1. The value of this bit cannot be changed.

PNX3000

Table 5 AFC switch

| AFN | MODE             |

|-----|------------------|

| 0   | normal operation |

| 1   | AFC not active   |

#### Table 6 AFC window

| AFW | AFC WINDOW |

|-----|------------|

| 0   | normal     |

| 1   | enlarged   |

#### Table 7 IF sensitivity

| IFS | IF SENSITIVITY |

|-----|----------------|

| 0   | normal         |

| 1   | reduced        |

#### Table 8 Internal or external AGC mode

| AGCM | MODE     |

|------|----------|

| 0    | internal |

| 1    | external |

#### Table 9 Fast filter IF PLL

| FFI | CONDITION               |

|-----|-------------------------|

| 0   | normal time constant    |

| 1   | increased time constant |

#### Table 10 Video modulation standard

| PMOD | CONDITION                      |

|------|--------------------------------|

| 0    | negative modulation (FM sound) |

| 1    | positive modulation (AM sound) |

#### Table 11 IF AGC speed

| AGC1 | AGC0 | AGC SPEED         |

|------|------|-------------------|

| 0    | 0    | $0.7 \times norm$ |

| 0    | 1    | norm              |

| 1    | 0    | 3 × norm          |

| 1    | 1    | 6 × norm          |

#### Table 12 IF amplifier on/off

| IFON | MODE                    |  |

|------|-------------------------|--|

| 0    | IF amplifier not active |  |

| 1    | normal operation        |  |

#### Table 13 Selection of signal on analog DTV output

| DSIF | DFIF | MODE             | LPF<br>ACTIVE |

|------|------|------------------|---------------|

| 0    | 0    | DTV second IF    | Υ             |

| 0    | 1    | DTV first IF     | N             |

| 1    | 0    | 2nd SIF internal | N             |

| 1    | 1    | spare            | N/A           |

#### Table 14 Vision IF input select

| DTV | MODE        |

|-----|-------------|

| 0   | VIF input   |

| 1   | DTVIF input |

#### Table 15 Calibration of IF PLL demodulator

| IFLH | MODE                          |

|------|-------------------------------|

| 0    | calibration system active     |

| 1    | calibration system not active |

#### Table 16 IF PLL mode

| SYNT | MODE             |  |

|------|------------------|--|

| 0    | normal mode      |  |

| 1    | synthesizer mode |  |

#### Table 17 Second sound IF input

| SSIF | MODE           |

|------|----------------|

| 0    | internal input |

| 1    | external input |

#### Table 18 Sound operation

| QSS | MODE               |

|-----|--------------------|

| 0   | intercarrier sound |

| 1   | quasi split sound  |

PNX3000

Table 19 IF AGC operation mode

| IFGT | MODE                    |  |

|------|-------------------------|--|

| 0    | non gated operation     |  |

| 1    | gated operation; note 1 |  |

#### Note

Gated operation improves weak signal performance. Gated operation is automatically disabled if CVBS\_IF is not selected as primary or secondary video signal. In this situation bit IFLH should be set to 1 to avoid recalibration of the IF VCO for white video patterns.

**Table 20** CVBS IF output signal amplitude correction for system I

| VAI | MODE           |                |

|-----|----------------|----------------|

|     | PMOD = 0       | PMOD = 1       |

| 0   | no correction  | no correction  |

| 1   | amplitude +8 % | amplitude -8 % |

Table 21 IF PLL offset adjustment

| IFO5 TO IFO0<br>(HEX) | CONTROL       |

|-----------------------|---------------|

| 00                    | tbf           |

| 20                    | no correction |

| 3F                    | tbf           |

Table 22 CVBS IF output signal amplitude

| VA1 | \/^0 | OUTPUT SIGNAL AMPLITUDE |                |

|-----|------|-------------------------|----------------|

| VAI | VA0  | PMOD = 0                | PMOD = 1       |

| 0   | 0    | no correction           | no correction  |

| 0   | 1    | spare                   | spare          |

| 1   | 0    | amplitude -5 %          | amplitude +5 % |

| 1   | 1    | amplitude +5 %          | amplitude -5 % |

Table 23 IF AGC tuner take over

| TTO5 TO TTO0<br>(HEX) | CONTROL                                      |

|-----------------------|----------------------------------------------|

| 3F                    | tuner take over at IF input signal of 0.4 mV |

| 00                    | tuner take over at IF input signal of 80 mV  |

Table 24 External reference frequency

| FXT | CONDITION |

|-----|-----------|

| 0   | 13.5 MHz  |

| 1   | 27 MHz    |

Table 25 PLL demodulator frequency setting

| IFA | IFB | IFC | IF FREQUENCY |

|-----|-----|-----|--------------|

| 0   | 0   | 0   | 58.75 MHz    |

| 0   | 0   | 1   | 45.75 MHz    |

| 0   | 1   | 0   | 38.90 MHz    |

| 0   | 1   | 1   | 38.00 MHz    |

| 1   | 0   | 0   | 33.40 MHz    |

| 1   | 1   | 0   | 33.90 MHz    |

**Table 26** IF VCO synthesizer frequency (SF7 to SF0); note 1

| SF7 TO SF0<br>(DECIMAL<br>NUMBER) | FREQUENCY  |

|-----------------------------------|------------|

| 95                                | f = 24 MHz |

| 255                               | f = 64 MHz |

#### Note

1.  $f_{synth} = (N + 1) \times 250 \text{ kHz}$ ; where  $95 \le N \le 255$ .

Table 27 Bypass UV anti-alias filters

| BPUV | MODE                         |  |

|------|------------------------------|--|

| 0    | normal operation             |  |

| 1    | UV anti-alias filters bypass |  |

Table 28 Bypass Y<sub>yuv</sub> anti-alias filter

| BPY | MODE                                      |  |

|-----|-------------------------------------------|--|

| 0   | normal operation                          |  |

| 1   | Y <sub>yuv</sub> anti-alias filter bypass |  |

Table 29 Bypass anti-alias filters of primary CVBS

| ВРР | MODE                                   |  |

|-----|----------------------------------------|--|

| 0   | normal operation                       |  |

| 1   | primary CVBS anti-alias filters bypass |  |

PNX3000

Table 30 Group delay correction

| GD | MODE                          |

|----|-------------------------------|

| 0  | group delay correction bypass |

| 1  | group delay correction active |

Table 31 2nd SIF LPF mode

| SLPM | MODE                                       |

|------|--------------------------------------------|

| 0    | 2nd SIF LPF active                         |

| 1    | 2nd SIF LPF bypass (for FM radio 10.7 MHz) |

Table 32 Bypass anti-alias filters of secondary CVBS

| BPS | MODE                                     |

|-----|------------------------------------------|

| 0   | normal operation                         |

| 1   | secondary CVBS anti-alias filters bypass |

Table 33 Sound trap frequency

| ST1 | ST0 | FREQUENCY |

|-----|-----|-----------|

| 0   | 0   | 5.5 MHz   |

| 0   | 1   | 4.5 MHz   |

| 1   | 0   | 6.0 MHz   |

| 1   | 1   | 6.5 MHz   |

Table 34 Data link transmitter test mode

| DRND | MODE                            |

|------|---------------------------------|

| 0    | normal operation                |

| 1    | pseudo random test mode; note 1 |

#### Note

The pseudo random mode can be used for in-circuit testing of the data link connections between data link transmitter in the analog front end IC and data link receiver in the digital video processor IC.

Table 35 YUV 2f<sub>H</sub> clamp pulse timing

| HDTV | MODE                        |

|------|-----------------------------|

| 0    | normal timing (480p signal) |

| 1    | HDTV timing (1080i signal)  |

Table 36 Data link modes; note 1

| DM | APPLICATION         | MODE |

|----|---------------------|------|

| 0  | Normal              | 0    |

| 1  | YUV 2f <sub>H</sub> | 1    |

#### Note

1. See Table 2 in Chapter "Functional description".

Table 37 Selection of secondary video signal

| SEC3 | SEC2 | SEC1 | SEC0 | SELECTED<br>SIGNAL |

|------|------|------|------|--------------------|

| 0    | 0    | 0    | 0    | CVBS_IF            |

| 0    | 0    | 0    | 1    | CVBS1              |

| 0    | 0    | 1    | 0    | CVBS2              |

| 0    | 0    | 1    | 1    | CVBS3              |

| 1    | 0    | 1    | 1    | Y + C3             |

| 0    | 1    | 0    | 0    | CVBS4              |

| 1    | 1    | 0    | 0    | Y + C4             |

| 0    | 1    | 0    | 1    | CVBS_DTV           |

|      | oth  | ner  |      | CVBS_IF            |

Table 38 Selection of primary video channel

| PRI3 | PRI2 | PRI1 | PRI0 | SELECTED<br>SIGNAL |

|------|------|------|------|--------------------|

| 0    | 0    | 0    | 0    | CVBS_IF            |

| 0    | 0    | 0    | 1    | CVBS1              |

| 0    | 0    | 1    | 0    | CVBS2              |

| 0    | 0    | 1    | 1    | CVBS3              |

| 1    | 0    | 1    | 1    | Y + C3             |

| 0    | 1    | 0    | 0    | CVBS4              |

| 1    | 1    | 0    | 0    | Y + C4             |

| 1    | 1    | 1    | 0    | YC_COMB            |

|      | oth  | ner  |      | CVBS_IF            |

Table 39 Video ident mode

| VIM | MODE                                          |

|-----|-----------------------------------------------|

| 0   | ident coupled to CVBS_IF                      |

| 1   | ident coupled to selected primary CVBS signal |

Table 40 IF video mute

| vsw | MODE             |  |

|-----|------------------|--|

| 0   | normal operation |  |

| 1   | CVBSOUTIF muted  |  |

PNX3000

Table 41 Clamp mode secondary CVBS channel

| CMS | MODE                      |  |

|-----|---------------------------|--|

| 0   | top sync clamping mode    |  |

| 1   | black level clamping mode |  |

Table 42 Clamp mode primary CVBS channel

| СМР | MODE                      |  |  |

|-----|---------------------------|--|--|

| 0   | top sync clamping mode    |  |  |

| 1   | black level clamping mode |  |  |

Table 43 Selection of CVBS output A

| CVA3  | CVA2 | CVA1 | CVA0 | SELECTED<br>SIGNAL |

|-------|------|------|------|--------------------|

| 0     | 0    | 0    | 0    | CVBS_IF            |

| 0     | 0    | 0    | 1    | CVBS1              |

| 0     | 0    | 1    | 0    | CVBS2              |

| 0     | 0    | 1    | 1    | CVBS3              |

| 1     | 0    | 1    | 1    | Y + C3             |

| 0     | 1    | 0    | 0    | CVBS4              |

| 1     | 1    | 0    | 0    | Y + C4             |

| 0     | 1    | 0    | 1    | CVBS_DTV           |

| other |      |      |      | output muted       |

Table 44 Mute SCART2 audio output

| MA2 | MODE                      |  |  |

|-----|---------------------------|--|--|

| 0   | normal operation          |  |  |

| 1   | SCART2 audio output muted |  |  |

Table 45 Mute SCART1 audio output

| MA1 | MODE                      |

|-----|---------------------------|

| 0   | normal operation          |

| 1   | SCART1 audio output muted |

Table 46 Mute LINE audio output

| MA0 | MODE                    |  |

|-----|-------------------------|--|

| 0   | normal operation        |  |

| 1   | LINE audio output muted |  |

Table 47 Selection of CVBS output B

| CVB3 | CVB2 | CVB1         | CVB0 | SELECTED<br>SIGNAL |

|------|------|--------------|------|--------------------|

| 0    | 0    | 0            | 0    | CVBS_IF            |

| 0    | 0    | 0            | 1    | CVBS1              |

| 0    | 0    | 1            | 0    | CVBS2              |

| 0    | 0    | 1            | 1    | CVBS3              |

| 1    | 0    | 1            | 1    | Y + C3             |

| 0    | 1    | 0            | 0    | CVBS4              |

| 1    | 1    | 0            | 0    | Y + C4             |

| 0    | 1    | 0            | 1    | CVBS_DTV           |

|      | oth  | output muted |      |                    |

Table 48 Selection of RGB/YUV input

| RSEL | SELECTED SIGNAL |  |

|------|-----------------|--|

| 0    | RGB1 input      |  |

| 1    | RGB2 input      |  |

Table 49 RGB/YUV input mode

| MAT | DVD | MODE                |

|-----|-----|---------------------|

| 0   | 0   | YUV input; note 1   |

| 0   | 1   | YPbPr input; note 2 |

| 1   | 0   | RGB input; note 3   |

| 1   | 1   | spare               |

#### **Notes**

- YUV input is an Y, –(B–Y) and –(R–Y) input with the specification:

- a) Y = 1.43 V (p-p); U = 1.33 V (p-p); V = 1.05 V (p-p).

- b) These signal amplitudes are based on a colour bar signal with 75 % saturation.

- 2. YPbPr input with the specification:

- a) Y = 1.0 V (p-p); Pb = 0.7 V (p-p); Pr = 0.7 V (p-p).

- b) These signal amplitudes are based on a colour bar signal with 100 % saturation.

- 3. RGB input with the specification:

- a)  $R = 0.7 \times V_{B-W}$ ;  $G = 0.7 \times V_{B-W}$ ;  $B = 0.7 \times V_{B-W}$ .

- b) These signal amplitudes are based on a colour bar signal with 100 % saturation.

### Analog front end for digital video processors

PNX3000

Table 50 Clamp mode for RGB and YUV signals

| CMR | MODE                   |  |  |

|-----|------------------------|--|--|

| 0   | top sync clamp mode    |  |  |

| 1   | black level clamp mode |  |  |

Table 51 Clamp pulse selection for RGB and YUV signals

| CLPS | MODE                             |  |  |

|------|----------------------------------|--|--|

| 0    | clamp pulse of primary channel   |  |  |

| 1    | clamp pulse of secondary channel |  |  |

Table 52 Selection of secondary audio channel

| SEA2 | SEA1 | SEA0 | SELECTED SIGNAL                    |

|------|------|------|------------------------------------|

| 0    | 0    | 0    | AMint (L) and AMext (R);<br>note 1 |

| 0    | 0    | 1    | L1 and R1                          |

| 0    | 1    | 0    | L2 and R2                          |

| 0    | 1    | 1    | L3 and R3                          |

| 1    | 0    | 0    | L4 and R4                          |

| 1    | 0    | 1    | L5 and R5                          |

| 1    | 1    | 0    | MIC1 (L) and MIC2 (R)              |

| 1    | 1    | 1    | AMext (L) and AMint (R);<br>note 1 |

#### Note

1. Selection between AMint and AMext must be done by digital video processor.

Table 53 Secondary audio channel mode

| MONO | MNM1 | MNM0 | MODE                              |

|------|------|------|-----------------------------------|

| 0    | _    | _    | stereo; see Table 52              |

| 1    | 0    | 0    | mono (L) and AMint (R);<br>note 1 |

| 1    | 0    | 1    | mono (L) and AMext (R);<br>note 1 |

| 1    | 1    | 0    | mono (L) and MIC1 (R);<br>note 1  |

| 1    | 1    | 1    | mono (L) and MIC2 (R);<br>note 1  |

#### Note

Mono is (L + R)/2; when AM is selected in Table 52, mono is AMint for SEA[2:0] = 000 and AMext for SEA[2:0] = 111. A more comprehensive table can be found in the application note.

Table 54 Selection of primary audio channel

| PRA2 | PRA1 | PRA0 | SELECTED SIGNAL                    |

|------|------|------|------------------------------------|

| 0    | 0    | 0    | AMint (L) and AMext (R);<br>note 1 |

| 0    | 0    | 1    | L1 and R1                          |

| 0    | 1    | 0    | L2 and R2                          |

| 0    | 1    | 1    | L3 and R3                          |

| 1    | 0    | 0    | L4 and R4                          |

| 1    | 0    | 1    | L5 and R5                          |

| 1    | 1    | 1    | AMext (L) and AMint (R);<br>note 1 |

#### Note

Selection between AMint and AMext must be done by digital video processor.

Table 55 Gain from DSND inputs to SCART outputs

| DSG | GAIN                                   |

|-----|----------------------------------------|

| 0   | 0 dB; to be used with 5 V audio supply |

| 1   | 6 dB; to be used with 8 V audio supply |

Table 56 Selection of SCART1 audio output

| AMX | A1S2 | A1S1 | A1S0 | SELECTED<br>SIGNAL |

|-----|------|------|------|--------------------|

| 0   | 0    | 0    | 0    | AMint              |

| 0   | 0    | 0    | 1    | LR1                |

| 0   | 0    | 1    | 0    | LR2                |

| 0   | 0    | 1    | 1    | LR3                |

| 0   | 1    | 0    | 0    | LR4                |

| 0   | 1    | 0    | 1    | LR5                |

| 0   | 1    | 1    | 0    | DSND1              |

| 0   | 1    | 1    | 1    | DSND2              |

| 1   | 0    | 0    | 0    | AMext              |

### Analog front end for digital video processors

PNX3000

Table 57 Selection of LINE audio output

| АМХ | A0S2 | A0S1 | A0S0 | SELECTED<br>SIGNAL |

|-----|------|------|------|--------------------|

| 0   | 0    | 0    | 0    | AMint              |

| 0   | 0    | 0    | 1    | LR1                |

| 0   | 0    | 1    | 0    | LR2                |

| 0   | 0    | 1    | 1    | LR3                |

| 0   | 1    | 0    | 0    | LR4                |

| 0   | 1    | 0    | 1    | LR5                |

| 0   | 1    | 1    | 0    | DSND1              |

| 0   | 1    | 1    | 1    | DSND2              |

| 1   | 0    | 0    | 0    | AMext              |

Table 58 Microphone input 2 gain

| M2G | GAIN |

|-----|------|

| 0   | low  |

| 1   | high |

Table 59 Microphone input 1 gain

| M1G | GAIN |

|-----|------|

| 0   | low  |

| 1   | high |

Table 60 Microphone amplifiers on/off

| MICON | MODE                             |

|-------|----------------------------------|

| 0     | microphone amplifiers not active |

| 1     | normal operation                 |

Table 61 Selection of SCART2 audio output

| AMX | A2S2 | A2S1 | A2S0 | SELECTED<br>SIGNAL |

|-----|------|------|------|--------------------|

| 0   | 0    | 0    | 0    | AMint              |

| 0   | 0    | 0    | 1    | LR1                |

| 0   | 0    | 1    | 0    | LR2                |

| 0   | 0    | 1    | 1    | LR3                |

| 0   | 1    | 0    | 0    | LR4                |

| 0   | 1    | 0    | 1    | LR5                |

| 0   | 1    | 1    | 0    | DSND1              |

| 0   | 1    | 1    | 1    | DSND2              |

| 1   | 0    | 0    | 0    | AMext.             |

Table 62 IRQ mask bits for status byte 0

| IM6 TO IM0 | IRQ OUTPUT <sup>(1)</sup>                                               |

|------------|-------------------------------------------------------------------------|

| 0          | IRQ output not activated                                                |

| 1          | IRQ output is activated when the corresponding status bit changes value |

#### Note

1. The IRQ output is always activated if status bit POR = 1.

8.2 Output status registers

Table 63 Output status registers; subaddresses must not be sent, they are automatically incremented

| FUNCTION      | SUB  | DATA BYTE |      |      |     |      |     |     |     |

|---------------|------|-----------|------|------|-----|------|-----|-----|-----|

| FUNCTION      | ADDR | D7        | D6   | D5   | D4  | D3   | D2  | D1  | D0  |

| Status byte 0 | 00   | POR       | MSUP | ASUP | ROK | LOCK | VID | AFA | AFB |

| Status byte 1 | 01   | 0         | 0    | 0    | 0   | 0    | DCF | 0   | AGC |

| Reserved      | 02   | 0         | 0    | 0    | 0   | 0    | 0   | 0   | 0   |

| Status byte 3 | 03   | ID7       | ID6  | ID5  | ID4 | ID3  | ID2 | ID1 | ID0 |

### Analog front end for digital video processors

PNX3000

Table 64 Power-on-reset

| POR | CONDITION  |

|-----|------------|

| 0   | normal     |

| 1   | Power-down |

#### Table 65 Main supply

| MSUP | CONDITION          |

|------|--------------------|

| 0    | main supply not OK |

| 1    | main supply OK     |

#### Table 66 Audio supply

| ASUP | CONDITION           |  |

|------|---------------------|--|

| 0    | audio supply not OK |  |

| 1    | audio supply OK     |  |

#### Table 67 Reference frequency

| ROK | CONDITION                       |

|-----|---------------------------------|

| 0   | reference frequency not present |

| 1   | reference frequency present     |

#### Table 68 IF PLL lock indication

| LOCK | INDICATION        |

|------|-------------------|

| 0    | IF PLL not locked |

| 1    | IF PLL locked     |

#### Table 69 Video identification

| VID | INDICATION               |  |

|-----|--------------------------|--|

| 0   | no video signal detected |  |

| 1   | video signal detected    |  |

#### Table 70 AFC output

| AFA | AFB | CONDITION                  |

|-----|-----|----------------------------|

| 0   | 0   | outside window; too low    |

| 0   | 1   | outside window; too high   |

| 1   | 0   | in window; below reference |

| 1   | 1   | in window; above reference |

#### Table 71 Data link current test

| DCF | INDICATION                  |  |

|-----|-----------------------------|--|

| 0   | data link current test OK   |  |

| 1   | data link current test FAIL |  |

#### Table 72 Tuner AGC output

| AGC | INDICATION                  |

|-----|-----------------------------|

| 0   | tuner gain reduction active |

| 1   | no gain reduction of tuner  |

#### Table 73 Mask version indication

| ID7 | ID6 | ID5 | ID4 | ID3 | MASK VERSION       |

|-----|-----|-----|-----|-----|--------------------|

| 0   | 0   | 0   | 0   | 0   | N1A or N1B version |

| 0   | 0   | 0   | 0   | 1   | _                  |

| 0   | 0   | 0   | 1   | 0   | N1C version        |

| 0   | 0   | 0   | 1   | 1   | N1D version        |

| 0   | 0   | 1   | 0   | 0   | N1E or N1F version |

| 0   | 0   | 1   | 0   | 1   | N2B version        |

| 0   | 0   | 1   | 1   | 0   | N3B version        |

### Analog front end for digital video processors

PNX3000

#### 9 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL                                           | PARAMETER                       | CONDITIONS                                     | MIN. | MAX.  | UNIT |

|--------------------------------------------------|---------------------------------|------------------------------------------------|------|-------|------|

| V <sub>P</sub>                                   | main supply voltage             |                                                | _    | 6.0   | V    |

| V <sub>CC(1ASW)</sub> ,<br>V <sub>CC(2ASW)</sub> | audio supply voltage            |                                                | _    | 9.0   | V    |

| T <sub>stg</sub>                                 | storage temperature             |                                                | -25  | +150  | °C   |

| T <sub>amb</sub>                                 | ambient temperature             |                                                | 0    | 70    | °C   |

| T <sub>sol</sub>                                 | soldering temperature           | for 5 s                                        | _    | 260   | °C   |

| Tj                                               | operating junction temperature  |                                                | _    | 150   | °C   |

| V <sub>esd</sub>                                 | electrostatic discharge voltage | Human Body Model; C = 100 pF; R = 1.5 kΩ       |      |       |      |

|                                                  |                                 | pin SDA                                        | _    | ±1500 | V    |

|                                                  |                                 | all other pins                                 | _    | ±2000 | V    |

|                                                  |                                 | Machine Model; C = 200 pF;<br>R = 0 k $\Omega$ | _    |       |      |

|                                                  |                                 | pin SDA                                        | _    | ±150  | V    |

|                                                  |                                 | all other pins                                 | _    | ±200  | V    |

#### 10 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS          | VALUE | UNIT |

|----------------------|---------------------------------------------|---------------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; note 1 | 30    | K/W  |

#### Note

1. The value given for the thermal resistance from junction to ambient should only be considered as an indication. Most of the dissipated heat is conveyed to the ambient air through the Printed-Circuit Board (PCB) on which the IC is mounted. The actual value of the thermal resistance depends on the number of metal layers, size and layout of the PCB, and also on the dissipation of other components on the PCB.

#### 11 QUALITY SPECIFICATION

In accordance with document "SNW-FQ-611".

#### 11.1 Latch-up performance

At T<sub>amb</sub> = 70 °C all pins meet the following specification:

- Positive stress test:  $I_{trigger} \ge 100$  mA or  $V_{trigger} \ge 1.5$   $V_{P(max)}$

- Negative stress test:  $I_{trigger} \le -100$  mA or  $V_{trigger} \le -0.5$   $V_{P(max)}$ .

# Analog front end for digital video processors

PNX3000

#### 12 CHARACTERISTICS

$V_{CC}$  = 5 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL                                           | PARAMETER                                       | CONDITIONS                                                                           | MIN.        | TYP.           | MAX.              | UNIT           |

|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|-------------|----------------|-------------------|----------------|

| Supplies                                         | -                                               | 1                                                                                    | <u>'</u>    | '              | '                 |                |

| Power Suppl                                      | JES                                             |                                                                                      |             |                |                   |                |

| V <sub>P</sub>                                   | main supply voltage                             |                                                                                      | 4.75        | 5.0            | 5.25              | V              |

| I <sub>P</sub>                                   | main supply current                             |                                                                                      | -           | 285            | 320               | mA             |

| V <sub>CC(1ASW)</sub> ,<br>V <sub>CC(2ASW)</sub> | audio supply voltage                            | note 1                                                                               | 4.75        | 8.0            | 8.4               | V              |

| I <sub>CC(ASW)</sub>                             | audio supply current                            | note 1                                                                               | _           | 3.5            | 5.0               | mA             |