# 9600

Data Compression Processor

**Data Sheet**

#### DS-0002-01, © 2003, Hi/fn<sup>®</sup>, Inc. All rights reserved. 2/03

No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the written permission of Hi/fn, Inc. ("Hifn")

#### Licensing and Government Use

Any Hifn software ("Licensed Programs") described in this document is furnished under a license and may be used and copied only in accordance with the terms of such license and with the inclusion of this copyright notice. Distribution of this document or any copies thereof and the ability to transfer title or ownership of this document's contents are subject to the terms of such license.

Such Licensed Programs and their documentation have been developed at private expense and no part of such Licensed Programs is in the public domain. Use, duplication, disclosure, and acquisition by the U.S. Government of such Licensed Programs is subject to the terms and definitions of their applicable license.

#### Disclaimer

Hifn reserves the right to make changes to its products, including the contents of this document, or to discontinue any product or service without notice. Hifn advises its customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied upon is current. Every effort has been made to keep the information in this document current and accurate as of the date of this document's publication or revision.

Hifn warrants performance of its products to the specifications applicable at the time of sale in accordance with Hifn's standard warranty or the warranty provisions specified in any applicable license. Testing and other quality control techniques are utilized to the extent Hifn deems necessary to support such warranty. Specific testing of all parameters, with the exception of those mandated by government requirements, of each product is not necessarily performed.

Certain applications using Hifn products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications"). Hifn products are not designed, intended, authorized, or warranted to be suitable for use in life saving, or life support applications, devices or systems or other critical applications. Inclusion of Hifn products in such critical applications is understood to be fully at the risk of the customer. Questions concerning potential risk applications should be directed to Hifn through a local sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals," should be validated for each customer application by the customer's technical experts.

Hifn does not warrant that its products are free from infringement of any patents, copyrights or other proprietary rights of third parties. In no event shall Hifn be liable for any special, incidental or consequential damages arising from infringement or alleged infringement of any patents, copyrights or other third party intellectual property rights.

The use of this product in stateful compression protocols (for example, PPP or multi-history applications) with certain configurations may require a license from Motorola. In such cases, a license agreement for the right to use Motorola patents may be obtained through Hifn or directly from Motorola.

#### Patents

May include one or more of the following United States patents: 4,701,745; 5,003,307; 5,016,009; 5,126,739; 5,146,221; 5,414,425; 5,463,390; 5,506,580; and 5,5532,694. Other patents pending.

#### **Trademarks**

$Hi/fn^{\text{(B)}}$ , MeterFlow<sup>(B)</sup>, MeterWorks<sup>(B)</sup>, and LZS<sup>(B)</sup>, are registered trademarks of Hi/fn, Inc. Hifn<sup>TM</sup> and the Hifn logo are trademarks of Hi/fn, Inc. All other trademarks and trade names are the property of their respective holders.

#### Exporting

This product may only be exported from the United States in accordance with applicable Export Administration Regulations. Diversion contrary to United States laws is prohibited.

| <br> |  |

|------|--|

| 1.   |  |

|      |  |

|      |  |

. . . . . . .

## Contents

. . . . . . . . .

| List of | Figure    | s          | • • • • • |             | • • • •   | ••• | •••  | ••• | •••     | • •   | • • •   | • •       | ••• | ••      | vii  |

|---------|-----------|------------|-----------|-------------|-----------|-----|------|-----|---------|-------|---------|-----------|-----|---------|------|

| List of | Table     |            |           |             |           | ••• |      |     |         |       |         | •••       | ••• |         | . ix |

| Prefac  | e         |            |           |             |           |     |      |     |         |       |         |           |     |         | . xi |

| Abou    | t This Do | ocument .  |           | •••••       |           |     |      |     |         |       |         |           |     |         | xi   |

| Audi    | ence      |            |           |             |           |     |      |     |         |       |         |           |     |         | xi   |

| Docu    | ment Co   | nventions  |           |             |           |     |      |     |         |       |         |           |     |         | xi   |

| Cust    | omer Sur  | oport      |           |             |           |     |      |     |         |       |         |           |     |         | xi   |

|         | -         |            |           |             |           |     |      |     |         |       |         |           |     |         |      |

|         |           |            |           |             |           |     |      |     |         |       |         |           |     |         |      |

| List of | Abbre     | viations   | and /     | Acro        | nym       | s.  |      |     |         |       |         |           |     |         | xiii |

|         |           |            |           |             | ·         |     |      |     |         |       |         |           |     |         |      |

| Chapte  | er 1      | Overvie    | w         |             |           |     |      |     |         |       |         |           |     |         | 1    |

| 1.1     | 9600 E    | escription |           |             |           |     |      |     |         |       |         |           |     |         | 1    |

| 1.2     |           | eatures    |           |             |           |     |      |     |         |       |         |           |     |         |      |

| 1.3     | Produc    | t Overviev | v         |             |           |     |      |     | • • • • |       | • • • • | •••       |     | · • • • | . 2  |

| 1.4     | Detaile   | ed Block D | iagram    | 1 <b></b> . |           |     |      |     | •••     |       | •••     | •••       |     | •••     | . 4  |

| 1.5     | Signal    | Summary    |           | ••••        |           |     |      |     | •••     | • • • | • • • • | •••       |     | •••     | . 5  |

| 1.6     | Registe   | er Summa   | ry        |             | • • • • • |     | •••• |     | •••     | •••   | ••••    | •••       | ••• | •••     | . 6  |

| Chapte  | er 2      | Operati    | on        |             |           |     |      |     |         |       |         |           |     |         | 7    |

| 2.1     | Record    | s          |           |             |           |     |      |     |         |       |         |           |     |         | 7    |

| 2.2     | Comm      | ands       |           |             |           |     |      |     |         |       |         |           |     |         | 7    |

| 2.3     | Comm      | and and R  | ecord T   | lermin      | nation    |     |      |     | •••     |       |         | , <b></b> |     |         | 8    |

|         | 2.3.1     | Commar     | nd Tern   | ninatio     | on        |     |      |     | •••     |       |         | , <b></b> |     |         | . 8  |

|         | 2.3.2     | Record 7   | ermina    | ation .     |           |     |      |     |         |       |         | •••       | ••• |         | . 8  |

|         | 2.3.3     | Results.   |           |             |           |     |      |     | •••     |       | • • • • | •••       |     |         | , 9  |

| 2.4     | Compr     | ession     |           | ••••        |           |     |      |     |         |       | • • • • | •••       |     | •••     | . 10 |

. . . . . . . . . . . .

•

|         | 2.4.1   | Compression, Step by Step 12                              |

|---------|---------|-----------------------------------------------------------|

| 2.5     | Compr   | ession History                                            |

| 2.6     | Decom   | pression                                                  |

|         | 2.6.1   | Decompression, Step by Step 14                            |

| 2.7     | Error H | Iandling                                                  |

| 2.8     | CRC/L   | CB Calculation                                            |

|         | 2.8.1   | CRC/LCB Algorithms                                        |

|         | 2.8.2   | Protected Records 17                                      |

| 2.9     | Feedba  | ck Mode                                                   |

|         | 2.9.1   | Errors in Feedback Mode 19                                |

|         | 2.9.2   | Feedback Mode Compression, Step by Step         19        |

| 2.10    | Data a  | nd Register Transfer                                      |

|         | 2.10.1  | DMA 20                                                    |

|         | 2.10.2  | Programmed I/O                                            |

|         | 2.10.3  | Mixing Programmed I/O and DMA transfers                   |

|         | 2.10.4  | Data Alignment Requirements23                             |

|         | 2.10.5  | Requirements for Writing to the Source FIFO               |

|         | 2.10.6  | Characteristics When Reading From the Destination FIFO 25 |

| 2.11    | FIFO I  | Data Flow                                                 |

|         | 2.11.1  | Source FIFO Data Flow                                     |

|         | 2.11.2  | Destination FIFO Data Flow                                |

| 2.12    | FIFO 7  | Thresholds                                                |

|         | 2.12.1  | Programmed I/O and the FIFOs 27                           |

| 2.13    | Clock . |                                                           |

|         |         |                                                           |

| Chapter | r 3     | Register Descriptions29                                   |

| 3.1     |         | er Overview                                               |

| 3.2     | Data (  |                                                           |

| 3.3     |         | and (1)                                                   |

| 0.0     | 3.3.1   | Commands                                                  |

|         | 3.3.2   | Command Fields                                            |

| 3.4     |         | (2,10)                                                    |

| 0.1     | 3.4.1   | CRC Error                                                 |

|         | 3.4.2   | CRC Value                                                 |

|         | 3.4.3   | Record Count       35                                     |

|         | 3.4.4   | Consumed Byte Count                                       |

|         | 3.4.5   | Destination Count                                         |

| 3.5     |         | uration (3)                                               |

| 2.0     | 3.5.1   | Feedback Mode   36                                        |

|         |         |                                                           |

#### \_ ents

| 1112 |     |    |   |     |    |   |   |   |   |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |     |    |   |   |   |   |   |   |   |   |   | C | on | te  | nt  | S |

|------|-----|----|---|-----|----|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|----|---|---|---|---|---|---|---|---|---|---|----|-----|-----|---|

| Hifn | ••• | •• | • | • • | •• | • | • | • | • | ••• | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • • | •• | • | • | • | • | • | • | • | • | • | • | •  | • • | • • | • |

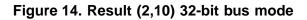

|         | 3.5.2    | Bus Width                               | 36 |

|---------|----------|-----------------------------------------|----|

|         | 3.5.3    | Big Endian                              | 36 |

|         | 3.5.4    | Reset                                   | 37 |

| 3.6     | Interruj | pt Enable (4,12)                        | 37 |

|         | 3.6.1    | Parity Error Interrupt Enable           | 37 |

|         | 3.6.2    | Command Ready Interrupt Enable          | 38 |

|         | 3.6.3    | SDREQ Interrupt Enable                  | 38 |

|         | 3.6.4    | DDREQ Interrupt Enable                  | 38 |

|         | 3.6.5    | Command/Result Overrun Interrupt Enable | 38 |

|         | 3.6.6    | Data Error Interrupt Enable             | 38 |

|         | 3.6.7    | CRC Error Interrupt Enable              | 38 |

| 3.7     | Status ( | 5,13)                                   | 38 |

|         | 3.7.1    | Parity Error                            | 39 |

|         | 3.7.2    | Command Ready                           | 39 |

|         | 3.7.3    | SDREQ                                   | 39 |

|         | 3.7.4    | DDREQ                                   | 39 |

|         | 3.7.5    | Command/Result Overrun                  | 40 |

|         | 3.7.6    | Data Error                              | 40 |

|         | 3.7.7    | CRC Error                               | 40 |

|         | 3.7.8    | Command In Progress                     | 40 |

|         | 3.7.9    | Result In Progress                      | 40 |

|         | 3.7.10   | Byte Enable                             | 40 |

|         | 3.7.11   | EOR                                     | 41 |

| 3.8     |          | onfiguration (7)                        |    |

|         | 3.8.1    | U/L                                     | 42 |

|         | 3.8.2    | Source FIFO Threshold                   | 42 |

|         | 3.8.3    | Destination FIFO Threshold              | 43 |

| 3.9     | Chip ID  | (11)                                    | 43 |

| Chapter | · 4   §  | Signal Descriptions                     | 45 |

| 4.1     | CPU Int  | terface                                 | 45 |

|         | 4.1.1    | System Data Bus (D[31-0]).              | 45 |

|         | 4.1.2    | Parity ([3-0])                          | 45 |

|         | 4.1.3    | Address (A[3-0])                        | 45 |

|         | 4.1.4    | Read/Write Command (R/W#)               | 45 |

|         | 4.1.5    | Command Strobe (CS#)                    | 46 |

|         | 4.1.6    | Interrupt (IRQ#)                        | 46 |

| 4.2     | DMA In   | terface                                 | 46 |

|         | 4.2.1    | Byte Enable (B[3-0])                    | 46 |

•

|         | 4.2.2    | DMA Ready (RDY#)                       | 46  |

|---------|----------|----------------------------------------|-----|

|         | 4.2.3    | End of Command (EOC#)                  | 47  |

|         | 4.2.4    | End of Record (EOR#)                   | 47  |

|         | 4.2.5    | Source FIFO DMA Request (SDREQ1#)      | 47  |

|         | 4.2.6    | Source DMA Acknowledge (SDACK1#)       | 47  |

|         | 4.2.7    | Destination FIFO DMA Request (DDREQ1#) | 47  |

|         | 4.2.8    | Destination DMA Acknowledge (DDACK1#)  | 48  |

|         | 4.2.9    | Command Ready                          | 48  |

| 4.3     | Miscell  | aneous Signals                         | .48 |

|         | 4.3.1    | Reset (RESET#)                         | 48  |

|         | 4.3.2    | Clock (CLK).                           | 48  |

|         | 4.3.3    | DIV1, DIV0                             | 48  |

| Chantar | <u> </u> |                                        | 40  |

| Chapter | Э        | Timing Descriptions                    | 49  |

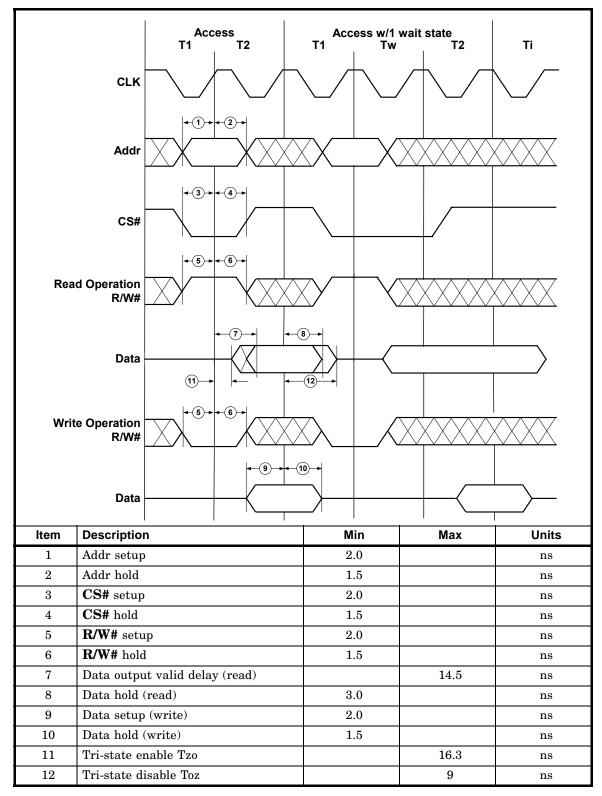

| 5.1     | CPU In   | terface                                | .49 |

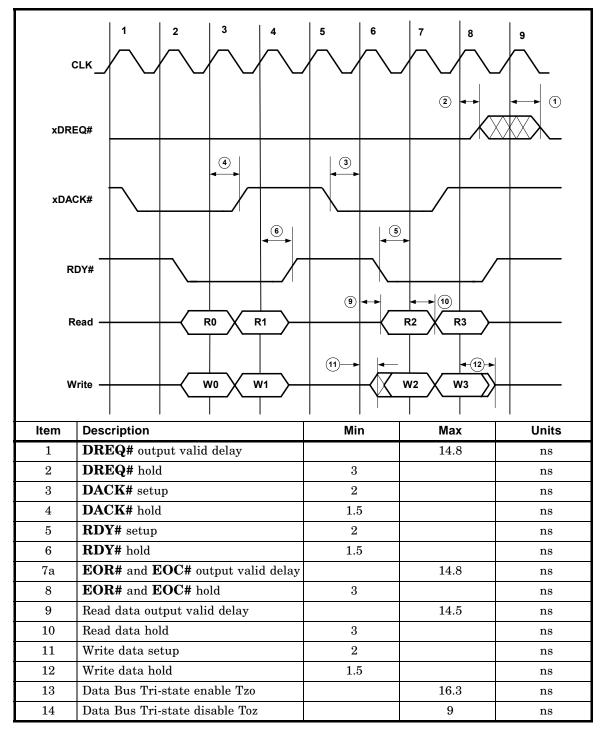

| 5.2     | DMA Ir   | nterface                               | .49 |

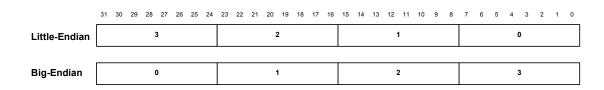

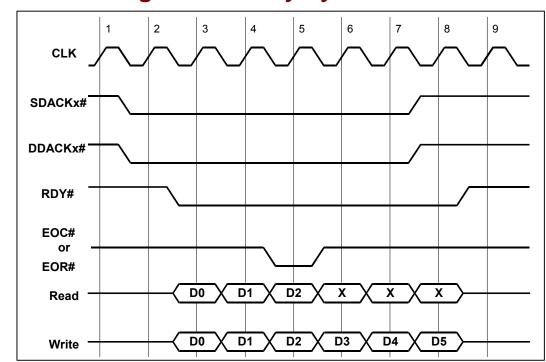

| 5.3     | DMA E    | xamples                                | .50 |

|         | 5.3.1    | Timing Diagram Terminology             | 50  |

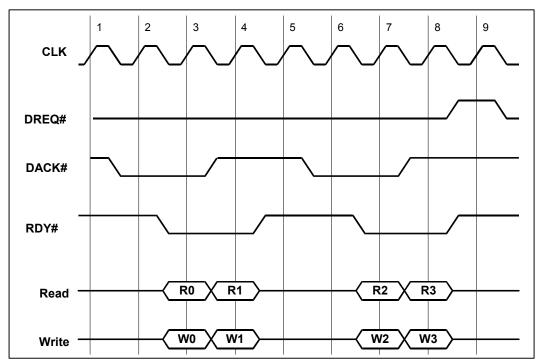

|         | 5.3.2    | Burst Transfer                         |     |

| 5.4     | Bus Tu   | rn-Around Time                         | .52 |

| 5.5     | Fixed-L  | ength Burst Transfers                  |     |

|         | 5.5.1    | Reducing Dead Time                     | 54  |

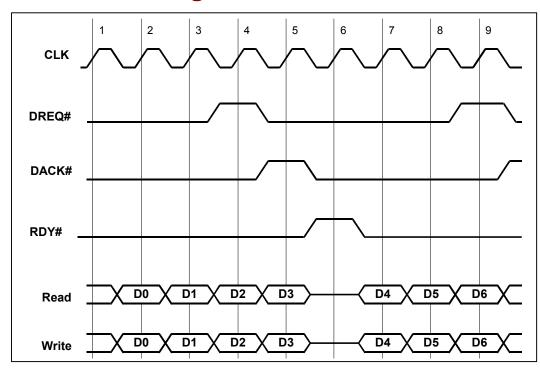

|         |          | e-Length Burst Transfers               |     |

|         |          | g with Wait States                     |     |

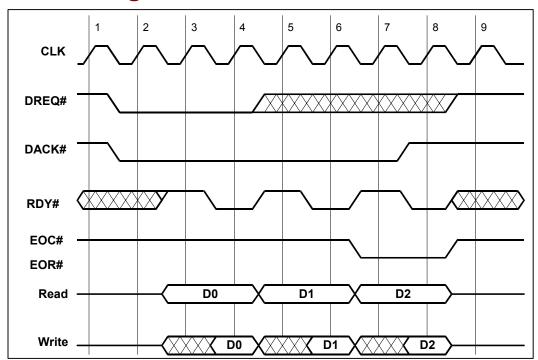

|         |          | g with Dummy Bytes                     |     |

|         | 5.8.1    | Write Transfers                        | 57  |

|         | 5.8.2    | Read Transfers                         | 58  |

| Chapter | 6        | Specifications                         | 59  |

| 6.1     | DC Spe   | cifications                            | .59 |

| 6.2     | AC Spe   | ecifications                           | .61 |

|         | 6.2.1    | Reset and Clock Timing                 | 61  |

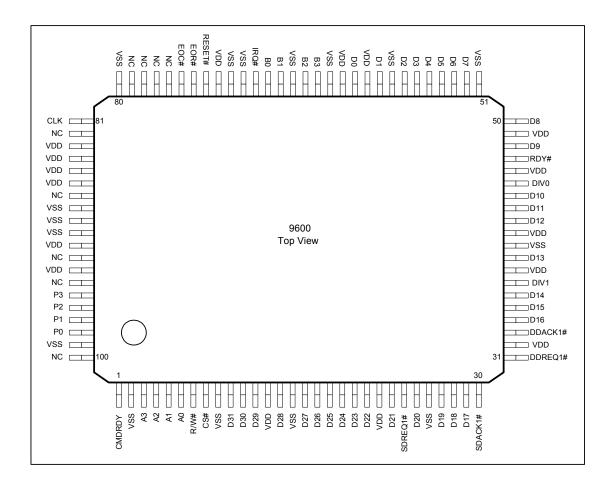

| 6.3     | Pin Des  | scription                              | .64 |

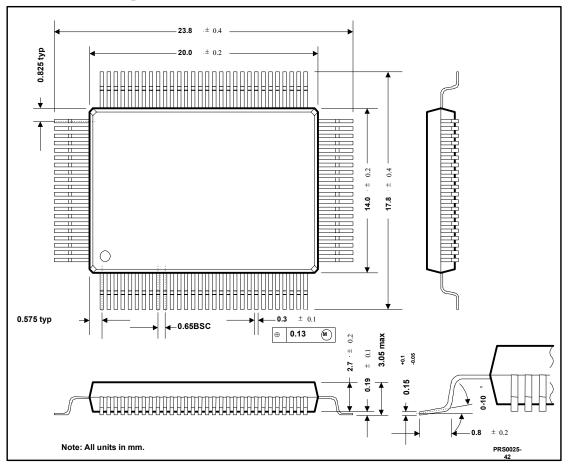

| 6.4     | Packag   | e Dimensions                           | .67 |

••••••

## Hifn .....

# **List of Figures**

| Figure 1. System block diagram                                 | <b>2</b> |

|----------------------------------------------------------------|----------|

| Figure 2. Internal block diagram                               | 3        |

| Figure 3. Channel architecture                                 | 3        |

| Figure 4. Detailed block diagram.                              | 4        |

| Figure 5. Compression example                                  | 11       |

| Figure 6. Compression example, fixed-length records            | 13       |

| Figure 7. Decompression example 1                              | 14       |

| Figure 8. CRC/LCB calculation in compression and decompression | 16       |

| Figure 9. CRC calculation in Feedback Mode 1                   | 18       |

| Figure 10. Data (0) 16-bit bus mode 3                          | 30       |

| Figure 11. Data (0) 32-bit bus mode 3                          | 30       |

| Figure 12. Command (1) 32-bit bus mode                         | 31       |

| Figure 13. Command (1) 16-bit bus mode                         | 31       |

| Figure 14. Result (2,10) 32-bit bus mode                       | 33       |

| Figure 15. Result (2,10) 16-bit bus mode                       | 34       |

| Figure 16. Big Endian 32-bit bus mode                          | 36       |

| Figure 17. Big Endian 16-bit bus mode                          | 37       |

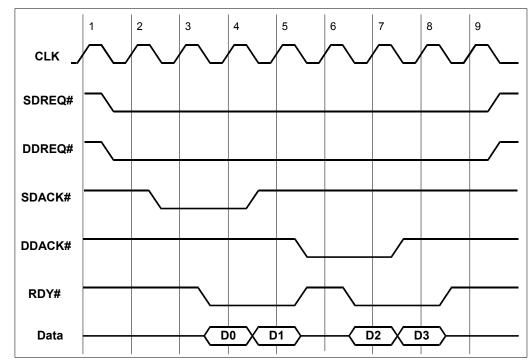

| Figure 18. Four-transfer DMA burst                             | 51       |

| Figure 19. DMA, bus turn around time 5                         | 52       |

| Figure 20. DMA, fixed length transfer                          | 53       |

| Figure 21. DMA, variable length transfer                       | 55       |

| Figure 22. DMA, three-transfer burst with wait states 5        | 56       |

| Figure 23. DMA, four-transfer burst 5                          | 57       |

| Figure 24. Pinout diagram                                      | 36       |

| Figure 25. 100-pin PQFP package dimensions                     | 37       |

THIS PAGE INTENTIONALLY LEFT BLANK

•

## Hifn .....

## List of Table

| Table 1: Signal summary                             |

|-----------------------------------------------------|

| Table 2: Register summary    6                      |

| Table 3: Writing to the source FIFO    24           |

| Table 4: Reading from the destination FIFO    25    |

| Table 5: Clock multiplier selection    28           |

| Table 6: Clock multiplier example    28             |

| Table 7: Register List                              |

| Table 8: Commands         32                        |

| Table 9: Byte enable    41                          |

| Table 10: Absolute maximum ratings    59            |

| Table 11: Recommended operating conditions    59    |

| Table 12: AC specification definition    59         |

| Table 13: DC electrical characteristics    60       |

| Table 14: Reset and power-up timing    61           |

| Table 15: CLK timing                                |

| Table 16: CPU timing    62                          |

| Table 17: DMA timing    63                          |

| Table 18: Pin Description, numerical order    64    |

| Table 19: Pin Description, alphabetical order    65 |

## List of Table

•

х

# Hifn

THIS PAGE INTENTIONALLY LEFT BLANK

# lifn .....

# **Preface**

### **About This Document**

Welcome to the 9600 Data Sheet for the Hifn 9600 Data Compression Processor. This document assumes you are already familiar with the chip technology and terminology.

#### Audience

This document is for integrators and application developers responsible for and familiar with software and hardware architecture of a target system.

#### **Document Conventions**

The following conventions may be used within this document:

- Small Courier typeface indicates code, functions, and variables .

- Bold Courier typeface indicates items the user types.

- *Italic* typeface indicates *file names* and *book titles*.

- **Registers** appear in **Bold** typeface.

- **SIGNAL** names appear in **BOLD** CAPS.

- Path names are written relative to the path //*filename*.

#### **Customer Support**

For technical support about this product, please contact your local Hifn sales office, representative, distributor.

### Web Site

For general information about Hifn and Hifn products refer to: www.hifn.com

. . .

This page left intentionally blank.

•

# **List of Abbreviations and Acronyms**

| Term                           | Definition                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                        | A single instruction to the 9600.                                                                                                                                                                                                                                                                                                                                      |

| Compressed Data<br>Stream      | A series of compressed bytes, which presumably consists of one or more compressed records.                                                                                                                                                                                                                                                                             |

| Compressed<br>Protected Record | A compressed record which, when decompressed, contains as its last four<br>bytes the CRC of the preceding bytes of the record.                                                                                                                                                                                                                                         |

| Compressed<br>Record           | A part of a compressed data stream ending with an embedded end marker that indicates end-of-record.                                                                                                                                                                                                                                                                    |

| CPU                            | Central Processing Unit                                                                                                                                                                                                                                                                                                                                                |

| CRC                            | cyclic redundancy calculation                                                                                                                                                                                                                                                                                                                                          |

| Data Stream                    | Any Series of input or output bytes.                                                                                                                                                                                                                                                                                                                                   |

| DMA                            | Direct Memory Access - Transfers using the 9600's request/acknowledge/<br>ready protocol. DMA transfers send data into and out of the FIFOs; they<br>cannot program internal registers.                                                                                                                                                                                |

| Dummy Bytes                    | Data that is transferred but is marked invalid through the byte enables.                                                                                                                                                                                                                                                                                               |

| End Marker                     | A token at the end of a compressed record that indicates the end of the record. This allows the end of the record to be detected during decompression.                                                                                                                                                                                                                 |

| EOC                            | End-of-Command condition. This can be indicated in a variety of ways, including with the <b>EOC#</b> signal and by the use of the record count fields to specify the amount of data to process.                                                                                                                                                                        |

| EOR                            | The end-of-record condition, which can be indicated by the <b>EOR#</b> signal or, for fixed-length records, by the use of the Source Count field in the <b>Command</b> register. On compression, an end marker is embedded into the compressed data stream to indicate the end of the record. On decompression, this end marker is detected by the 9600 automatically. |

| FIFO                           | First-In First-Out                                                                                                                                                                                                                                                                                                                                                     |

| LCB                            | longitudinal check byte                                                                                                                                                                                                                                                                                                                                                |

| LZS                            | Lempel-Ziv-Stac compression                                                                                                                                                                                                                                                                                                                                            |

| Padding                        | Data that rounds out a compressed record to an 8-bit boundary. Unlike<br>dummy bytes, padding consists of valid data, and is a required part of the<br>compressed data stream.                                                                                                                                                                                         |

| PLL                            | Phase-Locked Loop                                                                                                                                                                                                                                                                                                                                                      |

:

| Term                 | Definition                                                                                                                                                          |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmed I/O       | Transfers using the register access protocol. This method can access registers and the FIFOs.                                                                       |

| RAM                  | Random Access Memory                                                                                                                                                |

| Raw Data Stream      | A series of uncompressed bytes                                                                                                                                      |

| Raw protected record | A raw record containing, as its last four bytes, the CRC of all of the preceding bytes of the record. The CRC bytes are provided by the Host as part of the record. |

| Raw record           | A series of uncompressed bytes with the EOR condition indicated externally.                                                                                         |

| Record               | A portion of a data stream with a definite start and end. Compression and decompression operate on a record-by-record basis.                                        |

| SDRAM                | Synchronous Dynamic Random Access Memory                                                                                                                            |

•

# 1 **Overview**

## 1.1 9600 Description

The Hifn 9600 is a lossless Data Compression Processor. It uses the industrystandard Lempel-Ziv-Stac compression (LZS®) algorithm. The 9600 can compress or decompress data at up to \*80 MB/sec. The 9600 contains a second decompressonly engine that may be used in feedback mode to optionally verify successful compression operations. The second engine is not available for general decompression operations.

. . . . . . .

1

The 9600 system bus interface supports both register I/O and Direct Memory Access (DMA) transfers at bus widths of 16 and 32 bits. The DMA interface supports single-cycle bus transfers at a bus clock of up to 50 MHz. The bus interface is straightforward and easy to interface to.

Hifn's LZS compression algorithm has been standardized by many organizations, including ANSI (X.3.241), QIX (122), IETF (RFC 1967, RFC 1974), TIA/EIA (655), and the Frame Relay Forum (FRF.9).

\*Note: Can be achieved by using 40 MHz Bus Clock, a clock multiple of 2, which provides 80 MHz Core Logic Clock. See Section 2.13, for more details.

#### 1.2 9600 Features

- Compress or decompress at 80 MB/sec

- Industry-standard LZS algorithm

- Optional feedback mode to verify compression operation

- On-chip memory eliminates the need for external compression Random Access Memory (RAM)

- Processes multiple data records per command

- High-speed, single-cycle burst interface

2

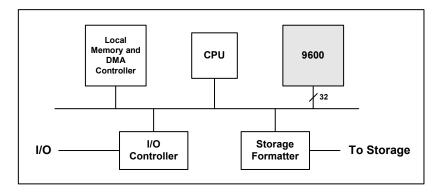

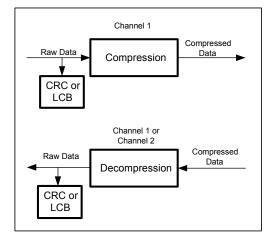

Figure 1. System block diagram

### **1.3 Product Overview**

The 9600 is a dual-channel device with a single system bus interface. Each channel contains input and output First-In First-Outs (FIFOs), a compression/ decompression engine, dedicated internal compression memory, command, status, and result registers. Channel 1 performs both compression and decompression; Channel 2 performs decompression only and is only used to verify the compression operation in feedback mode.

Feedback mode is a fault-detection feature that verifies the results of the compression engine in real time. In feedback mode, Channel 1 compresses the input data. Channel 2 decompresses the output of Channel 1 and verifies the resulting CRC.

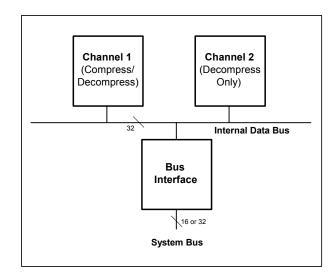

Figure 2 shows an internal block diagram of the 9600. Channel 1 has a pair of 64-byte FIFOs that buffer data to and from the system data bus. These are the *Source FIFOs* and *Destination FIFOs*. These FIFOs allow Channel 1 to operate at full speed over the I/O bus. Channel 1 also has its own DMA handshaking signal to control the movement of data into and out of the FIFOs.

The 9600 system bus interface supports both register I/O and DMA transfers at bus widths of 16 and 32 bits. The DMA interface supports single-cycle bursting at a 50 MHz bus speed.

Figure 2. Internal block diagram

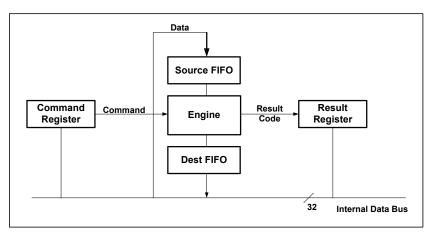

Figure 3 shows command and data flow in one of the Channels. Unlike data flow, command flow is not buffered by the FIFOs. The Host must wait until the previous command has completed before starting the next command.

Figure 3. Channel architecture

An external DMA controller uses the 9600 to perform compression or decompression by following these steps:

- 1. The **Command** register is loaded with the command parameters.

- 2. Source data is written to the Source FIFO; output data is read from the Destination FIFO. (This step continues until all source data has been written and all output has been read.)

- 3. Results are checked through polling or interrupts to verify that the command completed without errors.

While the FIFOs are flushed between commands, this has little impact on performance, since a single command can process any number of data records.

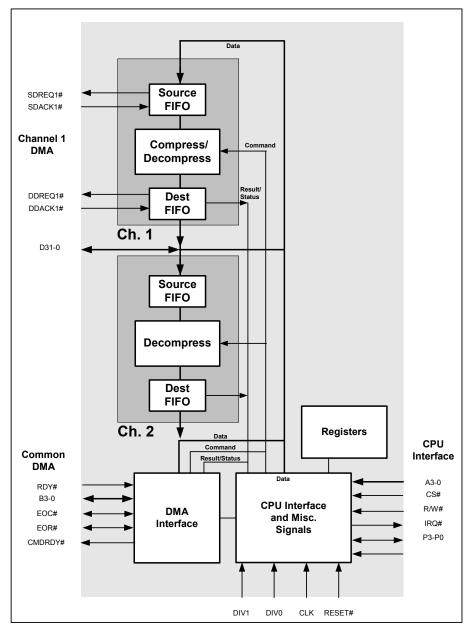

## 1.4 Detailed Block Diagram

Figure 4. Detailed block diagram

## 1.5 Signal Summary

. . . . .

The following table summarizes the 9600 signals. For a complete signal description, see Chapter 4. For a list of pins sorted by pin number, or sorted by signal name see Chapter 6.

. . . . . . . . . . . . . . . . .

| CPU Interface  | Signal  | Туре       | Description                        |

|----------------|---------|------------|------------------------------------|

| Common with    | D[31-0] | <i>I/O</i> | 32-bit System Data Bus             |

| DMA Interface  | P[3-0]  | <i>I/O</i> | Parity bits                        |

|                | A[3-0]  | Input      | Register Select                    |

| CPU/Register   | R/W#    | Input      | Read/Write                         |

| Interface Only | CS#     | Input      | Command Strobe                     |

|                | IRQ#    | Output     | Interrupt Request (open-collector) |

#### Table 1: Signal summary

| DMA Interface  | Signal  | Туре    | Description                                     |

|----------------|---------|---------|-------------------------------------------------|

|                | B[3-0]  | I/O     | Byte Enable                                     |

| Common to both | RDY#    | Input   | DMA Ready                                       |

| channels       | EOC#    | I/O     | End of Command                                  |

|                | EOR#    | I/O     | End of Record                                   |

|                | SDREQ1# | Output* | Channel 1 DMA Input Request (Source FIFO)       |

|                | SDACK1# | Input   | Channel 1 DMA Input Acknowledge                 |

| Channel 1      | DDREQ1# | Output* | Channel 1 DMA Output Request (Destination FIFO) |

|                | DDACK1# | Input   | Channel 1 DMA Output Acknowledge                |

| Miscellaneous<br>Signals                                                                    | Signal     | Туре  | Description                    |  |  |

|---------------------------------------------------------------------------------------------|------------|-------|--------------------------------|--|--|

|                                                                                             | RESET#     | Input | Hardware Reset (Schmitt input) |  |  |

|                                                                                             | CLK        | Input | Clock Input                    |  |  |

|                                                                                             | DIV1, DIV0 | Input | Clock Divisor Input            |  |  |

|                                                                                             | VCC        | Input | +3.3 Volt supply               |  |  |

|                                                                                             | GND        | Input | Ground                         |  |  |

| * External pull-up/pull-down resistors on these signals set the Phase-Lock Loop (PLL) clock |            |       |                                |  |  |

| multiple on reset. See Section 2.13.                                                        |            |       |                                |  |  |

•

. . . .

## 1.6 Register Summary

#### Table 2: Register summary

| Name                                              | Address   |           | Description                                                                                                                                                                                                                             |  |

|---------------------------------------------------|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                   | Channel 1 | Channel 2 | Description                                                                                                                                                                                                                             |  |

| Data                                              | 0         | Reserved  | 32-bit data register. Writing to this register adds<br>data to the Source FIFO. Reading removes data from<br>the Destination FIFO.                                                                                                      |  |

| Command                                           | 1         | Reserved  | 3x32-bit <b>Command</b> register. Contains Command<br>word, 32-bit Source Count, and 32-bit Record Count.<br>Successive reads or writes access the three words in<br>sequence.                                                          |  |

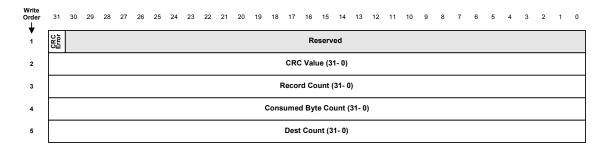

| Result                                            | 2         | 10        | 5x32-bit <b>Result</b> register. Contains result status<br>word, 32-bit CRC, 32-bit Record Count, 32-bit<br>Consumed Byte Count, and 32-bit Destination Byte<br>Count. Successive reads or writes access the five<br>words in sequence. |  |

| Configuration                                     | 3         | Reserved  | 16-bit <b>Configuration</b> register. Sets device<br>configuration, including Device Mode, Bus Width,<br>Big-Endian, and Software Reset fields.                                                                                         |  |

| Interrupt<br>Enable                               | 4         | 12        | 16-bit <b>Interrupt Enable</b> register. Allows interrupts to be enabled on a variety of conditions                                                                                                                                     |  |

| Status                                            | 5         | 13        | 16-bit <b>R/W Status</b> register. Reflects the state of each channel.                                                                                                                                                                  |  |

| Reserved                                          | 6         | 14        | <i>Reserved</i> for future expansion. Do not write to this register.                                                                                                                                                                    |  |

| FIFO<br>Configuration                             | 7         | Reserved  | 16-bit <b>FIFO Configuration</b> register. Sets the upper and lower FIFO thresholds for each channel. This controls the point at which each channel's DMA logic will request (or cease to request) data.                                |  |

| Chip ID                                           | 11        | Reserved  | 16-bit read-only Chip ID.                                                                                                                                                                                                               |  |

| See Chapter 3 for complete register descriptions. |           |           |                                                                                                                                                                                                                                         |  |

•

# 2 **Operation**

## 2.1 Records

The record is the fundamental unit of the compressed data stream. The number of records that can be processed by a single command is specified in the **record count** field in the **Command** register.

. . . . . . .

A data stream can consist of any series of data bytes. A record is a series of data bytes terminated by an end-of-record (EOR) indicator. During compression, the 9600 divides the raw data stream into records, then compresses the records, appends an end marker to the end of each record, and emits the records as a compressed output data stream. During decompression, the 9600 takes a compressed data stream and produces a series of raw records, reconstructing the original raw data stream.

## 2.2 Commands

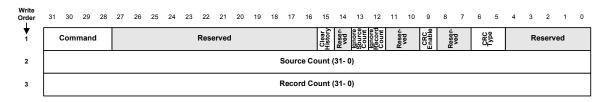

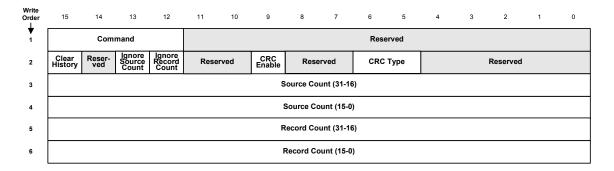

A command is a single 9600 instruction. A command can process any number of records. A command is launched when a command structure is written to the **Command** register. (There is also a **Configuration** register, shared by both channels that contains state information that will not change on a command-by-command basis, such as bus width.) A command consists of three 32-bit words (or six 16-bit words) written in sequence to the **Command** register. These words are the Command word, the Source Count, and the Record Count. Writing the last word launches the command. See Section 3.3 for a description of the **Command** register and its bit fields.

There are three valid commands: Compress, Decompress, and Passthrough. The Passthrough command is used mainly in diagnostics.

The concept of a command is specific to the 9600; it has no precise parallel to any feature of the compression standard. It is simply a way of processing one or more records with a single instruction.

## 2.3 Command and Record Termination

### 2.3.1 Command Termination

Commands can be terminated during compression or decompression as follows:

- By asserting the **EOC#** signal during a DMA write transfer.

- By setting the **EOC** bit in the **Status** register before a programmed I/O data write.

- When the number of records indicated by the record count field has been processed (if the **ignore record count** bit is not set).

- On a CRC error (if the CRC check is enabled).

The end-of-command (EOC) condition is associated with a specific byte of data, and flows through the channel along with that byte. Thus, when the EOC exits the Source FIFO, the Source FIFO is flushed and goes idle. No new data will be clocked into it until a new command is launched. When the EOC reaches the Engine, it updates its **Status** and **Results** registers and goes idle. When the EOC exits the Destination FIFO, the 9600 asserts the **EOC#** signal on the last output transfer containing valid data, or on a dummy transfer following the last data transfer. The Destination FIFO then goes idle. After the burst containing EOC, the Destination FIFO interface is disabled. Only the register I/O is active between commands.

Regardless of the source of the EOC, the condition is treated identically by the Channel. Whichever enabled condition is asserted first will terminate the command. For example, asserting the **EOC#** signal will terminate a command if asserted before the Record Counter reaches 0, and vice versa.

After each command, the **Result** register is updated, the FIFOs are flushed, and history is cleared.

See Section 2.10.4 for details on requirements for data alignment, padding, and dummy bytes during EOC.

### 2.3.2 Record Termination

Like EOC, the EOR condition is associated with a specific byte of data, and flows through the channel along with that byte. Regardless of the source of the EOR, the condition is treated identically by the channel. Any enabled EOR condition will end a record.

#### 2.3.2.1 Compression

During compression, the raw data stream can be divided into records either externally or internally. External termination occurs when the DMA controller asserts the **EOR#** signal on the last bus transfer of each record or on a dummy transfer following the last valid transfer. The last valid byte, as determined by the

8

byte enables, becomes the last byte of the record. (When using the programmed I/O mechanism to transfer data, the **eor** bit in the **Status** register needs to be set to mimic the assertion of **EOR#**.)

Records can also be terminated internally, with the raw data stream divided into records of equal length before compression. This length is set by the Source Count, which is a command field.

On output, the compressed record is always padded to a 32-bit boundary. Full bytes of padding are marked as invalid by the byte enables (that is, they are transferred as dummy bytes). In 16-bit bus mode, this padding to 32-bit boundaries may cause dummy transfers.

The **EOR#** signal is asserted by the 9600 on the transfer, from the Destination FIFO, of the last byte of data in the record.

#### 2.3.2.2 Decompression

On decompression, all record termination is internal, and is the result of embedded EOR tokens in the compressed data stream.

On input, the compressed data stream must consist of a multiple of four valid bytes. The 9600 assumes that padding exists after EOR and strips out the number of bytes necessary to pad the record to a multiple of four bytes. This operation is done after dummy bytes are stripped from the input stream, so if the record is padded with dummy bytes instead of valid bytes, the Channel will strip bytes from the beginning of the next record. This behavior is true only on input, and only during decompression.

On output, the Channel asserts the **EOR#** signal on a dummy transfer after the last word of the record has been transferred from the Destination FIFO.

Before each record, the CRC is initialized, the Source Counter is reset (on compression) to the maximum record length, the Record Counter is decremented, and history is reset if the **clear history command** bit is set.

#### 2.3.2.3 Alignment and Padding

See Section 2.10.4 for details on requirements for data alignment, padding, and dummy bytes during EOR.

#### 2.3.3 Results

The **Result** register is valid at the end of each command. It is cleared at the beginning of each new command, and its contents are undefined when a command is in progress.

Each command updates the **Results** register, a structure of five 32-bit words with the following fields:

. . . . . . .

- A status word.

- The 32-bit CRC of the last record processed. The CRC is calculated on the raw (uncompressed) data stream. In other words, the CRC is calculated on the input stream during compression and the output stream during decompression. The CRC value is usually of little interest by itself, but it can be useful in debugging.

- Record Count This starts with the Record Count given in the command, and decrements with each record. This is true even if the **ignore record count** bit is set. This allows you to determine how many records were processed, regardless of the source of EOR.

- Consumed Byte Count This counter is cleared at the beginning of the command, then updated at each EOR with the number of valid bytes processed so far in the command (dummy bytes are not counted). If the command doesn't end on EOR, the partial record at the end of the command is not counted. This counter is used mostly in decompression, where it gives the offset of the end of the successfully decompressed portion of the compressed data stream.

- Destination Count This value increments with each valid destination byte produced in either compression or decompression. The value is cumulative across all records in the command. It is reset to 0 at the beginning of each command.

The **Results** register is valid when the chip is idle. Attempting to read it during a command will cause Command/Result Overrun error. The value returned by such a read is undefined.

A Channel is idle when:

- The command ready bit in the Channel Status register is set, or

- **EOC#** has been asserted by the 9600 during an output transfer from the Channel Destination FIFO. In Feedback Mode, **EOC#** is used to signal that Channel 1 is idle, **CMDRDY** signals that Channel 2 is idle.

## 2.4 Compression

While both channels perform decompression, only Channel 1 can compress data. The DMA controller sends raw data to Channel 1 through the Channel 1 DMA interface. Incoming data is buffered in the Channel 1 Source FIFO, which generates a request signal (**SDREQ1#**) based on programmable thresholds. The Host DMA controller initiates transfers to Channel 1 with the **SDACK1#** signal and inserts wait states with **RDY#**. See Section 2.11.1 for further details. Data can also be transferred through the programmed I/O mechanism. See Section 2.11.2 for further details.

10

Raw data must be divided into records. This can be done internally, through the Source Count field in the command, or externally, with the **EOR#** signal. Data must also be divided into commands in a similar manner.

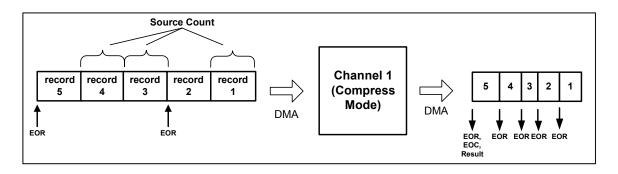

These external and internal methods of ending records can be mixed. Figure 5 shows a command that consists of five input records. Records 1, 3, and 4 are terminated when the Source Count reaches 0. Records 2 and 5 end when EOR# is asserted. The channel creates five compressed records, making no distinction between records that were terminated by EOR# or by the Source Count. These records are then compressed to varying degrees, depending on their contents.

Figure 5. Compression example

On output, EOR markers are embedded in the compressed output data stream. The output data stream is buffered by the Channel 1 Destination FIFO, which generates a request signal (**DDREQ1**#) based on programmable thresholds. The Host DMA controller initiates transfers from the Channel with the **DDACK1**# signal and inserts wait states with **RDY**#. During output transfers, **EOR**# and **EOC**# become outputs. **EOR**# is asserted when the last bytes of a record are transferred. **EOC**# is asserted when the last bytes of a command are transferred across the bus. The EOR and EOC bits in the **Status** register also follow the EOR and EOC status.

Output is 32-bit aligned; the output of a new record will begin with a new bus cycle, and will end with a bus cycle padded with dummy bytes, if necessary. Output padding guarantees that the output stream will never contain bytes from two different records. The requirements for alignment and padding are listed in Section 2.10.4.

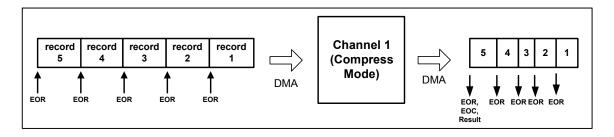

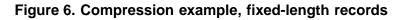

The record count field decrements with each record. In the example in Figure 6, after the first record is processed it will be set to 4, and it will have counted down to zero at the end of the command.

A CRC is calculated automatically on a per-record basis on the raw data. On compression, this is the input data.

#### 2.4.1 Compression, Step by Step

The steps below are for the case where the **EOR#** and **EOC#** signals are used instead of the Source Count and Record Count features, as shown in Figure 6. Compression is only available on Channel 1. (Details of register usage, signal definitions, and system bus timing are given in Chapter 3, Chapter 5, and Section 6.2.)

- 1. Deassert the **EOR#** and **EOC#** pins.

- 2. Test the **command ready** bit in the **Status** register. This can be done through polling or interrupts. (This step is not strictly necessary, as the 9600 is always ready to accept a new command after the previous command's EOC.)

- 3. Write three 32-bit words to the **Command** register: the Command Word (0x00003000), the Source Count (0), and the Record Count (0). (In this example, the **ignore source count** and **ignore record count** bits are set in the control word, so the values written to the Source and Record Count are don't-cares. These words must be written, however, to launch the command, even though the values are ignored.)

- 4. Start writing data to Channel 1. The handshaking is done entirely in hardware, using the Channel 1 source DMA control signals (SDREQ1#, SDACK1#, and the common signal RDY#). Assert EOR# along with the transfer containing the last byte of each record. This does not have to occur on the last transfer of a burst.

- 5. Start reading data from the Channel 1 destination DMA interface (using the handshaking signals **DDREQ1#**, **DDACK1#**, and **RDY#**). This is the compressed data stream. Unlike the input stream, we don't know how long this data stream is going to be. **EOR#** and **EOC#** will be asserted by the chip as we transfer the last words of each record and of the command.

- 6. At the end of the input data stream, assert **EOR#** and **EOC#** along with the last data transfer. Again, this does not have to be at the end of a burst, but all data transferred after **EOC#** will be discarded.

- 7. Once all the output data has been transferred (**EOC#** will be asserted by the chip on the last transfer), read the **Result** register to check the error status. Reading the **Result** register is optional (interrupts can be set for all error conditions). It is also acceptable to read only part of the five-word Result structure.

## 2.5 **Compression History**

Compression algorithms maintain data-dependent state information. This information is called the compression history. The compression history is stored in an internal compression RAM. The compression history is always cleared between commands. It can be retained across records within the same command, or cleared before each record, as determined by the **clear history** bit in the **Command** register.

## 2.6 Decompression

Compressed data is presented to the Channel as an undifferentiated data stream. As the data is decompressed, the record boundaries embedded in the data stream are detected. As in compression, the Command includes the Source Count and Record Count. For example, setting the Record Count to five will terminate the command after five records have been decompressed. The command will also terminate if the number of input bytes specified in Source Count has been consumed.

DMA data flow is almost identical to the case of compression, though in decompression **EOR#** will be ignored if asserted along with the source data stream. In the destination data stream, the chip asserts **EOR#** or **EOC#** in a dummy transfer at the end of each decompressed record or command. The start of each output record is aligned to a 32-bit boundary. Dummy bytes are inserted between output records to achieve this alignment.

See Section 2.10.4 for details of alignment and padding requirements for decompression.

### 2.6.1 Decompression, Step by Step

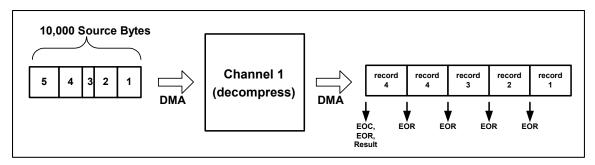

Figure 7. Decompression example

The example in Figure 7 assumes that we have chosen to decompress a block of 10,000 compressed bytes.

- 1. Deassert the **EOC#** pin.

- 2. Wait, through interrupts or polling, until **Status** register bit 14 (**command ready**) is set. (As in compression, this is not strictly necessary.)

- 3. Write three 32-bit words to the **Command** register: the Command (0x10001000), the Source Count (10,000), and the Record Count (0). (With the **ignore word count** bit set in the Command Word, the Record Count value will be ignored, but a write must still take place.)

- 4. Start writing data to Channel 1. This is the same as the previous example, except that **EOR#** should not be asserted.

- 5. Start reading data from Channel 1. This is the decompressed data stream. As in example 1, we don't know how long it will be. **EOR#** or **EOC#** will be asserted by the chip as we transfer the data at the ends of records or commands.

- 6. Stop sending data after you've transferred your 10,000 bytes. Alternatively, you can assert **EOC#** if you want to stop before 10,000 bytes have been transferred.

- 7. Wait until the last byte of decompressed data has been transferred from the channel (**EOC#** will be asserted after the last transfer of valid data.)

- 8. Read the **Result** register, which contains a data structure of five 32-bit words. Reading the Result is optional. Reading only part of the five-word Result structure is also acceptable.

- 9. Note that the command ended in the middle of record 5. The CRC in the **Result** register will be that of record 4, not for the incomplete record 5. The consumed byte count will also reflect the value at the EOR 4. If we wished to decompress record 5, the consumed byte count field would give the offset of the first byte of record 5.

## 2.7 Error Handling

The **Status** register contains error bits for command/result overrun, data error, and CRC error. These error bits are set under the following conditions:

Command/Result Overrun: The **Command** register was written or the **Result** register was read when there was a command in progress.

Data Error: The Source FIFO was overflowed or the Destination FIFO was underflowed.

CRC Error: A raw protected record with an invalid CRC was detected. The **crc enable** bit must be set for this test to take place.

Parity Error: A parity error was detected on the **P[3:0]** bus during a write to the Source FIFO.

When a CRC error is detected, the current command is terminated. The other errors simply cause the associated bits in the **Status** register to be set, and, if the associated **interrupt enable** bit is set, the **IRQ#** signal to be asserted.

These error bits can only be cleared by a hardware or software reset of the chip. A software reset is performed by writing a 1 to the **reset** bit of the **Configuration** register.

### 2.8 CRC/LCB Calculation

Figure 8. CRC/LCB calculation in compression and decompression.

In Figure 8, the 9600 calculates the CRC (cyclic redundancy calculation) or LCB (longitudinal check byte) of the raw (uncompressed) data stream automatically. In compression, it calculates the CRC or LCB of the input data. In decompression, it calculates the CRC or LCB of the output data. These calculations are done on a per-record basis. The CRC field in the **Result** register is the CRC or LCB of the last complete record. The CRC field is not updated on partial records.

#### 2.8.1 CRC/LCB Algorithms

In all three algorithms, the initial value is all ones (0xFFFFFFF for a 32-bit CRC, 0xFFFF for a 16-bit CRC, and 0xFF for an 8-bit LCB).

The CRC can be either 16 or 32 bits in length. The LCB is eight bits long. The 32bit CRC equation is:

$$x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$$

,

where x is the current data byte. The 16-bit CRC equation is:

$x^{16} + x^{12} + x^5 + 1$

The LCB is the exclusive-OR sum of each byte in the raw record. That is, with each data byte, the data is XORed with the partial LCB, and the result becomes the new LCB.

16

In addition, both CRC32 and CRC16 should be logically bit-wise inverted:

. . . . . . . . .

$\begin{aligned} &\operatorname{CRC32} = \sim (x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 \\ &+ x + 1); \end{aligned}$   $\begin{aligned} &\operatorname{CRC16} = \sim (x^{16} + x^{12} + x^5 + 1): \end{aligned}$

for a record to pass through the 9600 correctly (i.e., No CRC error).

#### 2.8.2 Protected Records

The 9600 may be configured to test the integrity of each record being processed. To function in this way, the data being processed must be formatted as protected records. A protected record is a record with a CRC-32 appended to the end.

Before records may be compressed, the system must append a CRC-32 to the end of each record. During compression, the 9600 will verify the integrity of the protected record by scanning the entire record, including the appended CRC-32. If the CRC-32 at the end of a protected record is valid, device operation will continue. If the CRC-32 is invalid, the device will terminate at the end of the record. The entire protected record (including the appended CRC-32) will be compressed by the device and becomes part of the compressed record.

During decompression, the protected record will be decompressed, resulting in the original uncompressed protected record (with the original appended CRC-32). The entire record, including the CRC-32 is scanned for integrity after decompression. If the CRC at the end of a protected record is valid, device operation will continue. If the CRC-32 is invalid, the device will terminate at the end of the record.

As described in the CRC/LCB Calculation section, the CRC-32 will always be calculated over the uncompressed data in a record. However, testing the integrity of protected records may be configured by the **crc enable** bit in the Command Word. The result of the integrity test is part of the **Result** and **Status** registers.

The 9600 updates the CRC Error flag only at the end of the record. A CRC error will not be flagged if a command terminates before the end of a record is processed. This prevents spurious CRC errors from being reported every time a command terminates in the middle of a record.

When a CRC error is detected at the end of a record, the command will terminate. A reset must be issued to clear the CRC Error flag.

#### 2.8.2.1 Notes on Protected Records

If the CRC-32 is calculated over an entire protected record (including the embedded CRC-32), the result will always be 0xDEBB20E3. This information may be useful when designing the external logic used to scan protected records decompressed by the 9600.

The CRC embedded in a protected record is part of the record. It is compressed and decompressed along with the rest of the record, and the 9600 treats it like any other data. The CRC is embedded by the Host; the 9600 neither adds it to the data stream nor removes it from the data stream. If the **crc enable** bit is set in the Command Word, four CRC bytes must be appended to the end of every raw record, or a CRC Error will be generated.

For example, if a 256-byte record has a 32-bit CRC of 0x1A9BFE29, appending the 32-bit constant 0x1A9BFE29 to the end of the record will create a new 260-byte protected record. When this record is processed by the 9600, it will return a CRC value of 0xDEBB20E3. This value is constant for every protected record with valid 32-bit CRC bytes.

### 2.9 Feedback Mode

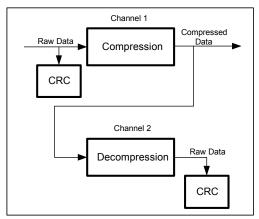

Figure 9. CRC calculation in Feedback Mode

The 9600 can operate with Feedback Mode enabled or disabled. In Feedback Mode, Channel 1 is used for both compression and decompression, while Channel 2 is used only to verify proper operation of the device in compression. The figure above shows feedback-mode operation.

Feedback Mode is enabled by setting the **feedback mode** bit in the **Configuration** register.

In Feedback Mode, Channel 1 is used for both compression and decompression; Channel 2 is dedicated to per-record CRC checking during compression. Channel 1 compresses records, while Channel 2 decompresses them to check their CRCs. Provided that the input data consists of valid raw protected records, this error will only occur if there has been some kind of hardware failure.

When the device is put into Feedback Mode, Channel 2 registers are programmed automatically for proper feedback operation. The only Channel 2 registers which can be accessed in Feedback mode are the **Result** register, the **Interrupt Enable** register, and the **Status** register. Writes to the other registers will be ignored; reads are undefined.

Feedback Mode ties the Destination FIFO of Channel 1 to the Source FIFO of Channel 2. Since both channels operate at the same speed, the bandwidth is the same whether compression uses Feedback Mode or not, but Feedback Mode adds a small amount of latency.

The **CMDRDY** pin is asserted when the Channel 2 command is complete, informing the Host system that the Channel 2 **Result** register is ready and that a new command can be started.

Checking the result requires that the Host read both **Results** registers. The Channel 2 result will not become ready at the same time as the Channel 1 result. For Channel 1, EOC takes place as usual, with the **EOC#** pin being asserted on the last valid data transfer from the Destination FIFO. Channel 2 has no opportunity to assert **EOC#**, as there are no data transfers from Channel 2. Channel 2 does, however, assert the **CMDRDY** signal at the end of the command. The 9600 is not ready for a new command until the **CMDRDY** signal has been asserted.

#### 2.9.1 Errors in Feedback Mode

If the 9600 is in Feedback Mode with the CRC test enabled, any record that fails the CRC test in either Channel will cause the command to abort. The CRC error status will be given in the **Result** register for each channel. A Channel 1 CRC failure indicates a data corruption problem. A Channel 2 CRC failure indicates a device failure.

The CRC error is only asserted on EOR. If a command ends partway through a record, no error is generated.

When the CRC test is enabled, both Channels check the CRC with every record, in both compression and decompression. The **crc error** bit is not only in the **Result** register but is also replicated in the **Status** register. The **Interrupt Enable** register determines whether a CRC error will cause an interrupt.

If a CRC error occurs in Channel 1, the command will terminate in Channel 1, but Channel 2 will keep going until any valid data produced by Channel 1 before the error has been processed. In this case, **EOC#** will be asserted first, followed by **CMDRDY** some number of cycles later.

If a CRC error occurs in Channel 2, the command is terminated immediately in both channels. In this case, **CMDRDY** may be asserted alone, and **EOC#** will not be asserted at all. The Host DMA state machine needs to take this into account.

If a CRC error occurs in both Channels on the same cycle, both **EOC#** and **CMDRDY** may be asserted at the same time.

#### 2.9.2 Feedback Mode Compression, Step by Step

This example gives the procedure for compression in Feedback Mode.

1. Enable Feedback Mode by setting the **feedback mode** bit in the **Configuration** register.

- 2. If desired, set the interrupt enable for the CRC Error in the Channel 2 Interrupt Enable register. This will catch device failures. This step is not absolutely necessary, since CRC errors will cause the command to terminate, and the crc error bit will be set in the Status and Result registers.

- 3. If desired, also set the interrupt enable for the CRC Error in the Channel 1 Interrupt Enable register. This will detect data corruption errors on the raw protected records. Again, the interrupt is not necessary to catch CRC errors, because the command will terminate on CRC errors.

- 4. Compress the data as usual.

- 5. When the last byte of output data has been transferred from the Channel 1 Destination FIFO, **EOC#** will be asserted as usual, unless there has been an error in Channel 2. The Channel 1 result can be checked after EOC if desired.

- 6. When Channel 2 has reached the end of the command, it will assert **CMDRDY**. This marks the true end of the command.

- 7. Test Channel 2 for errors as usual, through programmed I/O or interrupts. The CRC Error has special significance in Feedback Mode, of course, and should always be checked, or there is no point to operating the chip in Feedback Mode.

- 8. Begin a new command. The 9600 will be ready for a new command when **CMDRDY** is asserted.

## 2.10 Data and Register Transfer

Once a command has started, data can be transferred to the Channel. Input data is written to the Source FIFO. Output is read from the Destination FIFO. There are two mechanisms for transferring data: programmed I/O and DMA. DMA provides higher performance.

Both methods use FIFOs in an identical manner. Since the programmed I/O method does not use the EOR, EOC, or byte-enable signals, there are a set of **read/write status** register bits that provide the same function. Writing these bits has the same effect as asserting the signals; reading them gives the same information as sampling the signals.

DMA and programmed I/O data transfers should not be mixed in the same command.

The examples in this document will all use DMA unless it is explicitly stated that programmed I/O is being used.

#### 2.10.1 DMA

The most efficient way to use the 9600 is through its DMA interface. The DMA interface allows data to move directly between the Host DMA controller and the 9600 FIFOs. Channel 1 has two FIFOs: a Source FIFO and a Destination FIFO.

Each FIFO has its own request and acknowledge signals. Thus, Channel 1 has **SDREQ1#**, **SDACK1#**, **DDREQ1#**, and **DDACK1#**. The request signals are outputs; the acknowledge signals are inputs.

In addition to the FIFO-specific signals, there are a number of shared signals: **RDY#** input and the bidirectional **EOC#**, **EOR#**, **D** [31:0] data bus, and **B**[3:0] byte enables.

Once a command is issued, DMA transfers can begin. The Source FIFO is always empty at the beginning of a command, so the **SDREQ1#** signal will be asserted immediately. Data to be processed is written by the Host to the Source FIFO. The Host initiates a burst by asserting the **SDACK#** signal.

The **SDREQ1#** and **DDREQ1#** signals are controlled by programmable FIFO thresholds. These thresholds determine the points at which the signals are asserted and deasserted, based on how full or empty the FIFOs are. FIFO thresholds are discussed in Section 2.12.

The EOR and EOC conditions are indicated by the **EOR#** and **EOC#** signals. **EOR#** and **EOC#** are transferred with the data, or immediately after it as part of a dummy transfer. When the Host is writing data, it writes **EOR#** and **EOC#** as part of the last data write. When the Host reads data, it reads **EOR#** and **EOC#** from the 9600.

Data sent to the Channel after EOR is considered to be part of the next record (see the discussion of data alignment requirements in Section 2.10.4).

Any data sent to the Channel after EOC is ignored. Data read from the channel after EOC is invalid (these statements are also true of programmed I/O). In other words, the Host can continue to send data after EOC, and there will be no adverse effects. This is useful, for example, in decompression, where the Host often has no idea of the exact position of the end of a compressed record. The Host can send a too-large block of data, telling the 9600 to decompress the correct number of records. Leftover data at the end will be discarded automatically. The consumed byte count field in the **Result** register will report the number of valid bytes processed during the command (See Section 3.4.4 for details of the consumed byte count.)

DMA timing is covered in detail in Section 5.2.

#### 2.10.1.1 Byte-Enable Signals

The byte-enable signals, **BE[3:0]**, are written at the same time as data on the data bus. They indicate which bytes in the data word are valid. When writing data to the Source FIFO, the byte-enables can be asserted in any pattern, and the 9600 will discard invalid (dummy) bytes and process those marked valid. When reading from the Destination FIFO, the Host should discard any bytes for which the byteenables are not asserted. The Host DMA logic must monitor the byte-enables on every read transfer from the 9600. To indicate the end of a command or record without writing data, a dummy word may be written to the Source FIFO. When this dummy word is written, the **EOC#** or **EOR#** signals are asserted, but the byte-enables are not. This signals the EOR or EOC status without transferring data.

Dummy bytes and dummy transfers to the Source FIFO occupy space in the FIFO as if they were valid data. They are not discarded until they exit the FIFO. Thus, the design of the Host DMA controller must count dummy bytes as if they were valid for purposes of setting Source FIFO thresholds.

When using programmed I/O, the byte-enable bits in the **Status** register must be used to indicate which bytes are valid. This is described further in Section 2.12.1.

When reading from the Destination FIFO, the byte-enable signals are written by the 9600 along with the data. The first transfer of every record is always aligned to the bus boundary.

In some situations, there may be a destination transfer with no valid bytes to mark the EOC, record or both. This would be indicated by a transfer which has no valid data bytes, but for which the **EOC#** or **EOR#** signals are asserted. Since the word has no valid data, the **BE[3:0]** signals (or the **BE** bits in the **Status** register for programmed I/O) would be deasserted.

See Section 5.2 for a detailed description of the DMA interface protocol.

#### 2.10.2 Programmed I/O

Programmed I/O is a conventional interface using the CS# and R/W# signals for control, the A[3:0] bus for register addressing, and the D[31:0]bus for data transfers. See Section 2.10.2 for a detailed description of the programmed I/O bus protocol.

Programmed I/O is the only mechanism for reading and writing registers, including the **Command** register. The chip registers are inaccessible to the DMA interface. Thus, chip configuration, commands, results, and status are all transferred exclusively through programmed I/O.

The basic operation of programmed I/O consists of reading and writing registers. Most registers are either 16 or 32 bits long. The **Command** and **Results** structures contain multiple 32-bit words, which are read or written sequentially through consecutive accesses. For example, the **Command** structure consists of three 32-bit words (or six 16-bit words in 16-bit bus mode). In 32-bit bus mode, a command is launched by writing three words to the **Command** register: first the Command Word, then the Source Count, then the Record Count. The command is launched when the third word is written.

The **Result** structure is five 32-bit words long (or ten 16-bit words long in 16-bit bus mode), and is read through five (or ten) reads to the **Result** register. The **Command** can also be read back.

Programmed I/O can be used as an alternative to DMA for transferring data into and out of the 9600. Writes to the **Data** register send data into the Source FIFO. Reads from the **Data** register return data from the Destination FIFO.