## Current Mode PWM Controller

#### **FEATURES**

- Burst Mode function

- Low startup current (6.5uA)

- Low operating current (2.3mA)

- Built-edge blanking

- Built-in synchronized slope compensation

- Current mode

- External Programmable PWM Switching Frequency

- By-cycle current limit protection (OCP)

- VDD over-voltage clamping protection

- Low voltage shut down function (UVLO)

- Gate Drive Output Voltage Clamp (18V)

- Frequency jitter feature

- Constant output power limit

- Overload protection (OLP)

- Work does not produce audio noise

#### **APPLICATIONS**

Offline AC/DC flyback converter for

- Power Adaptor

- Open-frame SMPS

- Battery Charger

- Set-Top Box Power Supplies

#### GERNERAL DESCRIPTION

WIS2269 is a highly integrated, high performance current mode PWM controller chip. Apply to the power adapter and other small and medium-power switch power supply.

In order to reduce standby power consumption to meet the higher standards of environmental protection, the chip provides a pulse mode (Burst Mode) function, very low starting current and operating current. Pulse mode that is in the light load or no load conditions, WIS2269 can linearly decrease the switching frequency chip, thereby reducing switching loss; by optimizing the design, WIS2269 has a very low starting current and operating current, is not only beneficial to start the circuit design, and the start circuit can be used in high-value startup resistor, to reduce power consumption, improve power conversion efficiency.

WIS2269 built-in synchronized slope compensation circuit, to prevent the PWM controller when working in high-duty cycle may have harmonic oscillation. WIS2269 side in the current sample input pin edge blanking function built in, can effectively remove the current feedback signal of the glitch. Help to reduce the number of external components, reducing overall system cost.

WIS2269 offers a variety of comprehensive resume protection mode, including:-by-cycle current limit protection (OCP), over-load protection (OLP), VDD over-voltage clamping voltage and low voltage closed (UVLO). Which, in order to better protect the external MOSFET power transistor, the gate drive output voltage is clamped at 18V.

WIS2269 the totem pole gate drive output using a frequency jitter control technology and soft-switching technology, can be very good to improve EMI performance switching power supply system. By optimizing the design, when the chip's operating frequency less than 20KHz circumstances, the audio energy can be reduced to a minimum. Therefore, the audio can get greatly improved noise performance.

WIS2269-chip can be used as RCC-mode power supply linear power supply or the best alternative to enhance the overall performance of switching power supply system, and effectively reduce the system cost.

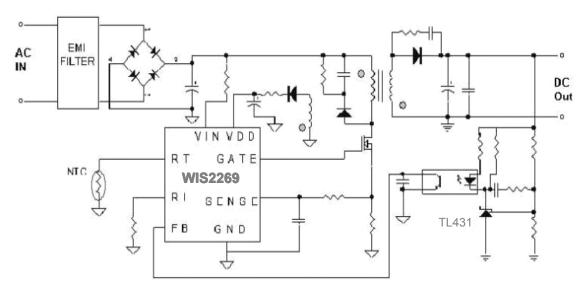

#### TYPICAL APPLICATION

## **GENERAL INFORMATION**

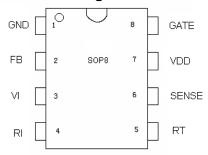

## **Pin Configuration**

## **TERMINAL ASSIGNMENTS**

| Pin Name | Pin No. | I/O | Description                                                                                                                                                                                                                                                                                          |  |  |

|----------|---------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GND      | 1       | Р   | Ground                                                                                                                                                                                                                                                                                               |  |  |

| FB       | 2       | I   | Feedback input pin. The input level value and 6-pin to monitor the value of current is indeed common set PWM duty cycle control signal. If the FB terminal of the input voltage is greater than a set set threshold voltage, the internal protection circuit will automatically turn off PWM output. |  |  |

| VI       | 3       | ı   | Through a high resistance of the resistor connected to the rectifier output, start the device into the working condition; while the voltage is sampled to generate line voltage compensation.                                                                                                        |  |  |

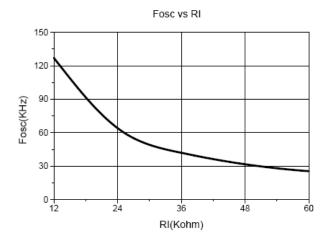

| RI       | 4       | I   | Internal Oscillator frequency setting pin. A resistor connected between RI and GND sets the PWM frequency.                                                                                                                                                                                           |  |  |

| RT       | 5       | ı   | Temperature monitoring of input pins. By a NTC resistor connected to ground.                                                                                                                                                                                                                         |  |  |

| SENSE    | 6       | I   | Current sense input pin. Connected to MOSFET current sensing resistor node.                                                                                                                                                                                                                          |  |  |

| VDD      | 7       | Р   | Chip DC power supply pin                                                                                                                                                                                                                                                                             |  |  |

| GATE     | 8       | 0   | Totem-pole gate drive output for the power MOSFET.                                                                                                                                                                                                                                                   |  |  |

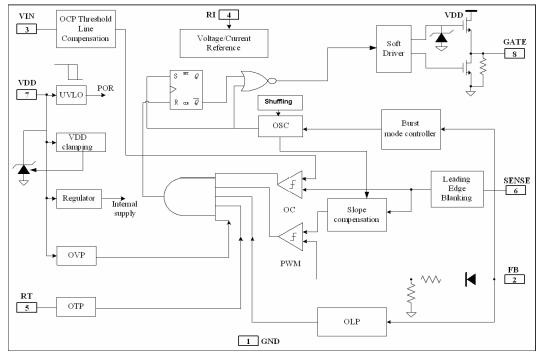

## **BLOCK DIAGRAM**

W

## RECOMMENDED OPERATING CONDITION

| Symbol          | Parameter                     | Min | Max | Unit       |

|-----------------|-------------------------------|-----|-----|------------|

| V <sub>DD</sub> | VDD Supply Voltage            | 12  | 23  | V          |

| RI              | RI Resistor Value             | 24  |     | ΚΩ         |

| Т               | Operating Ambient Temperature | -20 | 85  | $^{\circ}$ |

## **ABSOLUTE MAXIMUM RATINGS**

| Pin Name           | Parameter                            | Ratings | Units      |

|--------------------|--------------------------------------|---------|------------|

| V <sub>DD</sub>    | V <sub>DD</sub> Pin input voltage    | 30      | V          |

| V <sub>FB</sub>    | V <sub>FB</sub> Pin input voltage    | -0.3~7  | V          |

| V <sub>SENSE</sub> | V <sub>SENSE</sub> Pin input voltage | -0.3~7  | V          |

| V <sub>RI</sub>    | V <sub>RI</sub> Pin input voltage    | -0.3~7  | V          |

| V <sub>RT</sub>    | V <sub>RT</sub> Pin input voltage    | -0.3~7  | V          |

| T <sub>J</sub>     | Operating Junction Temperature       | -20~150 | $^{\circ}$ |

| T <sub>S</sub>     | Storage Temperature                  | -55~160 | $^{\circ}$ |

| Vcv                | V <sub>DD</sub> DC Clamping Voltage  | 34      | V          |

| I <sub>cc</sub>    | V <sub>DD</sub> DC Clamping Current  | 10      | mA         |

Note: more than the limit specified in the table parameters will result in permanent damage to the device. The device is not recommended in these extreme conditions of work, working conditions in the limit above which may affect device reliability.

# Electrical Characteristics (Tc = 25°C, $V_{DD}$ =16V, $R_{I}$ =25K $\Omega$ ,Unless otherwise specified )

| Symbol                 | Parameter                          | Conditions                          | Min  | Тур  | Max                        | Unit    |

|------------------------|------------------------------------|-------------------------------------|------|------|----------------------------|---------|

| I_VDD_Startup          | VDD startup current                | VDD=15V, measure current into VDD   |      | 6.5  | 20                         | uA      |

| I_VDD_Operation        | Operation Current                  | FB=3V                               |      | 2.3  |                            | mA      |

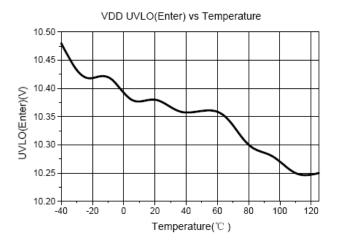

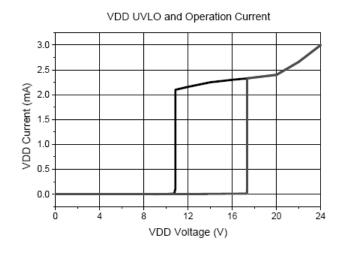

| ITH O(ON)              | VDD under voltage                  |                                     | 9.5  | 10.5 | 11.5                       | 3.7     |

| UVLO(ON)               | lockout enter                      |                                     | 9.5  | 10.5 | 11.5                       | V       |

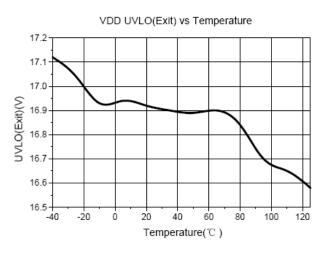

| UVLO(OFF)              | VDD under voltage<br>lockout exit  |                                     | 16   | 17   | 18                         | v       |

|                        | VDD Over Voltage                   |                                     |      |      |                            |         |

| OVP(ON)                | Protection Enter                   |                                     | 23.5 | 25   | 26.5                       | V       |

|                        | VDD Over Voltage                   |                                     |      |      | 11.5<br>18<br>26.5<br>24.7 |         |

| OVP(OFF)               | Protection Exit                    |                                     | 21.5 | 23.2 | 24.7                       | V       |

| TD OVP                 | OVP Debounce time                  |                                     |      | 80   |                            | us      |

| VDD Clamp              | VDD Clamp voltage                  | I(V <sub>DD</sub> )=5mA             |      | 36   |                            | V       |

| Feedback Input Se      | ction(FB Pin)                      | V                                   | 1    | ,    | '                          |         |

| Avcs                   | PWM Input Gain,                    | $\triangle V_{FB}/\triangle V_{CS}$ |      | 2.6  |                            | V/V     |

| VFB_Open               | VFB Open Voltage                   |                                     |      | 6    |                            | V       |

| I <sub>FB</sub> _Short | FB pin short current               | Short FB pin to GND                 |      | 0.8  |                            | mA      |

| VTH OD                 | Zero Duty Cycle FB                 |                                     |      |      | 0.05                       | v       |

| VTH_0D                 | Threshold Voltage                  |                                     |      |      | 0.93                       | v       |

| VTH_BM                 | Burst Mode FB<br>Threshold Voltage |                                     |      | 1.7  |                            | V       |

| VTH_PL                 | Power Limiting FB<br>Threshold     |                                     |      | 4.4  |                            | v       |

| TD_PL                  | Power Limiting Debounce Time       |                                     |      | 80   |                            | mSec    |

| ZFB IN                 | Input Impedance                    |                                     |      | 7.5  |                            | Kohm    |

| Current Sense Inp      |                                    |                                     |      | 7.5  |                            | 1101111 |

|                        | Sense Input Leading                |                                     |      |      |                            |         |

| T_blanking             | Edge Blanking Time                 |                                     |      | 300  |                            | nSec    |

| 7 DI                   | Sense Input                        |                                     |      | 20   |                            |         |

| Zsense_IN              | Impedance                          |                                     |      | 39   |                            | kohm    |

|                        | Over Current                       |                                     |      |      |                            |         |

| TD_OC                  | Detection and                      | C <sub>L</sub> =1nF at GATE         |      | 120  |                            | nSec    |

|                        | Control Delay                      |                                     |      |      |                            |         |

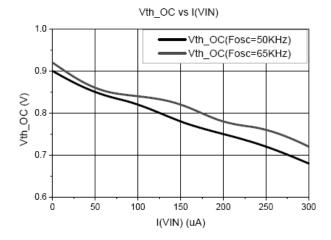

| VTH_OC_0               | Current Limiting                   |                                     |      |      |                            |         |

|                        | Threshold at No                    | I(VIN)=0uA                          | 0.85 | 0.9  | 0.95                       | V       |

|                        | Compensation                       |                                     |      |      |                            |         |

| VTH OC 1               | Current Limiting<br>Threshold at   | I/X/IND=150m A                      |      | 0.81 |                            | v       |

| VTH_OC_1               | Threshold at<br>Compensation       | I(VIN)=150uA                        |      | 0.61 |                            | , v     |

|                        | Compensation                       |                                     |      |      | L                          |         |

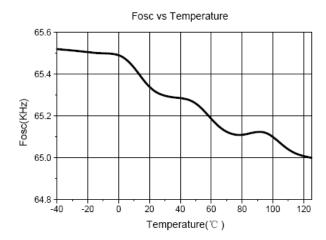

| Oscillator        |                     |                        |          |                                                  |                      |      |

|-------------------|---------------------|------------------------|----------|--------------------------------------------------|----------------------|------|

| Fosc              | Normal Oscillation  |                        | 60       | 65                                               | 70                   | KHz  |

| LOSC              | Frequency           |                        | 00       | 0.5                                              | /0                   | KHZ  |

|                   | Frequency           |                        |          |                                                  |                      |      |

| $\Delta f$ _Temp  | Temperature         | -20℃ to 100℃           |          | 5                                                |                      | %    |

|                   | Stability           |                        |          |                                                  |                      |      |

| Δf VDD            | Frequency Voltage   | VDD=12 to 24V          |          | 5                                                |                      | %    |

|                   | Stability           | 12D-12 W 2TV           |          |                                                  | 60<br>85<br>0<br>0.3 |      |

| RI_range          | Operating RI range  |                        | 12       | 24                                               | 60                   | Khom |

| V_RI_open         | RI open voltage     |                        |          | 2                                                |                      | V    |

| F_BM              | Burst mode Base     |                        |          | 22                                               |                      | KHz  |

| 1_DM              | frequency           |                        |          | 22                                               | 60<br>85<br>0        | IZIZ |

| DC max            | Maximum Duty        |                        | 75       | 80                                               | 85                   | %    |

| DC_max            | Cycle               |                        | 1,3      | 24 60 1<br>2 2 2 1<br>80 85 9<br>0 9<br>18 100 1 | 70                   |      |

| DC min            | Minimum Duty        |                        |          |                                                  | 0                    | %    |

|                   | Cycle               |                        |          |                                                  |                      | /0   |

| Gate Drive Output |                     |                        | _        |                                                  |                      |      |

| VOL               | Output low level    | Io=-20mA               |          |                                                  | 0.3                  | V    |

| VOH               | Output high level   | Io=+20mA               | 11       |                                                  |                      | V    |

| VG Clamp          | Output Clamp        | VDD=20V                |          | 18                                               |                      | v    |

| vo_clamp          | Voltage Level       | V DD-20 V              |          | 10                                               |                      | v    |

| T_r               | Output rising time  | C <sub>GATE</sub> =1nF |          |                                                  |                      | ns   |

| T_f               | Output falling time | C <sub>GATE</sub> =1nF |          | 50                                               |                      | ns   |

| Over Temperature  |                     |                        |          |                                                  |                      |      |

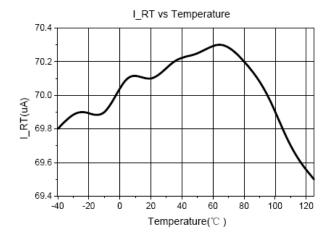

| I RT              | Output Current of   |                        |          | 70                                               |                      | uA   |

| 1_1(1             | RT Pin              |                        |          | 70                                               |                      | ur.  |

| VTH OTP           | OTP Threshold       |                        | 1        | 1.065                                            | 1 13                 | v    |

| VIII_011          | Voltage             |                        | <u> </u> | 1.005                                            | 1.13                 | v    |

| VTH_OTP_off       | OTP Recovery        |                        |          | 1 165                                            |                      | v    |

| VIII_01F_0II      | Threshold Voltage   |                        |          | 1.105                                            |                      | v    |

| TD OTP            | OTP De-bounce       |                        |          | 100                                              |                      | uSec |

| TD_OTP            | Time                |                        |          | 100                                              |                      | usec |

| V_RT_Open         | RT Pin Open         |                        |          | 3.5                                              |                      | v    |

| ·_m_open          | Voltage             | Io=-20mA               |          | '                                                |                      |      |

#### OPERATION DESCRIPTION

The WIS2269 is a highly integrated, high performance current mode PWM controller chip. Applicable to high power notebook power adapter switching power supply and switching power converters. Very low starting current and operating current, and light load or no load situations burstmode function, can effectively reduce the switching power supply system, standby power consumption, improve power conversion efficiency. Built-in synchronized slope compensation of the feedback pin of the leading edge blanking and other functions can not only reduce the number of switching power supply system components, but also increase the stability of the system, to avoid the production of harmonic oscillation. WIS2269 also offers a variety of comprehensive resume protected mode. Features functions described as follows:

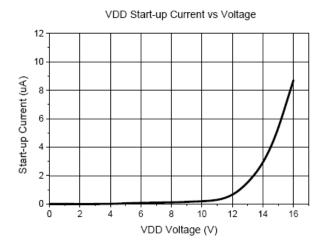

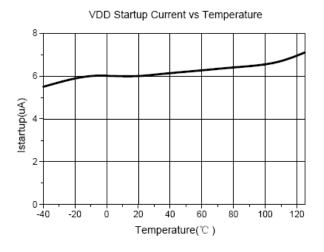

## Startup Current and Start up Control

Startup current of WIS2269 is designed to be very low(6.5uA) so that VDD could be charged up above UVLO threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet provides reliable startup in application. For AC/DC adaptor with universal input range design, a 2 M $\Omega$ , 1/8 W startup resistor could be used together with a VDD capacitor to provide a fast startup and low power dissipation solution.

## **Operating Current**

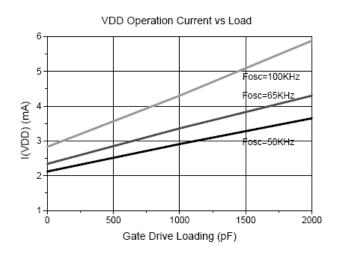

The Operating current of WIS2269 is low at 2.3mA. Good efficiency is achieved with WIS2269 low operating current together with extended burst mode control features.

#### **Burst Mode**

At no load or light load conditions, switching power supply in most of the power comes from the MOSFET's switching losses, transformer core losses and the loss of the buffer circuit. The size and power consumption within a certain period of time proportional to the number of MOSFET switches. Reduce the switching frequency also reduces power consumption, saving energy. WIS2269 built-in Burst Mode feature that automatically adjusts according to load switch mode. When the system is in no load or light / medium load, FB terminal voltage at the pulse input mode (BurstMode) threshold voltage (1.8V) below. According to the judge based on the device into the pulse mode control. Gate driver output voltage only when the VDD level below the pre-set value, and the FB input is active cases does the output. Other cases, the gate drive output to maintain the status of long-off to reduce consumption, which reduces standby consumption. The characteristics of high-frequency switch also reduced the audio noise at work.

#### Oscillator Operation

A resistor connected between RI and GND sets the constant current source to charge/discharge the internal cap and thus the PWM oscillator frequency is determined. The relationship between RI and switching frequency follows the below equation within the specified RI in Kohm range at nominal loading operational condition.

$$Fosc = \frac{1560}{RI(K\Omega)}(KHz)$$

## Current Sensing and Leading Edge Blanking

Cycle-by-Cycle current limiting is offered in WIS2269 current mode PWM control. The switch current is detected by a sense resistor into the sense pin. An internal leading edge blanking circuit chops off the sense voltage spike at initial MOSFET on state due to Snubber diode reverse recovery so that the external RC filtering on sense input is no longer required. The current limit comparator is disabled and thus cannot turn off the external MOSFET during the blanking period. PWM duty cycle is determined by the current sense input voltage and the FB input voltage.

#### Internal Synchronized Slope Compensation

Built-in slope compensation circuit adds voltage ramp onto the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

#### Gate Drive

WIS2269 Gate is connected to an external MOSFET gate for power switch control. Too weak the gate drive strength results in higher conduction and switch loss of MOSFET while too strong gate drive output compromises the EMI. A good tradeoff is achieved through the built-in totem pole gate design with right output strength and dead time control. The low idle loss and good EMI system design is easier to achieve with this dedicated control scheme. An internal 18V clamp is added for MOSFET gate protection at higher than expected VDD input.

## Over-temperature protection

Between RT and GND, and a common thread of a NTC resistor, can provide temperature sensing and protection. NTC resistance with the ambient temperature rises. With a fixed internal current flows through the resistor IRT, RT pin voltage with temperature

The rises. Within the OTP circuit to detect the voltage is less than VTH\_OP then triggered off when the MOSFET

#### Protection Controls

WIS2269 provides comprehensive protection features, the system can obtain the highest reliability. Including byweek limit protection (OCP), over-load protection (OLP), over-temperature protection (OTP), on-chip VDD over-voltage protection (OVP, optional), and low-voltage shutdown (UVLO).

When the ER into the VIN pin large, OCP threshold value is automatically reduced. OCP threshold slope adjustment helps compensate for over-current detection and control of AC voltage delay caused by the increasing of the power limit.

Recommended by WIS2269 OCP compensation circuit can obtain constant output power limit. WIS2269 OCP protection circuitry built-in can detect the duty cycle of PWM control signals, and through the line voltage compensation ensure a continuous AC input voltage range was constant output power limit.

In the case of output overload, FB bias voltage was higher, when FB input exceeds the power limit threshold.

voltage continue to 80ms, the control circuit will turn off MOSFET. Similarly, the control circuitry detects over-temperature in the case will be closed when the MOSFET. WIS2269 hysteresis temperature value at a temperature lower

than after the recovery. VDD output from the transformer provide the sub-winding. VDD is clamped at 36V. When VDD below the UVLO threshold time, MOSFET is turned off, the device and then entered on the electronic activation.

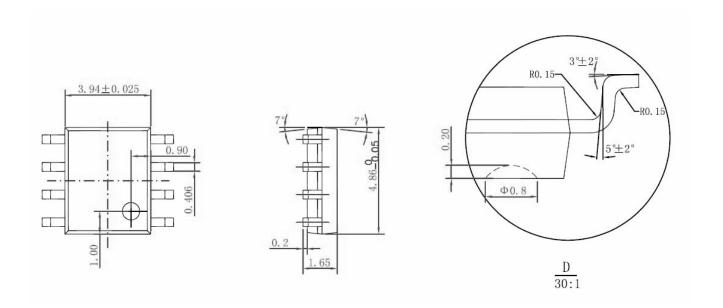

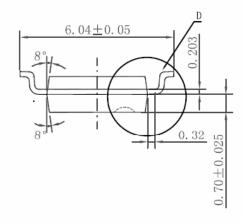

## SOP-8 Package Dimension