www.DataSheet4U.com

KAOHSIUNG FACTORY : NO. 18 Ta-Yeh St., Ta-Fa Industrial Park, Ta-Liao Hsiang, Kaohsiung Hsien 831, TAIWAN , R.O.C. TEL : 886-7-788-6800 FAX : 886-7-788-6806~8

# PART NO : <u>GG1206N8SKN1T</u> FOR MESSRS :

## **CONTENTS**

| NO. | ITEM                                           | PAGE  |

|-----|------------------------------------------------|-------|

| 1.  | COVER                                          | 1     |

| 2.  | RECORD OF REVISION                             | 2     |

| 3.  | GENERAL SPECIFICATION AND MECHANICAL DATA      | 3     |

| 4.  | ABSOLUTE MAXIMUM RATINGS                       | 4     |

| 5.  | ELECTRICAL AND OPTICAL CHARACTERISTICS         | 5~7   |

| 6.  | OUTLINE DIMENSION AND INTERFACE PIN CONNECTION | 8~11  |

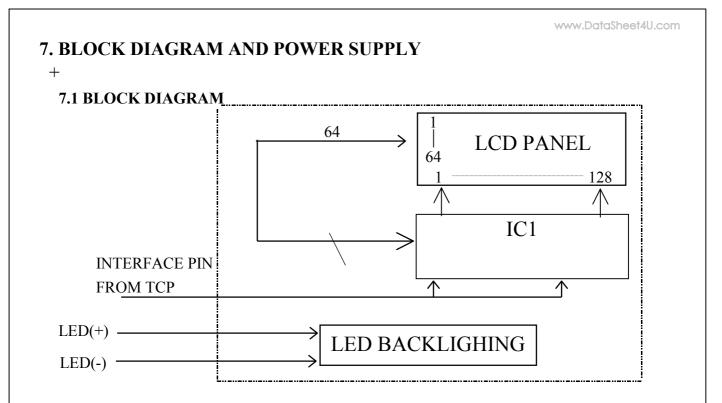

| 7.  | BLOCK DIAGRAM AND POWER SUPPLY                 | 13    |

| 8.  | DISPLAY CONTROL INSTRUCTIONS                   | 14~31 |

Accepted by : \_\_\_\_\_

Proposed by :

Date : 10,25,2002

SOLOMON GOLDENTEK DISPLAY CORP. TEL : 886-7-788-6800 FAX : 886-7-788-6806~8

GG1206N8SKN1T

PAGE : 1

**REV** : 1

www.DataSheet4U.com

# RECORD OF REVISION

|                                                                  | DATE                 | PAGE                  | SUMMARY            |          |

|------------------------------------------------------------------|----------------------|-----------------------|--------------------|----------|

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  |                      |                       |                    |          |

|                                                                  | L                    |                       |                    |          |

| DIOMON GOLDENTEK DISPLAY CORP. GG1206N8SKN1T REV:1               | OLOMON GOLDI         | ENTEK DISPLAY COR     | P. GG1206NIQCVNIT  | REV : 1  |

| EL: 886-7-788-6800 FAX: 886-7-788-6806~8 OG12001085K1N11 PAGE: 2 | `EL : 886-7-788-6800 | FAX : 886-7-788-6806~ | 8   001200105K1111 | PAGE : 2 |

www.DataSheet4U.com

## 3. GENERAL SPECIFICATIONS AND MECHANICAL DATA 3.1 GENERAL SPECIFICATIONS PLEASE REFER TO: "CUSTOMER ACCEPTANCE STANDARD SPECIFICATIONS (SP-10-000)".

**3.2 THIS INDIVIDUAL SPECIFICATION IS PRIOR TO GENERAL SPECIFICATIONS.**

## **3.3 MECHANICAL DATA**

- (1) NUMBER OF DOTS ------ 128Wx 64H DOTS

- (2) MODULE SIZE ------ 71.0Wx 59.3Hx 2.0D (MAX.) mm

- (3) VEWING AREA ----- 67.0W× 37.0H mm

- (4)DISPLAY AREA ----- 64.41Wx 30.69Hmm

- (5) DOT SIZE ----- 0.45W× 0.45H mm

- (6) DOT PITCH ----- 0.48W× 0.48H mm

- (7) VIEWING DIRECTION ----- 6 O'CLOCK

- (8) LCD COLOR ------ STN, GRAY, TRANSFLECTIVE

| SOLOMON      | GOLDEN   | ГЕК | DISPLAY     | CORP.   |

|--------------|----------|-----|-------------|---------|

| TEL : 886-7- | 788-6800 | FAX | : 886-7-788 | -6806~8 |

www.DataSheet4U.com

# 4. ABSOLUTE MAXIMUM RATINGS4.1 ELECTRICAL ABSOLUTE MAXIMUM RATINGS

| ITEM                   | SYMBOL  | MIN. | MAX. | UNIT | COMMENT  |

|------------------------|---------|------|------|------|----------|

| POWER SUPPLY FOR LOGIC | VDD-VSS | 2.4  | 6.0  | V    |          |

| INPUT VOLTAGE          | VI      | VSS  | VDD  | V    |          |

| STATIC ELECTRICITY     |         |      | 100  | V    | NOTE (1) |

NOTE (1) : TEST METHOD AND CONDITIONS AFTER CHARGING UP 200PF CAPACITOR BY STATED VOLTAGE, THE CAPACITOR IS CONNECTED WITH INTERFACE PINS OF THE MODULE.

#### 4.2 ENVIRONMENTAL ABSOLUTE MAXIMUM RAINGS

| ITEM                | OPER           | ATING                 | STO            | RAGE                 | COMMENT                |

|---------------------|----------------|-----------------------|----------------|----------------------|------------------------|

|                     | MIN.           | MAX.                  | MIN.           | MAX.                 | COMMULINI              |

| AMBIENT TEMPERATURE | 0°C            | 50°C                  | -20°C          | 60°C                 | NOTE (2)               |

| HUMIDITY            | NOTE (3)       |                       | NOTE (3)       |                      | WITHOUT CONDENSATION   |

|                     |                | $4.9 \text{ m/s}^2$   |                | $19.6 \text{ m/s}^2$ | 10~300HZ XYZ           |

| VIBRATION           |                | (0.5G)                |                | (2G)                 | DIRECTIONS 1 Hr. EACH  |

| SHOCK               |                | 29.4 m/s <sup>2</sup> |                | $49.0 \text{ m/s}^2$ | 10 ms XYZ              |

| SHOCK               |                | (3G)                  |                | (5G)                 | DIRECTIONS 1 TIME EACH |

| CORROSIVE GAS       | NOT ACCEPTABLE |                       | NOT ACCEPTABLE |                      |                        |

NOTE (2) : Ta AT -20°C : 48HR MAX. Ta AT 60°C : 168HR MAX.

NOTE (3) : Ta  $\leq 40^{\circ}$ C : 90% RH MAX.

Ta > 40°C : ABSOLUTE HUMIDITY MUST BE LOWER THAN THE HUMIDITY OF 90%RH AT 40°C . (50% RH AT 50°C )

| SOLOMON GOLDENTEK DISPLAY CORP.           | GG1206N8SKN1T | REV : 1 |

|-------------------------------------------|---------------|---------|

| TEL: 886-7-788-6800 FAX: 886-7-788-6806~8 |               | PAGE:4  |

www.DataSheet4U.com

## **5. ELECTRICAL AND OPTICAL CHARACTERISTICS**

#### **5.1 ELECRICAL CHARACTERISTICS**

| $Ta = 25^{\circ}C$                       | VDD = 2.4V  | ~6.0V              |         |       |         |      |

|------------------------------------------|-------------|--------------------|---------|-------|---------|------|

| ITEM                                     | SYMBOL      | CONDITION          | MIN.    | TYP.  | MAX.    | UNIT |

| LOGIC CIRCUIT<br>POWER SUPPLY<br>VOLTAGE | VDD-VSS     |                    | 2.4     |       | 6.0     | V    |

| INPUT VOLTAGE                            | VOH         | NOTE (1)           | 0.7*VDD |       | VDD     | V    |

| INPUT VOLTAGE                            | VOL         | NOTE (1)           | GND     |       | 0.3*VDD | V    |

| LOGIC CIRCUIT<br>POWER SUPPLY<br>CURRENT | IDD         | VDD-VSS<br>=5.0V   |         | 1.0   | 3.0     | mA   |

| RECOMMENDED                              | VDD - VO    | Ta = 0°C           |         |       |         | V    |

| LCD DRIVING                              | DUTY = 1/64 | $Ta = 25^{\circ}C$ |         | (8.8) |         | V    |

| VOLTAGE (NOTE 1)                         | § =10°      | $Ta = 50^{\circ}C$ |         |       |         | V    |

NOTE (1): CS1, CS2, R/W, D/I, DB0~DB7, E, RST

NOTE (2): RECOMMENDED LCD DRIVING VOLTAGE MAY FLUCTUATE ABOUT  $\pm$  0.5V BY EACH MODULE.

SOLOMON GOLDENTEK DISPLAY CORP. TEL : 886-7-788-6800 FAX : 886-7-788-6806~8

GG1206N8SKN1T

REV : 1 PAGE : 5

www.DataSheet4U.com

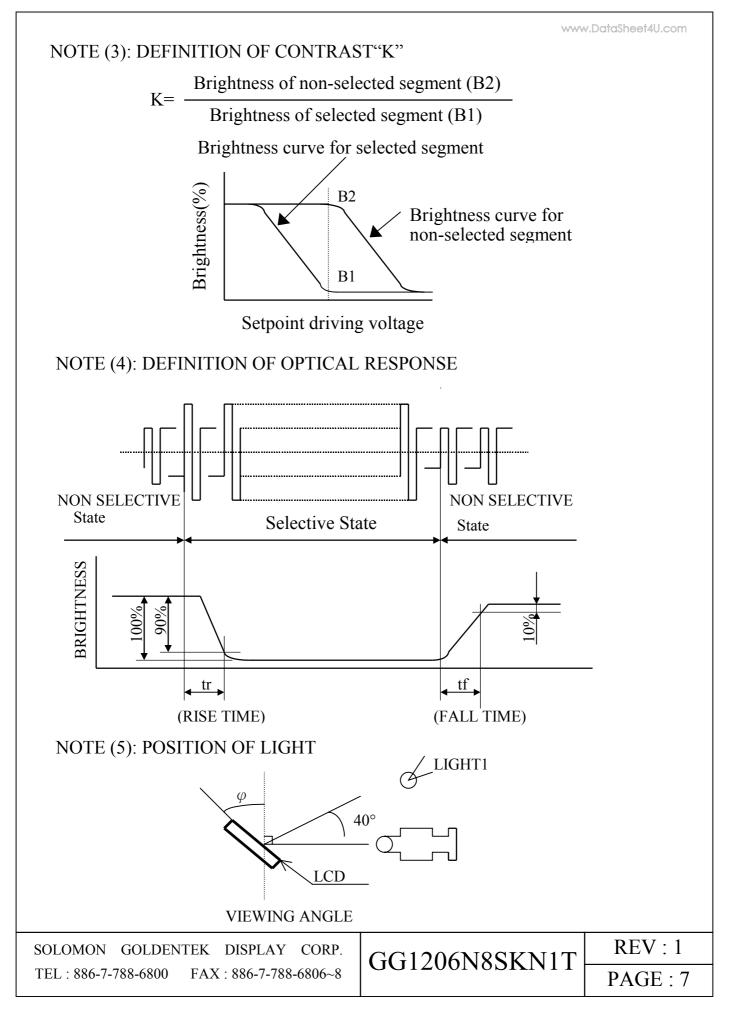

#### **5.2 OPTICAL CHARACTERISTICS**

| $Ta = 25^{\circ}C$ | VDD = 2  | .4V~6.0V                                 |      |      |      |      |

|--------------------|----------|------------------------------------------|------|------|------|------|

| I T E M            | SYMBOL   | CONDITION                                | MIN. | TYP. | MAX. | UNIT |

| VIEWING AREA       | Ф2-Ф1    | $K \ge 1.4$                              | 20   |      |      | deg. |

| CONTRAST RATIO     | К        | $\Phi = 10^{\circ}$ $\Theta = 0^{\circ}$ |      | 4    |      |      |

| DESDONSE TIME      | tr(rise) | $\Phi = 10^{\circ}$ $\Theta = 0^{\circ}$ |      | 250  | 350  | ms   |

| RESPONSE TIME      | tf(fall) | $\Phi = 10^{\circ}$ $\Theta = 0^{\circ}$ |      | 300  | 400  | ms   |

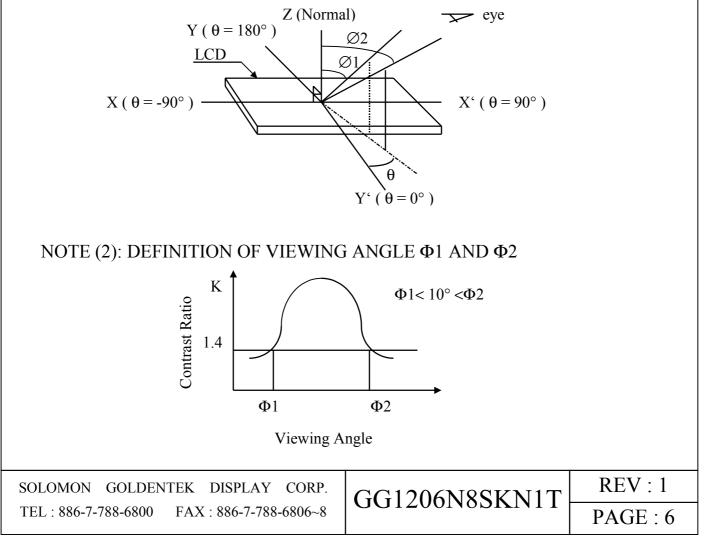

## NOTE (1): DEFINITION OF $\theta$ AND $\Phi$

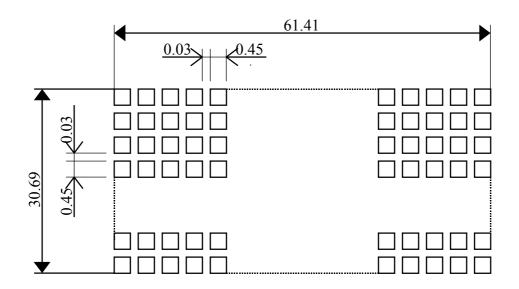

## 6. OUTLINE DIMENSION

www.DataSheet4U.com

| r - 1            | ر<br>ب<br>ب |           | ЭМАХ <u>.</u><br>4.8 |                           |         | 67           | 71.0<br>2.0MIN.4<br>61.41 ±             | (V,A,)                  |       |                          |             |      | 0.7 ±0.0   |               | 0MAX.<br>7 ±0.07 |     |

|------------------|-------------|-----------|----------------------|---------------------------|---------|--------------|-----------------------------------------|-------------------------|-------|--------------------------|-------------|------|------------|---------------|------------------|-----|

| 59.3±0.5<br>43.5 | 40.5        | 30.69±0.1 |                      |                           |         | 0.48<br>0.45 |                                         | 0.45                    |       |                          |             |      |            | Ç             |                  |     |

|                  |             | 7.35      |                      | . 17.5<br>. 14.5<br>. 9.2 |         | P1.0         | 36.(<br>36.(<br>#42=4<br>w=0.5:<br>52.6 | <u>2.0 ±0.</u><br>±0.05 |       |                          |             |      |            |               | )MAX.            |     |

| PIN              | 1           | 2         | 3                    | 4                         | 5       | 6            | 7                                       | 8                       | 9     | 10                       | 11          | 12   | 13         | 14            | 15               | 16  |

| SYMBOL           | N.C         | FR        | CL                   | DOF                       | CS1     | CS2          | RES                                     | A0                      | R/W   | Е                        | D0          | D1   | D2         | D3            | D4               | D5  |

| PIN              | 17          | 18        | 19                   | 20                        | 21      | 22           | 23                                      | 24                      | 25    | 26                       | 27          | 28   | 29         | 30            | 31               | 32  |

| SYMBOL           | D6          | D7        | VDD                  | VSS                       | VSS2    | VOUT         | CAP3-                                   | CAP1+                   | CAP1- | CAP2-                    | CAP2+       | VRS  | VDD        | V1            | V2               | V3  |

| PIN              | 33          | 34        | 35                   | 36                        | 37      | 38           | 39                                      | 40                      | 41    | 42                       | 43          |      |            |               |                  |     |

| SYMBOL           | V4          | V5        | VR                   | VDD                       | M/S     | CLS          | C86                                     | P/S                     | NUI   | SPEC<br>T : mr<br>LE : Ì |             | TOL  | ERAN       | ICE: <u>-</u> | =0.3             |     |

| SOLOMO           | N G         | OLDE      | INTER                | C DIS                     | SPLAY   | CC           | ORP.                                    |                         |       | 061                      | <b>18</b> 5 | K VI | <u>1</u> Т | I             | REV              | :1  |

| TEL : 886        | -7-788      | 8-6800    | FA                   | X : 88                    | 86-7-78 | 88-680       | 6~8                                     |                         |       | ,001                     | 100         | 1711 | 11         | P             | AGE              | 2:8 |

www.DataSheet4U.com

## NOTE (1): DETAIL DRAWING OF MATRIX PATTERN

#### INTERFACE CONNECTOR PIN

| Pin Name | I/O |                                        | Function                               |                              |                             |                  |  |  |  |  |  |  |

|----------|-----|----------------------------------------|----------------------------------------|------------------------------|-----------------------------|------------------|--|--|--|--|--|--|

| COM0     | О   | These are te liquid crys               | stal common driv                       | ve output.                   |                             |                  |  |  |  |  |  |  |

| to       |     | Part No.                               | COM                                    |                              | Part NO.                    |                  |  |  |  |  |  |  |

| COM31    |     | SED1565*                               | COM0~CO                                | M63                          | SED1565*                    | 64               |  |  |  |  |  |  |

|          |     | SED1566*                               | COM0~CO                                | M47                          | SED1566*                    | 48               |  |  |  |  |  |  |

|          |     | SED1567*                               | COM0~CO                                | M31                          | SED1567*                    | 32               |  |  |  |  |  |  |

|          |     | Through a combination VDD,V1,V4,and V5 | n of the contents                      | of the scan data and with th | e FR signal, a single level | is selected from |  |  |  |  |  |  |

|          |     | Scan Da                                | ta                                     | FR                           | Ou                          | tput Voltage     |  |  |  |  |  |  |

|          |     | Н                                      |                                        | Н                            |                             | V5               |  |  |  |  |  |  |

|          |     | Н                                      |                                        | L                            |                             | VDD              |  |  |  |  |  |  |

|          |     | L                                      |                                        | Н                            |                             | V1               |  |  |  |  |  |  |

|          |     | L                                      |                                        | L                            |                             | V4               |  |  |  |  |  |  |

|          |     | Power Sa                               | ve                                     |                              |                             | VDD              |  |  |  |  |  |  |

| COMS     | 0   | These ae the COM out                   | put terminals for                      | ls output the same signal.   |                             |                  |  |  |  |  |  |  |

|          |     | Leave these open if the                | Leave these open if they are not used. |                              |                             |                  |  |  |  |  |  |  |

|          |     | When in master/slave                   | mode, the same                         | signal is output by both mas | ter and slave.              |                  |  |  |  |  |  |  |

SOLOMON GOLDENTEK DISPLAY CORP. TEL : 886-7-788-6800 FAX : 886-7-788-6806~8

GG1206N8SKN1T

REV : 1

PAGE:9

| VSS     POWER SUPPLY     This is no V terminal connected to the system (SD.)       VSS     POWER SUPPLY     This is no certainly input VREG power supply for the 1CD power supply voltage regulator.       VSS     POWER SUPPLY     This is no certainly input VREG power supply for the 1CD power supply or longer regulator.       V122     POWER SUPPLY     This is a multi-velop power supply for the low voltage drivide or through changing the impedance to an on power supply criticalis produce the V1 to V4 voltage shown below.     V/D/C       V152     POWER SUPPLY     Master operation.     When the power supply the the voltage activation and the carbon set of the state of the voltage activation and the carbon set of the voltage activation and the CAP-terminal.       CAP1+     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2-terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1-terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal a                                                                                                                                                                                                                                                                                                                        | PIN NAME<br>VDD | I/O<br>POWER SUPPLY | Shared with the N                                        | IPU nower       | supply t      | FOUNCTION<br>erminal Vcc | \AAAA                                 | DataSheet4U.con         |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------|----------------------------------------------------------|-----------------|---------------|--------------------------|---------------------------------------|-------------------------|--|--|

| VYSE     POWER SUPPLY     This is the reference power supply for the step-up voltage crount for the luquid crystal drive.       VRS     POWER SUPPLY     This is the reference power supply for the ICD power supply voltage regulator       V1.02     POWER SUPPLY     This is a multi-level power supply for the liquid crystal drive. The voltage applied is determined by the liquid crystal drive. The voltage applied is determined by the liquid crystal drive. The voltage applied is determined by the input drive.       V1.9     POWER SUPPLY     This is a multi-level power supply for the liquid crystal drive. The voltage applied is determined by the input drive.       V1.9     POWER SUPPLY     This is a multi-level power supply for the liquid crystal drive. The voltage applied is determined by the input drive.       V1.9     POWER SUPPLY     This is a multi-level power supply for the liquid crystal drive. The voltage criteria crystal drive.       V3.4     V3     are applied in the power supply turns ON, the internal applied increating internal internal.       V3.4     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP1-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP3-     O     DC/DC voltage conv                                                                                                                                                                                                                                                                                              |                 |                     |                                                          | *               |               |                          |                                       |                         |  |  |

| VRS     POWER SUPPLY     This is the estemally-input VEEG power supply for the LCD power supply voltage regulator :<br>These are only enabled for the models with the VEEG external input option.       V1.V2     POWER SUPPLY     This is a multi-hevel power supply for the liquid crystal dirts. The voltage applied is determined by the liquid<br>crystal ecl, and a changed through the use of a resistive voltage direded or through changing the impedance us<br>and on pum. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown<br>below.       VDD     VDV/VDV2/V2/V2/V32/V42V5     Master operation :When the power supply times ON, the internal power supply circuits produce the V1 to V4<br>voltage shown below. The voltage scattering are selected using the LCD bias set command.       CAP1+     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAP1 terminal.       CAP2-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAP1 terminal.       CAP2-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAP1 terminal.       VR     1     Output voltage converter Connect a capacitor between this terminal and the CAP1 terminal.       VR     1     Output voltage converter Connect a capacitor between the streaminal and the CAP1 terminal.       VR     1     Output voltage converter Connect a capacitor between the streaminal and the CAP1 terminal.       VR     1     Output vol                                                                                                                                                                                                                            |                 |                     |                                                          |                 |               |                          | the liquid crystal driv               | 20                      |  |  |

| VI.V2     VI.V2 <th< td=""><td></td><td></td><td>-</td><td></td><td>-</td><td></td><td></td><td></td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                     | -                                                        |                 | -             |                          |                                       |                         |  |  |

| V1.V2   POWER SUPPLY   This is a multi-level power supply for the liquid cystal drive. The voltage inpide is determined by the liquid cystal eql, and is changed through the use of a resistive voltage divided or through changing the impedance as an op amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.     VD   VDD-(V10)EV122EV32V42V5     Master operation. When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltage shown below.   VDD/PO/DEV122V32V32V42V5     CAP1+   O   DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     CAP2+   O   DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     CAP2-   O   DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     CAP3-   O   DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     CAP3-   O   DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     V0IT   O   DD/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     V0IT   O   DD/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     V0IT   O   DD/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.     VR   I <td>VIC</td> <td>TOWER SOTTET</td> <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                          | VIC             | TOWER SOTTET        | -                                                        |                 |               |                          |                                       |                         |  |  |

| V3.V4 crystal cell, and is changed through the use of a resistive voltage divided or theogh changing the impedance us an op amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.   V10L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V1 V2           | POWER SUPPLY        |                                                          |                 |               |                          |                                       | ermined by the liquid   |  |  |

| V5     an op amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown<br>below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 | TOWERBOITET         | -                                                        |                 | -             |                          |                                       |                         |  |  |

| below:     VDD(-V0)2V12V22V32V42V5       Master operation: "When the power supply turns ON, the internal power supply circuits produce the V1 to V4       Voltage shown below. The voltage settings are selected using the 1CD bias set command.       CAP1+     O       O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.       CAP2+     O       O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.       CAP2-     O       O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.       CAP2-     O       O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.       VR     1     Output voltage regulator internal resistors are used (RS="17).<br>these cannot be used when the 'S voltage regulator internal resistors are used (RS="17).<br>these cannot be used when the 'S voltage regulator internal resistors are used (RS="17).       D7 to D0     100     This is an 8-bit bi-directional dua to that connects to an 8-bit of 16 bit standard MPU dua bas.       (St)     and D6 serves as the serial clock input terminal. (SCL). At this time, D0 to D7 are set to high impedance. When the chap select is inactive, D0 to D7 are display data. A0="1".idicates that D0 to D7 are control data.       /RES     1     When (RES is set to "1'he settings                                                                                                                                                                                                                                                                                                                                  |                 |                     | -                                                        |                 |               | -                        |                                       |                         |  |  |

| VDQ-V0j2V12V22V32V42V5       Master operation : When the power supply turns ON , the internal power supply circuits produce the V1 to V4 voltage shown below. The voltage settings are selected using the LCD bias set command.       CAPI-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI - terminal.       CAP2-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI - terminal.       CAP2-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI - terminal.       CAP3-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI - terminal.       VWR     1     Output voltage regulator terminal. Provides the voltage between VDI and V5 through a resistive voltage drive These are only enabled when the V5 voltage regulator interminal resistors are not used(RS="1").       D7 to D0     I/O     This is an 8-bit bi-directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.       (Si)     When the serial interface is selected (PS="1", then D7 serves as the serial data in input terminal (SI) and D6 serves as the serial data view. D0 to D7 are voltage between VD1 to D7 are control data.       A0     1     This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data tare data or a command.       (SI)     and D6 serves as the serial data to C21. At this tititin, D0 to D7 are control data.                                                                                                                                                                                                                                   |                 |                     |                                                          |                 |               |                          |                                       |                         |  |  |

| Master operation: When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltage advants below. The voltage settings are selected using the LCD bias set command.       CAP1+     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP2+     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP3-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       CAP3-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       VR     I     Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divide.       VR     I     Output voltage regulator internal resistors are not sed(RS=1').       O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       (S)     I     Output voltage regulator internal resistors are not sed(RS=1').       O     DD/D     IO     Dis is a S=bit b-directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.       (S)     II     Other the set signal theor.     Dit D7 are set to high impedance.                                                                                                                                                                                                                                                                                                                                                                |                 |                     | VDD(=V0)≥V1≥V2≥                                          | V3≥V4≥V5        |               |                          |                                       |                         |  |  |

| CAPI+   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.     CAPI+   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.     CAP2+   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP2+ terminal.     CAP3-   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP2+ terminal.     CAP3-   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP2+ terminal.     VR   I   Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divid<br>These are only enabled when the V5 outlage regulator internal resistors are not used(R85-TL7).<br>these cannot be used when the V5 outlage regulator internal resistors are not used(R85-TL7).<br>these cannot be used when the V5 outlage regulator internal resistors are not used(R85-TL7).<br>these are only enabled when the V5 outlage regulator internal resistors are not used(R85-TL7).<br>these are only enabled when the V5 outlage regulator internal resistors are not used(R85-TL7).<br>these are only enabled when the V5 outlage regulator internal resistors are used (R85-TL7).<br>these are not used(R85-TL7).<br>The the chip select is inactive, D0 to D7 are set to high impedance.<br>This is connect to the least significant bit of the normal MPU data bus.<br>are eat a or a command.<br>A0 The indicates that D0 to D7 are set to high impedance.     A0   I   This is connect to the "The settings are initialized.<br>The reset operation is performed by the 'RES signal level.                                                                                                  |                 |                     |                                                          |                 | supply turi   | ns ON, the internal p    | ower supply circuits j                | produce the V1 to V4    |  |  |

| CAPI     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.       CAP2+     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.       CAP3-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.       CAP3-     O     DC/DC voltage converter Connect a capacitor between this terminal and the CAPI+ terminal.       VR     I     Output voltage converter Connect a capacitor between this terminal and VS through a resistive voltage divided to the set of the set of voltage regulator internal resistors are not used(IRS="1").       D7 to D0     UO     This is an 8-bit bit-directional data bus that connects to an 8-bit ot 16 bit standard MPU data bus.       (S1)     and Do serves as the serial obte finant terminal (S1).     and Do serves as the serial obter function terminal (S1).       A0     I     This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bare can output statis when the visit obter more data. A0="1".'Idicates that D0 to D7 are control data.       //RES     I     When Res is set of when the RS signal level.       //CS1.CS2     I     This is the financiant by the /RES signal level.       //CS1.CS2     I     This is the financiant of the RS signal of the 8080 MPU and the SED 1565 series data bus is in an output statasit when th                                                                                                                                                                                                                                                                                              |                 |                     | voltage shown below.                                     | The voltage s   | ettings are   | selected using the LO    | CD bias set command                   | l.                      |  |  |

| CAP2-   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP2- terminal.     CAP2-   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP1+ terminal.     CAP3-   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP1+ terminal.     VW   1   Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage drive these are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). These are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). These are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). These are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). The times are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). The times are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). The times are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). The times are only cambled when the V5 voltage regulator internal resistors are not usder(RS="L"). The time the chip select is and D0 to D3 are set to high impedance. Whe the chip select is in active, D0 to D7 are set to high impedance.     A0   1   This is a connect to the least significant bit of the normal MPU address bus, and it determines whether the data tare data or a command.     A0   1   This is to connect to the RSS tignal of the S00 MPU.     A1   The resist operation is performed by the rRES signal level.     <                                                                                   | CAP1+           | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | I and the CAP1- term                  | ninal.                  |  |  |

| CAP2-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2- terminal.       CAP3-     O     DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.       VW     1     Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divid. These are only enabled when the V5 voltage regulator internal resistors are not used (RES="1").       DT to D0     I/O     This is an 8-bit bi-directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.       (S1)     When the serial interface is selected (P/S="1"), then D7 serves as the serial data input terminal (S0)       (SCL)     and D6 serves as the serial data input terminal.       (SCL)     and D6 serves as the serial data input terminal CL). At this time, D0 to D5 are set to high impedance. Whe the chip select is inactive, D0 to D7 are display data. A0="1":licitates that D0 to D7 are control data.       A0     1     This is connect to the last significant bit of the normal MPU address bus, and it determines whether the data bit are tare accound by the /RES signal level.       //RES     1     When the CS1="1" and CS2="1" idicates that D0 to D7 are control data.       //REVE     1     When connected to an 8080 MPU, this is active LOW.       //REVE     1     When connected to a 8080 MPU, this is active LOW.       This is the 6800 Series MPU interminal. <td>CAP1-</td> <td>0</td> <td>DC/DC voltage conve</td> <td>erter.Connect</td> <td>a capacitor</td> <td>between this termina</td> <td>and the CAP1+ terr</td> <td>ninal.</td>                                                                                                           | CAP1-           | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | and the CAP1+ terr                    | ninal.                  |  |  |

| CAP3   O   DC/DC voltage converter Connect a capacitor between this terminal and the CAP1+ terminal.     VOUT   O   DC/DC voltage converter Connect a capacitor between this terminal and Vss     VR   I   Output voltage converter Connect a capacitor between this terminal and Vss     VR   I   Output voltage regulator timinal provides the voltage between VDD and V5 through a resistive voltage dvic These are only enabled when the V5 voltage regulator internal resistors are not usdet(RS="1").     D7 to D0   I/O   This is an 8-bit to bit standard MPU data bus.     (S1)   When the serial interface is selected (P/S="1", then D7 serves as the serial data input terminal (S1) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance. Whether the chip select is significant bit of the normal MPU address bus, and it determines whether the data bare data or a command.     A0   I   This is connect to the last significant bit of the normal MPU address bus, and it determines whether the data bare data or a command.     /RES   I   When (RES is set or "L" he settings are initialized.     /RES   I   When (RES is set or "L" he settings are initialized.     /RES   I   When (RCS is set or "L" and CS2="H", then the chip select becomes active, and data" output status when this signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this                                                                                                                                                                                                                                  | CAP2+           | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | I and the CAP2- term                  | ninal.                  |  |  |

| VOUT     O     DC/DC volage converter.Connect a capacitor between this terminal and Vss       VR     1     Output voltage regulator terminal. Provides the voltage between VDD and VS through a resistive voltage divid<br>These are only enabled when the VS voltage regulator internal resistors are used (IRS="1").       D7 to D0     I/O     This is an 8-bit bi-directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.       (S1)     and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance. Whe<br>the chip select is inactive, D0 to D7 are set to high impedance.       A0     1     This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data b<br>are data or a command.<br>A0="1":Indicates that D0 to D7 are display data. A0="1":Idicates that D0 to D7 are control data.       //RES     1     When R/EE is set to "1",the settings are initialized.<br>The reset operation is performed by the /RES signal level.       //CS1,CS2     1     This is the chip select to an 8080 MPU, this is active LOW.<br>This pin is connected to an 8080 MPU, this is active LOW.<br>This pin is connected to the R/D signal of the 8080 MPU and the SED 1565 series data bus is in<br>an output straus when this signal is "1".<br>When connected to a 8080 Series MPU this is active HIGH.<br>This is the 6800 Series MPU this is active HIGH.<br>This is the 6800 Series MPU this is active HIGH.<br>This is the 6800 Series MPU this is active HIGH.<br>This is the Red/write control signal input terminal.<br>When R/W="11".Red. When R/W="1".Write<br>Wren connected to a 80808 MPU this as active HIGH.<br>This is the Red/Write memost to the | CAP2-           | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | and the CAP2+ terr                    | ninal.                  |  |  |

| VR   I   Output voltage regulator terminal. Provides the voltage togulator internal resistors are used (RS="1").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CAP3-           | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | I and the CAP1+ terr                  | ninal.                  |  |  |

| These are only enabled when the V5 voltage regulator internal resistors are used (RS="1").       these cannot be used when the V5 voltage regulator internal resistors are used (RS="1").       D7 to D0     I/O       This is an 8-bit bid directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.       (S1)     When the serial interface is selected (P/S="1"), then D7 serves as the serial data input terminal (S1) and D5 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance.       A0     1     This is a concent to the least significant bit of the normal MPU datess bus, and it determines whether the data bare data or a command.       A0="H1".indicates that D0 to D7 are estro bigh impedance.       /RES     1     When /RES is set to "L" be settings are initialized.       The reset operation is performed by the /RES signal level.     ////////////////////////////////////                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VOUT            | 0                   | DC/DC voltage conve                                      | erter.Connect   | a capacitor   | between this termina     | ll and Vss                            |                         |  |  |

| these cannot be used when the v5 voltage regulator internal resistors are used (IRS="H').       D7 to D0     1/O     This is an 8-bit bi-directional data bus that connects to an 8-bit or 16 bit standard MPU data bus.       (S1)     and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance. Whe the chip select is inactive, D0 to D7 are set to high impedance.     A0       A0     I     This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data b are data or a command.     A0="H':Indicates that D0 to D7 are set to high impedance.       /RES     I     When /RES is set to "L' the settings are initialized.     The reset operation is performed by the /RES signal level.       //CS1,CS2     I     This is the chip select signal. When /CS1="L"and CS2="H",then the chip select becomes active, and data/command UO is cnable.       /RD(E)     I     When connected to a 8080 MPU, this is active LOW.       This is the 6800 Series MPU anable clock input termined.     When connected to a 6800 Series MPU.       /WR,(R/W)     I     When connected to a 8080 MPU, this is active LOW.       This is the cad/write control signal of the S080 MPU and the data bus are latched at the rising edge of the /WR signal.     The signals on the data bus are latched at the rising edge of the /WR signal.       /WR,(R/W)     I     When connected to a 6800 Series MPU interface.                                                                                                                                                                                                                                                                              | VR              | Ι                   | Output voltage regula                                    | tor terminal. I | Provides th   | e voltage between VI     | DD and V5 through a                   | resistive voltage divid |  |  |

| D7 to D0   I/O   This is an 8-bit bi-directional data bus that connects to an 8-bit of 16 bit standard MPU data bus.     (S1)   When the serial interface is selected (PS="1"), then D7 serves as the serial data input terminal (S1) and D6 serves as the serial chock input terminal (SCL). At this time, D0 to D5 are set to high impedance. Whe the chip select is inactive, D0 to D7 are set to high impedance.     A0   I   This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data be are data or a command. A0="H":Indicates that D0 to D7 are display data. A0="L":Idicates that D0 to D7 are control data.     /RES   I   When /RES is set to "L" the settings are initialized. The reset operation is performed by the /RES signal level.     /RCS1,CS2   I   This is the chip select signal. When /CS1 ="L"and CS2="I", then the chip select becomes active, and data/command I/O is enable.     /RD(E)   I   When connected to a 8080 MPU, this is active LOW. This is in a orupt status when this signal is "L". When connected to a 6800 Series MPU enable clock input termined.     /WR,(R/W)   I   When connected to a 8080 MPU with is active LOW. This is the read/write control signal is "L". When connected to a 6800 Series MPU is signal. The signals on the data bus are latched at the rising edge of the /WR signal.     /WR,(R/W)   I   When connected to a 6800 Series MPU is is active LOW. This is the read/write control signal input terminal.     /WR, (R/W)   I   When conneceted to a 6800 Series MPU interface.                                                                                                                                                                                |                 |                     | •                                                        |                 | -             | •                        |                                       | ,                       |  |  |

| (SI)   When the serial interface is selected (P/S="L"), then D7 serves as the serial data input terminal (SI)     (SCL)   and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance . Whe the chip select is inactive, D0 to D7 are set to high impedance.     A0   1   This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bar data or a command.     A0="H":Indicates that D0 to D7 are display data. A0="L":Idicates that D0 to D7 are control data.     /RES   1   When /RES is set to "L":the settings are initialized.     /RES   1   This is connected to an 8080 MPU, this is active LOW.     /RD(E)   1   When connected to an 8080 MPU, this is active LOW.     /This pin is connected to the R/D signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L".     .   When connected to an 8080 MPU, this is active HGH .     This is the 6800 Series MPU enable clock input termined.     /WR,(R/W)   1   When connected to a 8080 MPU with is active HGH .     This is the ead/write control signal input terminal.   When R/W= #T*:Read/WHO WR signal.     /Wen R/W="H":Read/Write Control signal input terminal.   When R/W=#T*:Read/When R/W=+T*:Write.     C86   1   This is the P0/Dimetrace switch terminal.     When R/W=#T*:Read/When R/W=+T*:Senia                                                                                                                                                                                                                                                                                                                                                             |                 |                     |                                                          |                 |               |                          |                                       |                         |  |  |

| (SCL)   and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance. Whe the chip select is inactive, D0 to D7 are set to high impedance.     A0   I   This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data b are data or a command. A0="11":Indicates that D0 to D7 are display data. A0="11":Indicates that D0 to D7 are control data.     //RES   I   When /RES is set to "1."the settings are initialized. The reset operation is performed by the /RES signal level.     //CSI_CS2   I   This is the chip select signal. When /CS1 ="1."and CS2="11";then the chip select becomes active, and data/command I/O is enable.     //RD,(E)   I   . When connected to a 8080 MPU, this is active LOW. This pin is connected to the (RD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "1.". When connected to a 6800 Series MPU inbit is active LOW. This is in is connected to a 6800 Series MPU inbit is active LOW. This is the read/write control signal input terminal. When R/N="11";Read. When R/N="11";Write.     //WR,(R/W)   I   . When connected to a 6800 MPU inbit is active LOW. This is the read/write control signal input terminal. When R/N="11";Read. When R/N="11";Write.     //WR, R/W)   I   . When connected to a 6800 Series MPU is active LOW. This is is the read/write control signal input terminal. When R/N="11";Read. When R/N="11";Read. When R/N="11";Write.     //WR, R/W)   I   . When connected to a 6800 Series MPU is active LOW. This is is the tread/write control sig                                                                                                                 |                 | I/O                 |                                                          |                 |               |                          |                                       |                         |  |  |

| A0   I   This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data b are data or a command.<br>A0-"H'.Indicates that D0 to D7 are display data. A0-"L":Idicates that D0 to D7 are control data.     /RES   I   When /RES is set to "L"the settings are initialized.<br>The reset operation is performed by the /RES signal level.     //RD(E)   I   This is the chip select signal. When /CS1 ="L"and CS2="H", then the chip select becomes active, and data/command I/O is enable.     //RD(E)   I   . When connected to an 8080 MPU, this is active LOW.<br>This pin is connected to the /RD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L".<br>. When connected to a 6800 Series MPU, this is active HGH .<br>This is the 6800 Series MPU enable clock input termined.     /WR,(R/W)   I   When connected to an 8080 MPU, this is active LOW.<br>This is the factor on 8080 MPU (Mis is active LOW .<br>This is the 6800 Series MPU in terminal.<br>. When connected to a 6800 Series MPU :<br>This is the read/write control signal input terminal.<br>. When connected to a 6800 Series MPU :<br>This is the read/write control signal input terminal.<br>. When R/W="H":Read, When R/W="L":Write.     C86   I   This is the MPU interface switch terminal.<br>. Read/Write C86="H":6800 MPU /WR signal at input.<br>The following applies depending on the P/S status:<br>.     P/S   I   This is the paralled data input/serial data input.<br>. The following applies depending on the P/S status:<br>.     P/S   I   This is the paralled data input/serial data input.<br>. The following a                                                                        |                 |                     |                                                          |                 |               |                          | -                                     |                         |  |  |

| A0   I   This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data b are data or a command.     A0   — H":Indicates that D0 to D7 are display data. A0="L":Idicates that D0 to D7 are control data.     /RES   I   When /RES is set to "L"the settings are initialized.     /RES   I   This is the chip select signal. When /CS1 ="L"and CS2="H",then the chip select becomes active, and data/command I/O is enable.     /RD,(E)   I   . When connected to a 8080 MPU, this is active LOW.     This is the chip select signal. When /CS1 ="L"and CS2="H",then the chip select becomes active, and data/command I/O is enable.     /RD,(E)   I   . When connected to a 8080 MPU, this is active LOW.     This is the 6800 Series MPU enable clock input termined.   . When connected to a 8080 MPU /WR signal . The signals on the data bus are latched at the rising edge of the /WR signal.     /WR,(R/W)   I   . When connected to a 6800 Series MPU : This is the read/write control signal input terminal.     /When R/W="H":Read. When R/W="L":Write.   This is the Parallel data input serial data input switch terminal.     /WR, (R/W)   I   . When CMC="L":Write.     /WR   I   This is the MPU interface. C86="L":%300 MPU interface     /WR   I   This is the parallel data input switch terminal.     When R/W=":L":Main data input sw                                                                                                                                                                                                                                                                                                                                                                                   | (SCL)           |                     |                                                          | -               | -             |                          | , D0 to D5 are set to                 | high impedance. Whe     |  |  |

| are data or a command.   A0="H":Indicates that D0 to D7 are display data. A0="L":Idicates that D0 to D7 are control data.     /RES   1   When /RES is set to "L" the settings are initialized.     The reset operation is performed by the /RES signal level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | -                   |                                                          |                 |               |                          |                                       |                         |  |  |

| A0="H":Indicates that D0 to D7 are display data. A0="L":Idicates that D0 to D7 are control data.     /RES   I   When /RES is set to "L"the settings are initialized.     /RES   I   The reset operation is performed by the /RES signal level.     //CS1,CS2   I   This is the chip select signal. When /CS1 ="L":Idicates that D0 to D7 are control data.     /RD,(E)   I   . When connected to an 8080 MPU ,this is active LOW.     This pin is connected to the <i>k</i> PD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L".     . When connected to a 6800 Series MPU this is active HIGH.     This is the 6800 Series MPU enable clock input termined.     /WR,(R/W)   I   . When connected to a 8080 MPU /this is active LOW.     This is the foot of the /WR signal.   . When connected to a 6800 Series MPU intermined.     /WR,(R/W)   I   . When connected to a 6800 Series MPU intermined.     /WR,(R/W)   I   . When connected to a 6800 Series MPU interminal.     . When connected to a 6800 Series MPU interminal.   . When R/W="H":Read. When R/W="L":Write.     C86   I   This is the Paralle data input. P/S="L":Sorial data input.     P/S   I   This is the paralle data input. P/S="L":Sorial data input.     P/S   Data/Command   Data   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A0              | I                   |                                                          | -               | ant bit of th | ne normal MPU addre      | ess bus, and it determine             | nes whether the data b  |  |  |

| /RES   1   When /RES is set to "L"the settings are initialized.<br>The reset operation is performed by the /RES signal level.     /CS1,CS2   1   This is the chip select signal. When /CS1 ="L"and CS2="H",then the chip select becomes active, and data/command I/O is enable.     /RD,(E)   1   . When connected to an 8080 MPU, this is active LOW.<br>This pin is connected to the /RD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L".<br>. When connected to a 6800 Series MPU, this is active HIGH.<br>This is it the 6800 Series MPU enable clock input termined.     /WR,(R/W)   1   . When connected to a 8080 MPU, this is active LOW .<br>This terminal connects to the 8080 MPU /WR signal .The signals on the data bus are latched at the rising edge of the /WR signal input terminal.<br>. When connected to a 6800 Series MPU :<br>This is the read/write control signal input terminal.<br>. When connected to a 6800 Series MPU :<br>This is the read/write control signal input terminal.<br>. When R/W="H":Read. When R/W="L":Write.     C86   1   This is the paralle data input serial data input switch terminal.<br>. C86="H":6800 Series MPU interface C86="L":8080 MPU interface.     P/S   1   This is the parallel data input. P/S="L":Serial data input.<br>. The following applies depending on the P/S status:<br>                                                                                                                                                                                                                                                                                                                                                                                 |                 |                     |                                                          |                 |               | AO                       | h - + D0 + - D7                       | 41                      |  |  |

| The reset operation is performed by the /RES signal level.     /CS1,CS2   I   This is the chip select signal. When /CS1="L"and CS2="H", then the chip select becomes active, and data/command I/O is enable.     /RD,(E)   I   When connected to an 8080 MPU, this is active LOW.     This pin is connected to the /RD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L".   When connected to a 6800 Series MPU enable clock input termined.     (WR,(R/W)   I   When connected to a 8080 MPU, this is active LOW.   This is the 6800 Series MPU enable clock input termined.     (WR,(R/W)   I   When connected to a 8080 MPU is active LOW.   This terminal connects to the 8080 MPU is active LOW.     (WR,(R/W)   I   When connected to a 6800 Series MPU : This is active LOW.   This is the read/write control signal.     (WR,(R/W)   I   When connected to a 6800 Series MPU : This is the read/write control signal input terminal.   When connected to a 6800 Series MPU : This is the pradimeter set is the maint.     (WR, (R/W)   I   This is the praville data input terminal.   When R/W="1"; Write.     (WR, (R/W)   I   This is the praville data input serial data input serial data input.   The following applies depending on the P/S status:     (P/S)   I   This is the paralle data input.   P/S   Data   Read/Write                                                                                                                                                                                                                                                                                                                                                                                         | DES             | т                   |                                                          |                 |               |                          | that D0 to D7 are con                 |                         |  |  |

| /CS1,CS2   I   This is the chip select signal. When /CS1 ="L"and CS2="H", then the chip select becomes active, and data/command I/O is enable.     /RD,(E)   I   . When connected to an 8080 MPU, this is active LOW. This pin is connected to the /RD signal of the 8080 MPU, and the SED 1565 series data bus is in an output status when this signal is "L"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | /KES            | 1                   |                                                          | -               |               |                          |                                       |                         |  |  |

| data/command I/O is enable.     /RD,(E)   I   . When connected to a 8080 MPU, this is active LOW.<br>This pin is connected to the /RD signal of the 8080 MPU, and the SED 1565 series data bus is in<br>an output status when this signal is "L".<br>. When connected to a 6800 Series MPU this is active HIGH .<br>This is the 6800 Series MPU enable clock input termined.     (WR,(R/W)   I   . When connected to a 8080 MPU /WR signal. The signals on the data bus are latched at<br>the rising edge of the /WR signal.<br>. When connected to a 6800 Series MPU :<br>This terminal connects to the 8080 MPU /WR signal . The signals on the data bus are latched at<br>the rising edge of the /WR signal.<br>. When connected to a 6800 Series MPU :<br>This is the read/write control signal input terminal.<br>. When R/W="H":Read. When R/W="L": Write.     C86   I   This is the maPUinterface switch terminal.<br>C86="H":6800 Series MPU interface. C86="L":8080 MPU interface     P/S   I   This is the paralle data input/serial data input.<br>P/S="H":Parallel data input. P/S="L":Serial data input.<br>The following applies depending on the P/S status:<br>P/S   Data   Read/Write   Serial Clock<br>"H"     P/S   Data/Command   Data   Read/Write   Serial Clock<br>"H"   A0   SI(D7)   Write only   SCL(D6)     When P/S="L",D0 to D5 are HZ. D0 to D5 may be "H","L" or Open ./RD(E)and /WR(R/W)are fixed to either<br>"H" or "L". With serial data input, RAM display data reading is not supported.   REV : 1                                                                                                                                                                                                                                                    | /CS1 CS2        | I                   |                                                          |                 |               |                          | he chin select becom                  | es active and           |  |  |