# **Seat Positioning Surround Decoder**

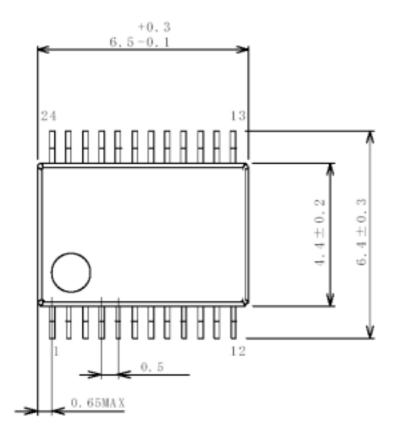

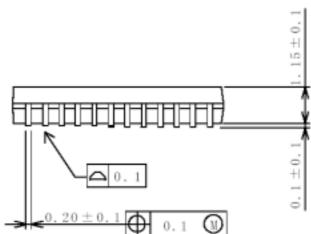

■Package

### General Description

The NJU26125 is a high performance 24-bit digital signal processor.

The NJU26125 provides NJRC Original Car Surround technology.

These kinds of sound functions are suitable for Car Audio that has four channel output speakers.

■ FEATURES NJU26125VC2

#### - Software

Seat Positioning Surround

Car Surround

Elevation

Bass Enhance

- Input Trimmer

- 7 Band PEQ: PEQ, LPF, HPF, LSF, HSF

- Filter: HPF(SDO0/SDO1), LPF(SDO2)

- Simulated Stereo

- Master Volume & Channel Trimmer

- Navigation Voice Mix Trimmer

#### - Hardware

24bit Fixed-point Digital Signal Processing

• Maximum System Clock Frequency: 12.288MHz Max. built-in PLL Circuit

• Digital Audio Interface : 3 Input ports / 3 Output ports

• Digital Audio Format : I<sup>2</sup>S 24bit, Left- justified, Right-justified, BCK : 32/64fs

• Master / Slave Mode

- Master Mode, MCK : 384fs @32kHz, 256fs @48kHz

• Host Interface : I<sup>2</sup>C bus (Fast-mode/400kbps)

• Power Supply : 3.3V

Input terminal : 5V Input tolerantPackage : SSOP24-C2 (Pb-Free)

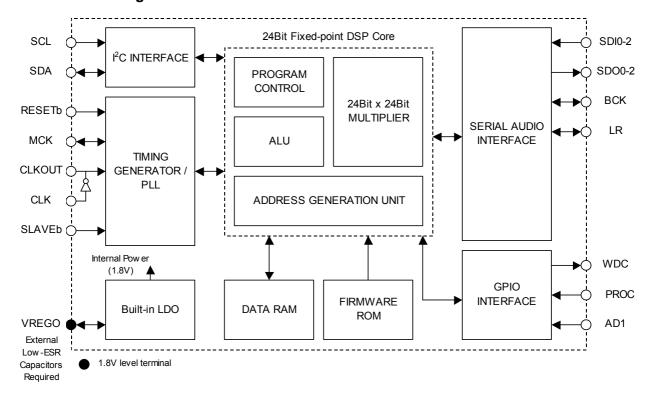

### Function Block Diagram

Fig. 1 NJU26125 Block Diagram

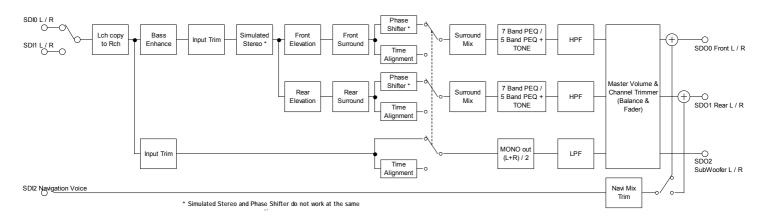

### **■ DSP Block Diagram**

Fig. 2 NJU26125 Function Diagram

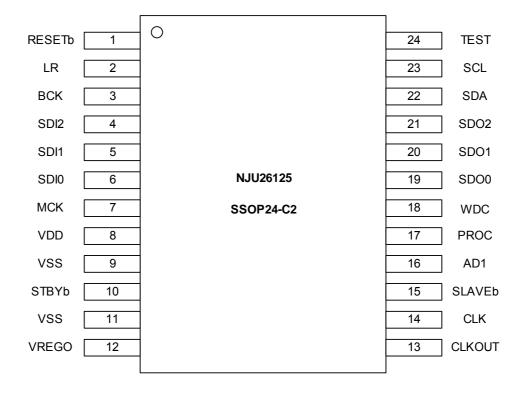

### Pin Configuration

Fig. 3 NJU26125 Pin Configuration

### Pin Description

**Table 1** Pin Description

| No. | Symbol | I/O | Description                   |  |

|-----|--------|-----|-------------------------------|--|

| 1   | RESETb | ı   | RESET (active Low)            |  |

| 2   | LR     | 1/0 | LR Clock                      |  |

| 3   | BCK    | 9   | Bit Clock                     |  |

| 4   | SDI2   |     | Audio Data Input 2 Navi Voice |  |

| 5   | SDI1   |     | Audio Data Input 1 L/R        |  |

| 6   | SDI0   |     | Audio Data Input 0 L/R        |  |

| 7   | MCK    | 9   | Master Clock                  |  |

| 8   | VDD    | -   | Power Supply +3.3V            |  |

| 9   | VSS    | -   | GND                           |  |

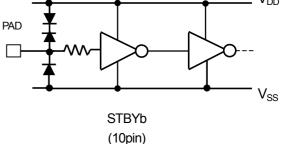

| 10  | STBYb  |     | For TEST (Connected to VDD)   |  |

| 11  | VSS    | -   | GND                           |  |

| 12  | VREGO  | PI  | Built-in Power Supply Bypass  |  |

| No. | Symbol | I/O | Description                   |

|-----|--------|-----|-------------------------------|

| 13  | CLKOUT | 0   | OSC Output                    |

| 14  | CLK    |     | OSC Clock Input               |

| 15  | SLAVEb | 1   | Slave select                  |

| 16  | AD1    |     | I <sup>2</sup> C Address      |

| 17  | PROC   | I   | Status select after Reset DSP |

| 18  | WDC    | OD  | Clock for Watch Dog Timer     |

| 19  | SDO0   | 0   | Audio Data Output 0 Front L/R |

| 20  | SDO1   | 0   | Audio Data Output 1 Rear L/R  |

| 21  | SDO2   | 0   | Audio Data Output 2 Subwoofer |

| 22  | SDA    | OD  | I <sup>2</sup> C I/O          |

| 23  | SCL    |     | I <sup>2</sup> C Clock        |

| 24  | TEST   |     | For TEST(Connected to VSS)    |

I: Input, O: Output, I/O: Bi-directional, OD: Open-Drain I/O, PI: Power Supply Bypass

AD1 (No.16) pin and PROC (No.17) pin are input pins. WDC (No.18) pin is open-drain pin with pull-up resistance. However, these pins operate as bi-directional pins. No.16pin and No.17pin connect with  $V_{DD}$  or  $V_{SS}$  through  $3.3k\Omega$  resistance. No.18pin do not connect or connect with  $V_{DD}$  through  $3.3k\Omega$  resistance when unused.

VREGO (No.12) pin is a built-in power supply bypass pin. Connect low-ESR capacitor of 4.7uF and 0.01uF in parallel between VSS (No.11) pin. A built-in power supply is used only for NJU26125 operation. Be not short-circuited of this pin. Do not take out the current, and connect other power supplies.

Do not open the terminals without pull-up resistance and pull-down resistance.

### Absolute Maximum Ratings

**Table 2 Absolute Maximum Ratings**

$(V_{SS}=0V=GND, Ta=25^{\circ}C)$

| Parame                  | ter     | Symbol                     | Rating                                | Units |

|-------------------------|---------|----------------------------|---------------------------------------|-------|

| Supply Voltage *        |         | $V_{DD}$                   | -0.3 to 4.2                           | V     |

| Supply Voltage Bypass * |         | $V_{REGO}$                 | -0.3 to 2.3                           | V     |

|                         | ln      | $V_{x(IN)}$                | -0.3 to 5.5 (V <sub>DD</sub> ≥ 3.0V)  |       |

| Pin Voltage *           | I/O, OD | $V_{x(I/O)}$ , $V_{x(OD)}$ | $-0.3$ to $4.2$ ( $V_{DD}$ < $3.0$ V) |       |

|                         | Out     | $V_{x(OUT)}$               |                                       | V     |

|                         | CLK     | $V_{x(CLK)}$               | -0.3 to 4.2                           |       |

|                         | CLKOUT  | $V_{x(CLKOUT)}$            |                                       | _     |

| Power Dissipation       |         | $P_{D}$                    | 565                                   | mW    |

| Operating Voltage       |         | T <sub>OPR</sub>           | -40 to 85                             | °C    |

| Storage Temperat        | ure     | T <sub>STR</sub>           | -40 to 125                            | °C    |

<sup>\*</sup> The LSI must be used inside of the "Absolute maximum ratings". Otherwise, a stress may cause permanent damage to the LSI.

$^*V_{DD}$  : 8 pin  $^*V_{REGO}$  : 12 pin

\*  $V_{x(IN)}$  : 1, 4, 5, 6, 10, 15, 23, 24 pin

\*  $V_{x(OD)}$  : 22 pin

\*  $V_{x(I/O)}$  : 2, 3, 7, 16, 17, 18 pin

\*  $V_{x(OUT)}$  : 19, 20, 21 pin

\*  $V_{x(CLK)}$  : 14 pin \*  $V_{x(CLKOUT)}$  : 13 pin

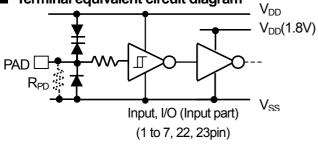

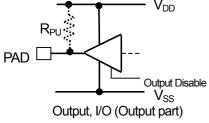

### Terminal equivalent circuit diagram

(with R<sub>PU</sub>: 18pin, With R<sub>PD</sub>: 15, 16, 17, 24pin)

(2, 3, 7, 16, 17, 19, 20, 21pin)

(Open Drain Output with R<sub>PU</sub>: 18pin) (Open Drain Output: 22pin) CLK/CLKOUT

(13, 14pin)

VDD

VDD(1.8V)

VSS

CLK/CLKOUT

(13, 14pin)

Fig.4 NJU26125 Terminal equivalent circuit diagram

#### Electric Characteristics

**Table 3 Electric Characteristics**

$(V_{DD}=3.3V, f_{OSC}=12.288MHz, Ta=25^{\circ}C)$

| Parameter                    | Symbol               | Test Condition                | Min.                  | Тур.   | Max.                  | Units |

|------------------------------|----------------------|-------------------------------|-----------------------|--------|-----------------------|-------|

| Operating Voltage *1         | V <sub>DD</sub>      | V <sub>DD</sub> pin           | 3.0                   | 3.3    | 3.6                   | V     |

| Operating Current            | I <sub>DD</sub>      | At no load                    | -                     | 20     | 35                    | mA    |

| High Level Input Voltage     | V <sub>IH</sub>      |                               | V <sub>DD</sub> x 0.7 | 1      | V <sub>DD</sub> *2    |       |

| Low Level Input Voltage      | V <sub>IL</sub>      |                               | 0                     | 1      | V <sub>DD</sub> x 0.3 | V     |

| High Level Output Voltage *3 | V <sub>OH</sub>      | (I <sub>OH</sub> = -1mA)      | V <sub>DD</sub> x 0.8 | 1      | $V_{DD}$              | μΑ    |

| Low Level Output Voltage     | V <sub>OL</sub>      | (I <sub>OL</sub> = 1mA)       | 0                     | 1      | V <sub>DD</sub> x 0.2 |       |

|                              | I <sub>IN</sub>      |                               | -10                   | 1      | 10                    |       |

| Leakage Current *4           | I <sub>IN(PU)</sub>  | $V_{IN} = V_{SS}$ to $V_{DD}$ | -120                  | 1      | 10                    |       |

|                              | I <sub>IN(PD)</sub>  |                               | -10                   | 1      | 120                   |       |

| Clock Frequency              | f <sub>OSC</sub>     |                               | 10                    | 12.288 | 13                    | MHz   |

| Clock Jitter *5              | f <sub>JIT(CC)</sub> | CLK, MCK *6                   | 0                     | -      | 3.0                   | ns    |

| Clock Duty Cycle             | r <sub>EC</sub>      |                               | 45                    | 50     | 55                    | %     |

<sup>\*1</sup> Please use the  $V_{DD}$  within the electric characteristics.  $V_{DD}$  is monotonous increase. Don't drop voltage under the electric characteristics after booting  $V_{DD}$  to regulation voltage. When it turns off DSP and turns on DSP again, it is necessary to drop  $V_{DD}$  to GND level. Then it turns on DSP again.

<sup>\*2</sup> Input pin, Output pin and Open-Drain input/output pin are +5.0V tolerant except CLK input pin.

<sup>\*3</sup> Except No.18pin: WDC (Open-Drain output) and No.22: SDA (Open-Drain input/output).

<sup>\*4</sup> I<sub>IN(PU)</sub>: 18pin, I<sub>IN(PD)</sub>: 15, 16, 17, 24 pin

<sup>\*5</sup> Clock Jitter shows Cycle-to-cycle period jitter (JEDEC JESD65).

<sup>\*6</sup> Provide clock frequency for fosc spec. NJU26125 needs clock frequency 12.288MHz when sampling rate is 48kHz.

### 1. Power Supply, Input/Output terminal, Clock, Reset

### 1.1 Power Supply

The NJU26125 has a power supply  $V_{DD}$ . To setup good power supply condition, the decoupling capacitors should be implemented at the all power supply terminals.

The NJU26125 include a built-in power supply (LDO) for internal logic. A built-in power supply generates 1.8V (-10% to +10%). VREGO (No.12) pin is a built-in power supply bypass pin. Connect low-ESR capacitor of 4.7uF and 0.01uF in parallel between VSS (No.11) pin.

A built-in power supply is used only for NJU26125 operation. Be not short-circuited of this pin. Do not take out the current, and connect other power supplies.

### 1.2 Input/Output terminal

It restricts, when the input terminals (AD1, PROC, RESETb, SDI0, SDI1, SDI2, STBYb, SLAVEb, SCL, TEST pins), the input/output terminals (LR, BCK, MCK pins) and the bi-directional Open-drain terminal (SDA pin) of NJU26125, and  $V_{DD}$  are supplied on regular voltage ( $V_{DD}$ =3.3V), and it becomes +5V Input tolerant.

### 1.3 Clock

The NJU26125 CLK pin requires the system clock that should be related to the sample frequency 256 Fs.

(For example: Fs=48kHz CLK=12.288MHz)

It is possible to be generated the system clock by connecting a crystal oscillator between CLK and CLKOUT. CLK/CLKOUT pins are not 5V tolerant, so check the voltage level of these pins.

When SLAVEb pin is fixed on Low level, NJU26125 supplies the system clock from MCK pin. Fix the clock input pin not used to Low level because either the CLK pin or the MCK pin is supplied in NJU26125.

The frequency divider for Master mode matched to the clock 256 times of Fs is installed in NJU26125. When clock except 256 times of Fs is used by Master mode, be careful to use because a dividing frequency of Master mode changes. Please check enough and decide parameter.

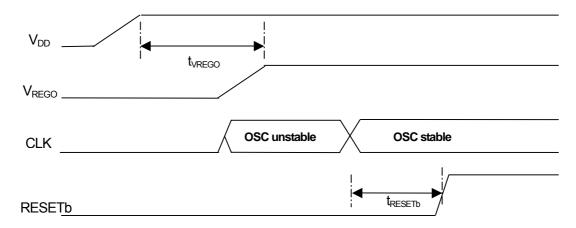

#### 1.4 Reset

To initialize the NJU26125, RESETb pin should be set Low level during some period. After some period of Low level, RESETb pin should be High level. This procedure starts the initialization of the NJU26125. After the power supply and the oscillation of the NJU26125 becomes stable, RESETb pin must be kept Low-level more than  $t_{RESETb}$  period. (Fig.5)

After RESETb pin level goes to "High" (after reset release), a setup of the internal hardware of a Serial Host Interface completes NJU26125 within 10msec. Then, it will be in the state which can communicate.

Fig.5 Reset Timing

Table 4 Reset Time

| Symbol              | Time      |

|---------------------|-----------|

| t <sub>VREGO</sub>  | ≥ 10msec  |

| t <sub>RESETb</sub> | ≥ 1.0msec |

#### Note:

Don't stop the supply of a clock while operating. NJU26125 installs PLL circuit internally. If the supply of a clock is stopped, PLL circuit cannot be sent a clock to the inside and NJU26125 does not operate normally.

If supply of a clock is stopped or the NJU26125 is reset again, putting a normal clock into CLK terminal, the period RESETb terminal of  $t_{\text{RESETb}}$  is kept "Low" level.(Table 4) Next, the NJU26125 is reset. Then redo from initial setting.

### 2. Digital Audio Clock

Digital audio data needs to synchronize and transmit between digital audio systems. The NJU26125 - master mode / slave mode - both of the modes are supported.

- In Master mode:

Use the clock of BCKO and a LRO pin output clock for digital audio data transfer.

- In Slave mode;

The clock output from a master device is needed for the input terminal of BCKI and LRI.

A device in the system generates the transmitted clock become a standard. The other devices are set according to the transmitted clock. The device generating transmitted clock is called Master Device. The device according to the transmitted clock is called Slave Device. NJU26125 usually operates Slave Device. However, NJU26125 becomes Master Device in case of SLAVEb set the High level and NJU26125 is set Master mode by firmware command. In Slave mode, clock inputted to the BCK pin and the LR pin is used to digital audio signal transmission. In Master mode, clock outputted to the BCK pin and the LR pin is used to digital audio signal transmission.

#### 2.1 Audio Clock

Three kinds of clocks are needed for digital audio data transfer.

- (1) LR clock (LR) is needed by serial-data transmission. It is the same as the sampling frequency of a digital audio signal.

- (2) Bit clock (BCK) is needed by serial-data transmission. It becomes the multiple of LR clock.

- (3) Master clock (MCK) is needed by A/D, D/A converter, etc. It becomes the multiple of LR clock. It is not related to serial audio data transmission.

In SLAVEb is High level, the MCK pin becomes buffer output pin for input clock to the CLK pin after NJU26125 resets. The MCK output is able to be stopped by firmware command.

In SLAVEb is Low level, MCK pin becomes system clock input pin. It is not insure to change the logical switch of SLAVEb pin during operating. If it is necessary to change SLAVEb pin setting, reset NJU26125 every time.

Table 5 SLAVEb, BCK, LR, MCK

| SLAVEb and firmware setting    | LR pin                                  | BCK pin                                     | MCK pin                                        |

|--------------------------------|-----------------------------------------|---------------------------------------------|------------------------------------------------|

| SLAVEb="Low"<br>Firmware: each | LR clock input                          | Bit clock input                             | NJU26125 operating clock input<br>(MCK or CLK) |

| SLAVEb="H"<br>Firmware: Slave  | DSP slave operating                     | DSP slave operating                         | Master clock output                            |

| SLAVEb="H"<br>Firmware: Master | LR clock output<br>DSP Master operating | Bit clock output<br>DSP Master<br>operating | (Buffer of CLK)                                |

In NJU26125 is used by 256 times of Maximum sampling frequency, NJU26125 is able to output LR clock of same sampling rate and two-third times of sampling rate, and output BCK clock of 32 times sampling rate and 64 times sampling rate in Master mode.

# Table 6 Input clock (In Slave mode)

| Mode  | Clock Signal        | Multiple Frequency                               | 32kHz     | 44.1kHz   | 48kHz    |  |

|-------|---------------------|--------------------------------------------------|-----------|-----------|----------|--|

|       | LR                  | 1fs                                              | 32kHz     | 44.1kHz   | 48kHz    |  |

|       | BCK (32fs)          | 32fs                                             | 1.024MHz  | 1.4112MHz | 1.536MHz |  |

| DSP   | BCK (64fs)          | 64fs                                             | 2.048MHz  | 2.822MHz  | 3.072MHz |  |

| Slave | MCK<br>(SLAVEb="L") | Input terminal: Clock is generated by MCK or CLK |           |           |          |  |

|       | MCK<br>(SLAVEb="H") | Buffer output of CLK                             | 12.288MHz |           |          |  |

# Table 7 Output clock (In Master mode)

| Mode Clock Signal |              | Multiple Frequency     | CLK pin frequency |           |          |  |

|-------------------|--------------|------------------------|-------------------|-----------|----------|--|

| IVIOGE            | Clock Signal | ividitiple i requericy | 32kHz             | 44.1kHz   | 48kHz    |  |

|                   | LR           | 1fs                    | 32kHz             | -         | 48kHz    |  |

| DSP               | BCK (32fs)   | 32fs                   | 1.024MHz          | -         | 1.536MHz |  |

| Master            | BCK (64fs)   | 64fs                   | 2.048MHz          | -         | 3.072MHz |  |

|                   | MCK          | Buffer output of CLK   |                   | 12.288MHz |          |  |

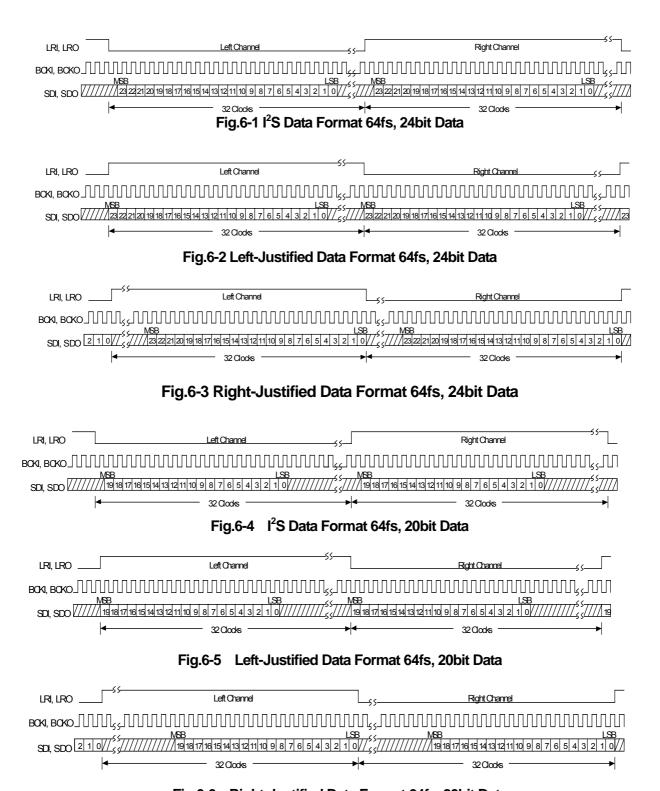

### 3. Digital Audio Interface

### 3.1 Digital Audio Data Format

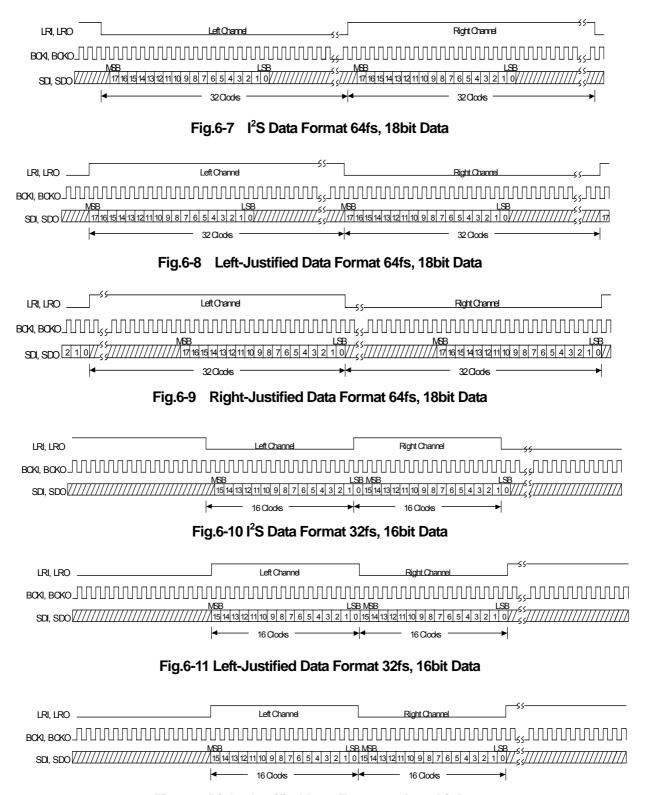

The NJU26125 can use three kinds of formats hereafter as industry-standard digital audio data format.

(1) I<sup>2</sup>S : MSB is put on the 2nd bit of LR clock change rate.(1 bit is delayed to left stuffing)

(2) Left-justified : LR clock -- MSB is placed for changing.

(3) Right-justified: LSB is placed just before LR clock change rate.

The main differences among three kinds of formats are in the position relation between LR clock (LR) and an audio data (SDI, SDO).

In every format: : a left channel is transmitted previously.

In Right/Left-justified : LR clock ='High' shows a left channel.

I'S : LR clock="Low" shows a left channel.

- The Bit clock BCK is used as a shift clock of transmission data. The number of clocks more than the number of sum total transmission bits of a L/R channel is needed at least.

- One cycle of LR clock is one sample of a stereo audio data. The frequency of LR clock becomes equal to a sample rate (Fs).

- The NJU26125 supports serial data format which includes 32(32fs) or 64(64fs) BCK clocks. This serial data format is applied to both MASTER and SLAVE mode.

### 3.2 Serial Audio Data Input/output

The NJU26125 audio interface includes 3 data input lines: SDI0, SDI1 and SDI2 (Table 8). 3 data output lines: SDO0, SDO1 and SDO2. (Table 9).

Table 8 Serial Audio Input Pin Description

| Pin No. | Symbol | Description        |                  |

|---------|--------|--------------------|------------------|

| 6       | SDI0   | Audio Data Input 0 | L/R              |

| 5       | SDI1   | Audio Data Input 1 | L/R              |

| 4       | SDI2   | Audio Data Input 2 | Navigation Voice |

Table 9

Serial Audio Output Pin Description

| Pin No. | Symbol | Description         |               |

|---------|--------|---------------------|---------------|

| 19      | SDO0   | Audio Data Output 0 | Front L/R     |

| 20      | SDO1   | Audio Data Output 1 | Rear L/R      |

| 21      | SDO2   | Audio Data Output 2 | Subwoofer L/R |

Please refer "Fig.2 NJU26125 Function Diagram".

The NJU26125 can use three kinds of formats hereafter as industry-standard digital audio data format; (1)  $I^2S$  (2) Left-Justified (3) Right-justified and 16 / 18 / 20 / 24bits data length. (Fig.6-1 to Fig6-12) An audio interface input and output data format become the same data format.

Fig.6-6 Right-Justified Data Format 64fs, 20bit Data

Fig.6-12 Right-Justified Data Format 32fs, 16bit Data

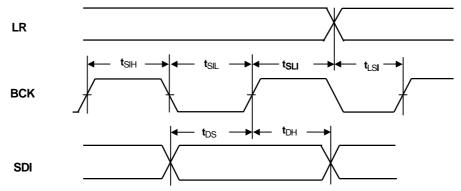

# 3.3 Serial Audio Input Timing

**Table 10 Serial Audio Input Timing Parameters**

| () | V <sub>DD</sub> = | 3.3 | V. | Ta=  | :25° | C) |

|----|-------------------|-----|----|------|------|----|

| •  | • DD—             | 0.0 | -, | . ~- |      | •, |

| Parameter                                     | Symbol                               | Test Condition | Min      | Тур. | Max | Units |

|-----------------------------------------------|--------------------------------------|----------------|----------|------|-----|-------|

| BCK Frequency *                               | f <sub>BCKI</sub>                    |                | -        | -    | 6.5 | MHz   |

| BCK Period * Low Pulse Width High Pulse Width | t <sub>sil</sub><br>t <sub>sih</sub> |                | 75<br>75 | -    | -   | ns    |

| BCK to LR Time **                             | t <sub>SLI</sub>                     |                | 40       | -    | -   | ns    |

| LR to BCK Time **                             | t <sub>LSI</sub>                     |                | 40       | -    | -   | ns    |

| Data Setup Time                               | t <sub>DS</sub>                      |                | 15       | -    | -   | ns    |

| Data Hold Time                                | t <sub>DH</sub>                      |                | 15       | -    | -   | ns    |

<sup>\*</sup> It is the regulation of absolute maximum ratings. Maximum frequency of BCK is limited.

<sup>\*\*</sup> It is the regulation in slave mode.

Fig.7 Serial Audio Input Timing

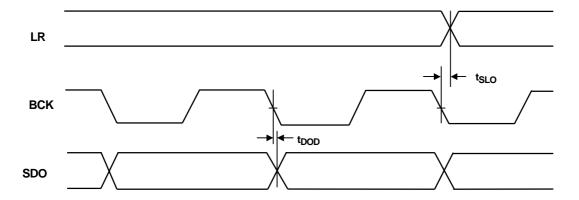

Serial Audio Output Timing Parameters

| Table 11 Serial Audio Output Timing Parameters |                  |                      |     |      | ( V <sub>DD</sub> =3.3V, Ta=25°C ) |       |  |

|------------------------------------------------|------------------|----------------------|-----|------|------------------------------------|-------|--|

| Parameter                                      | Symbol           | Test Condition       | Min | Тур. | Max                                | Units |  |

| BCK to LR Time * t <sub>SLO</sub>              |                  | C <sub>I</sub> =25pF | -15 | -    | 15                                 | ns    |  |

| Data Output Delay                              | t <sub>DOD</sub> | C <sub>L</sub> -25pr | -   | -    | 15                                 | ns    |  |

<sup>\*</sup> It is the regulation in Master mode.

Fig.8 Serial Audio Input Timing

#### Host Interface

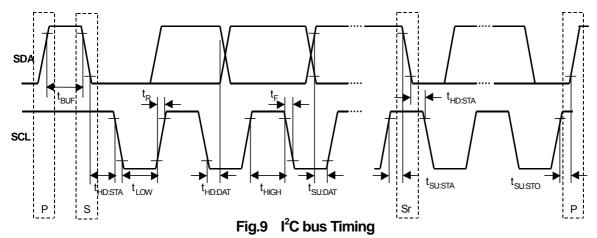

The NJU26125 can be controlled via Serial Host Interface (SHI) using I<sup>2</sup>C bus. Data transfers are in 8 bit packets (1 byte) when using either format. Refer to serial Host Interface Pin Description.(Table 12)

Table 12 Serial Host Interface Pin Description

| Pin No. | Symbol<br>(I <sup>2</sup> C bus) | I <sup>2</sup> C bus Format                           |

|---------|----------------------------------|-------------------------------------------------------|

| 16      | AD1                              | I <sup>2</sup> C bus address Bit                      |

| 22      | SDA                              | Serial Data Input/Output<br>(Open Drain Input/Output) |

| 23      | SCL                              | Serial Clock                                          |

Note: SDA pin (No.22) is a bi-directional open drain terminal. This pin requires a pull-up resister.

AD1 (No.16) pin is input pin with pull-down. AD1 (No.16) pin is connected with  $V_{DD}$  or  $V_{SS}$  through  $3.3k\Omega$  resistance.

When NJU26125 is stopped by power supply VDD, SDA pin and SCL pin become Hi-Z. But these pins are not 5V tolerant when VDD stops.

## ■ I<sup>2</sup>C bus

I<sup>2</sup>C bus interface transfers data to the SDA pin and clocks data to the SCL pin. SDA pin is a bi-directional open drain and requires a pull-up resister.

AD1 pin is used to configure the seven-bit SLAVE address of the serial host interface. (Table 13) This offers additional flexibility to a system design by two different SLAVE addresses of the NJU26125. An address can be arbitrarily set up by the AD1 pin. The I<sup>2</sup>C address of AD1 is decided by connection of AD1 pin.

Table 13 I<sup>2</sup>C bus SLAVE Address

| bit7 |              | bit6 | bit5 | 5       | bit4   | bit    | 3 | bit2 | AD<br>bit  |     | R/W<br>bit0 |

|------|--------------|------|------|---------|--------|--------|---|------|------------|-----|-------------|

| 0    |              | 0    | 1    |         | 1      | •      | 1 | 0    | 0          |     | RW          |

| 0    |              | 0    | 1    |         | 1      |        | 1 | 0    | 1          |     | 1000        |

|      |              |      |      | 1       |        |        | / |      |            |     |             |

|      | Start<br>bit |      |      | Slave A | ddress | 7bit ) |   |      | R/W<br>bit | ACK |             |

<sup>\*</sup> SLAVE address is 0 when AD1 is "Low". SLAVE address is 1 when AD1 is "High".

<sup>\*</sup> SLAVE address is 0 when RW is "W". SLAVE address is 1 when RW is "R".

| Table 14 | I <sup>2</sup> C bus Interface Timing Parar | neters | ( V <sub>DD</sub> =3.3 | 3V, f <sub>OSC</sub> =12.28 | 88MHz, Ta=25°C ) |

|----------|---------------------------------------------|--------|------------------------|-----------------------------|------------------|

|          |                                             |        |                        | l                           |                  |

| Parameter                  | Symbol              | Min | Max  | Units |

|----------------------------|---------------------|-----|------|-------|

| SCL Clock Frequency        | f <sub>SCL</sub>    | 0   | 400  | kHz   |

| Start Condition Hold Time  | t <sub>HD:STA</sub> | 0.6 | -    | μs    |

| SCL "Low" Duration         | t <sub>LOW</sub>    | 1.3 | -    | μs    |

| SCL "High" Duration        | t <sub>HIGH</sub>   | 0.6 | -    | μs    |

| Start Condition Setup Time | t <sub>SU:STA</sub> | 0.6 | -    | μs    |

| Data Hole Time *1          | t <sub>HD:DAT</sub> | 0   | 0.9  | μs    |

| Data Setup Time            | t <sub>SU:DAT</sub> | 250 | -    | ns    |

| Rising Time                | t <sub>R</sub>      | -   | 1000 | ns    |

| Falling Time               | t <sub>F</sub>      | -   | 300  | ns    |

| Stop Condition Setup Time  | t <sub>su:sto</sub> | 0.6 | -    | μs    |

| Bus Release Time *2        | t <sub>BUF</sub>    | 1.3 | _    | μS    |

### Note:

- \*1  $t_{HD:DAT}$ : Keep data 100ns hold time to avoid indefinite state by SCL falling edge.

- \*2 This item shows the interface specification. The interval of a continuous command is specified separately.

### Pin setting

The NJU26125 operates default command setting after resetting the NJU26125. In addition, the NJU26125 restricts operation at power on by setting PROC pin (No.17) (Table 15). This pin is input pin. However, this pin operates as bi-directional pin. Connect with  $V_{DD}$  or  $V_{SS}$  through  $3.3k\Omega$  resistance.

Table 15 Pin setting

| Pin No. | Symbol | Setting | Function                                                                                             |

|---------|--------|---------|------------------------------------------------------------------------------------------------------|

| 17      | PROC   | "High"  | The NJU26125 does not operate after reset. Sending start command is required for starting operation. |

| 17      | PROC   | "Low"   | The NJU26125 operates default setting after reset. The default value of Master Volume is Mute.       |

### ■ WatchDog Clock

The NJU26125 outputs clock pulse through WDC (No.18) pin during normal operation.

The NJU26125 generates a clock pulse through the WDC terminal after resetting the NJU26125. The WDC clock is useful to check the status of the NJU26125 operation. For example, a microcomputer monitors the WDC clock and checks the status of the NJU26125. When the WDC clock pulse is lost or not normal clock cycle, the NJU26125 does not operate correctly. Then reset the NJU26125 and set up the NJU26125 again. Watchdog clock output cycle is about 100msec.

**Note:** If input and output of an audio signal stop and an audio interface stops, WDC can't output. That is because it has controlled based on the signal of an audio interface.

### ■ NJU26125 Command Table

# Table 16 NJU26125 Command

|     | 10 NOOZO125 COMMINANG |

|-----|-----------------------|

| No. | Command               |

| 1   | Set Task              |

| 2   | System State          |

| 3   | Sample Rate Select    |

| 4   | Smooth Control Config |

| 5   | Master Volume Control |

| 6   | Channel Trim Control  |

| 7   | Input Trim            |

| 8   | Surround Gain         |

| 9   | Surround Channel Gain |

| 10  | Surround Mix Ratio    |

| 11  | Phase Shifter Fc      |

| 12  | Phase Shifter Mode    |

| 13  | Time Alignment        |

| 14  | Filter Fc             |

| 15  | Filter Switch         |

| No. | Command                          |

|-----|----------------------------------|

| 16  | Elevation Gain                   |

| 17  | Bass Enhance LPF Fc              |

| 18  | Bass Enhance Gain                |

| 19  | Bass Enhance Release Time Select |

| 20  | PEQ F0                           |

| 21  | PEQ Q                            |

| 22  | PEQ Gain                         |

| 23  | PEQ Mode Config                  |

| 24  | PEQ Smooth Config                |

| 25  | Navigation Voice Mix Trim        |

| 26  | Firmware Revision Number Request |

| 27  | DSP Reset Command                |

| 28  | Boot with Mute                   |

| 29  | Boot with Unmute                 |

| 30  | No Operation (Nop)               |

### Package

SSOP24-C2, Pb-Free

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.