# **CY3663 Hardware User's Manual**

Version 1.5

Cypress Semiconductor 3901 North First Street San Jose, CA 95134 Tel.: (800) 858-1810 (toll-free in the U.S.)

(408) 943-2600 www.cypress.com

# Warranty Disclaimer and Limited Liability

Cypress Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Cypress's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Cypress are granted by

the Company in connection with the sale of Cypress products, expressly or by implication. Cypress's products are not authorized for use as critical components in life support devices or systems.

CY16 is a trademark of the Cypress Corporation. All other product names are trademarks are registered trademarks of their respective owners.

CY3663 Hardware User's Manual, Version 1.5.

Copyright © 2003 Cypress Semiconductor Corporation.

All rights reserved.

# Table of Contents

| Chapter 1. Introduction                          |                 |

|--------------------------------------------------|-----------------|

| 1.1 Introduction                                 | 1-1             |

| Chantar 2 Currence Strong A DM Single Board Comp |                 |

| Chapter 2. Cypress StrongARM Single Board Comp   |                 |

| 2.1 Introduction                                 |                 |

| 2.2 System Block Diagram                         | 2-2             |

| 2.3 Processor and Memory                         | 2-:             |

| 2.4 Serial Ports                                 | 2-:             |

| 2.4.1 Serial Port #1                             | 2-:             |

| 2.4.2 Serial Port #2                             | 2               |

| 2.4.3 Serial Port #3                             | 2               |

| 2.4.4 Serial Port #4                             | 2-4             |

| 2.5 Expansion Port                               | 2-4             |

| 2.6 CPLD                                         | 2-0             |

| 2.7 User Interface                               | 2- <sup>-</sup> |

| 2.7.1 LCD                                        | 2- <sup>-</sup> |

| 2.7.2 LEDs                                       | 2-              |

| 2.7.2.1 Power LEDs                               | 2- <sup>-</sup> |

| 2.7.2.2 General Purpose LEDs                     | 2-8             |

| 2.7.2.3 Network LEDs                             | 2-8             |

| 2.7.2.4 Other LEDs                               | 2-              |

| 2.7.3 DIP Switches                               | 2-8             |

| 2.7.4 Pushbuttons                                | 2-8             |

| 2.8 Ethernet                                     | 2-8             |

| 2.9 Power                                        | 2-8             |

| 2.10 Miscellaneous Jumpers                       | 2-9             |

| Chapter 3. Cypress EZ-Host Development Board     |                 |

| 3.1 Introduction                                 | 3-              |

| 3.2 System Block Diagram                         |                 |

| 3.3 Processor and Memory                         |                 |

| 3.4 Asynchronous Sorial Ports                    |                 |

# (Table of Contents)

|    | 3.4.1 UART                                | . 3-4            |

|----|-------------------------------------------|------------------|

|    | 3.4.2 High Speed Serial (HSS)             | . 3-4            |

|    | 3.5 SPI                                   | . 3-4            |

|    | 3.6 Co-processor Connection               | . 3-5            |

|    | 3.7 CPLD                                  | . 3-5            |

|    | 3.8 User Interface                        | . 3-5            |

|    | 3.8.1 Seven Segment Display               | . 3-6            |

|    | 3.8.2 DIP Switches                        | . 3-6            |

|    | 3.8.3 LEDs                                | . 3-6            |

|    | 3.8.3.1 Power LEDs                        | . 3-6            |

|    | 3.8.3.2 General Purpose LEDs              | . 3-6            |

|    | 3.8.3.3 IDE LED                           | . 3-7            |

|    | 3.8.4 Pushbuttons                         | . 3-7            |

|    | 3.9 Power                                 | . 3-7            |

|    | 3.10 USB Ports                            | . 3-7            |

|    | 3.11 Miscellaneous                        | . 3-8            |

|    |                                           |                  |

| Ch | apter 4. Cypress EZ-OTG Development Board |                  |

|    | 4.1 Introduction                          | 4-1              |

|    | 4.2 System Block Diagram                  |                  |

|    | 4.3 Processor and Memory                  |                  |

|    | 4.4 Asynchronous Serial Ports             |                  |

|    | 4.4.1 UART                                |                  |

|    | 4.4.2 High Speed Serial (HSS)             |                  |

|    | 4.5 SPI                                   |                  |

|    | 4.6 Co-processor Connection               |                  |

|    | 4.7 CPLD                                  |                  |

|    | 4.8 User Interface                        |                  |

|    | 4.8.1 Seven Segment Display               |                  |

|    | 4.8.2 DIP Switches                        |                  |

|    | 4.8.3 LEDs                                |                  |

|    | 4.8.3.1 Power LEDs                        |                  |

|    | 4.8.3.2 General Purpose LEDs              |                  |

|    | 4.8.4 Pushbuttons                         |                  |

|    | 4.9 Power                                 |                  |

|    | 4.10 USB Ports                            |                  |

|    | 4.11 Miscellaneous.                       |                  |

|    |                                           | . <del></del> () |

ii Table of Contents

# (Table of Contents)

# Chapter 5. Developing with the EZ-Host and EZ-OTG Boards

| 5.1 | Standalone Mode Operation                               | 5-1  |

|-----|---------------------------------------------------------|------|

|     | 5.1.1 Power-up EEPROM Selection                         | 5-1  |

|     | 5.1.2 DIP Switches                                      | 5-1  |

|     | 5.1.3 Pushbutton Inputs                                 | 5-1  |

|     | 5.1.4 LEDs: OTG ERROR, SESSION ACTIVE, HOST, PERIPHERAL | 5-1  |

|     | 5.1.5 LEDs: RUN/STOP                                    | 5-1  |

|     | 5.1.6 Seven Segment Display                             | 5-2  |

|     | 5.1.7 Debugging Through the UART                        | 5-2  |

|     | 5.1.8 CPLD Accesses                                     | 5-2  |

| 5.2 | Co-processor Mode Operation                             | 5-3  |

|     | 5.2.1 Power-up Port Selection                           | 5-3  |

|     | 5.2.2 DIP Switches                                      | 5-3  |

|     | 5.2.3 Push Button Inputs                                | 5-4  |

|     | 5.2.4 LEDs                                              | 5-4  |

|     | 5.2.5 Seven Segment Display                             | 5-4  |

|     | 5.2.6 CPLD Accesses                                     | 5-4  |

|     | 5.2.7 Debugging Through the UART                        | 5-4  |

| 5.3 | Addressing of EZ-Host/OTG CPLD                          | 5-4  |

|     | 5.3.1 ADD_Reg                                           | 5-5  |

|     | 5.3.2 Data_Reg                                          | 5-5  |

| 5.4 | Memory Map for Indirect CPLD Registers                  | 5-6  |

| 5.5 | EZ-Host/OTG CPLD Indirect Register Descriptions         | 5-6  |

|     | 5.5.1 PB_Read                                           | 5-6  |

|     | 5.5.2 PB_UP_Clr                                         | 5-7  |

|     | 5.5.3 PB_LEFT_Clr                                       | 5-7  |

|     | 5.5.4 PB_RIGHT_Clr                                      | 5-7  |

|     | 5.5.5 PB_DOWN_Clr                                       | 5-7  |

|     | 5.5.6 PB_ENTER_Clr                                      | 5-8  |

|     | 5.5.7 DIP_Read                                          | 5-8  |

|     | 5.5.8 LED_Write                                         | 5-8  |

|     | 5.5.9 SSD_Write                                         | 5-9  |

|     | 5.5.10 VBUS_Level                                       | 5-9  |

|     | 5.5.11 VBUS_On_GPIO_30                                  |      |

|     | 5.5.12 Add_Reg_Read                                     |      |

|     | 5.5.13 EEPROM_MFG_CTL                                   |      |

| 5.6 | F7-Host/OTG Board Pushbutton and DIP Switch Definitions | 5-11 |

# (Table of Contents)

|    | 5.6.1 DIP Switch Settings                                       | 5-11         |

|----|-----------------------------------------------------------------|--------------|

|    | 5.6.2 Pushbuttons                                               | 5-14         |

|    | 5.6.3 LEDs                                                      | 5-14         |

|    | 5.6.4 Hex Display                                               | 5-15         |

|    | 5.7 Co-processor Mode Hints                                     | 5-15         |

|    | 5.8 Recommended GPIO Settings for the EZ-Host/OTG Boards        | 5-16         |

|    | 5.9 Restoring the EZ-Host and EZ-OTG Boards to Factory Defaults | 5-17         |

| Ch | napter 6. Developing with the Cypress StrongArm SBC             |              |

|    | 6.1 Normal Operation of the Cypress StrongARM SBC               | 6-1          |

|    | 6.1.1 Running Design Examples                                   | 6-1          |

|    | 6.1.2 Operation as a Linux USB Muti-port Host                   | 6-1          |

|    | 6.2 Linux Development with the Cypress StrongARM SBC            |              |

|    | 6.2.1 Boot Sequence                                             |              |

|    | 6.2.2 Using Ethernet Downloads During Development               | 6-3          |

|    | 6.2.2.1 Updating FLASH contents over Ethernet                   | 6-4          |

|    | 6.2.3 Using Serial Downloads During Development                 | 6-4          |

|    | 6.2.3.1 Updating FLASH contents over Serial                     | 6-5          |

|    | 6.3 Restoring the SBC to Factory Defaults                       | 6-6          |

|    | 6.4 Cypress StrongARM SBC Memory Map                            | 6-7          |

|    | 6.5 SBC CPLD Register Descriptions                              | 6-10         |

|    | 6.5.1 NETWORK_DECODE                                            |              |

|    | 6.5.2 DIP_PB_CTL                                                | 6-10         |

|    | 6.5.3 LED_CTL                                                   | 6-11         |

|    | 6.5.4 LCD_CTL                                                   | 6-11         |

|    | 6.5.5 LCD_STATUS_0                                              | 6-12         |

|    | 6.5.6 LCD_STATUS_1                                              | 6-12         |

|    | 6.5.7 LCD_STATUS_3                                              | 6-13         |

|    | 6.5.8 CPLD_VERSION                                              | 6-13         |

|    | 6.5.9 SBC_EXP_RST                                               | 6-14         |

|    | 6.5.10 MEZ_CARD_PRESENT                                         |              |

|    | 6.5.11 MEZ_CARD_DIP                                             | 6-15         |

| Αp | ppendix A                                                       |              |

| •  | - Definitions                                                   | Annendiy - 1 |

|    |                                                                 |              |

iv Table of Contents

# List of Figures

| Figure 2-1. | Cypress StrongARM Single Board Computer           | 2-1 |

|-------------|---------------------------------------------------|-----|

| Figure 2-2. | Cypress StrongARM SBC - Block Diagram             | 2-2 |

| Figure 2-3. | Serial Port Location                              | 2-3 |

| Figure 2-4. | SBC Expansion Port Location                       | 2-5 |

| Figure 2-5. | CPLD                                              | 2-6 |

| Figure 2-6. | User Interface                                    | 2-7 |

| Figure 3-1. | Cypress EZ-Host Development Board                 | 3-1 |

| Figure 3-2. | Cypress EZ-Host Development Board - Block Diagram | 3-3 |

| Figure 3-3. | EZ-Host User Interface                            | 3-5 |

| Figure 4-1. | Cypress EZ-OTG Development Board - Block Diagram  | 4-2 |

| Figure 5-1. | Timing Waveforms                                  | 5-3 |

vi List of Figures

# **Chapter 1. Introduction**

#### 1.1 Introduction

This manual describes the hardware in the Cypress CY3663 Development Kit (DVK). The three individual boards included in the kit are the Cypress StrongARM Single Board Computer (SBC), the EZ-Host DVK board, and the EZ-OTG DVK board. The next three chapters provide a description of the hardware circuitry on each of the boards, and the last two chapters give the developer details on using the boards.

Please refer as needed to the Appendix for a definition of abbreviations and terms used throughout the manual.

Additional hardware documentation that should be used in conjunction with this document can be found in the "Hardware" subdirectory that was installed from the kit CD. This directory contains schematics, layout files, Bill-of-Materials, and CPLD source for all three boards in this kit.

Chapter 1. Introduction Page 1-1

# **Chapter 2. Cypress StrongARM Single Board Computer**

#### 2.1 Introduction

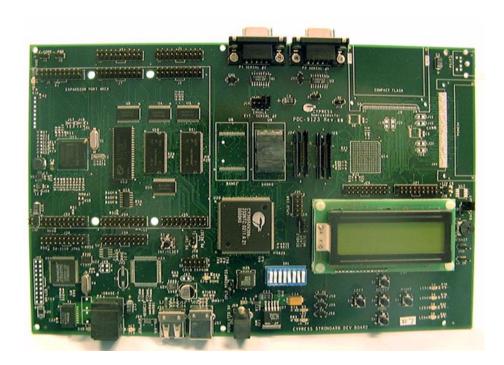

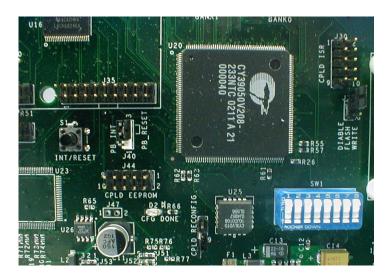

Figure 2-1. Cypress StrongARM Single Board Computer

The Cypress StrongARM Single Board Computer (SBC) is a versatile development platform that currently supports the Linux operation system. Other features include:

- 133 MHz Intel StrongARM SA-1110 microprocessor

- 32 Mbytes SDRAM, 16 Mbytes FLASH, 512 Kbytes SRAM

- User interface including two-line LCD, LEDs, and pushbuttons

#### CY3663 Hardware User's Guide

- High density, flexible in-circuit programmable CPLD

- Ethernet port

- Multiple synchronous and asynchronous serial ports

- High signal visibility with quick connect logic analyzer support

- · Robust buffered expansion port

# 2.2 System Block Diagram

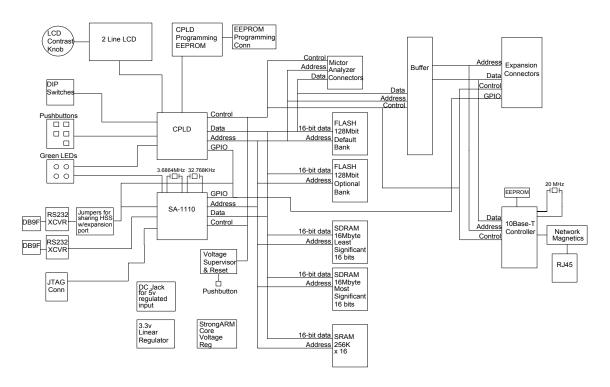

The following is a block diagram of the Cypress StrongARM SBC.

Figure 2-2. Cypress StrongARM SBC - Block Diagram

# 2.3 Processor and Memory

The Cypress StrongARM SBC uses the Intel StrongARM SA-1110 microprocessor running at 133 MHz. The SA-1110 has built-in serial ports, memory management unit, programmable chip select unit, interrupt controller, JTAG interface, instruction cache, data cache, and programmable memory controller. The Cypress StrongARM SBC has the following memory:

- 32 Mbytes SDRAM (two 8 Meg x 16-bit parts used to make a 32-bit bus)

- 16 Mbytes FLASH (one 8 Meg x 16-bit part loaded, a second 8Meg x 16-bit part unpopulated)

- 512 Kbytes SRAM (one 256K x 16-bit part)

#### 2.4 Serial Ports

#### 2.4.1 Serial Port #1

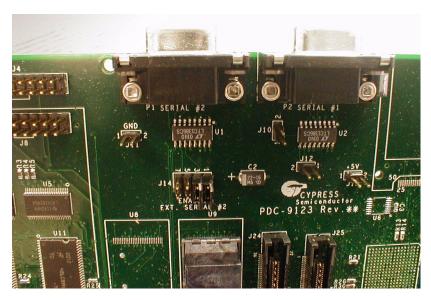

This asynchronous serial port provides communication with a terminal for control of the SBC. It does not support hardware handshaking. The port has an external DB9F connector and is labeled in silkscreen "P2 Serial #1". This port uses the on-chip StrongARM SA-1110 Channel 1 UART. Its default settings are 115200 baud, no parity, 8 data bits, and 1 stop bit. Refer to *Figure 2-3* for port location.

Figure 2-3. Serial Port Location

#### 2.4.2 Serial Port #2

This asynchronous serial port provides communication with a host PC running the DVK software application. By default, it does not support hardware handshaking, but hardware handshaking can be configured by loading shunts on the appropriate pins of J14 and modifying the Linux kernel to support it. Note that the hardware handshaking signals are shared with serial port #3 and are mutually exclusive with that port. Serial port #2 has an external DB9F connector and is labeled in silkscreen "P1 Serial #2". This port uses the on-chip StrongARM SA-1110 Channel 3 UART. Refer to Figure 2-3 for port location.

#### 2.4.3 Serial Port #3

This asynchronous serial port provides communication with a serial interface on the expansion port. By default, it does not support hardware handshaking, but hardware handshaking can be used via the CTS\_3 and RTS\_3 signals on J34. Note that the hardware handshaking signals are shared with serial port #2 and are mutually exclusive with that port. The port does not have an external connector or serial transceiver but is directly routed to the expansion port on J7 (signal names GPIO\_IR1 as receive and GPIO\_IR2 as transmit). This port uses the on-chip StrongARM SA-1110 Channel 2 UART.

#### 2.4.4 Serial Port #4

This synchronous serial port provides communication with a synchronous serial interface on the expansion port. The port does not have an external connector or serial transceiver but is directly routed to the expansion port on J33 (signal names SSP\_SFRM, SSP\_SCLK, SSP\_TXD, SSP\_RXD). The serial port supports various synchronous serial protocols including SPI. This port uses the on-chip StrongARM SA-1110 Channel 4 Synchronous Serial Controller.

## 2.5 Expansion Port

The expansion port is a group of connectors (J3, J4, J6, J7, J8, J32, J33, J34, J35) that allows expansion cards to be connected to the SBC. The EZ-Host DVK board and EZ-OTG DVK board are examples of two expansion boards that fit this form factor. The expansion port offers the following features:

- Buffered 16-bit or 32-bit data bus, buffered address bus, buffered bus control, and buffered master active low reset

- Interrupt support

- Direct connection to several GPIO pins on StrongARM SA-1110

- Direct connection to UART and synchronous serial port on SA-1110

- Direct connection to separate programmable clocks from SA-1110

- Connection of expansion port clock to SBC's CPLD

- Direct connection to several GPIO signals from the CPLD

- Two chip selects with programmable wait states. One chip select supports the use of RDY for variable latency peripherals.

- 3.3 volt and 5 volt power from SBC.

- Expansion port connectors in 20-pin dual row connectors, which are compatible with Agilent logic analyzer terminator adapters.

Figure 2-4. SBC Expansion Port Location

Note: Be careful when removing expansion boards from the expansion port. The high number of 0.1" spacing dual row connectors in the expansion port creates so much static friction that removal of expansion cards can cause PCA flex and possible damage.

#### 2.6 CPLD

The CPLD is a Cypress Delta39K series part offering high density, great flexibility, and easy in-system programming. The configuration for the CPLD is stored in U25, which is a serial EEPROM. At power-up, the CPLD loads the configuration from the EEPROM, then allows the board to come out of reset. D2 is an LED that is lit when the configuration is finished loading in the CPLD. The CPLD has the following functions and features:

- LCD controller

- Chip select decode for network controller chip, FLASH, and LCD

- Expansion port buffer control

- · DIP switch, push button, and LED control

- GPIO controller

- Expansion port reset control

- Over 86% of resources free for custom logic

Figure 2-5. CPLD

#### 2.7 User Interface

Figure 2-6 shows the location of some LEDs, LCD, DIP switches, and pushbuttons that are part of the User Interface.

Figure 2-6. User Interface

#### 2.7.1 LCD

The SBC has a two line by 16 characters LCD that is controlled by the CPLD and is used as the primary on-board display. There is a contrast dial located on the right side of the PCA to adjust the LCD contrast. The jumper located at J31 turns on the LCD backlight if shunted.

#### 2.7.2 LEDs

The SBC has several LEDs on-board to allow the user feedback about board operation.

#### **2.7.2.1 Power LEDs**

- D5 Green LED lit when 5 volts is available

- D7 Green LED lit when 3.3 volts is available

- D1 Green LED lit when 1.55 volts is available (used for the SA-1110 core)

#### 2.7.2.2 General Purpose LEDs

- D3 Green LED connected to GPIO of SA-1110

- D4 Green LED connected to GPIO of SA-1110

- D6 Green LED connected to CPLD

- D8 Green LED connected to CPLD

#### 2.7.2.3 Network LEDs

- D9 Green LED active when network link is established

- D10 Green LED that blinks during network activity

#### 2.7.2.4 Other LEDs

D2 – Green LED active when CPLD has successfully loaded its configuration from EEPROM

#### 2.7.3 DIP Switches

The SBC has a bank of eight DIP switches for configuration. Unless indicated otherwise by other documentation, the DIP switches should be set to all OFF for normal operation.

#### 2.7.4 Pushbuttons

The SBC has six pushbuttons on board. Pushbutton S1 is the master hard reset for the board. Pushing it will result in the entire board being reset. Alternatively, it can be connected to a GPIO on the SA-1110 by moving the shunt on J40. Pushbuttons S2 through S6 provide a menu navigation interface if such a menu is implemented in software; otherwise they provide a bank of general purpose pushbuttons.

#### 2.8 Ethernet

The SBC has support for a 10Base-T network connection. The network cable is connected to the RJ45 connector located at P3, and LEDs D9 and D10 provide link and activity indication.

#### 2.9 Power

The SBC receives power from a 5 volt regulated wall transformer. Power is fused on board by the fast acting non-resetable fuse at F1. 5 volts is distributed around the board and to the expansion

port. A 3.3 volt regulator provides 3.3 volts to the board and expansion port. A 1.55 volt regulator provides voltage to the SA-1110 core. Several two-pin jumpers are sprinkled around the board providing convenient ground, 3.3 volt, and 5 volt connection.

# 2.10 Miscellaneous Jumpers

Other jumpers are present on the PCA as follows:

- J14 Isolation jumper for Serial port #2. For normal operation, pins 1-2 and 2-3 should be shunted.

- J24 and J25 These are Mictor footprints for connection of a logic analyzer supporting the Mictor form factor. If development with the SBC results in the need for logic analyzer connection to the main memory bus, Mictor connectors can be soldered in these two locations for analyzer support.

- J26, J27, and J39 These are debug headers for easy connection to an Agilent logic analyzer with a termination adapter.

- J38 This header is the JTAG interface for the SA-1110.

- J36 This jumper allows all FLASH to be protected from writes. Note that the FLASH file system in Linux needs FLASH to be writable.

- J44 This header connects to an in-circuit EEPROM programmer for CPLD configuration updates.

- Unloaded components and connections There are several unloaded component and connector footprints on the PCB. These are for future use and have not been tested.

# Chapter 3. Cypress EZ-Host Development Board

#### 3.1 Introduction

The Cypress EZ-Host development board is a versatile development platform used to demonstrate and develop with the Cypress EZ-Host USB host/peripheral controller (CY7C67300).

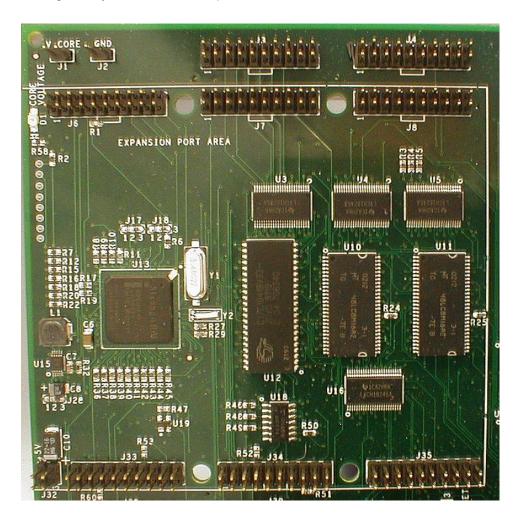

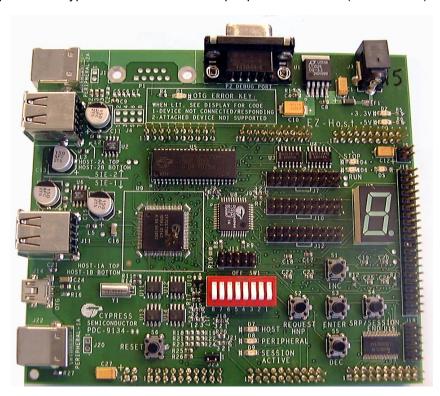

Figure 3-1. Cypress EZ-Host Development Board

#### Other features include:

48 MHz Cypress CY16 microprocessor in the Cypress EZ-Host USB host/peripheral controller (CY7C67300)

#### CY3663 Hardware User's Guide

- 64Kybtes external SRAM (one 64K x 16 part, with 32K x 16 accessible)

- 8-bit FLASH footprint (not loaded)

- User interface including seven segment display, LEDs, and pushbuttons

- In-circuit programmable CPLD

- Serial port

- Multiple host and peripheral USB ports and USB On-The-Go (OTG) support

- Charge pump for up to 10mA of five volt power for OTG VBUS

- High signal visibility with quick connect logic analyzer support

- 40-pin IDE connector

- User selectable operation either in standalone mode or co-processor mode

- Support for co-processor mode connection to the Cypress StrongARM SBC

- Support for power from external wall transformer or co-processor

# 3.2 System Block Diagram

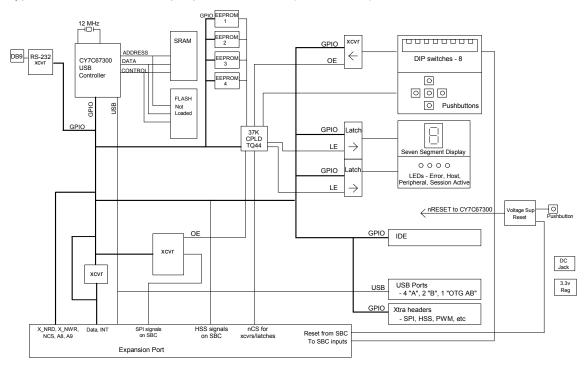

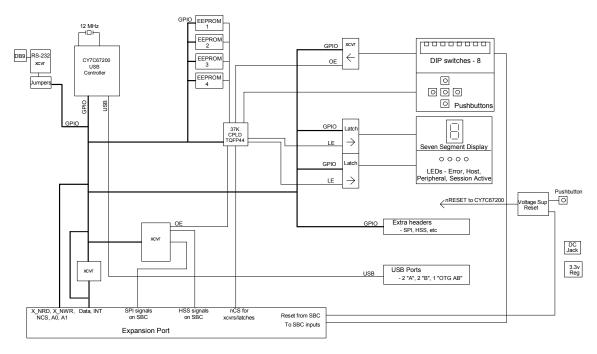

The following is a block diagram of the Cypress EZ-Host development board containing the Cypress EZ-Host USB host/peripheral controller (CY7C67300).

Figure 3-2. Cypress EZ-Host Development Board - Block Diagram

# 3.3 Processor and Memory

The Cypress EZ-Host development board is centered around the Cypress EZ-Host USB host/peripheral controller (CY7C67300). This USB controller has several on-chip features as listed below:

- 16-bit RISC Processor

- 8 Kbytes Internal ROM BIOS

- 16 Kbytes Internal SRAM

- Two UARTs

- Up to four Full-speed USB 2.0 compliant host ports

#### CY3663 Hardware User's Guide

- Up to two Full-speed USB 2.0 compliant peripheral ports

- One Full-speed USB 2.0 compliant On-The-Go (OTG) port

- Watch-dog Timer

- External SRAM and DRAM controllers

- IDE Controller

- HPI Controller

- SPI Master/Slave Controller

- Timers

# 3.4 Asynchronous Serial Ports

#### 3.4.1 UART

This serial port provides a debug and development interface for the EZ-Host chip. It does not support hardware or software handshaking. This port has an external DB9F connector with reference designator P2 and is labeled in silkscreen "DEBUG PORT".

# 3.4.2 High Speed Serial (HSS)

This serial port provides a high speed asynchronous serial interface to a co-processor. It is routed to the expansion connectors on J25 and J30 (signal names GPIO\_16, GPIO\_17, GPIO\_18, GPIO\_26). If the EZ-Host board is connected as a co-processor to the Cypress StrongARM SBC and HSS operation is selected by the appropriate DIP switch settings, the HSS port communicates with one of the serial ports on the SBC. The HSS port supports hardware handshaking. An optional connection for HSS would be to load the components for J4, U16 (and its surrounding capacitors), and P1 for an RS232 compliant port. Note that if these optional components are used, the baud rate may be limited by the maximum switching frequency of the serial transceiver at U16.

#### 3.5 SPI

The CY7C67300 contains a master/slave SPI controller. When the EZ-Host board is connected to the Cypress StrongARM SBC and SPI operation is selected by the appropriate DIP switch settings, the SPI port operates in slave mode only and is buffered before connecting to the SBC. The buffered SPI signals are available on J31 (SBC\_NSSI, SBC\_SCK, SBC\_MOSI, SBC\_MISO). The DIP switches configure the EZ-Host board for SPI operation.

# 3.6 Co-processor Connection

The EZ-Host board has a group of connectors (J24, J25, J26, J29, J30, J31, J32) which allow connection of it to the Cypress StrongARM SBC. The DIP switches configure the EZ-Host board for operation in one of the three co-processor modes: HPI, SPI, or HSS.

Note: Be careful when removing this board from the expansion port of the Cypress StrongARM SBC. The high number of 0.1" spacing dual row connectors in the expansion port creates so much static friction that removal of expansion cards can cause PCA flex and possible damage.

#### 3.7 CPLD

The CPLD is a Cypress 37K series part offering flexibility and in-circuit programming. The CPLD controls the mode the CY7C67300 powers up in by reading the DIP switch settings and driving the boot pins (GPIO\_30, GPIO\_31) appropriately. It also controls serial EEPROM selection, buffer control, and pushbutton control. The header in position J13 allows an in-circuit programmer to update the CPLD.

#### 3.8 User Interface

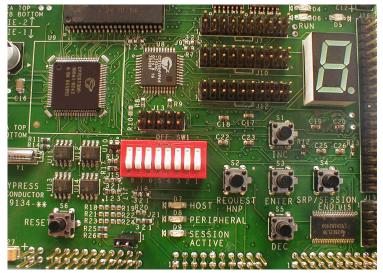

Figure 3-3 shows the location of LEDs, DIP switches, Pushbuttons, and SSD for the EZ-Host User Interface.

Figure 3-3. EZ-Host User Interface

#### 3.8.1 Seven Segment Display

The Seven Segment Display (SSD) allows hex digits to be displayed to the user. When in standalone mode, the SSD is driven by the CY7C67300. When in co-processor mode, the SSD is driven by the Cypress StrongARM SBC.

#### 3.8.2 DIP Switches

A bank of eight DIP switches controls the operation of the EZ-Host board. Based on the switch settings, the EZ-Host board powers up in standalone mode with one of four serial EEPROMs active, or in one of the three co-processor modes. The DIP switches also select any of several demonstration examples. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for a table of DIP switch settings and their definitions.

#### 3.8.3 LEDs

The EZ-Host board has several LEDs on-board to allow the user feedback about board operation.

#### 3.8.3.1 Power LEDs

- D3 Green LED lit when 5 volts is available

- D2 Green LED lit when 3.3 volts is available

### 3.8.3.2 General Purpose LEDs

- D1 Red LED lit when an OTG error is encountered during the OTG design example

- D7 Green LED lit when the board is operating in the host position during the OTG design example

- D8 Green LED lit when the board is operating in the peripheral position during the OTG design example

- D9 Green LED lit when the board has an active USB session during the OTG design example

- D4 Red general purpose LED.

- D6 Green general purpose LED.

Note: When in stand-alone mode, D1, D7, D8, and D9 are driven by the CY7C67300. When in co-processor mode, these four LEDs are driven by the Cypress StrongARM SBC.

#### 3.8.3.3 IDE LED

D5 – Green LED lit when a connected IDE device drives the nDASP line.

#### 3.8.4 Pushbuttons

The EZ-Host board has six pushbuttons on-board. Pushbutton S6 causes a hard reset to the board when in standalone mode. It has no effect in co-processor mode. Note that this pushbutton can be disabled by removing the shunt on J23. Pushbuttons S1 through S5 are general purpose input buttons that are used during the operation of the design examples. Note that the pushbuttons are read and cleared by the CY7C67300 in stand-alone mode and by the Cypress StrongARM SBC in co-processor mode.

#### 3.9 Power

The EZ-Host board can receive power either from an external five volt wall transformer or through the co-processor connectors. When in standalone mode, the power from the external five volt wall transformer is fused on board by a fast acting non-resetable fuse at F1. A 3.3 volt regulator provides 3.3 volts to the logic on the board. When in co-processor mode, power is provided by the Cypress StrongARM SBC; five volts through J32 and 3.3 volts through J24 and J30.

#### 3.10 USB Ports

The EZ-Host board has four USB host ports, two USB peripheral ports, and one USB OTG port. Not all ports can be connected at the same time. See the CY7C67300 datasheet for a table of possible simultaneous active ports. Some details for the USB section follow:

- USB host VBUS current limiting Each of the four USB host ports has a current limiting device on VBUS to prevent a USB device from drawing so much current over VBUS that the host would be damaged. These current limiting devices automatically reset after the overcurrent situation is remedied.

- USB host VBUS power Each of the four USB host ports can supply up to 500mA current

to a device, but not all four ports can simultaneously supply 500mA to peripherals. No

more than two USB host ports should be connected to devices consuming greater than

100mA current or the five volt power on the board will be drawn down.

- VBUS detect for USB peripheral ports The board supports detection of valid VBUS on both of its peripheral ports. Peripheral port one VBUS is detected via the OTG VBUS pin that connects to the CY7C67300. Peripheral port two VBUS can be detected in one of several ways:

- In standalone or co-processor mode, a register in the CPLD can be read that shows VBUS level. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for register settings.

- 2. In standalone or co-processor mode the VBUS level can be output on GPIO\_30 by setting a register in the CPLD. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for register settings.

- 3. In standalone mode, R10 can be loaded to put VBUS on GPIO 20.

#### 3.11 Miscellaneous

The EZ-Host board has several features to allow easy development and debug as listed below.

- Voltage supervisor An on-board voltage supervisor ensures clean system resets under all conditions including voltage brownout.

- EEPROM support The board has support for four separate EEPROMs. These

EEPROMs are shipped as 256-Kbit devices, but any smaller size can also be used for

custom development. If 16Kbit or smaller EEPROMs are loaded, the resistors at J15 and

J17 must be moved to the opposite position (see schematic).

- Boot pin support The board automatically sets the boot pins for the CY7C67300 in the

correct configuration based on the DIP switches. But the board can be forced into a single

boot configuration regardless of DIP switch settings if the appropriate combination of R18,

R19, R21, and R22 are loaded and R47 and R49 are removed.

- Debug headers All the 20-pin headers on the board are compatible with Agilent logic analyzer terminator adapters. This feature allows quick and simple debug connection.

# Chapter 4. Cypress EZ-OTG Development Board

#### 4.1 Introduction

The Cypress EZ-OTG development board is a versatile development platform used to demonstrate and develop with the Cypress EZ-OTG USB host/peripheral controller (CY7C67200). Other features include:

- 48 MHz Cypress CY16 microprocessor in the Cypress EZ-OTG USB Host/peripheral controller (CY7C67200)

- User interface including seven segment display, LEDs, and pushbuttons

- In-circuit Programmable CPLD

- Serial Port

- Multiple Host and peripheral USB ports and USB On-The-Go (OTG) support

- Charge pump for up to 10mA of five volt power for OTG VBUS

- High signal visibility with quick connect logic analyzer support

- · User selectable operation either in standalone mode or co-processor mode

- Support for co-processor mode connection to the Cypress StrongARM SBC

- Support for power from external wall transformer or co-processor

# 4.2 System Block Diagram

The following is a block diagram of the Cypress EZ-OTG development board containing the Cypress EZ-OTG USB host/peripheral controller (CY7C67200).

Figure 4-1. Cypress EZ-OTG Development Board - Block Diagram

# 4.3 Processor and Memory

The Cypress EZ-OTG development board is centered around the Cypress EZ-OTG USB host/peripheral controller (CY7C67200). This USB controller has several on-chip features as listed below:

- 16-bit RISC Processor

- 8 Kbytes Internal ROM BIOS

- 16 Kbytes Internal SRAM

- Two UARTs

- Up to two Full-speed USB 2.0 compliant host ports

- Up to two Full-speed USB 2.0 compliant peripheral ports

- One Full-speed USB 2.0 compliant On-The-Go (OTG) port

- Watch-dog Timer

- HPI Controller

- SPI Master/Slave Controller

- Timers

# 4.4 Asynchronous Serial Ports

#### 4.4.1 UART

This serial port provides a debug and development interface for the EZ-OTG chip. It does not support hardware or software handshaking. This port has an external DB9F connector at P2 and is labeled in silkscreen "DEBUG PORT". Note that the serial debug port on the EZ-OTG board cannot be used when in co-processor mode. To use the serial port in standalone mode, the header at J33 must have shunts applied between pins 1-2 and 3-4. In addition, the UART should not be used if the firmware uses the DIP switches or SSD. The shunts on J33 must be removed for co-processor mode.

#### 4.4.2 High Speed Serial (HSS)

This serial port provides a high speed asynchronous serial interface to a co-processor. It is routed through a buffer to the expansion connectors on J25 and J30 (signal names GPIO\_12, GPIO\_13, GPIO\_14, GPIO\_15). If the EZ-OTG board is connected as a co-processor to the Cypress StrongARM SBC and HSS operation is selected by the appropriate DIP switch settings, the HSS port communicates with one of the serial ports on the SBC. The HSS port supports hardware hand-shaking. An optional connection for HSS would be to load the components for J4, U16 (and its surrounding capacitors), and P1 for an RS232 compliant port. Note that if these optional components are used, the baud rate may be limited by the maximum switching frequency of the serial transceiver at U16.

#### 4.5 SPI

The CY7C67200 contains a master/slave SPI controller. When the EZ-OTG board is connected to the Cypress StrongARM SBC and SPI operation is selected by the appropriate DIP switch settings, the SPI port operates in slave mode only and is buffered before connecting to the SBC. The buffered SPI signals are available on J31 (SBC\_NSSI, SBC\_SCK, SBC\_MOSI, SBC\_MISO). The DIP switches configure the EZ-OTG board for SPI operation.

# 4.6 Co-processor Connection

The EZ-OTG board has a group of connectors (J24, J25, J26, J29, J30, J31, J32) which allow connection of it to the Cypress StrongARM SBC. But even in standalone mode, the UART should not be used if the firmware accesses the DIP switches or SSD on the board. The DIP switches configure the EZ-OTG board for operation in one of the three co-processor modes: HPI, SPI, or HSS.

Note: Be careful when removing this board from the expansion port of the Cypress StrongARM SBC. The high number of 0.1" spacing dual row connectors in the expansion port creates so much static friction that removal of expansion cards can cause PCA flex and possible damage.

#### **4.7 CPLD**

The CPLD is a Cypress 37K series part offering flexibility and in-circuit programming. The CPLD controls the mode the CY7C67200 powers up in by reading the DIP switch settings and driving the boot pins (GPIO\_30, GPIO\_31) appropriately. It also controls serial EEPROM selection, buffer control, and pushbutton control. The header in position J13 allows an in-circuit programmer to update the CPLD.

#### 4.8 User Interface

#### 4.8.1 Seven Segment Display

The Seven Segment Display (SSD) allows hex digits to be displayed to the user. When in standalone mode, the SSD is driven by the CY7C67200. When in co-processor mode, the SSD is driven by the Cypress StrongARM SBC.

#### 4.8.2 DIP Switches

A bank of eight DIP switches controls the operation of the EZ-OTG board. Based on the switch settings, the EZ-OTG board powers up in standalone mode with one of four serial EEPROMs active, or in one of the three co-processor modes. The DIP switches also select any of several demonstration examples. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for a table of DIP switch settings and their definitions.

#### 4.8.3 LEDs

The EZ-OTG board has several LEDs on-board to allow the user feedback about board operation.

#### **4.8.3.1 Power LEDs**

- D3 Green LED lit when 5 volts is available

- D2 Green LED lit when 3.3 volts is available

#### 4.8.3.2 General Purpose LEDs

- D1 Red LED lit when an OTG error is encountered during the OTG design example

- D7 Green LED lit when the board is operating in the host position during the OTG design example

- D8 Green LED lit when the board is operating in the peripheral position during the OTG design example

- D9 Green LED lit when the board has an active session during the OTG design example

Note: When in stand-alone mode, D1, D7, D8, and D9 are driven by the CY7C67200. When in co-processor mode, these four LEDs are driven by the Cypress StrongARM SBC.

#### 4.8.4 Pushbuttons

The EZ-OTG board has six pushbuttons on-board. Pushbutton S6 causes a hard reset to the board when in standalone mode. It has no effect in co-processor mode. Note that this pushbutton can be disabled by removing the shunt on J23. Pushbuttons S1 through S5 are general purpose input buttons that are used during the operation of the design examples. Note that the pushbuttons are read and cleared by the CY7C67200 in stand-alone mode and by the Cypress StrongARM SBC in co-processor mode.

#### 4.9 Power

The EZ-OTG board can receive power either from an external five volt wall transformer or through the co-processor connectors. When in standalone mode, the power from the external five volt wall transformer is fused on board by a fast acting non-resetable fuse at F1. A 3.3 volt regulator provides 3.3 volts to the logic on the board. When in co-processor mode power is provided by the Cypress StrongARM SBC; five volts through J32 and 3.3 volts through J24 and J30.

#### 4.10 USB Ports

The EZ-OTG board has two USB host ports, two USB peripheral ports, and one USB OTG port. Not all ports can be connected at the same time. See the CY7C67200 datasheet for a table of possible simultaneous active ports. Some details for the USB section follow:

USB host VBUS current limiting – Each of the two USB host ports has a current limiting device on VBUS to prevent a USB device from drawing so much current over VBUS that the host would be damaged. These current limiting devices automatically reset after the overcurrent situation is remedied.

- USB host VBUS power Each of the two USB host ports can supply up to 500mA current to a device.

- VBUS detect for USB peripheral ports The board supports detection of valid VBUS on both of its peripheral ports. Peripheral port one VBUS is detected via the OTG VBUS pin that connects to the CY7C67200. Peripheral port two VBUS can be detected in one of several ways:

- In standalone or co-processor mode, a register in the CPLD can be read that shows VBUS level. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for register settings.

- In standalone or co-processor mode the VBUS level can be output on GPIO\_30 by setting a register in the CPLD. Refer to Chapter 5. "Developing with the EZ-Host and EZ-OTG Boards" for register settings.

- 3. In standalone mode, R10 can be loaded to put VBUS on GPIO\_20.

#### 4.11 Miscellaneous

The EZ-OTG board has several features to allow easy development and debug as listed below.

- Voltage supervisor An on-board voltage supervisor ensures clean system resets under all conditions including voltage brownout.

- EEPROM support The board has support for four separate EEPROMs. These

EEPROMs are shipped as 128Kbit devices, but any smaller size can also be used for custom development. If 16Kbit or smaller EEPROMs are loaded, then the resistors at J15

and J17 must be moved to the opposite position (see schematic).

- Boot pin support The board automatically sets the boot pins for the CY7C67200 in the

correct configuration based on the DIP switches. But the board can be forced into a single

boot configuration regardless of DIP switch settings if the appropriate combination of R18,

R19, R21, and R22 are loaded and R47 and R49 are removed.

- Debug headers All the 20-pin headers on the board are compatible with Agilent logic analyzer terminator adapters. This feature allows quick and simple debug connection.

# Chapter 5. Developing with the EZ-Host and EZ-OTG Boards

# 5.1 Standalone Mode Operation

#### 5.1.1 Power-up EEPROM Selection

Since no signal is present on the CP\_PRESENT (co-processor present) line, the CPLD looks at the DIP switch settings and decides which EEPROM should be enabled.

#### 5.1.2 DIP Switches

- Read via the CPLD

- Note on EZ-OTG board, if Debug UART is being used, then the upper two DIP positions cannot be read.

# 5.1.3 Pushbutton Inputs

- PB inputs are latched in CPLD

- · Read through CPLD

- Cleared through CPLD write, one write per button

## 5.1.4 LEDs: OTG ERROR, SESSION ACTIVE, HOST, PERIPHERAL

Written through the CPLD.

#### 5.1.5 LEDs: RUN/STOP

Only available on EZ-Host board. Any write to external ROM space affects these two LEDs based on the lowest two data bus bits as follows:

Table 5-1. Run/Stop LEDs

| CY7C67300 memory<br>bus data bit 1 (D1) | CY7C67300 memory<br>bus data bit 0 (D0) | STOP LED<br>(red) | RUN LED<br>(green) |

|-----------------------------------------|-----------------------------------------|-------------------|--------------------|

| 0                                       | 0                                       | ON                | ON                 |

| 0                                       | 1                                       | ON                | OFF                |

| 1                                       | 0                                       | OFF               | ON                 |

| 1                                       | 1                                       | OFF               | OFF                |

MOTE: L

NOTE: LEDs reset on power-up to OFF

#### 5.1.6 Seven Segment Display

- Similar to LEDs. Written through CPLD

- Note that if the UART is enabled on the EZ-OTG board, the upper two segments cannot be written and will be driven to whatever happens to be on the UART pins at the time of the write.

#### 5.1.7 Debugging Through the UART

- The UART will work in all situations with the EZ-Host board.

- The UART can be used in standalone mode with the EZ-OTG board. The limitation is that

whenever the CPLD is accessed, GPIO\_6 must not be changed from its UART configuration as an input. And because the UART uses GPIO\_6 and GPIO\_7, the upper two DIP

switch positions cannot be reliably read, and the upper two segments cannot be reliably

written on the Seven Segment Display.

#### 5.1.8 CPLD Accesses

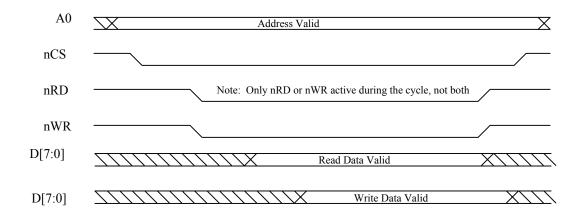

In stand-alone mode, the CY7C67300 or CY7C67200 accesses the peripherals through the CPLD by creating a typical memory access type cycle using the following GPIO signals:

Address: A0 (GPIO\_19)

Chip Select: nCS (GPIO\_21)

Read Strobe: nRD (GPIO\_23)

Write Strobe: nWR (GPIO\_22)

Data: D[7:0] (GPIO\_[7:0], where GPIO\_7 is the most significant bit)

See the waveform diagram below. Note that nRD and nWR are mutually exclusive; that is, only one should be asserted (low) per access. Timing should not be an issues since f/w is bit-banging these signal bits creating plenty of timing margin between signal transitions.

Figure 5-1. Timing Waveforms

# 5.2 Co-processor Mode Operation

### 5.2.1 Power-up Port Selection

Since the CP\_PRESENT pin will be driven by the SBC, the EZ-Host/OTG CPLD will strap the boot pins to whatever the DIP inputs select (HPI, HSS, or SPI), assuming it is a legitimate combination of demo and communication method. The EZ-Host/OTG controller will power up into that mode.

NOTE: In SPI and HSS mode, the EZ-Host/OTG controller must be configured to tri-state GPIO[24:19] and GPIO[7:0] or the SBC cannot read and write the DIP switches, pushbuttons, LEDS, and SSD.

### 5.2.2 DIP Switches

- HPI mode: SBC can read them through the EZ-Host/OTG CPLD

- SPI mode: SBC can read them through the EZ-Host/OTG CPLD

- HSS mode: SBC can read them through the EZ-Host/OTG CPLD

- Additionally, SBC can read them through its own CPLD (the SBC CPLD)

### 5.2.3 Push Button Inputs

- HPI mode: SBC can read them through EZ-Host/OTG CPLD and clear them individually through EZ-Host/OTG CPLD

- SPI mode: SBC can read them through the EZ-Host/OTG CPLD and clear them individually through EZ-Host/OTG CPLD

- HSS mode: SBC can read them through the EZ-Host/OTG CPLD and clear them individually through EZ-Host/OTG CPLD

### 5.2.4 LEDs

HPI mode: SBC can write them via the EZ-Host/OTG CPLD

SPI mode: SBC can write them via the EZ-Host/OTG CPLD

HSS mode: SBC can write them via the EZ-Host/OTG CPLD

### 5.2.5 Seven Segment Display

Similar to LEDs in all three co-processor modes

### 5.2.6 CPLD Accesses

The co-processor will access the EZ-Host/OTG CPLD with a normal asynchronous memory-type access. Refer to Section 5.3. "Addressing of EZ-Host/OTG CPLD" for more details.

### 5.2.7 Debugging Through the UART

- The UART will work in all situations with the EZ-Host board.

- The UART cannot be reliably used in co-processor mode with the EZ-OTG board. Unrelated memory cycles on the SBC will clobber both transmit and receive data randomly.

# 5.3 Addressing of EZ-Host/OTG CPLD

All EZ-Host/OTG CPLD activity is controlled by indirect addressing. There are two direct registers in the CPLD: the pointer register (called ADD\_Reg), and the data register (called Data\_Reg). Writing to the CPLD with A0 = 0 (this is the GPIO\_19 pin) will write to the ADD\_Reg, which makes the Data\_Reg register point to the new indirect register. Reading or writing with A0 = 1 will read or write to that indirect register.

Table 5-2. Memory Map for Direct CPLD Registers

| Direct Address | Register Name | Description                                                                              |                                                    |

|----------------|---------------|------------------------------------------------------------------------------------------|----------------------------------------------------|

| A0 = 0         | ADD_Reg       | Address Pointer Register. Writes to pointer register                                     | Write Only (Read value can be accessed indirectly) |

| A0 = 1         | Data_Reg      | Read or write from/to indirect register pointed to by Address Pointer Register (ADD_Reg) | Read/Write                                         |

# 5.3.1 ADD\_Reg

Register that contains the address pointer to the indirect registers

Address A0 = 0x0 (Direct address)

Write only

Resets to XXX00000

### Bit Description

4:0 Address pointer to indirect registers

7:5 Unused

## 5.3.2 Data\_Reg

Register that writes to or reads from an indirect register. Controlled by the address in the ADD\_Reg register

Address A0 = 0x1 (Direct address)

Read/Write

Resets to XXXXXXXX

### Bit Description

7:0 Data in indirect register pointed to by ADD\_Reg

# 5.4 Memory Map for Indirect CPLD Registers

Table 5-3. Memory Map for Indirect CPLD Registers

| Register Name   | Indirect Address |            |  |

|-----------------|------------------|------------|--|

| PB_Read         | 0x0              | Read only  |  |

| PB_UP_Clr       | 0x1              | Write only |  |

| PB_LEFT_Clr     | 0x2              | Write only |  |

| PB_RIGHT_Clr    | 0x3              | Write only |  |

| PB_DOWN_CIr     | 0x4              | Write only |  |

| PB_ENTER_Clr    | 0x5              | Write only |  |

| DIP_Read        | 0x6              | Read only  |  |

| LED_Write       | 0x7              | Write only |  |

| SSD_Write       | 0x8              | Write only |  |

| VBUS_Level      | 0x9              | Read only  |  |

| VBUS_On_GPIO_30 | 0xA              | Read/Write |  |

| ADD_Reg_Read    | 0xB              | Read only  |  |

| EEPROM_MFG_CTL  | 0xC              | Read/Write |  |

# 5.5 EZ-Host/OTG CPLD Indirect Register Descriptions

# 5.5.1 PB\_Read

Register that holds latched value of push-buttons

Address 0x0

Read only

Resets to XXX11111

| <u>Bit</u> | <u>Description</u>                                 |

|------------|----------------------------------------------------|

| 0          | PB_UP latched value (0 is latched, 1 is unlatched) |

| 1          | PB_LEFT latched value                              |

| 2          | PB_RIGHT latched value                             |

| 3          | PB_DOWN latched value                              |

| 4          | PB_ENTER latched value                             |

| 7:5        | Unused                                             |

# 5.5.2 PB\_UP\_CIr

Register that clears the latch of a pushbutton

Address 0x1

Write only

Any write of any value to this register will result in the PB\_UP latch being cleared.

# 5.5.3 PB\_LEFT\_CIr

Register that clears the latch of a pushbutton

Address 0x2

Write only

Any write of any value to this register will result in the PB\_LEFT latch being cleared.

### 5.5.4 PB\_RIGHT\_CIr

Register that clears the latch of a pushbutton

Address 0x3

Write only

Any write of any value to this register will result in the PB\_RIGHT latch being cleared.

# 5.5.5 PB\_DOWN\_CIr

Register that clears the latch of a pushbutton

Address 0x4

Write only

Any write of any value to this register will result in the PB\_DOWN latch being cleared.

# 5.5.6 PB\_ENTER\_CIr

Register that clears the latch of a pushbutton

Address 0x5 Write only

Any write of any value to this register will result in the PB\_ENTER latch being cleared.

# 5.5.7 DIP\_Read

Register that allows the read of the bank of 8 DIP switches

Address 0x6 Read only

| <u>Bit</u> | <u>Description</u> |

|------------|--------------------|

| 0          | DIP_1 switch value |

| 1          | DIP_2 switch value |

| 2          | DIP_3 switch value |

| 3          | DIP_4 switch value |

| 4          | DIP_5 switch value |

| 5          | DIP_6 switch value |

| 6          | DIP_7 switch value |

| 7          | DIP_8 switch value |

# 5.5.8 LED\_Write

Register that allows the four individual LEDs to be written

Address 0x7 Write only Resets to XXXXXXXX

| <u>Bit</u> | <u>Description</u>                    |

|------------|---------------------------------------|

| 0          | ERROR LED – Writing a "0" turns it on |

| 1          | HOST LED                              |

| 2          | PERIPHERAL LED                        |

| 3          | SESSION ACTIVE LED                    |

| 7.4        | Not connected Write any value         |

# 5.5.9 SSD\_Write

Register that allows the Seven-Segment-Display to be written

Address 0x8

Write only

Resets to XXXXXXXX

| <u>Bit</u> | <u>Description</u>                    |             |

|------------|---------------------------------------|-------------|

| 0          | A Segment – Writing a "0" turns it on | <b>a</b>    |

| 1          | B Segment                             |             |

| 2          | C Segment                             | <b>ਰ</b>    |

| 3          | D Segment                             |             |

| 4          | E Segment                             | e e         |

| 5          | F Segment                             | (d) () (lm) |

| 6          | G Segment                             |             |

| 7          | DP Segment                            |             |

# 5.5.10 VBUS\_Level

Register that contains the VBUS level of the peripheral port on SIE2 of the EZ-Host/OTG controller.

**Note:** This is a TTL input reading an analog voltage. If the actual VBUS voltage is between about 0.8 volts and 2.7 volts, the register may read low or high.

Address 0x9

Read only

| <u>Bit</u> | <u>Description</u>                    |

|------------|---------------------------------------|

| 0          | VBUS level on peripheral port of SIE2 |

| 7:1        | Unused                                |

### 5.5.11 VBUS\_On\_GPIO\_30

Register that drives VBUS from the peripheral port of SIE2 of the EZ-Host/OTG controller onto signal pin GPIO\_30.

**NOTE:** In standalone mode GPIO\_30 is used as the EEPROM clock (SCL), so make sure EEPROM activity is done before configuring GPIO\_30 to reflect the SIE2 VBUS level.

Address 0xA Read/Write Resets to XXXXXXX0

### **Bit Description**

- If set, drive the level of VBUS on peripheral port of SIE2 onto GPIO\_30. If clear, GPIO\_30 is driven to a level dictated by the DIP switches

- 7:1 Not used

### 5.5.12 Add\_Reg\_Read

Register that contains the indirect register address. This register is probably not very useful.

Address 0xB

Read Only

Resets to XXXXXXXX

### Bit Description

- 3:0 Value of indirect register address

- 7:4 Not used

### 5.5.13 EEPROM\_MFG\_CTL

Register that allows a co-processor to drive the EEPROM address lines, clock and data lines. It also allows the EZ-Host/OTG controller to select any EEPROM regardless of the DIP switch settings. This register is meant for manufacturing use and is probably not useful for development.

**NOTE:** Control of the EEPROM using this register does not allow EEPROM reads through the CPLD. The actual data pin of the EEPROM (SDA) is read through one of the SBC's directly connected general purpose pins. Also, when reading an EEPROM, the user must make sure to drive

the SCL pin high (set bit 0 of this register) because that drives a pull-up, which is required for that signal.

Address 0xC Read/Write Resets to XXX00000

# Bit Description Value to drive SCL if bit 2 is set Value to drive SDA if bit 2 is set Setting this bit makes the other bits of this register drive the EEPROM address lines and control lines. EEPROM address select bit 0 if bit 2 is set. See table below. EEPROM address select bit 1 if bit 2 is set. See table below. Not used

Table 5-4. EEPROM Address Select Bits 3 and 4

| EEPROM_MFG_CTL[4] | EEPROM_MFG_CTL[3] | EEPROM Selected |

|-------------------|-------------------|-----------------|

| 0                 | 0                 | EEPROM 1        |

| 0                 | 1                 | EEPROM 2        |

| 1                 | 0                 | EEPROM 3        |

| 1                 | 1                 | EEPROM 4        |

# 5.6 EZ-Host/OTG Board Pushbutton and DIP Switch Definitions

### 5.6.1 DIP Switch Settings

There is a bank of eight DIP switches on the EZ-Host/OTG board. Note that only the DIP switches on the EZ-Host/OTG board will be used to configure the demos, not the DIP switches on the SBC. The DIP switches are labeled 1-8 on the part and also have an "OFF" or "OPEN" label for one direction. Note: "OFF" is a logical 1 when read by hardware, and "ON" is logical 0 when read by hardware. In addition not all combinations of Communication Mode (DIP switches 1 and 2) are valid with all combinations of Design Example Number (DIP switches 3, 4, 5, and 6).

Table 5-5. Switch Settings for Switch 1 and 2

| Switch 2 | Switch 1 | Communication Mode |

|----------|----------|--------------------|

| OFF      | OFF      | Standalone         |

| OFF      | ON       | SPI                |

| ON       | OFF      | HPI                |

| ON       | ON       | HSS                |

Table 5-6. Switch Settings for Switch 3, 4, 5, and 6

| Switch 6 | Switch 5 | Switch 4 | Switch 3 | Design Example #                                                                                                                    |

|----------|----------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| OFF      | OFF      | OFF      | OFF      | Default *                                                                                                                           |

| OFF      | OFF      | OFF      | ON       | Design Example 1 – OTG Standalone mode - Valid, EEPROM 1 enabled Coprocessor mode - Valid, HPI only                                 |

| OFF      | OFF      | ON       | OFF      | Design Example 2 – Dual Slave<br>Standalone mode - Invalid<br>Coprocessor mode - Valid                                              |

| OFF      | OFF      | ON       | ON       | Design Example 3 – Peripheral-Host<br>Passthrough<br>Standalone mode- Valid, EEPROM 2 enabled<br>Coprocessor mode - Valid, HPI only |

| OFF      | ON       | OFF      | OFF      | Design Example 4 - Dual Host<br>Standalone mode - Valid, EEPROM 3 enabled<br>Coprocessor mode - Valid, HPI only                     |

| OFF      | ON       | Х        | ON       | Invalid                                                                                                                             |

| OFF      | ON       | ON       | Х        | Invalid                                                                                                                             |

| ON       | OFF      | Х        | Х        | Invalid                                                                                                                             |

| ON       | ON       | OFF      | OFF      | Standalone mode - Valid, IDE enabled, CPLD inactive, EEPROM 4 Enabled Coprocessor mode - Invalid                                    |

| ON       | ON       | OFF      | ON       | Invalid                                                                                                                             |

| ON       | ON       | ON       | OFF      | Invalid                                                                                                                             |

| ON       | ON       | ON       | ON       | Standalone mode - Valid, EEPROM 4 enabled Coprocessor mode - Invalid                                                                |

<sup>\*</sup> Default means the following:

<sup>-</sup> Coprocessor mode: Power up in HPI mode.

**Note:** The four switches assigned to selecting the Design Example # are more than is currently necessary, but they allow more selections as demos are added in the future.

<sup>-</sup> Standalone mode: Power up with no EEPROM (BIOS configures EZ-Host/OTG controller)

Note: If an invalid switch combination is set and the EZ-Host/OTG board is connected to a co-processor, the EZ-Host/OTG controller will power up in HPI mode, but the SBC will not be able to talk to the EZ-Host/OTG controller. The SBC can, however, talk to the rest of the DVK board. If an invalid switch combination is set and the EZ-Host/OTG board is NOT connected to a co-processor, it will power up in standalone mode with no boot EEPROM.

Table 5-7. Switch Settings for Switch 7 and 8

| Switch 7 | Switch 8 | Function                      |

|----------|----------|-------------------------------|

| OFF      | OFF      | Default to allow demos to run |

| X        | ON       | Undefined                     |

| ON       | Х        | Undefined                     |

Note: The EZ-Host/OTG board does not look at switches 7 and 8 for power-up h/w configuration.

Table 5-8. Table of Valid Switch Combinations

| DIP[6:1] | Description                                                                                |

|----------|--------------------------------------------------------------------------------------------|

| 000000   | "User" setting. Standalone mode has no EEPROM selected. Co-processor mode has HPI enabled. |

| 000100   | Demo 1, OTG, Standalone mode, EEPROM 1 Active                                              |

| 000110   | Demo 1, OTG, Co-processor mode, HPI communication                                          |

| 001001   | Demo 2, Dual Slave, Co-processor mode, SPI communication                                   |

| 001010   | Demo 2, Dual Slave, Co-processor mode, HPI communication                                   |

| 001011   | Demo 2, Dual Slave, Co-processor mode, HSS communication                                   |

| 001100   | Demo 3, Peripheral Host Passthrough, Standalone mode, EEPROM 2 Active                      |

| 001110   | Demo 3, Peripheral Host Passthrough, Co-processor mode, HPI communication                  |

| 010000   | Demo 4, Dual Host, Standalone mode, EEPROM 3 Active                                        |

| 010010   | Demo 4, Dual Host, Co-processor mode, HPI communication                                    |

| 1100XX   | Standalone mode, EEPROM 4 active, IDE mode, CPLD disabled                                  |

| 111100   | Standalone mode, EEPROM 4 active                                                           |

Note: In this table, OFF=0 and ON=1

### 5.6.2 Pushbuttons

The pushbuttons necessary on the EZ-Host/OTG board for the demo functionality are as follows. They are laid out in a form factor resembling the SBC board as shown in the diagram below.

$$\begin{matrix} & & X \\ X & X & X \\ & X \end{matrix}$$

- Top button S1: PB\_UP, labeled "INC" (increment or "+")

- Bottom button S5: PB DOWN, labeled "DEC" (decrement or "-")

- Left Button S2: PB\_LEFT, labeled "Request HNP" (request a Host Negotiation Protocol

if I am an OTG device at the moment)

- Right Button S4: PB\_RIGHT, labeled "SRP/Session End" (Request a Session Request Protocol if I am an OTG device and there is no active session. Force an end of session if I am an OTG host)

- Center button S3: PB ENTER, labeled "ENTER". Not used in the demos.

**Note:** There is a pushbutton (S6) available that causes a hard reset to the EZ-Host/OTG board. Note that it would be a bad idea to push this button when connected to the SBC because communication with the SBC would be broken and likely not recoverable without a system power cycle.

### 5.6.3 LEDs

- There is an "OTG ERROR" LED to indicate that one of the few OTG reportable errors has occurred, such as over current on the VBUS line or device not supported. This LED will work in conjunction with the hex display. In the case of an error, the "OTG ERROR" LED will be lit and the appropriate error code will be displayed on the hex display. Silkscreen on the board will be a key to the errors. See the LED\_Write register for the "OTG ERROR" bit position.

- There are a "HOST" LED and a separate "PERIPHERAL" LED on the board that will be

displayed when the board is acting in the appropriate function. These LEDs will only be

useful when running the OTG demo because some of the other demos require the EZHost/OTG board to be a host and peripheral simultaneously. See the LED\_Write register

for the "HOST" and "Peripheral" bit position.

- There is a "SESSION ACTIVE" LED. Once again, it is only useful in the OTG demo. See the LED\_Write register for the "SESSION ACTIVE" bit position.

- There is a "+5v" LED and a "+3.3v" LED. These will be lit when the appropriate power is present.

### 5.6.4 Hex Display

A seven segment hex display is available. It will be used in the OTG demo to show an incrementing or decrementing value or to display an error code. This display may also be used in other demos as a debugging aid. See the SSD\_Write register for its bit positions.

# 5.7 Co-processor Mode Hints

When a EZ-Host/OTG board is in co-processor mode, it will:

- 1. Power up and be idle until the SBC toggles its hardware reset.

- 2. Read its DIP switch settings.

- 3. Detect it is in co-processor mode.

- 4. Detect what its method of communication with the SBC is based on DIP switch settings.

- 5. Configure itself for that mode.

- Wait for communication from the SBC.

### The SBC has the ability to:

- Determine that an EZ-Host/OTG board is attached.

- Control the hardware reset line of the EZ-Host/OTG board.

- Read the DIP switch settings of the EZ-Host/OTG board no matter the what mode the EZ-Host/OTG board thinks it is in. The ability of the SBC to read the DIP switches gives the opportunity to report back to the controlling software if the user has not configured the EZ-Host/OTG board correctly.

A couple of things to be aware of are:

- The SBC should reset the EZ-Host/OTG board.

- The SBC must wait a reasonable amount of time for the EZ-Host/OTG board BIOS to configure itself (see datasheet for minimum time delay).

- When the EZ-Host/OTG board is powered up correctly, the SBC will then have access to the pushbuttons and DIP switches and must drive the LEDs and seven-segment display on the EZ-Host/OTG board appropriately.

# 5.8 Recommended GPIO Settings for the EZ-Host/OTG Boards

The following table gives recommended GPIO settings for the EZ-Host/OTG controller when used on either the EZ-Host or EZ-OTG DVK board. Note the differences in parenthesis for the EZ-OTG controller.

### Table Key:

I - Input I/O - Bidirectional

O - Output NA - BIOS sets it for you

Table 5-9. GPIO Settings

| GPIO# | Standalone | Co-processor<br>HPI | Co-processor<br>SPI | Co-processor<br>HSS |

|-------|------------|---------------------|---------------------|---------------------|

| 0     | I/O        | NA                  | I                   | I                   |

| 1     | I/O        | NA                  | I                   | I                   |

| 2     | I/O        | NA                  | I                   | I                   |

| 3     | I/O        | NA                  | I                   | I                   |

| 4     | I/O        | NA                  | I                   | I                   |

| 5     | I/O        | NA                  | I                   | I                   |

| 6     | I/O        | NA                  | I                   | I                   |

| 7     | I/O        | NA                  | I                   | I                   |

| 8     | 0          | NA                  | NA                  | 0                   |

| 9     | 0          | NA                  | NA                  | I                   |

| 10    | 0          | NA                  | NA                  | I                   |

| 11    | 0          | NA                  | NA                  | I                   |

| 12    | 0          | NA                  | 0                   | O (NA for EZ-OTG)   |

| 13    | 0          | NA                  | O (I for EZ-OTG)    | O (NA for EZ-OTG)   |

| 14    | 0          | NA                  | 0                   | O (NA for EZ-OTG)   |

| 15    | 0          | NA                  | O (I for EZ-OTG)    | O (NA for EZ-OTG)   |

| 16    | 0          | 0                   | 0                   | NA                  |

| 17    | I          | I                   | I                   | NA                  |

| 18    | 0          | 0                   | 0                   | NA                  |

| 19    | 0          | NA                  | I                   | I                   |

| 20    | 0          | NA                  | I                   | I                   |

| 21    | 0          | NA                  | I                   | I                   |

| 22    | 0          | NA                  | ı                   | 1                   |

Table 5-9. GPIO Settings

| GPIO# | Standalone | Co-processor<br>HPI | Co-processor<br>SPI | Co-processor<br>HSS |

|-------|------------|---------------------|---------------------|---------------------|

| 23    | 0          | NA                  | I                   | ı                   |

| 24    | I          | NA                  | I                   | I                   |

| 25    | I          | I                   | I                   | I                   |

| 26    | I          | I                   | I                   | NA                  |

| 27    | I          | I                   | I                   | I                   |

| 28    | 0          | 0                   | 0                   | 0                   |

| 29    | I          | I                   | I                   | I                   |

| 30    | NA         | I                   | I                   | I                   |

| 31    | NA         | I                   | I                   | I                   |

# 5.9 Restoring the EZ-Host and EZ-OTG Boards to Factory Defaults

The EZ-Host board and the EZ-OTG board can be restored to factory defaults by doing the following things:

- 1. If the EZ-Host or EZ-OTG board is connected to the expansion port of a SBC, remove it.

- 2. Set all DIP switches to the OFF or OPEN position

- 3. Plug a USB cable from the PC to either of the board's USB peripheral ports. Note the PC must have the CY3663 DVK software installed.

- 4. Power on the EZ-Host or EZ-OTG board. The board will power up in a debug mode.

- 5. Open a DOS window. Alternatively, you can open a BASH shell.

- 6. Change your DOS prompt or BASH shell prompt to the Tools\Utilities subdirectory that was installed from the CD that originally shipped with the kit.

- 7. Set the DIP switches to only DIP switch 3 ON.

- 8. Type in the following at the DOS prompt. This runs a utility that downloads the de1\_scan.bin file over USB to the board and programs it into the EEPROM that is selected by the DIP switch settings (EEPROM 1 in this case). Note that if you are using a BASH shell you must replace the backslash characters with forward slash characters.

```

qtui2c ..\..\cy3663~1\stand-alone\de1_scan.bin f

```

- 9. Wait for the prompt to come back. The OTG design example is now restored to factory default. NOTE: This programming step is only valid on the EZ-Host board since the EZ-OTG board does not support the OTG design example in standalone mode.

- 10. Set the DIP switches to only 3 and 4 ON.

11. Type in the following at the DOS prompt. This runs a utility that downloads the de3\_scan.bin file over USB to the board and programs it into the EEPROM that is selected by the DIP switch settings (EEPROM 2 in this case). Note that if you are using a BASH shell you must replace the backslash characters with forward slash characters.

```

qtui2c ..\..\cy3663~1\stand-alone\de3_scan.bin f

```

- 12. Wait for the prompt to come back. The Peripheral-Host design example is now restored to factory default

- 13. Set the DIP switches to only 5 ON.

- 14. Type in the following at the DOS prompt. This runs a utility that downloads the de4\_scan.bin file over USB to the board and programs it into the EEPROM that is selected by the DIP switch settings (EEPROM 3 in this case). Note that if you are using a BASH shell you must replace the backslash characters with forward slash characters.

```

qtui2c ..\..\cy3663~1\stand-alone\de4_scan.bin f

```

15. Wait for the prompt to come back. The Dual Host design example is now restored to factory default. NOTE: This programming step is only valid on the EZ-Host board since the EZ-OTG board does not support the Dual Host design example in standalone mode.

# Chapter 6. Developing with the Cypress StrongArm SBC

# 6.1 Normal Operation of the Cypress StrongARM SBC

### 6.1.1 Running Design Examples

The Cypress StrongARM SBC can be used for normal operation to run the Design Examples right out of the box. Do the following to connect it:

- 1. Connect the desired mezzanine card (either the EZ-Host board or the EZ-OTG board) to the expansion port.

- 2. Connect a PC running the OTG-Host Navigator software to the serial port on the SBC marked "P1 Serial #2".

- Verify that the bank of DIP switches on the SBC near the LCD has all switches in the off position.

- 4. Connect the power supply to the SBC.

- 5. Follow the instructions in the Design Example tutorial software.

# 6.1.2 Operation as a Linux USB Muti-port Host

The Cypress StrongARM SBC can be used as a multi-port USB host system right out of the box. The Linux kernel that ships on the board has USB class driver support for hub, mass storage, and audio. Do the following to boot the board into the multi-port USB host system mode:

- If not already attached, connect the desired mezzanine card (either the EZ-Host board or the EZ-OTG board) to the expansion port.

- Connect a PC running a serial terminal program such as HyperTerminal to the serial port on the SBC marked "P2 Serial #1". The terminal software should be set up for 115200 baud, no parity, 8 data bits, 1 stop bit, and no flow control.

- 3. Verify that the bank of DIP switches on the SBC near the LCD has all switches in the OFF or OPEN position.

- 4. Verify that the bank of DIP switches on the EZ-Host or EZ-OTG card (which is connected to the expansion port of the SBC) are in the OFF or OPEN position.

- 5. Connect the power supply to the SBC.

6. Watch the terminal window to see it boot to the Linux login prompt. Login username is "root", and there is no password.

# 6.2 Linux Development with the Cypress StrongARM SBC

### 6.2.1 Boot Sequence

The normal boot sequence of Cypress StrongARM SBC is as follows:

- 1. At power-on-reset, the ARMBoot boot loader executes.