May. 2001 ver1.1

# 8-BIT SINGLE-CHIP MONITOR MICROCONTROLLERS

# HMS9xC7132 HMS9xC7134

**User's Manual**

| <b>T</b> 7 |       | -1 | 1 |

|------------|-------|----|---|

| V/A        | rsion |    |   |

|            |       |    |   |

Published by MCU Application Team bjinlim@hynix.com blackjoe@hynix.com

© 2001 HYNIX Semiconductor All right reserved.

Additional information of this manual may be served by HYNIX Semiconductor offices in Korea or Distributors and Representatives listed at address directory.

HYNIX Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, HYNIX Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

| 1. OVERVIEW                          | . 1 | 13.2 Watchdog timer overflow               | . 37     |

|--------------------------------------|-----|--------------------------------------------|----------|

| 1.1 Description                      |     | 13.3 Low VDD voltage reset                 | . 37     |

| 1.2 Features                         |     | 14. WATCHDOG TIMER                         | 38       |

| 2. BLOCK DIAGRAM                     |     | 15. TIMER                                  |          |

| 3. PIN ASSIGNMENT                    |     | 15.1 Timer0 and Timer1                     |          |

| 3.1 40PDIP pinning                   |     | 15.2 TIMER2                                |          |

| 3.2 42SDIP pinning                   |     | 16. DDC INTERFACE                          |          |

| 4. PACKAGE DIMENSIONS                |     | 16.1 The SFRs for DDC Interface            |          |

| 4.1 40 PDIP                          |     | 16.2 DDC1 protocol                         |          |

| 4.2 42 SDIP                          |     | 16.3 DDC2B protocol                        |          |

| 5. PIN FUNCTION                      |     | 16.4 DDC2AB/DDC2B+ protocol                |          |

| 5.1 40DIP Pin Description            |     | 16.5 The RAM Buffer and DDC application    |          |

| 5.2 42SDIP Pin Description           |     | 17. I2C INTERFACE                          |          |

| 6. PORT STRUCTURES                   |     | 17.1 The SFRs for I2C Interface            |          |

|                                      |     | 17.2 Programmer's Guide for I2C and DDC2   |          |

| 7. ELECTRICAL CHARACTERISTICS        |     | 18. PULSE WIDTH MODULATION                 |          |

| 7.1 Absolute Maximum Ratings         |     | 18.1 Static PWM                            |          |

| 7.2 Recommended Operating Conditions |     | 18.2 Dynamic PWM                           |          |

| 7.3 DC Electrical Characteristics    |     | 19. SYNC PROCESSOR                         |          |

| 7.4 AC Characteristics               |     | 19.1 Sync input signals                    |          |

| 8. MEMORY ORGANIZATION               |     | 19.2 Horizontal polarity correction        |          |

| 8.1 Registers                        |     | 19.3 Vertical polarity correction          |          |

| 8.2 Program Memory                   |     | 19.4 Vertical sync separation              |          |

| 8.3 Data memory                      |     | 19.5 Horizontal sync. detection            |          |

| 8.4 List of SFRS                     |     | 19.6 Vertical sync. detection              |          |

| 8.5 Addressing Mode                  |     | 19.7 Horizontal sync. generator            |          |

| 9. INTERRUPTS                        |     | 19.8 Vertical sync. generator              |          |

| 9.1 Interrupt sources                |     | 19.9 HSYNC / VSYNC output driver           |          |

| 9.2 Interrupt Enable structure       |     | 19.10 Clamp pulse generator                |          |

| 9.3 Interrupt Priority structure     |     | 19.11 Pattern generator                    |          |

| 9.4 How Interrupt are handled        |     | 19.12 Suspend mode                         |          |

| 10. POWER-SAVING MODE                |     | 20. AD-CONVERTOR (ADC)                     |          |

| 10.1 Power control register          |     | 21. OPERATION MODE                         |          |

| 10.2 Idle mode                       |     | 21.1 OTP MODE                              |          |

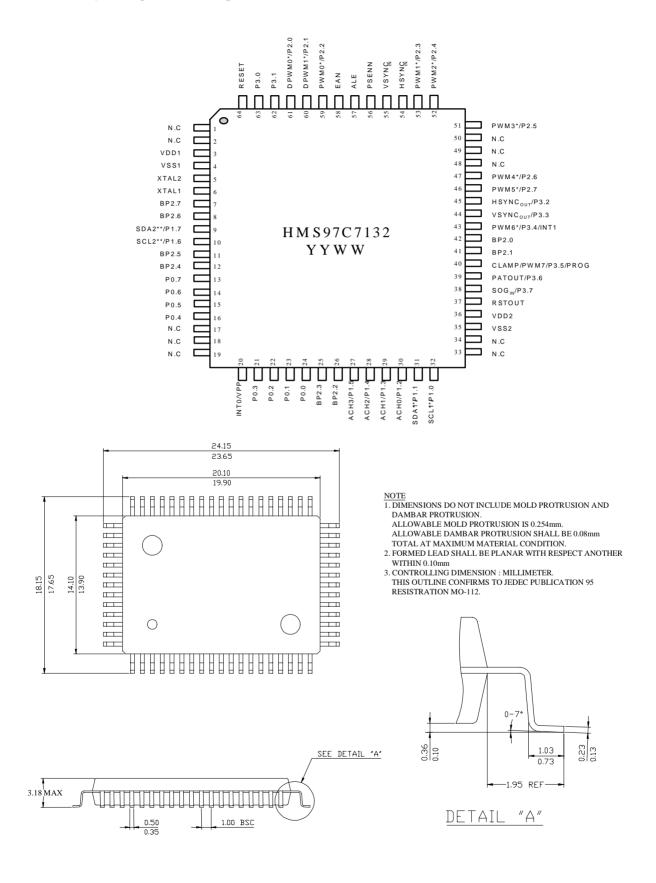

| 10.3 Power-down mode                 |     | 21.2 64MQFP pinning and Package Dimensions |          |

| 11. I/O PORTS                        |     | 21.3 64MQFP Pin Description                |          |

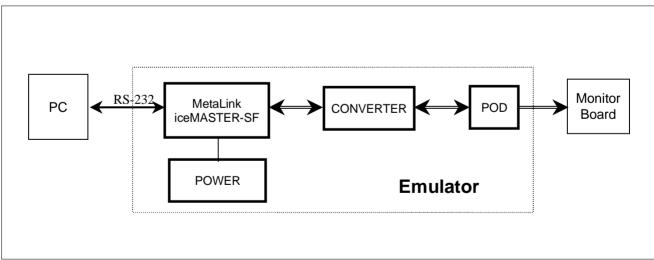

| 11.1 Pin function selection          |     | 21.4 Development Tools                     |          |

| 12. OSCIALLTOR                       |     | 22. INSTRUCTION SET                        |          |

| 13. RESET                            | 37  | 22. 110 1100 11011 021                     | <u>ر</u> |

| 12.1 External reset                  |     |                                            |          |

ициіх

# HMS9xC7132 / HMS9xC7134

# CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER FOR MONITOR

#### 1. OVERVIEW

# 1.1 Description

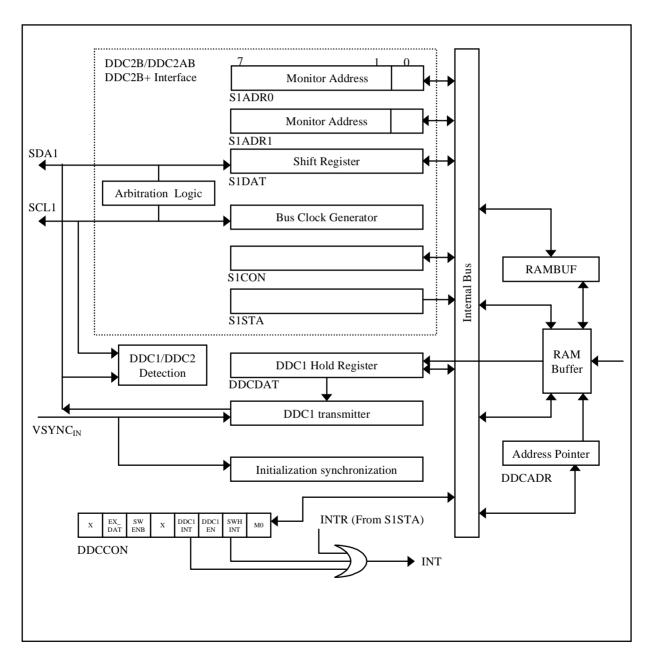

The HMS9xC7132/4 is a single-chip microcontroller of the 80C51 family, which is dedicated for monitor application. It is particularly suitable for multi-sync computer monitor controller. This contains DDC interfaces to the PC host, sync-detector and sync-processor for auto-sync application, ADC, static PWM, dynamic PWM and  $I^2C$  bus interface for control of the video and deflection functions of the monitor.

| Device name  | ROM Size              | RAM<br>Size | I/O                     | ОТР          | Package                                       |

|--------------|-----------------------|-------------|-------------------------|--------------|-----------------------------------------------|

| HMS91C7132/4 | 32K bytes<br>Mask ROM | 512 bytes   | 30(42DIP)<br>32(42SDIP) | HMS97C7132/4 | 40DIP(HMS91C7132/4),<br>42SDIP(HMS91C7132/4K) |

#### 1.2 Features

- 80C51 core

- 32K bytes of ROM for HMS91C7132/4

(32K bytes of OTP ROM for HMS97C7132/4)

- 256 bytes of RAM and 256 bytes of XRAM for DDC operation

- · Uses an external crystal of 12 MHz

- One DDC compliant interface :

- Fully supports DDC1 with dedicated hardware

- DDC2B, DDC2AB and DDC2B+ compliant dedicated hardware based on an I<sup>2</sup>C bus interface

- RAM buffer with programmable size, 128 bytes or 256 bytes, which can be used for DDC operation or shared as system RAM

- On-chip sync processor

- HSYNC frequency with 12-bit resolution

- VSYNC frequency with 12-bit resolution

- HSYNC and VSYNC polarity

- HSYNC and VSYNC presence detection

- Composite sync separation

- Free running sync. generation

- Clamping pulse output

- Pattern generation

- Separate input for a SOG signal

- Missing pulse insertion option

- HSYNC/ VSYNC change interrupt

- One multi-master/slave I2C interface (up to 400K bit/s) for control of other system IC's

- Eight 8-bit Static PWM outputs for digital control applications

- Two 8-bit Dynamic PWM outputs for various waveform generation

- One 8-bit ADC with 4 input channels

- LED driver port; two port lines with

15 mA drive capability

- One 8-bit port only for I/O function

- 24 derivative I/O ports configurable for alternative functions

- Watchdog timer (524ms max.)

- On-chip low VDD voltage detect and reset (reset period: 524ms)

- Operating temperature : 0 °C to 70 °C

- Special idle and power-down modes with low power consumption

- Single power supply: 4.5V to 5.5V

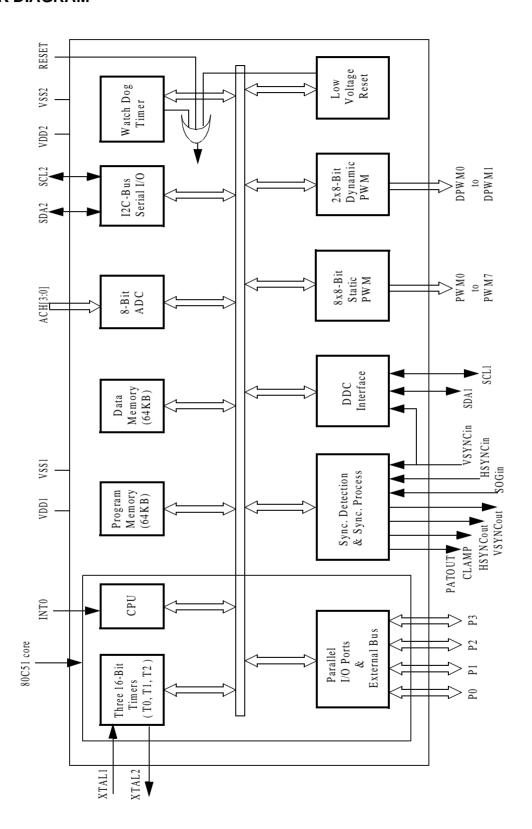

# 2. BLOCK DIAGRAM

# 3. PIN ASSIGNMENT

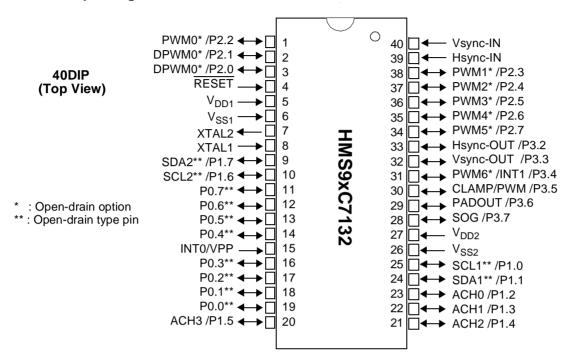

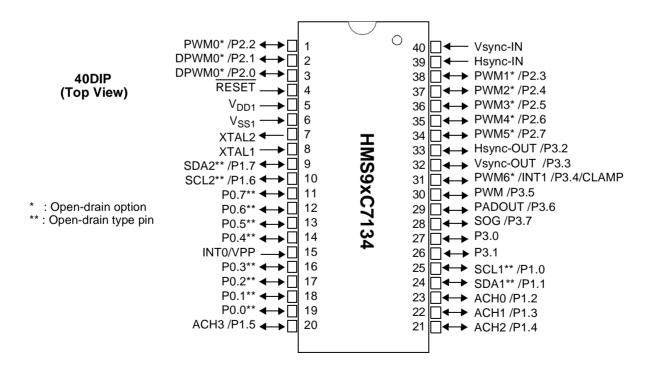

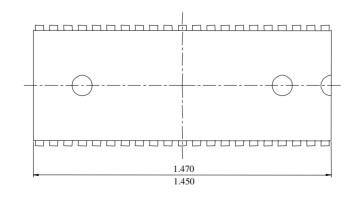

#### 3.1 40PDIP pinning

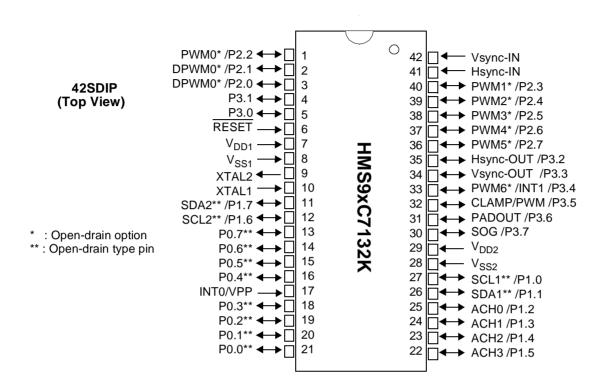

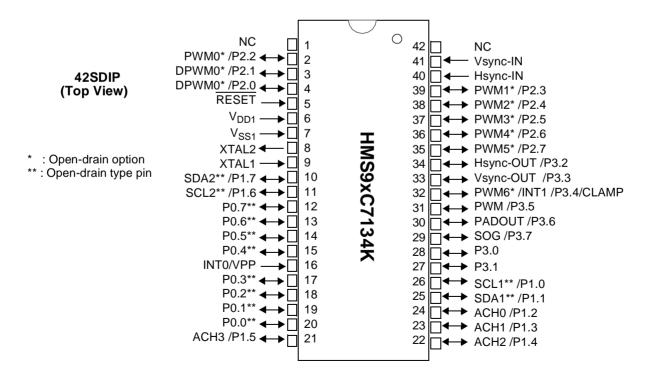

# 3.2 42SDIP pinning

# 4. PACKAGE DIMENSIONS

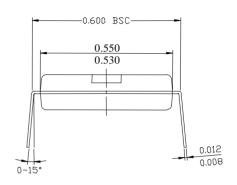

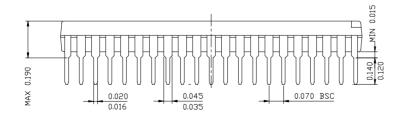

# 4.1 40 PDIP

# NOTE 1. DIMENSIONS DO NOT INCLUDE MOLD FLASH AND DAMBAR PROTRUSION. ALLOWABLE MOLD FLASH IS 0.010 INCH. 2. CONTROLLING DIMENSION: INCH.

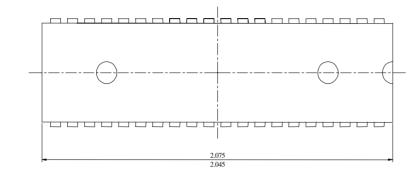

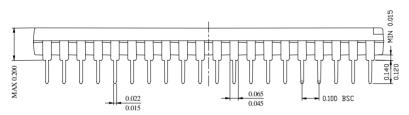

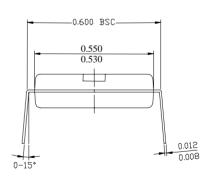

# 4.2 42 SDIP

NOTE

1. DIMENSIONS DO NOT INCLUDE MOLD

FLASH AND DAMBAR PROTRUSION.

ALLOWABLE MOLD FLASH IS 0.010 INCH.

2. CONTROLLING DIMENSION: INCH.

# 5. PIN FUNCTION

$V_{DD1}$ : Supply voltage (Digital).

V<sub>SS1</sub>: Circuit ground (Digital).

V<sub>DD2</sub>: Supply voltage (Analog).

V<sub>SS2</sub>: Circuit ground (Analog).

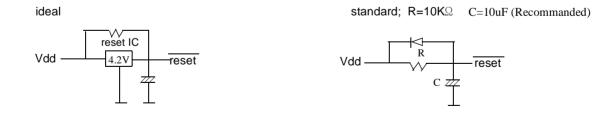

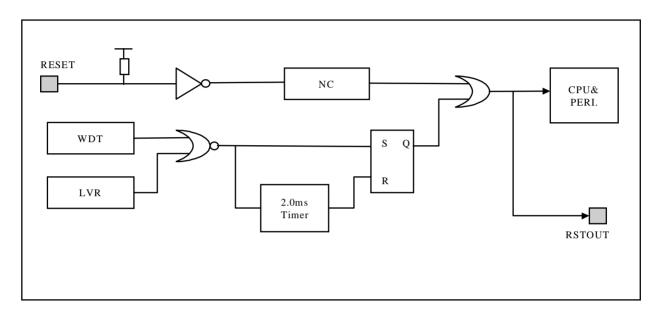

**RESET**: Reset the MCU.

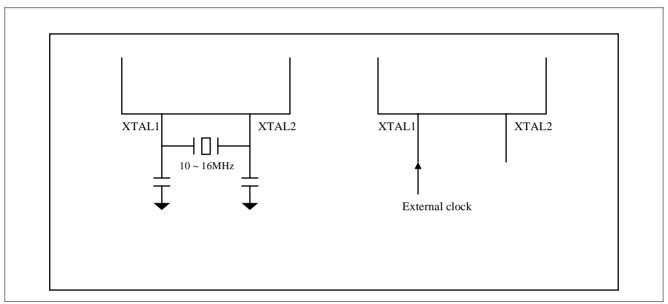

**XTAL1**: Input to the inverting oscillator amplifier and input to the internal main clock operating circuit.

**XTAL2**: Output from the inverting oscillator amplifier.

HSYNC<sub>IN</sub>: Horizontal sync input VSYNC<sub>IN</sub>: Vertical sync input

INT0/V<sub>PP</sub>: External Interrupt input. Programming supply voltage(during OTP programming)

#### PORT:

The HMS9xC7132 has four 8-bit ports (Port0, Port1, Port2, and Port3). Port0 - Port3 are the same as in the 80C51, with the exception of the additional functions of Port1, Port2 and Port3. Each has latch, SFR P0~P3' output driver and input buffer.

**P0.0~P0.7**: P0 is an 8-bit CMOS bidirectional I/O port. P0 pins have not pull-up resister and open-drain port. It has the capability of drive LED. However, while the alternative function is performed, the port type will remain the same. In case of application to extention of external memory, P0 outputted Write/Read byte and lower byte of external memory address. Therefore when it is used as normal I/O port, P0 is open-drain driver and when it used as bus port, P0 is 3-state driver.

| Port pin | Alternate function         |

|----------|----------------------------|

| P0.0     | No (Only for I/O function) |

| P0.1     | No (Only for I/O function) |

| P0.2     | No (Only for I/O function) |

| P0.3     | No (Only for I/O function) |

| P0.4     | No (Only for I/O function) |

| P0.5     | No (Only for I/O function) |

| P0.6     | No (Only for I/O function) |

| P0.7     | No (Only for I/O function) |

**P1.0~P1.7**: P1 is an 8-bit CMOS bidirectional I/O port. Because P1 pins have pull-up resister, it is called as Quasi-Bidirectional port.

| Port pin | Alternate function          |

|----------|-----------------------------|

| P1.0     | SCL1 (DDC-SCL)              |

| P1.1     | SDA1 (DDC-SDA)              |

| P1.2     | ACH0                        |

| P1.3     | ACH1                        |

| P1.4     | ACH2                        |

| P1.5     | ACH3                        |

| P1.6     | SCL2 (I <sup>2</sup> C-SCL) |

| P1.7     | SDA2 (I <sup>2</sup> C-SDA) |

**P2.0~P2.7**: P2 is an 8-bit CMOS bidirectional I/O port. Because P2 pins have pull-up resister, it is called as Quasi-Bidirectional port. .

| Port pin | Alternate function |

|----------|--------------------|

| P2.0     | DPWM0*             |

| P2.1     | DPWM1*             |

| P2.2     | PWM0*              |

| P2.3     | PWM1*              |

| P2.4     | PWM2*              |

| P2.5     | PWM3*              |

| P2.6     | PWM4*              |

| P2.7     | PWM5*              |

**P3.0~P3.7**: P3 is an 8-bit CMOS bidirectional I/O port. Because P3 pins have pull-up resister, it is called as Quasi-Bidirectional port.

| Port pin | Alternate function   |

|----------|----------------------|

| P3.0     | Reserved             |

| P3.1     | Reserved             |

| P3.2     | HSYNC <sub>OUT</sub> |

| P3.3     | VSYNC <sub>OUT</sub> |

| P3.4     | PWM6*                |

| P3.5     | CLAMP/PWM7           |

| P3.6     | PATOUT               |

| P3.7     | SOG                  |

# 5.1 40DIP Pin Description

| PIN NAME                    | Pin | In/Out           |                                                                           | Function                                                        |

|-----------------------------|-----|------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|

| (Alternate)                 | No. | (Alter-<br>nate) | Basic                                                                     | Alternate                                                       |

| PWM0 /P2.2                  | 1   | I/O              | General I/O port P2.2                                                     | 8-bit Pulse Width Modulation output0                            |

| DPWM0 /P2.1                 | 2   | I/O              | General I/O port P2.1                                                     | 8-bit Dynamic Pulse Width Modulation output0                    |

| DPWM0 /P2.0                 | 3   | I/O              | General I/O port P2.0                                                     | 8-bit Dynamic Pulse Width Modulation output1                    |

| RESET                       | 4   | I                | Reset input                                                               |                                                                 |

| V <sub>DD1</sub>            | 5   | -                | Power supply1(+5V)                                                        |                                                                 |

| V <sub>SS1</sub>            | 6   | -                | Ground1                                                                   |                                                                 |

| XTAL2                       | 7   | 0                | Oscillator output pin for system clock                                    |                                                                 |

| XTAL1                       | 8   | I                | Oscillator input pin for system clock                                     |                                                                 |

| SDA2 /P1.7                  | 9   | I/O              | General I/O port P1.7                                                     | I <sup>2</sup> C serial data I/O port                           |

| SCL2 /P1.6                  | 10  | I/O              | General I/O port P1.6                                                     | I <sup>2</sup> C serial clock I/O port                          |

| P0.7                        | 11  | I/O              | General I/O port P0.7; adapted for LE                                     | D driver                                                        |

| P0.6                        | 12  | I/O              | General I/O port P1.6; adapted for LE                                     | D driver                                                        |

| P0.5                        | 13  | I/O              | General I/O port P0.5                                                     |                                                                 |

| P0.4                        | 14  | I/O              | General I/O port P0.4                                                     |                                                                 |

| INT0 /V <sub>PP</sub>       | 15  | ı                | External interrupt input0; Programmin                                     | g supply voltage (during OTP programming)                       |

| P0.3                        | 16  | I/O              | General I/O port P0.3                                                     |                                                                 |

| P0.2                        | 17  | I/O              | General I/O port P0.2                                                     |                                                                 |

| P0.1                        | 18  | I/O              | General I/O port P0.1                                                     |                                                                 |

| P0.0                        | 19  | I/O              | General I/O port P0.0                                                     |                                                                 |

| ACH3 /P1.5                  | 20  | I/O              | General I/O port P1.5                                                     | ADC channel3 input                                              |

| ACH2 /P1.4                  | 21  | I/O              | General I/O port P1.4                                                     | ADC channel2 input                                              |

| ACH0 /P1.3                  | 22  | I/O              | General I/O port P1.3                                                     | ADC channel1 input                                              |

| ACH0 /P1.2                  | 23  | I/O              | General I/O port P1.2                                                     | ADC channel0 input                                              |

| SDA1 /P1.1                  | 24  | I/O              | General I/O port P1.1                                                     | I <sup>2</sup> C serial data I/O port for DDC interface         |

| SCL1 /P1.0                  | 25  | I/O              | General I/O port P1.0                                                     | I <sup>2</sup> C serial clock I/O port for DDC interface        |

| V <sub>SS2</sub>            | 26  | -                | Ground2                                                                   |                                                                 |

| $V_{DD2}$                   | 27  | -                | Power supply2(+5V)                                                        |                                                                 |

| SOGin /P3.7                 | 28  | I/O              | General I/O port P3.7                                                     | Sync on Green input                                             |

| PATOUT /P3.7                | 29  | I/O              | General I/O port P3.6                                                     | Pattern out                                                     |

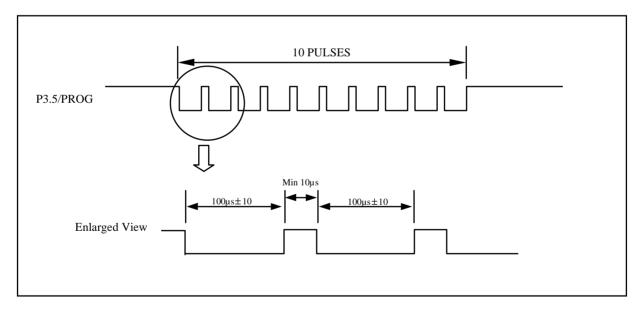

| CLAMP /PWM7 /<br>P3.5 /PROG | 30  | I/O              | General output only port P3.5 Program pulse input(during OTP programming) | Clamp out ; 8-bit Pulse Width Modulation output7                |

| PWM6 /P3.4 /<br>INT1        | 31  | I/O              | General I/O port P3.4                                                     | 8-bit Pulse Width Modulation output6; External interrupt input1 |

| VSYNCout /P3.3              | 32  | I/O              | General I/O port P3.3                                                     | Vertical sync output                                            |

| HSYNCout /P3.2              | 33  | I/O              | General I/O port P3.2                                                     | Horizontal sync output                                          |

| PWM5 /P2.7                  | 34  | I/O              | General I/O port P2.7                                                     | 8-bit Pulse Width Modulation output5                            |

| PWM4 /P2.6                  | 35  | I/O              | General I/O port P2.6                                                     | 8-bit Pulse Width Modulation output4                            |

| PWM3 /P2.5                  | 36  | I/O              | General I/O port P2.5                                                     | 8-bit Pulse Width Modulation output3                            |

| PWM2 /P2.4                  | 37  | I/O              | General I/O port P2.4                                                     | 8-bit Pulse Width Modulation output2                            |

Table 5-1 Port Function Description(40DIP)

| PIN NAME    | Pin | In/Out           | Function              |                                      |  |  |  |

|-------------|-----|------------------|-----------------------|--------------------------------------|--|--|--|

| (Alternate) | No. | (Alter-<br>nate) | Basic                 | Alternate                            |  |  |  |

| PWM1 /P2.3  | 38  | I/O              | General I/O port P2.3 | 8-bit Pulse Width Modulation output1 |  |  |  |

| HSYNCin     | 39  | I                | Horizontal sync input |                                      |  |  |  |

| VSYNCin     | 40  | I                | Vertical sync input   |                                      |  |  |  |

**Table 5-1 Port Function Description(40DIP)**

# 5.2 42SDIP Pin Description

The 42SDIP type pin description is the same as The 40DIP type pin description except for adding two pins(P3.1, P3.0) to it between pin no.4 and 5.

# ициіх

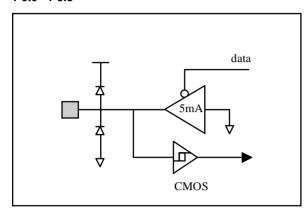

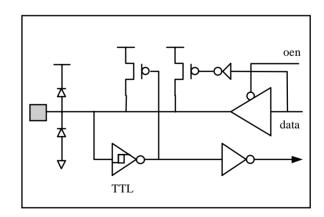

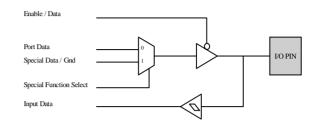

# **6. PORT STRUCTURES**

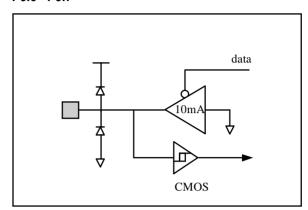

P0.0 - P0.5

P0.6 - P0.7

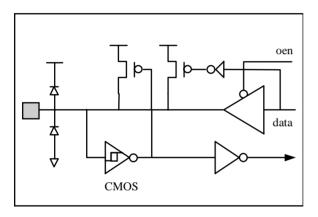

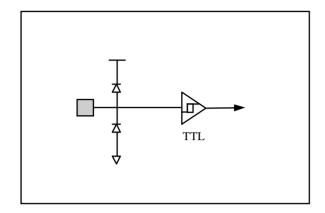

P1.0, P1.1, P1.6, P1.7, P2.0~7, P3.0, P3.1, P3.4, P3.6

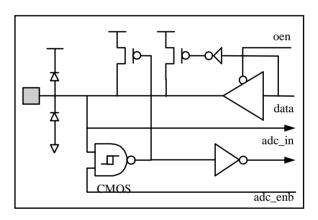

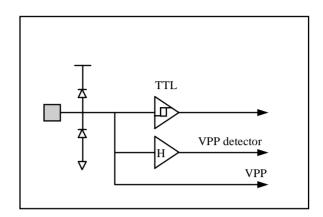

P1.2 - P1.5

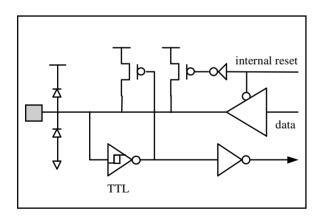

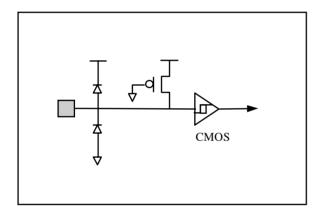

P3.2, P3.3, P3.5

P3.7

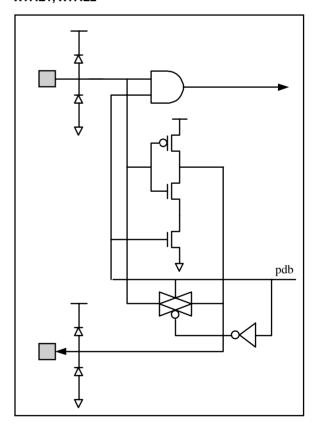

# HSYNCIN, VSYNCIN

# INTO/VPP

# RESET

# XTAL1, XTAL2

# 7. ELECTRICAL CHARACTERISTICS

# 7.1 Absolute Maximum Ratings

Supply voltage .....-0.5 to +6.5 V Storage Temperature ....-65 to +150 °C Voltage on any pin with respect to Ground (VSS) ....-0.5 to VDD+0.5

Note: Stresses above those listed under "Absolute Maxi-

mum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 7.2 Recommended Operating Conditions

| Parameter             | Symbol           | Condition                 | Specifi | cations | Unit |  |

|-----------------------|------------------|---------------------------|---------|---------|------|--|

|                       | Syllibol         | Condition                 | Min.    | Max.    | Oill |  |

| Supply Voltage        | V <sub>DD</sub>  | f <sub>XIN</sub> =12MHz   | 4.5     | 5.5     | V    |  |

| Operating Frequency   | f <sub>XIN</sub> | V <sub>DD</sub> =4.5~5.5V | 10      | 16      | MHz  |  |

| Operating Temperature | T <sub>OPR</sub> | -                         | 0       | 70      | °C   |  |

# 7.3 DC Electrical Characteristics

$(T_A = 0 \sim 70^{\circ}C, V_{DD} = 4.5 \sim 5.5V, V_{SS} = 0V),$

| 0         | D                              | O a malitia m | Sp      | ecificatio | ns      |      |

|-----------|--------------------------------|---------------|---------|------------|---------|------|

| Symbol    | Parameter                      | Condition     | Min.    | Тур.       | Max.    | Unit |

| SUPPLY    |                                |               | '       |            | 1       |      |

| VDD       | power supply voltage           | -             | 4.5     | 5.0        | 5.5     | V    |

| IDD       | power supply current           | Fosc - 12MHz  | -       | TBD        | -       | mA   |

| VLVR      | low voltage reset              | -             | 3.3     | 3.7        | 4.1     | V    |

| OTP SUPF  | PLY                            |               |         |            | '       |      |

| VDD       | power supply voltage           | -             | 4.5     | 5.0        | 5.5     | V    |

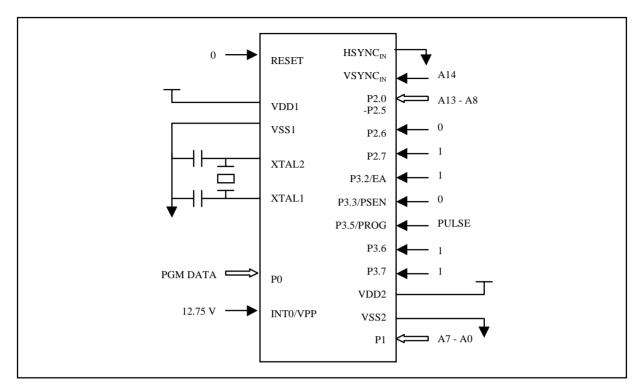

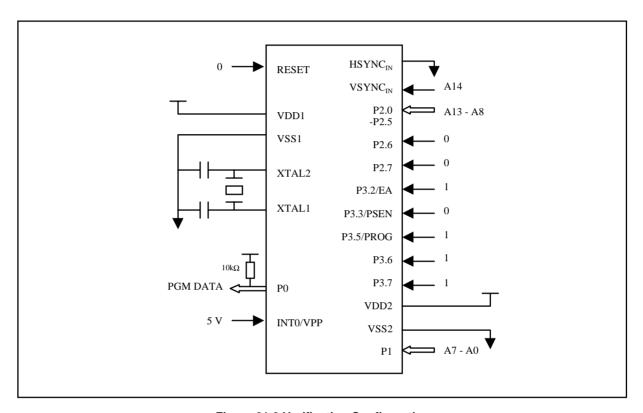

| VPP       | programming voltage            | -             | -       | 12.75      | -       | V    |

| IDDP      | power supply current           | Fosc - 4MHz   | -       | TBD        | -       | mA   |

| IPP       | programming current            | Fosc - 4MHz   | -       | TBD        | -       | mA   |

| RESET     |                                |               |         |            | -       |      |

| IRST      | RESET input pull-up resistance | VIN - 0V      | -       | 33         | -       | μΑ   |

| IIH       | input leakage current          | VIN - VDD     | -       | 0          | 1       | μΑ   |

| VIL1      | LOW-level input voltage        | -             | VSS-0.5 | -          | 0.3VDD  | V    |

| VIH1      | HIGH-level input voltage       | -             | 0.7VDD  | -          | VDD+0.5 | V    |

| XTAL      |                                |               | '       |            | -       |      |

| VOP       | open bias voltage              | -             | -       | 2.5        | -       | V    |

| IFR       | feedback resistor current      | VIN - 5V      | -       | 10         | -       | μΑ   |

| VIL1      | LOW-level input voltage        | -             | VSS-0.5 | -          | 0.3VDD  | V    |

| VIH1      | HIGH-level input voltage       | -             | 0.7VDD  | -          | VDD+0.5 | V    |

| INT0, HSY | NCIN, VSYNCIN                  |               | '       |            | 1       |      |

| IIL       | input leakage current          | VIN - VSS     | -1      | 0          | -       | μΑ   |

| IIH       | input leakage current          | VIN - VDD     | -       | 0          | 1       | μΑ   |

| VIL       | LOW-level input voltage        | -             | VSS-0.5 | -          | 0.3VDD  | V    |

| Cumbal      | Poromotor                   | Condition   | Specifications |      |         | 1114        |

|-------------|-----------------------------|-------------|----------------|------|---------|-------------|

| Symbol      | Parameter                   | Condition   | Min.           | Тур. | Max.    | Unit        |

| VIH         | HIGH-level input voltage    | -           | 2.0            | -    | VDD+0.5 | V           |

| SOG/P3.7    |                             |             |                |      |         |             |

| IIL1        | input leakage current       | VIN - 0.45V | -55            | -    | -10     | μΑ          |

| ITL         | input transition current    | VIN - 2.0V  | -650           | -    | -65     | μΑ          |

| IIH         | input leakage current       | VIN - VDD   | -              | 0    | 1       | μΑ          |

| VIL         | LOW-level input voltage     | -           | VSS-0.5        | -    | 0.8     | V           |

| VIH         | HIGH-level input voltage    | -           | 2.0            | -    | VDD+0.5 | V           |

| VOL         | LOW-level output voltage    | IOL - 5mA   | 0              | -    | 0.4     | V           |

| VOH         | HIGH-level input voltage    | IOH - 5mA   | 3.5            | -    | VDD     | V           |

| P0.0 to P0. | .5                          |             | <u> </u>       |      |         |             |

| IIL         | input leakage current       | VIN - VSS   | -1             | 0    | -       | μΑ          |

| IIH         | input leakage current       | VIN - VDD   | -              | 0    | 1       | μΑ          |

| VIL1        | LOW-level input voltage     | -           | VSS-0.5        | -    | 0.3VDD  | V           |

| VIH1        | HIGH-level input voltage    | -           | 0.7VDD         | -    | VDD+0.5 | V           |

| VOL         | LOW-level output voltage    | IOL - 5mA   | 0              | -    | 0.4     | V           |

| P0.6 to P0. | .7                          | -           |                |      |         |             |

| IIL         | input leakage current       | VIN - VSS   | -1             | 0    | -       | μΑ          |

| IIH         | input leakage current       | VIN - VDD   | -              | 0    | 1       | μΑ          |

| VIL1        | LOW-level input voltage     | -           | VSS-0.5        | -    | 0.3VDD  | V           |

| VIH1        | HIGH-level input voltage    | -           | 0.7VDD         | -    | VDD+0.5 | V           |

| VOL1        | LOW-level output voltage    | IOL - 10mA  | 0              | -    | 0.4     | V           |

| P2.0 to P2. | .7(BP2.0 to BP2.7)          |             |                |      |         |             |

| IIL1        | input leakage current       | VIN - 0.45V | -55            | -    | -10     | μΑ          |

| ITL1        | input transition current    | VIN - 3.5V  | -650           | -    | -65     | <u>.</u> μΑ |

| IIH         | input leakage current       | VIN - VDD   | -              | 0    | 1       | μΑ          |

| VIL1        | LOW-level input voltage     | -           | VSS-0.5        | -    | 0.3VDD  | V           |

| VIH1        | HIGH-level input voltage    | -           | 0.7VDD         | -    | VDD+0.5 | V           |

| VOL         | LOW-level output voltage    | IOL - 5mA   | 0              | -    | 0.4     | V           |

| VOH         | HIGH-level input voltage    | IOH - 5mA   | 3.5            | -    | VDD     | V           |

| P1.0 to P1. | .7,P3.0,P3.1,P3.4,P3.6,P3.7 |             |                |      |         |             |

| IIL1        | input leakage current       | VIN - 0.45V | -55            | -    | -10     | μΑ          |

| ITL1        | input transition current    | VIN - 3.5V  | -650           | -    | -65     | μΑ          |

| IIH         | input leakage current       | VIN - VDD   | -              | 0    | 1       | μA          |

| VIL1        | LOW-level input voltage     | -           | VSS-0.5        | -    | 0.3VDD  | V           |

| VIH1        | HIGH-level input voltage    | -           | 0.7VDD         | -    | VDD+0.5 | V           |

| VOL         | LOW-level output voltage    | IOL - 5mA   | 0              | -    | 0.4     | V           |

| VOH         | HIGH-level input voltage    | IOH - 5mA   | 3.5            | -    | VDD     | V           |

| P3.2 to P3. | •                           |             | I              |      | 1       |             |

| IIL2        | input leakage current       | VIN - 0.45V | -960           |      | -320    | μΑ          |

| ITL2        | input transition current    | VIN - 2.0V  | -1240          |      | -350    | μΑ          |

| IIH         | input leakage current       | VIN - VDD   |                | 0    | 1       | μΑ          |

| VIL         | LOW-level input voltage     | -           | VSS-0.5        |      | 0.8     | V           |

| VIH         | HIGH-level input voltage    | -           | 2.0            |      | VDD+0.5 | V           |

| Symbol | Parameter                | Condition | S    | Unit |      |       |

|--------|--------------------------|-----------|------|------|------|-------|

|        | raiametei                | Condition | Min. | Тур. | Max. | Oilit |

| VOL    | LOW-level output voltage | IOL - 5mA | 0    |      | 0.4  | V     |

| VOH    | HIGH-level input voltage | IOH - 5mA | 3.5  |      | VDD  | V     |

# 7.4 AC Characteristics

$(T_A = -0 \sim 70^{\circ}C, V_{DD} = 5.0V, V_{SS} = 0V)$

| Symbol                | Parameter                      | Condition    | S        | Unit |      |                   |

|-----------------------|--------------------------------|--------------|----------|------|------|-------------------|

| Symbol                | Parameter                      | Condition    | Min.     | Тур. | Max. | Unit              |

| XTAL                  |                                |              | <u>'</u> |      | 1    |                   |

| fosc                  | oscillator frequency           | VDD - 5V     | 10       | 12   | 16   | MHz               |

| C1                    | xtal1 external Cap.            | -            | -        | 20   | -    | pF                |

| C2                    | xtal2 external Cap.            | -            | -        | 20   | -    | pF                |

| A/D Converte          | r                              | 1            |          |      |      |                   |

| V <sub>AIN</sub>      | analog input voltage           | -            | VSS      | -    | VDD  | V                 |

| n <sub>AOFF</sub>     | zero offset error              | -            | -        | -    | TBD  | LSB               |

| $n_{FS}$              | full scale error               | -            | -        | 20   | TBD  | LSB               |

| n <sub>ACC</sub>      | overall accuracy               | -            | -        | -    | TBD  | LSB               |

| t <sub>CONV</sub>     | conversion time                | fosc - 12MHz | -        | 13   | -    | μS                |

| DDC1 Mode             |                                |              | <u> </u> |      | 1    |                   |

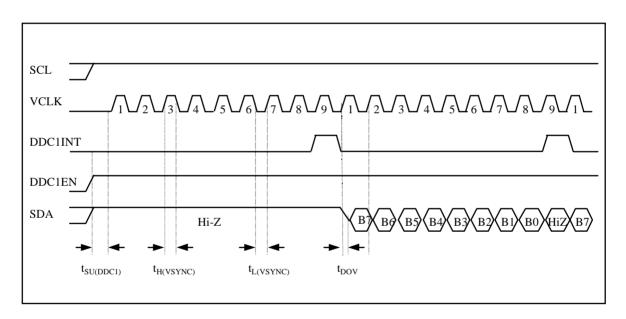

| t <sub>H(VCLK)</sub>  | VCLK high time                 | -            | 20       | -    | -    | μsV               |

| t <sub>L(VCLK)</sub>  | VCLK low time                  | -            | 20       | -    | -    | μS                |

| t <sub>DOV</sub>      | VCLK to output valid           | fosc - 12MHz | -        |      | 680  | μs                |

| t <sub>SU(DDC1)</sub> | DDC1 mode setup time           | -            | -        | TBD  | -    | μs                |

| t <sub>NC(IN)</sub>   | cancelled noise input          | fosc - 12MHz | -        | -    | 300  | μs                |

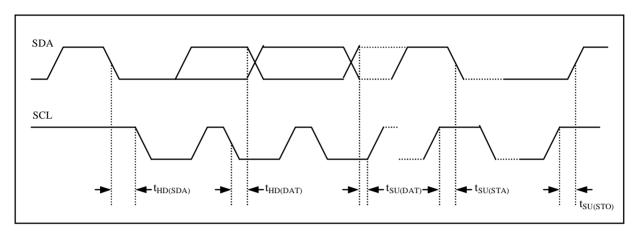

| DDC2 Mode             |                                |              | <u> </u> |      |      | .1                |

| f <sub>SCL</sub>      | SCL clock frequency            | -            | 0        | -    | 100  | kHz               |

| t <sub>HD(SDA)</sub>  | Start condition hold time      | -            | 4.0      | -    | -    | μs                |

| t <sub>SU(STO)</sub>  | Stop condition setup time      | -            | 4.0      | -    | -    | μs                |

| t <sub>HD(DAT)</sub>  | Data hold time                 | -            | 300      | -    | -    | μs                |

| t <sub>SU(STA)</sub>  | Rstart(1) condition setup time | -            | 4.7      | -    | -    | μs                |

| t <sub>H(SCL)</sub>   | SCL high period                | -            | 4.0      | -    | -    | μs                |

| t <sub>L(SCL)</sub>   | SCL low period                 | -            | 4.7      | -    | -    | μs                |

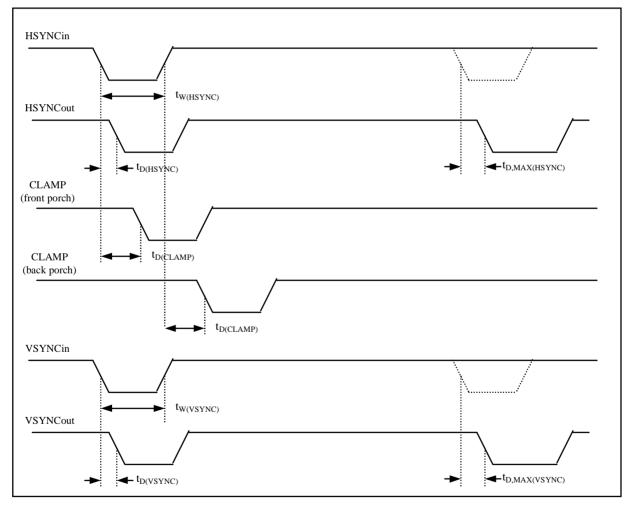

| HSYNCin               |                                |              |          |      |      |                   |

| f <sub>(HSYNC)</sub>  | HSYNC input frequency          | -            | 12       | -    | 120  | kHz               |

| t <sub>W(HSYNC)</sub> | HSYNC input pulse width        | -            | 0.25     | -    | 8    | μs                |

| d <sub>(HSYNC)</sub>  | HSYNC duty cycle               | -            | -        | -    | 25   | %                 |

| VSYNCin               |                                | 1            |          | 1    | 1    | 1                 |

| f <sub>(VSYNC)</sub>  | VSYNC input frequency          | -            | 32       | -    | 200  | Hz                |

| t <sub>W(VSYNC)</sub> | VSYNC input pulse width        | -            | 1        | -    | 24   | t <sub>P(H)</sub> |

| d <sub>(VSYNC)</sub>  | VSYNC duty cycle               | -            | -        | -    | 25   | %                 |

| SOGin                 | , ,                            | 1            |          | 1    |      | 1                 |

| Symbol                                                                | Parameter                                   | Condition | S    | pecificatio | ns   | Unit              |

|-----------------------------------------------------------------------|---------------------------------------------|-----------|------|-------------|------|-------------------|

| Symbol                                                                | Parameter                                   | Condition | Min. | Тур.        | Max. | Unit              |

| t <sub>P(EQ)</sub>                                                    | equalizing pulse period                     | -         | -    | 0.5         | -    | t <sub>P(H)</sub> |

| t <sub>W(EQ)</sub>                                                    | equalizing pulse width                      | -         | -    | 0.5         | -    | t <sub>W(H)</sub> |

| n <sub>(EQ)</sub>                                                     | equalizing pulse interval                   | -         | -    | -           | 30   | t <sub>P(H)</sub> |

| HSYNCout, VSYNCout                                                    |                                             |           |      |             |      |                   |

| t <sub>D(HSYNC)</sub>                                                 | HSYNC input to output                       | -         | -    | -           | 100  | ns                |

| t <sub>D,MAX(HSYNC)</sub>                                             | HSYNC input to output after missing HSYNCin | -         | -    | -           | 250  | ns                |

| t <sub>D(HSYNC)</sub>                                                 | VSYNC input to output                       | -         | -    | -           | 180  | ns                |

| t <sub>D,MAX(VSYNC)</sub> VSYNC input to output after missing VSYNCin |                                             | -         | -    | -           | 1    | t <sub>P(H)</sub> |

| t <sub>D(CLAMP)</sub>                                                 | HSYNCin to CLAMP                            | -         | -    | -           | 100  | ns                |

Figure 7-1 timing on the I2C-bus

Figure 7-2 SYNC timing

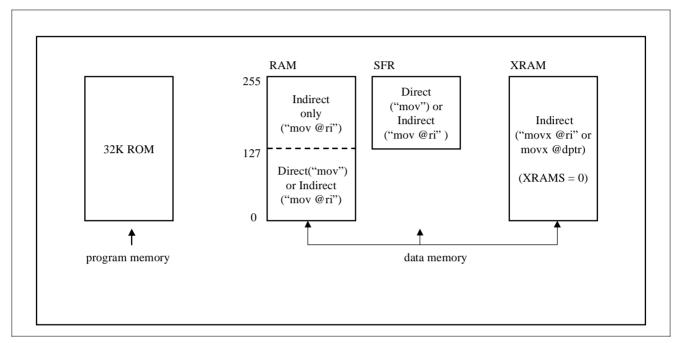

# 8. MEMORY ORGANIZATION

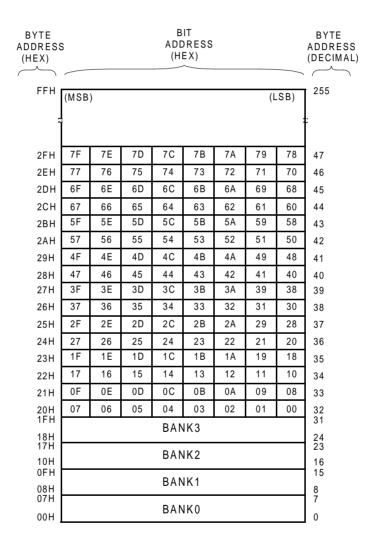

The HMS91C7132 has separate address spaces for Program memory, Data Memory. Program memory can only be read, not written to. It can be up to 32K bytes of Program memory.(OPT type: HMS97C7132 32K bytes)

Data memory can be read and written to up to 256 bytes including the stack area.(Internal RAM) and 256bytes (External RAM: 256bytes of XRAM0).

Figure 8-1 Memory map and address spaces

# 8.1 Registers

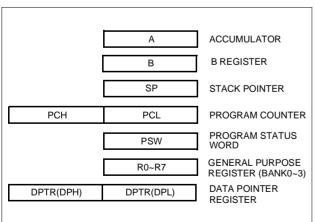

This device has several registers that are the Program Counter (PC), Accumulator (A), B register(B), the Stack Pointer (SP), the Program Status Word(PSW), General purpose register(R0~R7) and DPTR(Data pointer register).

Figure 8-2 Configuration of Registers

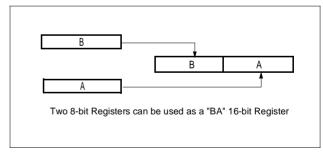

**Accumulator:** The Accumulator is the 8-bit general purpose register, used for data operation such as transfer, temporary saving,

and conditional judgement, etc. The Accumulator can be used as a 16-bit register with B Register as shown below.

Figure 8-3 Configuration of BA 16-bit Registers

**B Register:** The B Register is the 8-bit purpose register, used for an arithmatic operation such as multiply, division with Accumulator

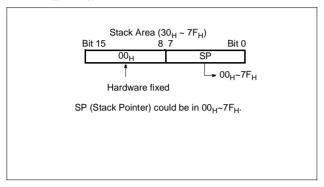

**Stack Pointer**: The Stack Pointer is an 8-bit register used for occurrence interrupts and calling out subroutines. Stack Pointer identifies the location in the stack to be access (save or restore). The stack can be located at any position within  $0000_{\rm H}$  to  $007F_{\rm H}$  of the internal data memory. The SP is not initialized by hardware, requiring to write the initial value (the location with

which the use of the stack starts) by using the initialization routine. Normally, the initial value of "07 $_{

m H}$ " is used and the stack area is  $00_{

m H}$  to 7F $_{

m H}$ .

**Program Counter:** The Program Counter is a 16-bit wide which consists of two 8-bit registers, PCH and PCL. This counter indicates the address of the next instruction to be executed. In reset state, the program counter has reset routine address ( $PC_H:0FF_H$ ,  $PC_L:0FE_H$ ).

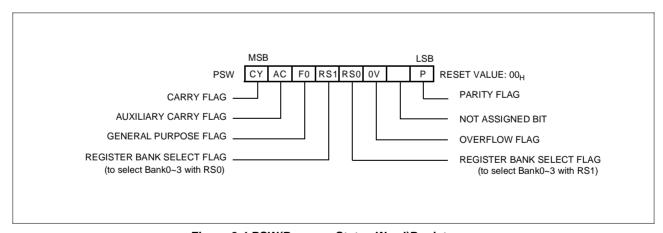

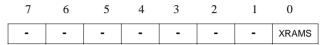

**Program Status Word**: The Program Status Word (PSW) contains several bits that reflect the current state of the CPU and select Internal RAM(00H~1FH:Bank0~Bank3). The PSW is described in Figure 8-4. It contains the Carry flag, the Auxiliary carry flag, the Half Carry (for BCD operation), the General purpose flag, the Register bank select flags, the Overflow flag, the undefined flag and Parity flag.

[Carry flag CY]

This flag stores any carry or not borrow from the ALU of CPU after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

#### [Auxiliary carry flag AC]

After operation, this is set when there is a carry from bit 3 of ALU or there is no borrow from bit 4 of ALU.

#### [Register bank select flags RS0, RS1]

This flags select one of four bank(00~07H:bank0, 08~0fH:bank1, 10~17H:bank2, 17~1FH:bank3)in Internal RAM.

#### [Overflow flag OV]

This flag is set to "1" when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds  $+127(7F_{\rm H})$  or  $-128(80_{\rm H})$ . The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, bit 6 of memory is copied to this flag.

#### [Parity flag P]

This flag reflect on number of Accumulator's 1. If number of Accumulator's 1 is odd, P=0. otherwise P=1. Sum of adding Accumulator's 1 to P is always even.

#### R0~R7: General purpose register.

**Data Pointer Register:**Data Pointer Register is 16-bit wide which consists of two-8bit registers, DPH and DPL. This register is used as a data pointer for the data transmission with external data memory.

Figure 8-4 PSW(Program Status Word)Register

#### 8.2 Program Memory

The program memory consists of ROM: 32K bytes (HMS91C7132) and 32K bytes (HMS97C7132)

#### 8.3 Data memory

The internal data memory is divided into four physically separated part: 256 bytes of RAM, 256 bytes of XRAM0, and 128 bytes of Special Function Registers (SFRs) areas.

#### **RAM**

Four register banks, each 8 registers wide, occupy locations 0 through 31 in the lower RAM area. Only one of these banks may be enabled at a time. The next 16 bytes, locations 32 through 47,

contain 128 directly addressable bit locations. The stack depth is only limited by the available internal RAM space of 256 bytes.

#### XRAM0

The 256 bytes of XRAM0 used to support DDC interface is also available for system usage by indirect addressing through the address pointer DDCADR and data I/O buffer RAMBUF. The address pointer(DDCADR) is equipped with the postincrement capability to facilitate the transfer of data in bulk (for details refer to DDC Interface part). However, it is also possible to address the DRAM through MOVX command as usually used in the internal

RAM extension of 80C51 derivatives. XRAM0 0 to 255 is directly addressable as external data memory locations 0 to 255 via MOVX-DPTR instruction or via MOVX-Ri instruction when the EXCON's LSB is zero. Since external access function is not available, any access to XRAM0 0 to 255 will not affect the ports.

Table 8-1 Extended control Register(EXCON)

Figure 8-5 RAM ADDRESS

# SFR

The SFRs can only be addressed directly in the address range from 128 to 255. Table 8.2 gives an overview of the Special Function Registers space. Sixteen address in the SFRs space are both-

byte and bit-addressable. The bit-addressable SFRs are those whose address ends in 0H and 8H. The bit addresses in this area are 80H to FFH.

| E8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F8 | -      | HVGEN   | CPGEN | VFH    | VFL    | HFH    | HFL    |        | FF |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|---------|-------|--------|--------|--------|--------|--------|----|

| E0         *ACC         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td>F0</td> <td>*B</td> <td>MDCON</td> <td>MDST</td> <td>VPH</td> <td>HPH</td> <td>VHPL</td> <td></td> <td></td> <td>F7</td> | F0 | *B     | MDCON   | MDST  | VPH    | HPH    | VHPL   |        |        | F7 |

| D8         *S1CON         S1STA         S1DAT         S1ADR0         S2CON         S2STA         S2DAT         S2ADR           D0         *PSW         S1SDR1         RAMBUF         DDCDAT         DDCADR         DDCCO           C8         *T2CON         -         RC2L         RC2H         -         -           C0         -         -         -         -         -           B8         *IP         -         -         -         -           B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                           | E8 | *EXCON |         |       |        |        | -      | -      | -      | EF |

| DO         *PSW         S1SDR1         RAMBUF         DDCDAT         DDCADR         DDCCO           C8         *T2CON         -         RC2L         RC2H         -         -           C0         -         -         -         -         -           B8         *IP         -         -         IPA         -           B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1         TH1                                                                                                                                                                                                                                                                                                            | E0 | *ACC   | -       | -     |        | -      | -      | -      | -      | E7 |

| C8         *T2CON         -         RC2L         RC2H         -         -           C0         -         -         -         -         -           B8         *IP         -         -         -         -           B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                              | D8 | *S1CON | S1STA   | S1DAT | S1ADR0 | S2CON  | S2STA  | S2DAT  | S2ADR  | DF |

| CO         -           B8         *IP         -           B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D0 | *PSW   |         |       | S1SDR1 | RAMBUF | DDCDAT | DDCADR | DDCCON | D7 |

| B8         *IP         -         -         IPA         -           B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C8 | *T2CON | -       | RC2L  | RC2H   | -      | -      |        |        | CF |

| B0         *P3         DPWMCON         DPWM0         DPWM1         -         IPA         -           A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C0 | -      |         |       |        |        |        | -      |        | C7 |

| A8         *IE         -         PWM4         PWM5         PWM6         PWM7         WDTKEY           A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td< td=""><td>В8</td><td>*IP</td><td>-</td><td></td><td></td><td></td><td></td><td></td><td></td><td>BF</td></td<>            | В8 | *IP    | -       |       |        |        |        |        |        | BF |

| A0         *P2         PWMCON         PWM0         PWM1         PWM2         PWM3         WDTRST         IEA           98         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                  | В0 | *P3    | DPWMCON | DPWM0 | DPWM1  |        | -      | IPA    | -      | В7 |

| 98         -         -           90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A8 | *IE    | -       | PWM4  | PWM5   | PWM6   | PWM7   | WDTKEY |        | AF |

| 90         *P1         P1SFS         P2SFS         P3SFS         ADAT         ACON           88         *TCON         TMOD         TL0         TL1         TH0         TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A0 | *P2    | PWMCON  | PWM0  | PWM1   | PWM2   | PWM3   | WDTRST | IEA    | A7 |

| 88 *TCON TMOD TL0 TL1 TH0 TH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 98 | -      | -       |       |        |        |        |        |        | 9F |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90 | *P1    | P1SFS   | P2SFS | P3SFS  |        |        | ADAT   | ACON   | 97 |

| 80         *P0         SP         DPL         DPH         PCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88 | *TCON  | TMOD    | TL0   | TL1    | TH0    | TH1    |        |        | 8F |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 80 | *P0    | SP      | DPL   | DPH    |        |        |        | PCON   | 87 |

Table 8-2 SFR Memory Map

Note: \* The register that can be bit-addressing.

# 8.4 List of SFRS

| Pogiatar | Description                               | Address | D/M |   | ı | nit | ial | Va | lue | • |   |

|----------|-------------------------------------------|---------|-----|---|---|-----|-----|----|-----|---|---|

| Register | Description                               | Address | R/W | 7 | 6 | 5   | 4   | 3  | 2   | 1 | 0 |

| P0       | Port0 Register                            | 80H     | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| SP       | Stack Point register                      | 81H     | R/W | 0 | 0 | 0   | 0   | 0  | 1   | 1 | 1 |

| DPL      | Data Pointer(Low byte) Register           | 82H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| DPH      | Data Pointer(High byte) Register          | 83H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| PCON     | Power Control Register                    | 87H     | R/W | х | х | 0   | 0   | 0  | 0   | 0 | 0 |

| TCON     | Timer/Counter Control Register            | 88H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| TMOD     | Timer/Counter Mode Control Register       | 89H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| TL0      | Timer/Counter0 Low byte Register          | 8AH     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| TL1      | Timer/Counter1 Low byte Register          | 8BH     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| TH0      | Timer/Counter0 High byte Register         | 8CH     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| TH1      | Timer/Counter1 High byte Register         | 8DH     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| P1       | Port1 Register                            | 90H     | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| P1SFS    | Port1 Special Function Selection Register | 91H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| P2SFS    | Port2 Special Function Selection Register | 92H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| P3SFS    | Port3 Special Function Selection Register | 93H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

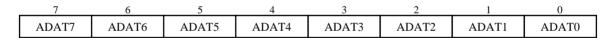

| ADAT     | ADC Data Register                         | 96H     | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| ACON     | ADC Control Register                      | 97H     | R/W | х | х | 0   | х   | 0  | 0   | 0 | 1 |

| P2       | Port2 Register                            | 0A0H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWMCON   | PWM Control Register                      | 0A1H    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| PWM0     | PWM0 Output Register                      | 0A2H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM1     | PWM1 Output Register                      | 0A3H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM2     | PWM2 Output Register                      | 0A4H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM3     | PWM3 Output Register                      | 0A5H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM4     | PWM4 Output Register                      | 0AAH    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM5     | PWM5 Output Register                      | 0ABH    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM6     | PWM6 Output Register                      | 0ACH    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| PWM7     | PWM7 Output Register                      | 0ADH    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| WDTKEY   | Watchdog Key Register                     | 0AEH    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| WDTRST   | Watchdog Timer Reset Register             | 0A6H    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| IEA      | Interrupt Enable Register                 | 0A7H    | R/W | 0 | х | х   | х   | х  | х   | 0 | 0 |

| IE       | Interrupt Enable Register                 | 0A8H    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| P3       | Port3 Register                            | 0B0H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| DPWMCON  | Dynamic PWM Control Register              | 0B1H    | R/W | 0 | х | х   | х   | х  | х   | 0 | 0 |

| DPWM0    | Dynamic PWM0 Output Register              | 0B2H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

| DPWM1    | Dynamic PWM1 Output Register              | 0B3H    | R/W | 1 | 1 | 1   | 1   | 1  | 1   | 1 | 1 |

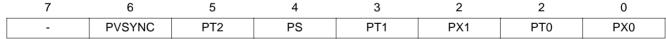

| IPA      | Interrupt Priority Register               | 0B6H    | R/W | 0 | х | х   | х   | х  | х   | 0 | 0 |

| IP       | Interrupt Priority Register               | 0B8H    | R/W | х | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| T2CON    | Timer2 Control Register                   | 0C8H    | R/W | 0 | х | х   | х   | х  | 0   | х | х |

| RC2L     | Reload Low Register                       | 0CAH    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| RC2H     | Reload High Register                      | 0CBH    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| PSW      | Program Status Word Register              | 0D0H    | R/W | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| RAMBUF   | RAM Buffer I/O Interface Register         | 0D4H    | R/W | х | х | х   | х   | х  | х   | х | х |

| Register | Description                                                    | Address | R/W   |   | ı | nit | ial | Va | lue | ; |   |

|----------|----------------------------------------------------------------|---------|-------|---|---|-----|-----|----|-----|---|---|

| Register | Description                                                    | Auuless | IX/VV | 7 | 6 | 5   | 4   | 3  | 2   | 1 | 0 |

| DDCDAT   | Data Shift Register for DDC1                                   | 0D5H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| DDCADR   | DDC Address Pointer Register                                   | 0D6H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| DDCCON   | DDC Mode Status and DDC1 Control Register                      | 0D7H    | R/W   | х | 0 | 0   | х   | 0  | 0   | 0 | 0 |

| S1CON    | Serial Control Register for DDC2                               | 0D8H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| S1STA    | Serial Status Register for DDC2                                | 0D9H    | R     | 0 | х | 0   | 0   | х  | х   | х | х |

| S1DAT    | Data Shift Register for DDC2                                   | 0DAH    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| S1ADR0   | Serial Address0 Register for DDC2                              | 0DBH    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | х |

| S1ADR1   | Serial Address1 Register for DDC2                              | 0D3H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | х |

| S2CON    | Serial Control Register                                        | 0DCH    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| S2STA    | Serial Status Register                                         | 0DDH    | R     | 0 | х | 0   | 0   | х  | х   | х | х |

| S2ADR    | Serial Address Register for I2C                                | 0DFH    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | х |

| S2DAT    | Data Shift Register for I2C                                    | 0DEH    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| ACC      | Accumulator                                                    | 0E0H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| EXCON    | Extended Control Register                                      | 0E8H    | R/W   | х | х | х   | х   | х  | х   | х | 0 |

| В        | B Register                                                     | 0F0H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| MDCON    | Mode Indication Register                                       | 0F1H    | R/W   | 0 | 0 | 0   | х   | х  | 0   | 0 | 0 |

| MDST     | Mode Status Register                                           | 0F2H    | R     | х | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| VPH      | Vertical scan period High byte Register                        | 0F3H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| HPH      | Horizontal scan period High byte Register                      | 0F4H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| VHPL     | V/H scan period High byte Register                             | 0F5H    | R/W   | 0 | 0 | 0   | 0   | 0  | 0   | 0 | 0 |

| HVGEN    | H/V pulse Control Register                                     | 0F9H    | R/W   | х | 0 | 0   | 0   | х  | 0   | 0 | 0 |

| CPGEN    | Clamping pulse and Pattern Control register                    | 0FAH    | R/W   | 0 | 0 | 0   | 0   | 0  | х   | 0 | 0 |

| VFH      | Vertical free-running output pulse period High byte register   | 0FBH    | R/W   | 0 | 0 | 1   | 0   | 0  | 0   | 0 | 0 |

| VFL      | Vertical free-running output pulse period Low byte register    | 0FCH    | R/W   | 0 | 0 | 0   | 0   | 1  | 0   | 1 | 0 |

| HFH      | Horizontal free-running output pulse period High byte register | 0FDH    | R/W   | 0 | 1 | 1   | 0   | 0  | 0   | 0 | 0 |

| HFL      | Horizontal free-running output pulse period Low byte register  | 0FEH    | R/W   | 0 | 0 | x   | 1   | 1  | 1   | 1 | 1 |

# 8.5 Addressing Mode

The addressing modes in HMS9xC7132 instruction set are as follows

- · Direct addressing

- · Indirect addressing

- · Register addressing

- · Register-specific addressing

- Immediate constants addressing

- Indexed addressing

Note that refer to "Chapter 22. Instruction Set" those addressing modes and related instructions.

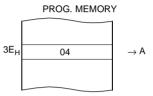

# (1) Direct addressing

In a direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal Data RAM and SFRs(80~FFH RAM) can be directly addressed.

Example:

mov A, 3EH ; A

$$\leftarrow$$

RAM[3E]

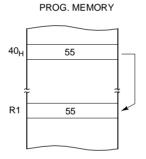

#### (2) Indirect addressing

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed. The address register for 8-bit addresses can be R0 or R1 of the selected register bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

Example:

mov @R1, 40H ; [R1]

$$\leftarrow$$

[40H]

#### (3) Register addressing

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of four banks is selected at execution time by the two bank select bits in the PSW.

Example; mov PSW, #0001000B; select Bank0

mov A, #30H mov R1, A

#### (4) Register-specific addressing

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data

Pointer, etc., so no address byte is needed to point it. The opcode itself does that.

# (5) Immediate constants addressing

The value of a constant can follow the opcode in Program memory.

Example; mov A, #100H.

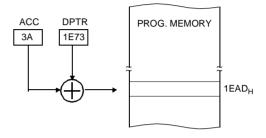

#### (6)Indexed addressing

Only Program memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program memory. A 16-bit base register (either DPTR or PC) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program memory is formed by adding the Accumulator data to the base pointer.

Example; movc A, @A+DPTR

HMS9xC7132 / HMS9xC7134

# ициіх

# 9. INTERRUPTS

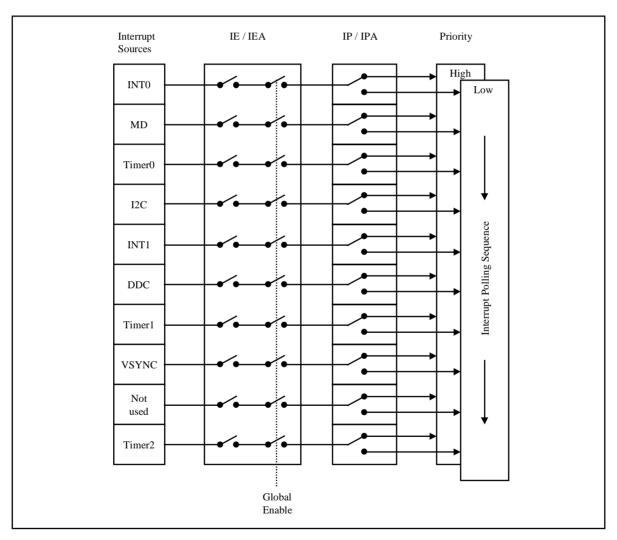

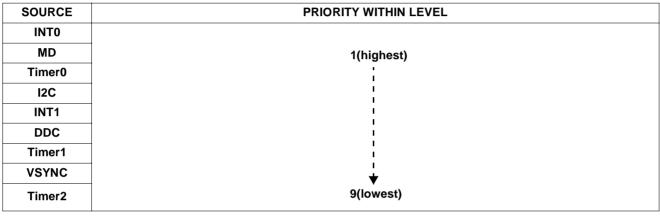

There are interrupt requests from 9 sources as follows.

- INT0 external interrupt

- INT1 external interrupt

- •Timer0 interrupt

- Timer1 interrupt

- Timer2 interrupt

- DDC interrupt

- MD interrupt

- VSYNC interrupt

- I2C interrupt

### 9.1 Interrupt sources

#### INT0 external interrupt:

- •The INTO can be either level-active or transition-active depending on bit ITO in register TCON. The flag that actually generates this interrupt is bit IEO in TCON.

- When an external interrupt is generated, the corresponding request flag is cleared by the hardware when the service routine is

vectored to only if the interrupt was transition-activated.

• If the interrupt was level-activated then the interrupt request flag remains set until the requested interrupt is actually generated. Then it has to deactivate the request before the interrupt service routine is completed, or else another interrupt will be generated.

#### **INT1** external interrupt:

- •The INT1 can be either level-active or transition-active depending on bit IT1 in register TCON. The flag that actually generates this interrupt is bit IE1 in TCON.

- When an external interrupt is generated, the corresponding request flag is cleared by the hardware when the service routine is

vectored to only if the interrupt was transition-activated.

• If the interrupt was level-activated then the interrupt request flag remains set until the requested interrupt is actually generated. Then it has to deactivate the request before the interrupt service routine is completed, or else another interrupt will be generated.

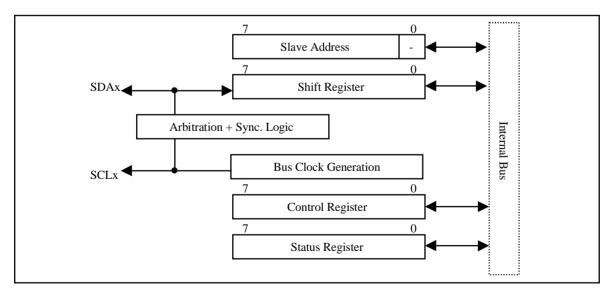

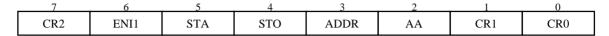

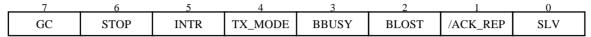

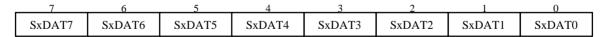

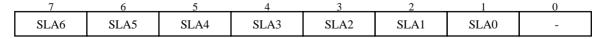

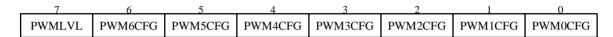

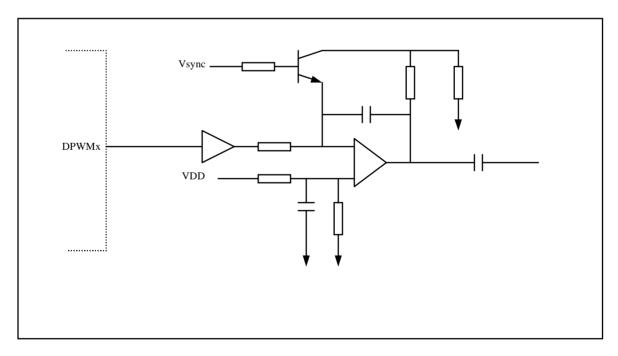

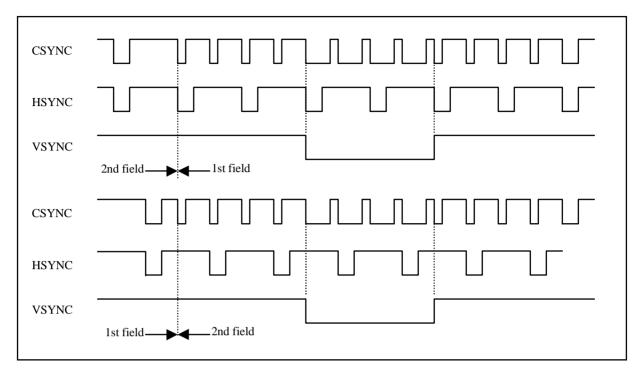

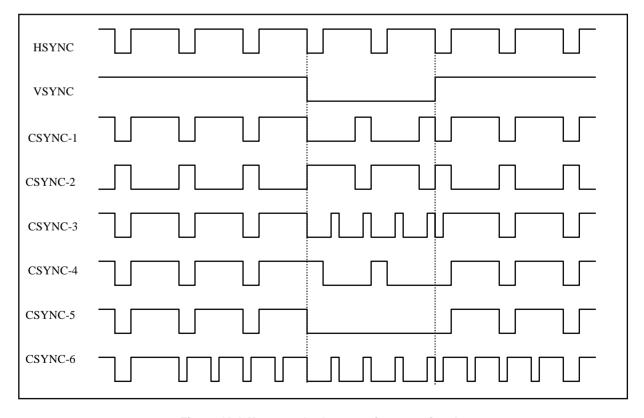

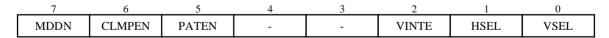

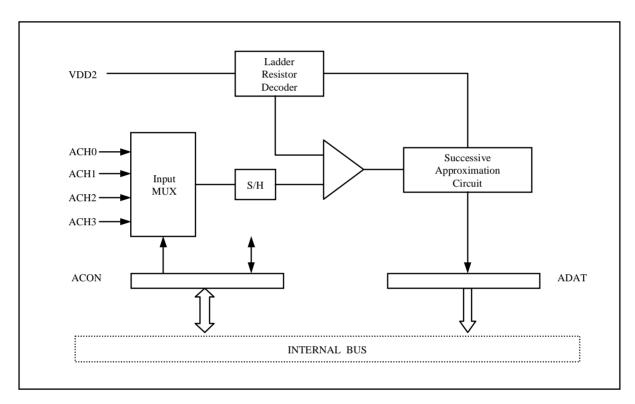

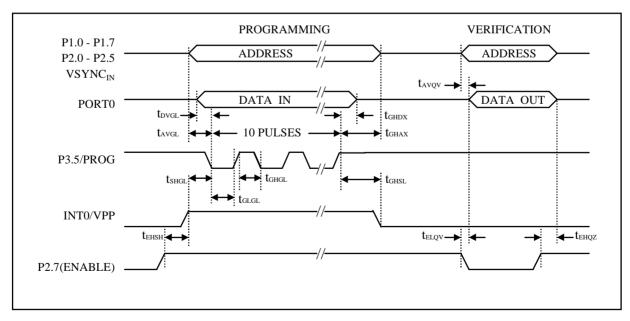

#### MD interrupt: