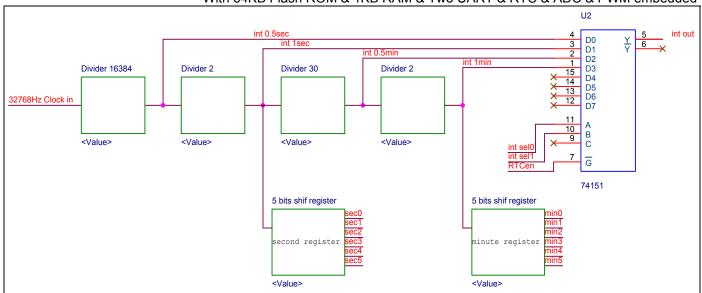

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **Product List**

SM89T16R1L16, 16MHz 64KB internal flash MCU SM89T16R1C25, 25MHz 64KB internal flash MCU

# **General Description**

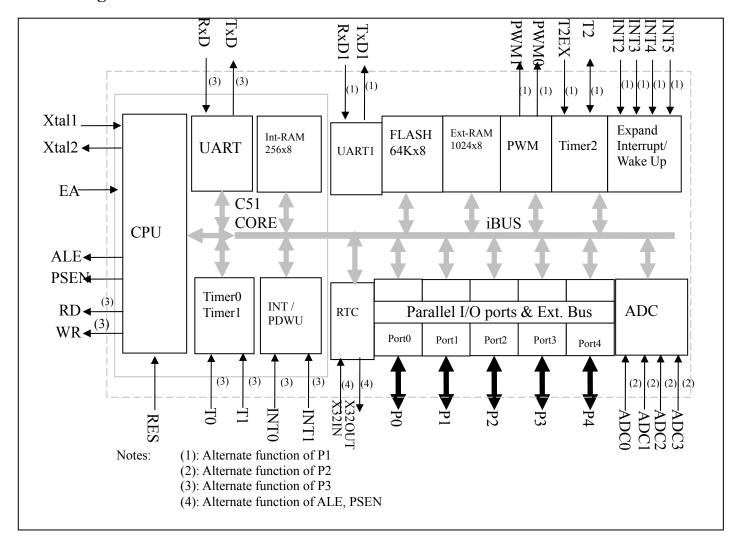

The SM89T16R1 is a high speed (4 clocks / machine cycle) single-chip 8-bits microcontroller manufactured in an advanced CMOS process with on chip flash memory. It supports a derivative of the 80C51 microcontroller family. The SM89T16R1 has the same instructions set as the 80C51.

The SM89T16R1 contains a 64KB on chip program flash, a volatile 1280 x 8 bits data RAM, four 8-bits I/O ports, one 4-bits I/O port, two 16-bits timer/event counters, and an additional 16-bits timer coupled to capture and compare latches, a two-priority-level, nested interrupt structure, two pulse-width- modulation outputs, two UART and two DPTR, an on-chip oscillator and timing circuit. For system that requires extra capability the SM89T16R1 can be expanded using standard TTL compatible memory and logic.

In addition, The SM89T16R1 has two software selectable modes of power saving – IDLE mode and POWER-DOWN mode. The IDLE mode freezes the CPU while allowing the RAM, timer, serial ports, and interrupt system to continue functioning. The POWER-DOWN mode saves the RAM contents but freezes the oscillator, causing all other chip functions to be inoperative.

The Power Management Mode (PMM) is useful for portable or battery-powered applications. This feature allows software to select a lower speed clock as the main time base.

# **Ordering Information**

SM89T16R1ihhkL yymmv

i: process identifier {L= $3.0V\sim3.6V$ ,C= $4.5V\sim5.5V$ }

hh: working clock in MHz {16,25}

k: package type postfix {as below table}

yy: year mm: month

v: version identifier { , A, B, ...}

L: PB Free identifier

{No text is Non-PB Free,"P" is PB Free}

#### **Feature**

- Working Voltage: 3.3V or 5.0V.

- 80C51 Central Processor Unit (CPU),

High-Speed Architecture (4 clocks / machine cycle), the maximum clock rate is 25 MHz.

- 64K x 8 on chip flash memory can be programmed at V<sub>PP</sub> = 12V

- 1280 x 8 RAM (On-Chip 256 bytes and Expand 1024 bytes), expandable externally to 64KB

- Two standard 16-bits timers/counters

- An additional 16-bits timer/counter coupled to a capture and compare register.

- Two 8-bits / 5-bits resolution Pulse-Width-Modulation (PWM) outputs.

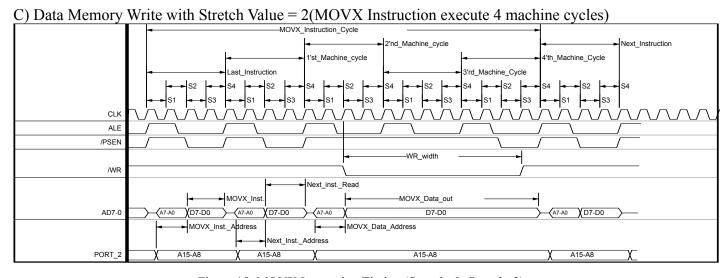

- Four channels 6 bits Analog to Digital Converter (ADC).

- Four 8-bits I/O ports.(For PDIP package)

- Four 8-bits I/O ports plus one 4-bits I/O port. (For PLCC or PQFP package)

- Two Full-duplex Enhance UART

- Two DPTR (either data pointer can be incremented and decrement).

- 13 interrupt sources (default 6 + int2, int3, int4, int5, UART1, ADC, RTC) with 2 priority levels.

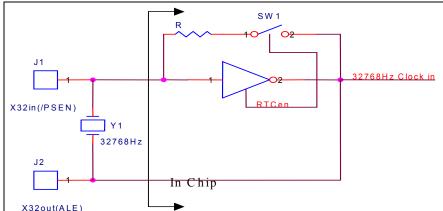

- RTC (Real Time Clock) function.

- Extended temperature range (-40 $^{\circ}$ C to +85 $^{\circ}$ C)

- Software enable/disable ALE output pulse

- Wake-up from POWER-DOWN mode by external interrupt, RTCI or H/W Reset.

Taiwan 6F, No.10-2 Li- Hsin 1st Road , Science-based Industrial Park, Hsinchu, Taiwan 30078

TEL: 886-3-567-1820 886-3-567-1880 FAX: 886-3-567-1891 886-3-567-1894

Specifications subject to change without notice contact your sales representatives for the most recent information.

1

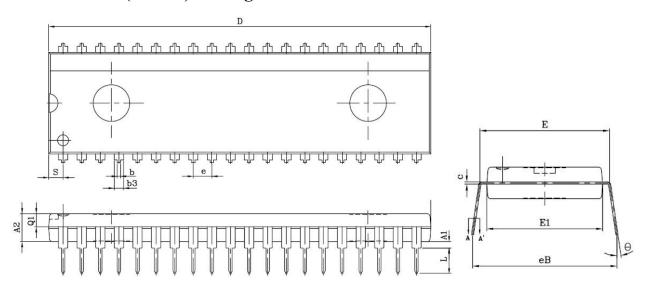

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded **Package Spec.**

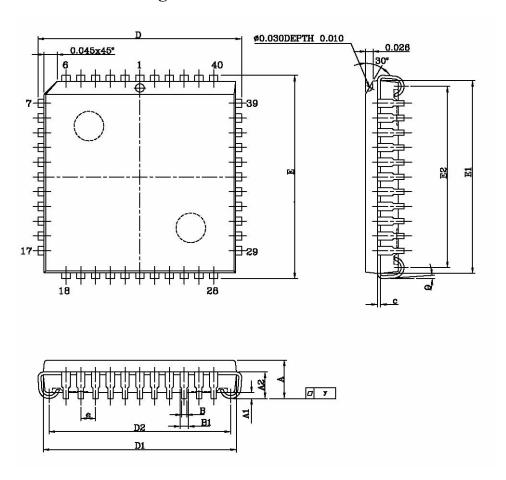

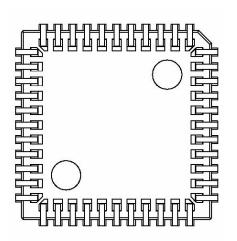

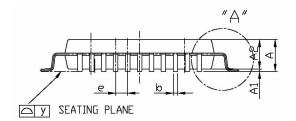

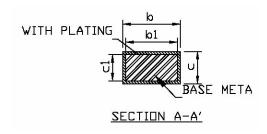

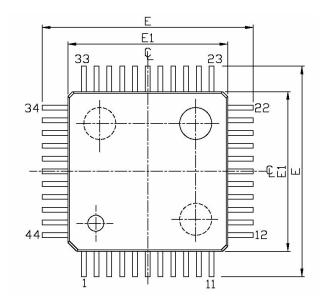

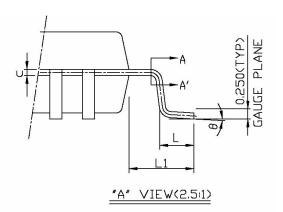

| Package  | Pin / PAD | Frequency                      |

|----------|-----------|--------------------------------|

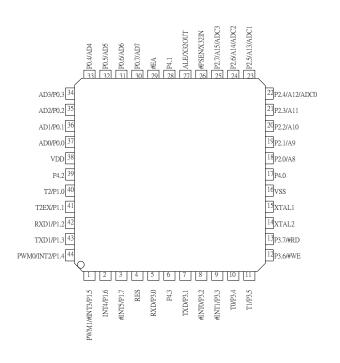

| 44L PQFP | Figure 1  | 16 MHz at 3.3V and 25MHz at 5V |

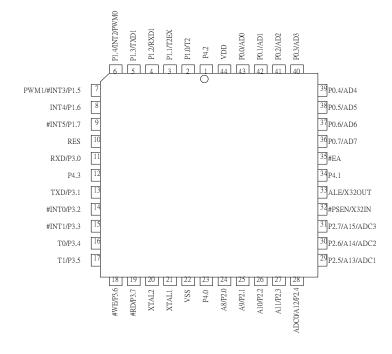

| 44L PLCC | Figure 2  | 16 MHz at 3.3V and 25MHz at 5V |

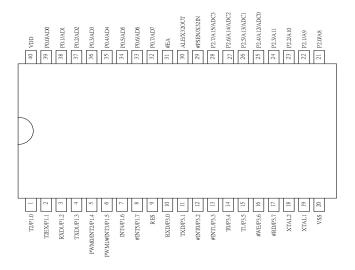

| 40L PDIP | Figure 3  | 16 MHz at 3.3V and 25MHz at 5V |

# **Pin Configuration**

Figure 1 44L PQFP Package

Figure 2 44L PLCC Package

Figure 3 40L PDIP Package

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **Block Diagram**

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **Pin Description**

| 19.0 - P0.7   39,38,37,36   37,36,35,34   34,42,41,40   39,38,37,36   33,32,31,30   33,38,37,36   33,38,37,36   33,38,37,36   33,38,37,36   33,38,37,36   33,38,37,36   33,38,37,36   33,38,37,36   Port 0: Port 0: an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them become floating and can be used as high-impedance inputs. Port 0: a shot be multiplexed low-order is and data to the use days in given by the properties and data to the use of the program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory. In this application traces sees to external program and data memory that the program and data memory in the program and data memory that program and the season and the program and | MNEMONIC    | DIP 40 pin | PQFP 44 Pin | PLCC 44 pin | Names and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35,34,33,32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VDD         | 40         | 38          | 44          | +3.3V and +5V power supply pin during normal operations and power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P1.0 - P1.7    1,2,3,4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P0.0 – P0.7 |            |             |             | Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them become floating and can be used as high- impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory. In this application, it uses strong internal pull-ups when emitting 1s.  Port Pin Alternative function  P0.0 AD0  P0.1 AD1  P0.2 AD2  P0.3 AD3  P0.4 AD4  P0.5 AD5  P0.6 AD6                                                                                                                                                                                                                                                                                                                                                                                                           |

| Reset: A high on this pin for two machine cycles while the oscillator is running resets the device. An internal resistor to VSS permits a power-on reset using only an external capacitor to VCC.  22.0 – P2.7  21,22,23,24, 25,26,27,28  22,23,24,25  28,29,30,31  24,25,26,27, 28,29,30,31  Port 2: Port 2: Port 2 is an 8-bits bidirectional I/O port with internal pull-ups. Port 2 pin that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: III.). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bits addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. Durin accesses to external data memory that uses 8-bits addresses (MOV @Ri port 2 emits the contents of the P2 special function register. Port Pin Alternative function P2.0 A8 P2.1 A9 P2.2 A10 P2.3 A11 P2.4 A12/ADC0 P2.5 A13/ADC1 P2.6 A14/ADC2 P2.7 A15/ADC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P1.0 – P1.7 |            |             |             | Port 1:  An 8-bits bidirectional I/O port with internal pull-ups on all pins. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: IIL).  Alternate function of SM89T16R1 include: Port Pin Alternative function P1.0 T2: TIMER2 clock output P1.1 T2EX: TIMER2 reload/capture DIR. P1.2 RxD1: UART1 input P1.3 TxD1: UART1 output P1.4 PWM0: PWM channel 0 output INT2: rising edge trigger P1.5 PWM1: PWM channel 1 output #INT3: falling edge trigger P1.6 INT4: rising edge trigger                                                                                                                                                                |

| P2.0 – P2.7  21,22,23,24, 25,26,27,28  21,22,23,24,25  28,29,30,31  Port 2: Port 2 is an 8-bits bidirectional I/O port with internal pull-ups. Port 2 pin that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: IIL). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bits addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. Durin accesses to external data memory that uses 8-bits addresses (MOV @Ri port 2 emits the contents of the P2 special function register.  Port Pin Alternative function P2.0 A8 P2.1 A9 P2.2 A10 P2.3 A11 P2.4 A12/ADC0 P2.5 A13/ADC1 P2.6 A14/ADC2 P2.7 A15/ADC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RST         | 9          | 4           | 10          | Reset: A high on this pin for two machine cycles while the oscillator is running resets the device. An internal resistor to VSS permits a power-on reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P2.0 – P2.7 |            |             |             | Port 2: Port 2 is an 8-bits bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. (See DC Electrical Characteristics: IIL). Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bits addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external data memory that uses 8-bits addresses (MOV @Ri), port 2 emits the contents of the P2 special function register.  Port Pin Alternative function P2.0 A8 P2.1 A9 P2.2 A10 P2.3 A11 P2.4 A12/ADC0 P2.5 A13/ADC1 P2.6 A14/ADC2 |

| MNEMONIC   DIP 40 pin   POFP 44 Pin   PLCC 44 pin   Names and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MNEMONIC    | DIP 40 pin | PQFP 44 Pin | PLCC 44 pin | Names and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

|             |                            | WILLI 04ND              | i lasii iXOIVI & Ir          | RAIN & TWO DANT & NTC & ADC & FWIN ellibedded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------|-------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3.0 – P3.7 | 10,11,12,13<br>14,15,16,17 | 5,7,8,9,<br>10,11,12,13 | 11, 13,14,15,<br>16,17,18,19 | Port 3: Port 3 is an 8-bits bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. (See DC Electrical Characteristics: IIL). Port 3 also serves the special features.  Port Pin Alternative function P3.0 RxD UART input P3.1 TxD UART output P3.2 #EX0 external interrupt 0 P3.3 #EX1 external interrupt 1 P3.4 T0: Timer 0 external input P3.5 T1: Timer 1 external input P3.6 #WR External data memory write strobe P3.7 #RD External data memory read strobe |

| ALE/X32OUT  | 30                         | 27                      | 33                           | Address Latch Enable: Output pulse for latching the low byte of the address during an access to external memory. In normal operation, ALE is emitted twice every machine cycle, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. Setting SFR SCONF.0 can disable ALE. With this bit set, ALE will be active only during a MOVX instruction.  X32OUT: The 32.768KHz crystal output for RTC function.                                                                                                                                                                                             |

| #PSEN/X32IN | 29                         | 26                      | 32                           | Program Store Enable: The read strobe to external program memory. When executing code from the external program memory, #PSEN is activated twice each machine cycle, except that two #PSEN activations are skipped during each access to external data memory. #PSEN is not activated during fetches from internal program memory.  X32IN: The 32.768KHz crystal input for RTC function.                                                                                                                                                                                                                                                                                       |

| #EA         | 31                         | 29                      | 35                           | External Access Enable:  #EA must be externally held low to enable the device to fetch code from external program memory locations. If #EA is held high, the device executes from internal program memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

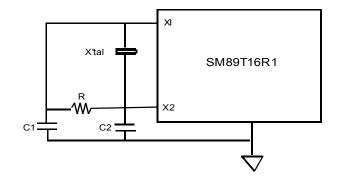

| XTAL1       | 19                         | 15                      | 21                           | Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL2       | 18                         | 14                      | 20                           | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **SFR Mapping**

The special function register of SM89T16R1 fall into the following categories

- C51 CORE register: ACC, B, DPL, DPH, PSW, SP

- I/O ports: P0,P1, P2, P3, P4

- Timer/Counter register: T2CON, T2MOD, TCON, TMOD, TH0, TH1, TH2, TL0, TL1, TL2, RCA2PL, RCAP2H

- The Second DPTR register: DPS, DPH1, DPL1

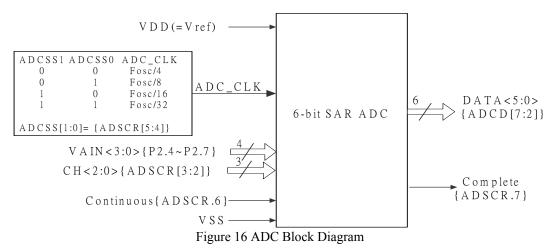

- UART I/O register: SBUF, SCON

- UART1 I/O register: SBUF1, SCON1

- ADC register: ADCSC, ADCD, P2CON

- Power and system control register: PCON, SCONF

- Interrupt system register: IP, IE, IP1, IE1, IFR

- Expand External Interrupt register: EIE, EIP, EXIF

- RTC register: RTCC, RTCS

- PWM output register: PWMC0, PWMC1, PWMD0, PWMD1, P1CON

- PMM (Power Management) register: PMR

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded Table 1 SFR Map

| \$F8 | SCON1     | SBUF1     |           |           |           |           |           |           | \$FF |

|------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|------|

|      | 0000 0000 | xxxx xxxx |           |           |           |           |           |           |      |

| \$F0 | В         |           |           |           |           |           |           |           | \$F7 |

|      | 0000 0000 |           |           |           |           |           |           |           |      |

| \$E8 |           | SADEN     | SADEN1    |           |           |           |           |           | \$EF |

|      |           | 0000 0000 | 0000 0000 |           |           |           |           |           |      |

| \$E0 | ACC       |           |           |           |           |           |           |           | \$E7 |

|      | 0000 0000 |           |           |           |           |           |           |           |      |

| \$D8 | P4        | SADDR     | SADDR1    |           |           |           |           |           | \$DF |

|      | xxxx 1111 | 0000 0000 | 0000 0000 |           |           |           |           |           |      |

| \$D0 | PSW       | PMR       |           | PWMC0     | PWMC1     |           |           |           | \$D7 |

|      | 0000 0000 | 01xx 0000 |           | 0000 0000 | 0000 0000 |           |           |           |      |

| \$C8 | T2CON     | T2MOD     | RCAP2L    | RCAP2H    | TL2       | TH2       |           |           | \$CF |

|      | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 |           |           |      |

| \$C0 |           |           |           |           |           |           |           |           | \$C7 |

|      |           |           |           |           |           |           |           |           |      |

| \$B8 | IP        | IP1       | EIP       |           |           |           |           | SCONF     | \$BF |

|      | x000 0000 | 0000 0000 | xxxx 0000 |           |           |           |           | 0000 0000 |      |

| \$B0 | P3        |           |           | PWMD0     | PWMD1     |           |           |           | \$B7 |

|      | 1111 1111 |           |           | 0000 0000 | 0000 0000 |           |           |           |      |

| \$A8 | IE        | IE1       | IFR       | EIE       |           |           |           |           | \$AF |

|      | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 |           |           |           |           |      |

| \$A0 | P2        | RTCS      | RTCC      | CKCON     | DPL1      | DPH1      | DPS       |           | \$A7 |

|      | 1111 1111 | 0000 0000 | 0000 0000 | 0000 0001 | 0000 0000 | 0000 0000 | 0000 0000 |           |      |

| \$98 | SCON      | SBUF      |           | P1CON     | P2CON     |           |           |           | \$9F |

|      | 0000 0000 | XXXX XXXX | LEDDA     | 0000 0000 | 0000 0000 | LEBBA     | 1.555.4   |           |      |

| \$90 | P1        | EXIF      | LEDP0     | LEDP1     | LEDP2     | LEDP3     | LEDP4     |           | \$97 |

|      | 1111 1111 | 0000 1xxx | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 |           |      |

| \$88 | TCON      | TMOD      | TL0       | TL1       | TH0       | TH1       | ADCSC     | ADCD      | \$8F |

|      | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 | 0000 0000 |      |

| \$80 | P0        | SP        | DPL       | DPH       |           |           |           | PCON      | \$87 |

|      | 1111 1111 | 0000 0111 | 0000 0000 | 0000 0000 |           |           |           | 00xx 0000 |      |

# Table 2 All SFR list (ADC, RTC, PWM, LED Driving Capability Control)

| Symbol | Description          | Direct | Bit 7     | Bit 6       | Bit 5        | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | RESET |

|--------|----------------------|--------|-----------|-------------|--------------|---------|--------|--------|--------|--------|-------|

|        | A/D Converter        |        |           |             |              |         |        |        |        |        |       |

| ADCSC  | ADC status & control | 8EH    | COM       | CON         | ADCSS1       | ADCSS0  | CH1    | CH0    |        |        | 00H   |

| ADCD   | ADC data register    | 8FH    | AD.5      | AD.4        | AD.3         | AD.2    | AD.1   | AD.0   |        |        | 00H   |

|        |                      |        |           | Real Tin    | ner Clock (R | TC)     |        |        |        |        |       |

| RTCS   | RTC Status           | A1H    | RTCen     | Stable      | Sec.5        | Sec.4   | Sec.3  | Sec.2  | Sec.1  | Sec.0  | 00H   |

| RTCC   | RTC Control          | A2H    | Int_sel.1 | Int_sel.0   | Min.5        | Min.4   | Min.3  | Min.2  | Min.1  | Min.0  | 00H   |

|        |                      |        |           | PV          | VM output    |         |        |        |        |        |       |

| PWMC0  | PWM 0 Control        | D3H    |           |             |              |         |        | PBS    | PFS1   | PFS0   | 00H   |

| PWMC1  | PWM 1 Control        | D4H    |           |             |              |         |        | PBS    | PFS1   | PFS0   | 00H   |

| PWMD0  | PWM 0 Data           | ВЗН    | PWMD.7    | PWMD.6      | PWMD.5       | PWMD.4  | PWMD.3 | PWMD.2 | PWMD.1 | PWMD.0 | 00H   |

| PWMD1  | PWM 1 Data           | B4H    | PWMD.7    | PWMD.6      | PWMD.5       | PWMD.4  | PWMD.3 | PWMD.2 | PWMD.1 | PWMD.0 | 00H   |

|        |                      |        |           | LED Driving | g Capability | Control |        |        |        |        |       |

| LEDP 0 | LED output in P0     | 92H    |           |             |              |         |        |        |        |        | 00H   |

| LEDP 1 | LED output in P1     | 93H    |           |             |              |         |        |        |        |        | 00H   |

| LEDP 2 | LED output in P2     | 94H    |           |             |              |         |        |        |        |        | 00H   |

| LEDP 3 | LED output in P3     | 95H    |           |             |              |         |        |        |        |        | 00H   |

| LEDP 4 | LED output in P4     | 96H    |           |             |              |         |        |        |        |        | 00H   |

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

Table 3: All SFR list (8051, I/O, Timer, UART/UART1, System, Interrupt)

| Symbol   | Description                 | Direct | Bit 7       | Bit 6 | Bit 5        | Bit 4    | Bit 3 | Bit 2  | Bit 1 | Bit 0    | RESET |

|----------|-----------------------------|--------|-------------|-------|--------------|----------|-------|--------|-------|----------|-------|

| ACC*     | Accumulator                 | E0     | T           | 8     | 051 Core     |          |       | T      | T     |          | 00H   |

| В        | B register                  | F0     |             |       |              |          |       |        |       |          | 00H   |

| SP       | Stack Pointer               | 81H    |             |       |              |          |       |        |       |          | 07H   |

| PSW*     | Process Status              | D0H    | CY          | AC    | F0           | RS1      | RS0   | OV     |       | P        | 00H   |

| DPTR     | Data Pointer (2 Bytes)      | DOII   | CI          | AC    | 1.0          | KSI      | KSU   | OV     |       | 1        | 0011  |

| DPH      | Data Pointer (2 Bytes)      | 83H    |             |       |              |          |       |        |       |          | 00H   |

| DPL      | Data Pointer Low            | 82H    |             |       |              |          |       |        |       |          | 00H   |

| DFL      | Data Folliter Low           | 0211   |             | I/    | O PORT       |          |       |        |       | _        | 0011  |

| P0*      | Port 0                      | 80H    | P0.7        | P0.6  | P0.5         | P0.4     | P0.3  | P0.2   | P0.1  | P0.0     | FFH   |

| P1*      | Port 1                      | 90H    | P1.7        | P1.6  | P1.5         | P1.4     | P1.3  | P1.2   | P1.1  | P1.0     | FFH   |

| P2*      | Port 2                      | A0H    | P2.7        | P2.6  | P2.5         | P2.4     | P2.3  | P2.2   | P2.1  | P2.0     | FFH   |

| P3*      | Port 3                      | ВОН    | P3.7        | P3.6  | P3.5         | P3.4     | P3.3  | P3.2   | P3.1  | P3.0     | FFH   |

| P4*      | Port 4                      | D8H    |             |       |              |          | P4.3  | P4.2   | P4.1  | P4.0     | XFH   |

| P1CON    | P1 Control                  | 9BH    |             |       | PWM1E        | PWM0E    |       |        | -     | -        | 00H   |

| P2CON    | P2 Control                  | 9CH    | ADCE3       | ADCE2 | ADCE1        | ADCE0    |       |        |       |          | 00H   |

| 12001    | 12 0011101                  | 7011   | 112 023     |       | ER / Counter |          |       |        |       |          | 0011  |

| TCON*    | Timer Control register      | 88H    | TF1         | TF1   | TF0          | TR0      | IE1   | IT1    | IE0   | IT0      | 00H   |

| THL0     | Timer 0 (2 Bytes)           |        |             |       |              |          |       |        |       |          |       |

| TH0      | Timer 0 High                | 8CH    |             |       |              |          |       |        |       |          | 00H   |

| TL0      | Timer 0 Low                 | 8AH    |             |       |              |          |       |        |       |          | 00H   |

| THL1     | Timer 1 (2 Bytes)           |        |             |       |              |          |       |        |       |          |       |

| TH1      | Timer 1 High                | 8DH    |             |       |              |          |       |        |       |          | 00H   |

| TL1      | Timer 1 Low                 | 8BH    |             |       |              |          |       |        |       |          | 00H   |

| T2CON*   | Timer 2 Control             | C8H    | TF2         | EXF2  | RCLK         | TCLK     | EXEN2 | TR2    | CT2   | CPRL2    | 00H   |

| T2MOD    | Timer 2 Mode Control        | С9Н    | HC5         | HC4   | HC3          | HC2      | T2CR  | 1112   | T2OE  | DCEN     | 00H   |

| RCAP2HL  | Reload/Capture (2 bytes)    | 6711   | 1103        | 1101  | 1103         | 1102     | 12010 |        | TEGE  | BCEIT    | 0011  |

| RCAP2H   | RCAP2 High                  | СВН    |             |       |              |          |       |        |       |          | 00H   |

| RCAP2L   | RCAP2 Low                   | CAH    |             |       |              |          |       |        |       |          | 00H   |

| THL2     | Time 2 (2 bytes)            | Crim   |             |       |              |          |       |        |       |          | 0011  |

| TH2      | Timer 2 High                | CDH    |             |       |              |          |       |        |       |          | 00H   |

| TL2      | Time 2 Low                  | CCH    |             |       |              |          |       |        |       |          | 00H   |

| TEZ      | Time 2 Eow                  | CCII   |             | UAR   | T & UART1    |          |       |        | 1     |          | 0011  |

| SCON*    | UART Control                | 98H    | SM0/FE      | SM1   | SM2          | REN      | TB8   | RB8    | TI    | RI       | 00H   |

| SBUF     | UART Buffer                 | 99H    | 51110/12    | 51111 | 51.12        | TELL     | 120   | TEBU   |       | 10       | XXH   |

| SCON1    | UART 1 Control              | F8H    | SM0 1/FE 1  | SM1 1 | SM2 1        | REN 1    | TB8 1 | RB8 1  | TI 1  | RI 1     | 00H   |

| SBUF1    | UART 1 Buffer               | F9H    | 510_1/1 2_1 | 5     | 51.12_1      | TCDI (_I | 120_1 | 100_1  |       | 10_1     | XXH   |

| SADDR    | Slave Address               | D9H    |             |       |              |          |       |        |       |          | 00H   |

| SADDR1   | Slave Address 1             | DAH    |             |       |              |          |       |        |       |          | 00H   |

|          | Slave Address Mask          |        |             |       |              |          |       |        |       |          |       |

| SADEN    | Enable                      | Е9Н    |             |       |              |          |       |        |       |          | 00H   |

| SADEN1   | Slave Address 1 Mask        | EAH    |             |       |              |          |       |        |       |          | 00H   |

| SADENI   | Enable                      | LAII   |             |       |              |          |       |        |       |          | 0011  |

|          |                             | 1      |             | Da    | ata Point 1  |          | 1     | 1      |       |          |       |

| DPTR1    | Data Pointer 1 (2 Bytes)    |        |             |       |              |          |       |        |       |          |       |

| DPH1     | Data Pointer 1 High         | A5H    |             |       |              |          |       |        |       |          | 00H   |

| DPL1     | Data Pointer 1 Low          | A4H    |             |       |              |          |       |        |       |          | 00H   |

| DPS      | Data Point Select           | A6H    |             |       |              |          |       |        |       | DPS.0    | 00H   |

| DGG:     |                             | 1 05** |             |       | r and System | 1        |       |        |       | **       | 0077  |

| PCON     | Power Control register      | 87H    | SMOD        | SMOD0 |              |          |       |        | PD    | IDLE     | 00H   |

| SCONF    | System Control              | BFH    | SMOD1       |       |              | PDWUE    |       |        | OME   | ALEI     | 00H   |

| PMR      | Power Management            | D1H    | CD1         | CD0   |              |          | XTOFF |        |       |          | 40H   |

|          | Register                    |        |             |       |              |          |       |        |       |          |       |

| TEA      | X ( E 11                    | A OTT  |             |       | rrupt system | EGO      | DT1   | T77/1  | EEO   | EXC      | 0011  |

| IE*      | Interrupt Enable            | A8H    | EA          | ES1   | ET2          | ES0      | ET1   | EX1    | ET0   | EX0      | H00   |

| IE1      | Interrupt Enable 1          | A9H    |             |       |              |          | EADC  | ERTC   |       |          | 00H   |

| IFR      | Interrupt Flag 1            | AAH    | 1           |       |              |          | ADCIF | RTCIF  | T7772 | 7777     | 00H   |

| EIE      | External Interrupt Enable   | ABH    | 1           | DG1   | D.T.O.       | PGO      | EX5   | EX4    | EX3   | EX2      | 00H   |

| IP*      | Interrupt Priority          | B8H    |             | PS1   | PT2          | PS0      | PT1   | PX1    | PT0   | PX0      | 00H   |

| IP1      | Interrupt Priority 1        | В9Н    |             |       |              |          | PADC  | PRTC   | DYYC  | D775     | 00H   |

| EIP      | External Interrupt Priority | BAH    |             |       |              |          | PX5   | PX4    | PX3   | PX2      | X0H   |

| OV. COLL |                             | 1 . 2  |             | Clo   | ock Control  | mus.     | TO Y  | ) (D - | ) m:  | ) (T. 2) | 0.177 |

| CKCON    | Clock Control               | A3H    |             |       | T2M          | T1M      | T0M   | MD2    | MD1   | MD0      | 01H   |

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **Operating Conditions**

| Symbol  | Description           | Min. | Тур. | Max. | Unit.        | Remarks                        |

|---------|-----------------------|------|------|------|--------------|--------------------------------|

| TA      | Operating temperature | -40  | 25   | 85   | $^{\circ}$ C | Ambient temperature under bias |

| VCC33   | Supply voltage        | 3.0  | 3.3  | 3.6  | V            |                                |

| VCC5    | Supply voltage        | 4.5  | 5.0  | 5.5  | V            |                                |

| Fosc 16 | Oscillator Frequency  |      |      | 16   | MHz          | For 3.3V application           |

| Fosc 25 | Oscillator Frequency  |      |      | 25   | MHz          | For 5.0V application           |

# **DC** Characteristic

$V_{CC} = 5V (\pm 10\%), V_{SS} = 0V T_A = -40^{\circ}C$  to  $85^{\circ}C$

| SYMBOL             | PARAMETER                                    | TEST                                          | LIN    | <b>MITS</b> | UNIT |

|--------------------|----------------------------------------------|-----------------------------------------------|--------|-------------|------|

| STNIBOL            | TARAMETER                                    | CONDITIONS                                    | MIN    | MAX         | UNII |

| $V_{CC}$           | Supply Voltage                               |                                               | 4.5    | 5.5         | V    |

| $I_{CC}$           | Supply current operating                     | See notes 1 $f_{CLK} = 12MHz V_{CC} = 5.0V$   |        | 30          | mA   |

| $I_{\mathrm{ID}}$  | Supply current IDLE Mode                     | See note 2<br>$f_{CLK} = 12MHz V_{CC} = 5.0V$ |        | 15          | mA   |

| т                  | Supply current Power-Down MODE RTC Disable   | See note 3; $V_{CC} = 5.5V$                   |        | 30          | μΑ   |

| $I_{PD}$           | Supply current Power-Down MODE RTC<br>Enable | See note 3; $V_{CC} = 5.5V$                   |        | 100         | uA   |

|                    |                                              | INPUT                                         | ·      |             | ·    |

| $V_{\mathrm{IL1}}$ | Input LOW voltage, P0, P1, P2, P3, P4, /EA   |                                               | -0.5   | 0.8         | V    |

| $V_{IL2}$          | Input LOW voltage, RES, XTAL1                |                                               | 0      | 0.8         | V    |

| $V_{\mathrm{IH1}}$ | Input HIGH voltage, P0, P1, P2, P3, P4, /EA  |                                               | 2.0    | Vcc+0.5     | V    |

| $V_{\rm IH2}$      | Input HIGH voltage, RES, XTAL1               |                                               | 70%VCC | Vcc+0.5     | V    |

| ${ m I}_{ m IL}$   | Input current LOW level Port 1,2,3,4         | VIN = 0.45V                                   |        | -75         | μA   |

| $I_{TL}$           | Transition current High to Low Port 1,2,3,4  | VIN = 2.0 V                                   |        | -650        | μΑ   |

| $I_{LI}$           | Input leakage current                        | 0.45V < VIN < VCC-0.3V                        |        | ±10         | μA   |

|                    |                                              | OUTPUT                                        |        |             |      |

| $V_{OL1}$          | Output LOW voltage, Port 0,ALE, /PSEN        | IOL = 3.2 mA, $VCC = 5.0 V$                   |        | 0.45        | V    |

| $V_{\mathrm{OL2}}$ | Output LOW voltage, Port 1, 2, 3, 4          | IOL = 1.6 mA, $VCC = 5.0 V$                   |        | 0.45        | V    |

| $V_{\mathrm{OH1}}$ | Output High voltage Port0 ALE, /PSEN         | IOH = -800uA , VCC =5.0V                      | 2.4    |             | V    |

| $V_{\mathrm{OH1}}$ | Output High voltage Port 1,2,3,4             | $IOH = -60\mu A$ , $VCC = 5.0V$               | 2.4    |             | V    |

| R <sub>RST</sub>   | Internal RESET pull-down resistor            | ·                                             | 50     | 300         | kΩ   |

| C <sub>IO</sub>    | Pin capacitance                              | Test freq=1MHz, TA=25°C                       |        | 10          | pF   |

# $V_{CC} = 3.3 \text{V } (\pm 10\%), V_{SS} = 0 \text{V }, T_A = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$

| SYMBOL            | PARAMETER                                   | TEST                                           | LI              | MITS            | UNIT |

|-------------------|---------------------------------------------|------------------------------------------------|-----------------|-----------------|------|

| STMIDOL           | TAKAMETEK                                   | CONDITIONS                                     | MIN             | MAX             | UNII |

| $V_{CC}$          | Supply Voltage                              |                                                | 3.0             | 3.6             | V    |

| $I_{CC}$          | Supply current operating                    | See notes 1<br>$f_{CLK} = 12MHz V_{CC} = 3.6V$ |                 | 20              | mA   |

| $I_{\mathrm{ID}}$ | Supply current IDLE Mode                    | See note 2<br>$f_{CLK} = 12MHz V_{CC} = 3.6V$  |                 | 10              | mA   |

| T                 | Supply current Power-Down MODE RTC Disable  | See note 3; $V_{CC} = 3.6V$                    |                 | 20              | μΑ   |

| $I_{PD}$          | Supply current Power-Down MODE RTC Enable   | See note 3; $V_{CC} = 3.6V$                    |                 | 30              | μΑ   |

|                   |                                             | NPUT                                           |                 |                 |      |

| $V_{\rm IL1}$     | Input LOW voltage, P0, P1, P2, P3, P4, /EA  | VCC = 3.6V                                     | 0               | 0.2 VCC<br>-0.2 | V    |

| $V_{IL2}$         | Input LOW voltage, RST,XTAL1                | VCC = 3.6V                                     | 0               | 0.2 VCC<br>-0.2 | V    |

| VIH1              | Input HIGH voltage, P0, P1, P2, P3, P4, /EA | VCC = 3.6V                                     | 0               | 0.2 VCC<br>-0.2 | V    |

| VIH2              | Input HIGH voltage, RST                     | VCC = 3.6V                                     | 0.6 VCC<br>-0.4 | VCC + 0.2       | V    |

| VIH3              | Input HIGH voltage, XTAL1                   | VCC = 3.6V                                     | 0.6 VCC         | VCC + 0.2       | V    |

#### With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

|                    |                                             |                                                                                          | -0.4 |     |    |  |  |  |  |  |

|--------------------|---------------------------------------------|------------------------------------------------------------------------------------------|------|-----|----|--|--|--|--|--|

| IIN1               | Input current LOW level Port 1,2,3,4        | $VCC = 3.0V \sim 3.6V,$<br>VIN = 0.45V.                                                  | -10  | 50  | μΑ |  |  |  |  |  |

| ITL                | Transition current High to Low Port 1,2,3,4 | See note 4<br>VCC = 3.6V, VIN = 1.2 V                                                    | -75  | 400 | μΑ |  |  |  |  |  |

| ILI                | Input leakage current P0, /EA               | VCC = 3.0V ~3.6V,<br>0.45V <vin<vcc< td=""><td>-10</td><td>10</td><td>μΑ</td></vin<vcc<> | -10  | 10  | μΑ |  |  |  |  |  |

|                    | OUTPUT                                      |                                                                                          |      |     |    |  |  |  |  |  |

| $V_{OL1}$          | Output Low voltage, Port 0,ALE, /PSEN       | $I_{OL} = 7 \text{mA} \cdot V_{CC} = 3.3 \text{V}$                                       |      | 0.4 | V  |  |  |  |  |  |

| $V_{OL2}$          | Output Low voltage Port 1,2,3,4             | $I_{OL} = 7 \text{mA}$ , $V_{CC} = 3.3 \text{V}$                                         |      | 0.4 | V  |  |  |  |  |  |

| $V_{\mathrm{OH1}}$ | Output High voltage Port0, ALE, /PSEN       | IOH =-300uA , VCC =3.3V                                                                  | 2.4  |     | V  |  |  |  |  |  |

| $V_{\mathrm{OH2}}$ | Output High voltage Port 1,2,3,4            | IOH =-20μA , VCC =3.3V                                                                   | 2.4  |     | V  |  |  |  |  |  |

| $I_{SK1}$          | Sink Current Port 1, 2, 3, 4                | VCC = 3.3V, VIN = 0.4 V                                                                  |      | 6   | mA |  |  |  |  |  |

| $I_{SK2}$          | Sink Current Port 0,ALE, /PSEN              | VCC = 3.3V, VIN = 0.4 V                                                                  |      | 8   | mA |  |  |  |  |  |

| $I_{SR1}$          | Source Current Port 1, 2, 3, 4              | VCC = 3.3V, VIN = 2.4 V                                                                  |      | -80 | uA |  |  |  |  |  |

| $I_{SR2}$          | Source Current Port 0,ALE, /PSEN            | VCC = 3.3V, VIN = 2.4 V                                                                  |      | -8  | mA |  |  |  |  |  |

| R <sub>RST</sub>   | Internal RESET pull-down resistor           |                                                                                          | 50   | 300 | kΩ |  |  |  |  |  |

| $C_{IO}$           | Pin capacitance                             | Test freq=1MHz, TA=25°C                                                                  |      | 10  | pF |  |  |  |  |  |

#### NOTES FOR DC ELECTRICAL CHARACTERISTICS

- 1. The operating supply current is measured with all output disconnected; XTAL1 driven with  $t_r = t_f = 5$ ns;  $V_{IL} = V_{SS} + 0.5V$ ;  $V_{IH} = V_{CC} 0.5V$ ; XTAL2 not connect;/EA=RST=Port0= $V_{CC}$ .

- 2. The IDLE MODE supply current is measured with all output pins disconnected; XTAL1 driven with  $t_r$  =  $t_f$  = 5ns;  $V_{IL}$  =  $V_{SS}$ +0.5V;  $V_{IH}$ = $V_{CC}$ -0.5V; XTAL2 not connect;/EA= Port0= $V_{CC}$ .

- 3. The POWER-DOWN MODE supply current is measured with all output pins disconnected; VIL =  $V_{SS}$ +0.5V;  $V_{IH}$ = $V_{CC}$ -0.5V; XTAL2 not connect; /EA= Port0= $V_{CC}$ .

- 4. Port 1, 2, 3, and 4 sources a transition current when they are being externally driven from HIGH to LOW. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 5. Capacities loading on port 0 and 2 may cause spurious noise to be superimposed on V<sub>OL</sub> of ALE and port 1, 3, and 4. The noise is due to external bus capacitance discharging into port 0 and port 2 pins when these pins make 1-to-0 transitions during bus operations. In the worst cases (capacities loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt trigger STROBE input.

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **AC Characteristic**

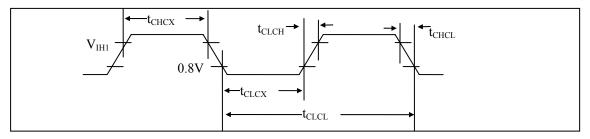

$V_{CC}$ =3.3V±10%,  $V_{SS}$ =0V,  $t_{clk}$  min = 1/  $f_{max}$ (maximum operating frequency)

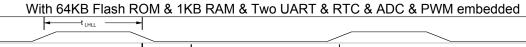

$T_A=-40^{\circ}C$  to  $+85^{\circ}C$

C<sub>L</sub>=100pF for Port0, ALE and /PSEN; C<sub>L</sub>=80pF for all other outputs unless otherwise specified.

| Symbol            | FIGURE | PARAMETER                              | MIN      | MAX | UNIT |

|-------------------|--------|----------------------------------------|----------|-----|------|

|                   |        | External Clock drive into X            | TAL1     | l . |      |

| $t_{CLCL}$        | 4      | Xtal1 Period                           | 62.5 (1) | -   | ns   |

| t <sub>CHCX</sub> | 4      | Xtal1 HIGH time                        | 31       | -   | ns   |

| $t_{CLCX}$        | 4      | Xtal1 LOW time                         | 31       | -   | ns   |

| t <sub>CLCH</sub> | 4      | XTAL1 rise time                        | -        | 15  | ns   |

| $t_{CHCL}$        | 4      | XTAL1 fall time                        | -        | 15  | ns   |

| $t_{\rm CYC}$     | 4      | Controller cycle time = $t_{CLCL} / 4$ | 5.2      | -   | ns   |

# NOTES:

1. Operating at 25MHz.

| Symbol             | FIGURE | PARAMETER                                 | MIN                      | MAX                      | UNIT |

|--------------------|--------|-------------------------------------------|--------------------------|--------------------------|------|

|                    |        | Program Memory                            | •                        |                          |      |

| $1/t_{CLCL}$       | 7      | System clock frequency                    | 3.0                      | 16                       | MHz  |

| $t_{ m LHLL}$      | 7      | ALE pulse width                           | 1.5 t <sub>CLCL</sub> -5 |                          | ns   |

| t <sub>AVLL</sub>  | 7      | Address valid to ALE low                  | 0.5 t <sub>CLCL</sub> -5 |                          | ns   |

| $t_{LLAX}$         | 7      | Address hold after ALE low                | 0.5 t <sub>CLCL</sub> -5 |                          | ns   |

| $t_{LLAX}$         | 8      | Address hold after ALE low for MOVX Write | 0.5 t <sub>CLCL</sub> -5 |                          | ns   |

| $t_{LLIV}$         | 7      | ALE LOW to valid instruction in           |                          | 2.5t <sub>CLCL</sub> -20 | ns   |

| $t_{\rm LLPL}$     | 7      | ALE LOW to /PSEN LOW                      | 0.5 t <sub>CLCL</sub> -5 |                          | ns   |

| $t_{\rm PLPH}$     | 7      | /PSEN pulse width                         | 2.0 t <sub>CLCL</sub> -5 |                          | ns   |

| $t_{PLIV}$         | 7      | /PSEN LOW to valid instruction in         |                          | 2.0t <sub>CLCL</sub> -20 | ns   |

| $t_{PXIX}$         | 7      | Input instruction hold after /PSEN        | 0                        |                          | ns   |

| $t_{PXIZ}$         | 7      | Input instruction float after /PSEN       |                          | t <sub>CLCL</sub> -5     | ns   |

| t <sub>AVIV1</sub> | 7      | Port 0 Address to valid instruction in    |                          | 3.0t <sub>CLCL</sub> -20 | ns   |

| t <sub>AVIV2</sub> | 7      | Port 2 Address to valid instruction in    |                          | 3.5t <sub>CLCL</sub> -20 | ns   |

| $t_{PLAZ}$         | 7      | /PSEN low to address float                | 0                        |                          | ns   |

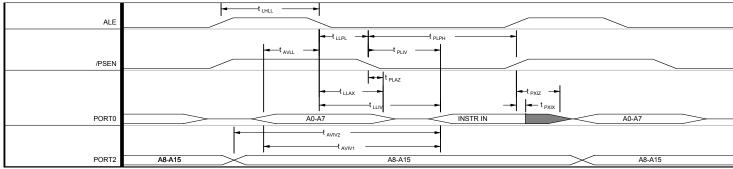

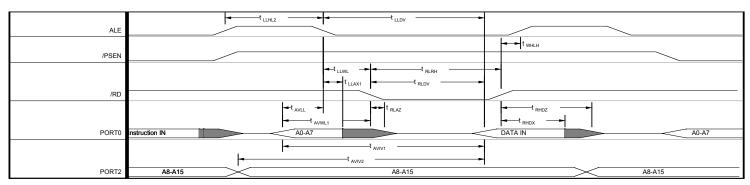

MOVX Characteristics Using Stretch Memory Cycles

| Symbol             | FIGURE | PARAMETER                                 | MIN                      | MAX                       | UNIT | Stretch              |

|--------------------|--------|-------------------------------------------|--------------------------|---------------------------|------|----------------------|

| t <sub>LHLL2</sub> | 8      | ALE pulse width                           | 1.5 t <sub>CLCL</sub> -5 |                           | ns   | $t_{MCS}=0$          |

|                    |        |                                           | 2.0 t <sub>CLCL</sub> -5 |                           |      | $t_{MCS} > 0$        |

| $t_{\rm LLAX2}$    | 9      | Address hold after ALE low for MOVX Write | 0.5 t <sub>CLCL</sub> -5 |                           | ns   |                      |

| $t_{RLRH}$         | 8      | /RD pulse width                           | $2.0 t_{CLCL} - 5$       |                           | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           | $t_{MCS}$ -10            |                           |      | $t_{\text{MCS}} > 0$ |

| $t_{WLWH}$         | 9      | /WR pulse width                           | $2.0 t_{CLCL} - 5$       |                           | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           | $t_{MCS}$ -10            |                           |      | $t_{\text{MCS}} > 0$ |

| $t_{RLDV}$         | 8      | /RD LOW to valid data in                  |                          | $2.0 t_{CLCL} - 20$       | ns   | $t_{MCS} = 0$        |

|                    |        |                                           |                          | t <sub>MCS</sub> -20      |      | $t_{MCS} > 0$        |

| $t_{RHDX}$         | 8      | Data hold after /RD                       | 0                        |                           | ns   |                      |

| $t_{RHDZ}$         | 8      | Data float after /RD                      |                          | t <sub>CLCL</sub> –5      | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           |                          | 2.0 t <sub>CLCL</sub> -5  |      | $t_{MCS} > 0$        |

| $t_{LLDV}$         | 8      | ALE LOW to valid data in                  |                          | 2.5 t <sub>CLCL</sub> -5  | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           |                          | $t_{MCS}+2.0t_{CLCL}-40$  |      | $t_{MCS} > 0$        |

| $t_{AVIV1}$        | 8      | Port 0 Address to valid instruction in    |                          | 3.0 t <sub>CLCL</sub> -20 | ns   | $t_{MCS} = 0$        |

|                    |        |                                           |                          | 2.0 t <sub>CLCL</sub> -5  |      | $t_{MCS} > 0$        |

| $t_{AVIV2}$        | 7,8    | Port 2 Address to valid instruction in    |                          | $3.5 t_{CLCL}$ -20        | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           |                          | 2.5 t <sub>CLCL</sub> -5  |      | $t_{MCS} > 0$        |

| $t_{LLWL}$         | 8,9    | ALE LOW to /RD or /WR LOW                 | $0.5 t_{CLCL} - 5$       | $0.5 t_{CLCL} + 5$        | ns   | $t_{\text{MCS}} = 0$ |

|                    |        |                                           | $1.5 t_{CLCL} - 5$       | 1.5 t <sub>CLCL</sub> +5  |      | $t_{MCS} > 0$        |

| $t_{AVWL1}$        | 8,9    | Port0 Address valid to /WR or /RD LOW     | $t_{CLCL}$ -5            |                           | ns   | $t_{MCS} = 0$        |

|                    |        |                                           | $2.0 t_{CLCL} - 5$       |                           |      | $t_{MCS} > 0$        |

| $t_{AVDV2}$        | 9      | Port2 Address valid to /WR or /RD LOW     | $1.5t_{CLCL}-5$          |                           | ns   | $t_{MCS}=0$          |

# With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

|               |     |                              | 2.5 t <sub>CLCL</sub> -5 |                    |    | $t_{MCS} > 0$        |

|---------------|-----|------------------------------|--------------------------|--------------------|----|----------------------|

| $t_{QVWX}$    | 9   | Data valid to /WR transition | -5                       |                    | ns | $t_{\text{MCS}} = 0$ |

|               |     |                              | 1.0 t <sub>CLCL</sub> -5 |                    |    | $t_{MCS} > 0$        |

| $t_{ m WHQX}$ | 9   | Data hold after /WR          | 1.0 t <sub>CLCL</sub> -5 |                    | ns | $t_{\text{MCS}} = 0$ |

|               |     |                              | 2.0 t <sub>CLCL</sub> -5 |                    |    | $t_{MCS} > 0$        |

| $t_{RLAZ}$    | 8   | /RD LOW to address float     |                          | $0.5 t_{CLCL} - 5$ | ns |                      |

| $t_{ m WHLH}$ | 8,9 | /RD or /WR HIGH to ALE HIGH  | 0                        | 10                 | ns | $t_{\text{MCS}} = 0$ |

|               |     |                              | 1.0 t <sub>CLCL</sub> -5 | $1.0 t_{CLCL} + 5$ |    | $t_{\text{MCS}} > 0$ |

#### **Notes:**

t<sub>MCS</sub> is time period related to the Stretch memory cycle selection. The following table shows the value of t<sub>MCS</sub> for each Stretch selection.

| M2 | M1 | M0 | MOVX Cycles      | $t_{MCS}$            |

|----|----|----|------------------|----------------------|

| 0  | 0  | 0  | 2 machine cycles | 0                    |

| 0  | 0  | 1  | 3 machine cycles | 4 t <sub>CLCL</sub>  |

| 0  | 1  | 0  | 4 machine cycles | 8 t <sub>CLCL</sub>  |

| 0  | 1  | 1  | 5 machine cycles | $12 t_{CLCL}$        |

| 1  | 0  | 0  | 6 machine cycles | 16 t <sub>CLCL</sub> |

| 1  | 0  | 1  | 7 machine cycles | $20 t_{CLCL}$        |

| 1  | 1  | 0  | 8 machine cycles | 24 t <sub>CLCL</sub> |

| 1  | 1  | 1  | 9 machine cycles | $28 t_{CLCL}$        |

| Parameter                             | Figure | Symbol        | Min | Тур                  | Max | Unit |

|---------------------------------------|--------|---------------|-----|----------------------|-----|------|

| Serial Port Clock Cycle Time          | 10     | $t_{ m XLXL}$ |     | 12 t <sub>CLCL</sub> |     | ns   |

| SM2=0,12 clocks per cycle             |        |               |     | $4 t_{CLCL}$         |     | ns   |

| SM2=1,4 clocks per cycles             |        |               |     |                      |     |      |

| Output Data Setup to Clock Rising     | 10     | $t_{QVXH}$    |     | 12 t <sub>CLCL</sub> |     | ns   |

| SM2=0,12 clocks per cycle             |        |               |     | 4 t <sub>CLCL</sub>  |     | ns   |

| SM2=1,4 clocks per cycles             |        |               |     |                      |     |      |

| Output Data Hold to Clock Rising      | 10     | $t_{XHQX}$    |     | 12 t <sub>CLCL</sub> |     | ns   |

| SM2=0,12 clocks per cycle             |        |               |     | $4 t_{CLCL}$         |     | ns   |

| SM2=1,4 clocks per cycles             |        |               |     |                      |     |      |

| Input Data Hold to Clock Rising       | 10     | $t_{XHDX}$    |     | 12 t <sub>CLCL</sub> |     | ns   |

| SM2=0,12 clocks per cycle             |        |               |     | $4 t_{CLCL}$         |     | ns   |

| SM2=1,4 clocks per cycles             |        |               |     |                      |     |      |

| Clock Rising Edge to Input Data Valid | 10     | $t_{XHDV}$    |     | 12 t <sub>CLCL</sub> |     | ns   |

| SM2=0,12 clocks per cycle             |        |               |     | $4 t_{CLCL}$         |     | ns   |

| SM2=1,4 clocks per cycles             |        |               |     |                      |     |      |

Figure 4 External Clock Drive waveform

#### Notes:

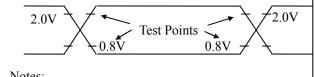

AC inputs during testing are driven at 2.4V for logic "HIGH" and 0.45V for logic "LOW". Timing measurements are at 2.0V for logic "HIGH" and 0.8V for logic "LOW"

Figure 5 AC Testing Input/Output

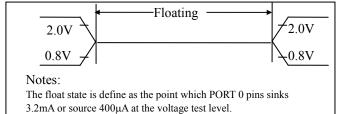

Figure 6 AC Testing, Floating Waveform

Figure 7 External Program Memory Read Cycle

Figure 8 External Data Memory Read cycle

Figure 9 External Data Memory Write cycle

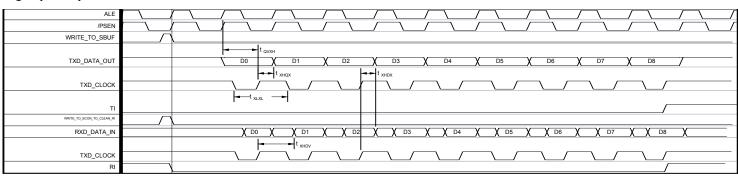

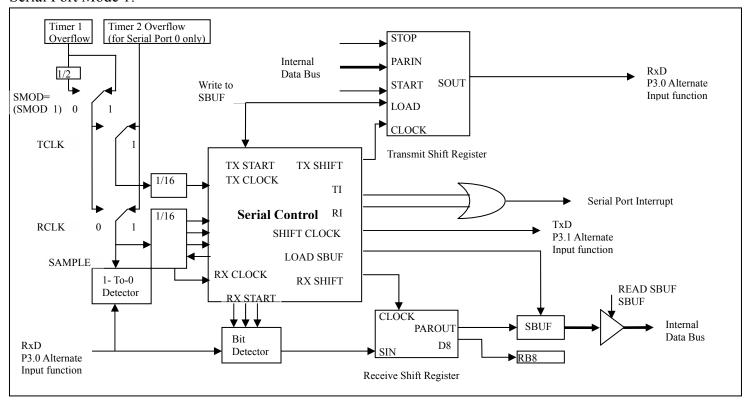

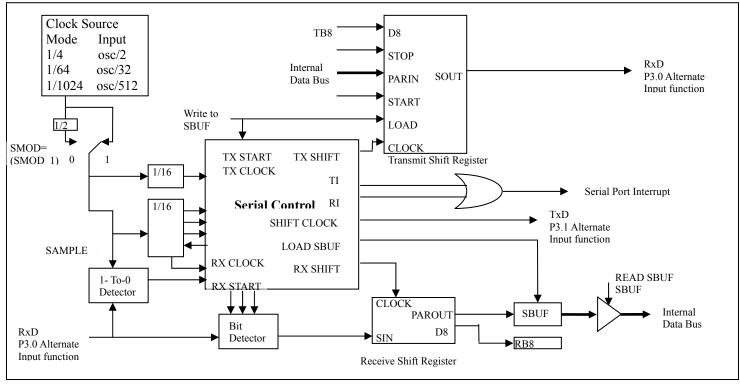

# **UART (Synchronous Mode)**

High Speed Operation SM2=1 => TXD Clock =XTAL/4

Figure 10 UART Mode 1Timing

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **UART (Synchronous Mode)**

SM2=0 => TXD Clock =XTAL/12

Figure 11 UART Mode 0 Timing

# **Function Description**

The SM89T16R1 is a High-Speed (4 clocks/machine cycle) stand-alone high-performance microcontroller designed for use in 3V/5V application, such as LCD monitor, instrumentation, or high-end consumer applications. In addition to the 80C51 standard functions, the device provides a number of dedicated hardware functions for these applications.

The SM89T16R1 is a control-oriented CPU with on-chip program and data memory. It can be extended with external data memory up to 64K bytes. For system requiring extra capability, the SM89T16R1 can be enhanced by using external memory and peripherals.

The SM89T16R1 has two software selectable modes of saving power consumption-IDLE and POWER-DOWN. The IDLE mode freezes the CPU while allowing the RAM, timer, serial ports and interrupt system to continue functioning. The POWER-DOWN mode save the RAM contents but freezes the oscillator causing all other chip functions to be inoperative. The POWER-DOWN mode can be terminated by H/W reset, or by any one of the six external interrupt or RTC function.

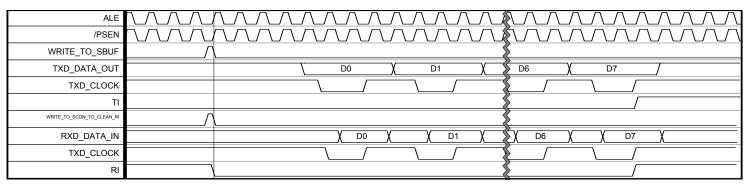

# **CPU**

The CPU of SM89T16R1 is High-Speed 80C51. The structure of this CPU is shown as FIGURE 12. It contains Instruction Register (IR), Instruction Decoder, Program Counter (PC), Accumulator (ACC), B Register, and control logic. This CPU provides an 8-bits bi-direction bus to communicate with other blocks in the chip. The address and data are transferred through on the same 8-bits bus.

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

Figure 12 The CPU Structure

# **CPU Timing**

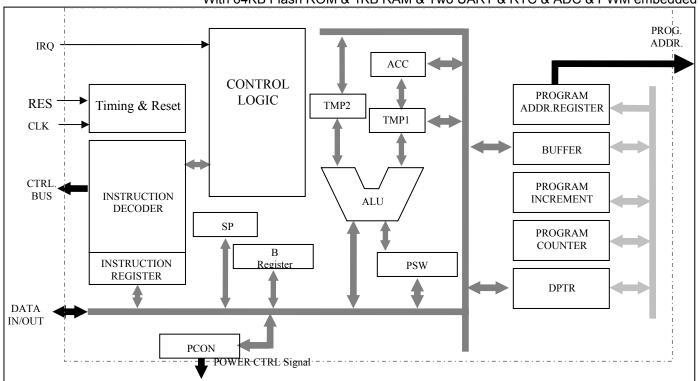

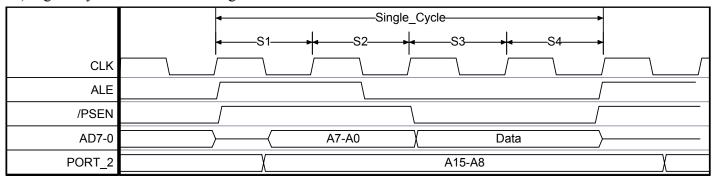

The machine cycle consists of a sequence of 4 states, numbered S1 through S4. Only one-oscillator periods for each state time. Thus a machine cycle takes 4 oscillator periods. FIGURE 13 Shows relationships between oscillator, phase, and S1-S4.

Figure 13 Sequences and Phases

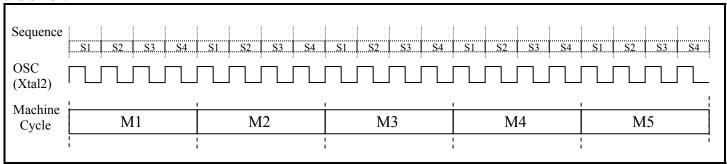

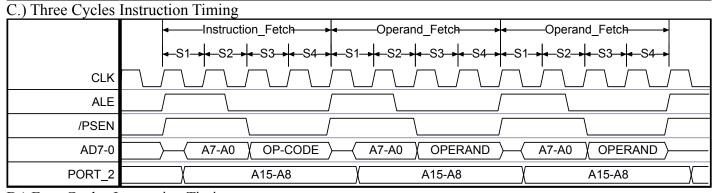

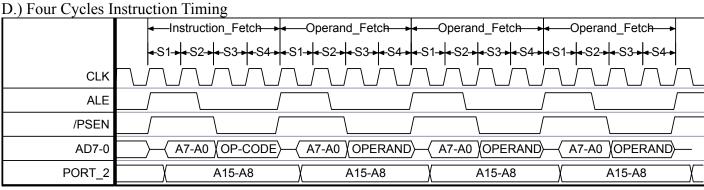

FIGURE 14 shows the fetch / execute sequences in states and phases for various kinds of instructions. Normally the program fetches are generated during each machine cycle, even if the instruction being executed doesn't require it. If the instruction being executed doesn't need more code bytes, the CPU simply ignores the extra fetch, and the PROGRAM COUNTER is incremented accordingly.

Due to the reduced time for each instruction execution, both of the clocks edges are used for internal timing. Hence it is important that the duty cycle of the clock be as close to 50% as possible to avoid timing conflicts. The SM89T16R1 dose one op-code fetch per machine cycle. Therefore, in most of the instructions, the number of machine cycles needed to execute the instruction is equal to the number of bytes in the instruction. Of the 256 available op-codes, 128 of them are signal cycle instruction. See Figure14 shows the different cycle (A-D) instruction timing.

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# A.) Signal Cycle Instruction Timing

# B.) Two Cycles Instruction Timing Instruction\_Fetch Operand\_Fetch S1 S2 S3 S4 S1 S2 S3 S4 CLK ALE /PSEN AD7-0 A7-A0 OP-CODE OP-CODE A7-A0 OP-CODE OP-COD

Figure 14 Timing of various instructions

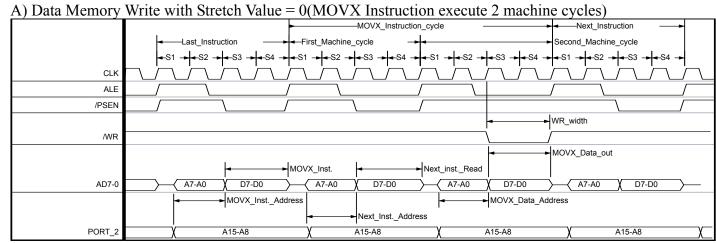

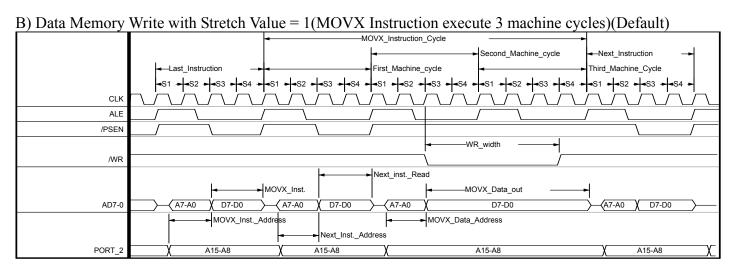

In standard 8032, the MOVX instructions take two machine cycles to execute. However in the SM89T16R1, the user has a facility to stretch the duration of this instruction from 2 machines cycle to 9 machines. The /RD and /WR strobe lines are also proportionately elongated. This gives the user flexibility in accessing both fast and slow peripherals without the use of external circuitry and with minimum software overhead. See FIGURE 15

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

Figure 15: MOVX Instruction Timing (Stretch=0~Stretch=2)

With 64KB Flash ROM & 1KB RAM & Two UART & RTC & ADC & PWM embedded

# **Instruction Set**

The SM89T16R1 is High-Speed 80C51; it's contained 4 clocks per machine. The SM89T16R1 dose one op-code fetch per machine cycle .It consists of 111 instructions used 40 single-cycle, 38 used two-cycles, 19 used three-cycles, and 10 used four-cycles.

A summary of the instruction set is given in Table 4.

# **Addressing Mode**

Notes on instruction set and address modes:

| Rn      | Register R7-R0 of the currently selected register bank.                                                                                                                         |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Direct  | 8-bits internal data location's address. This could be internal DATA RAM location (0-127) or a SFR[i.e., I/O port, control register, status register, etc.(128-255)]            |  |

| @Ri     | 8-bits RAM location addressed indirectly through register R1 or R0 of the actual register bank                                                                                  |  |