## 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE Haus

Rev C1, Page 1/36

#### **FEATURES**

16 bidirectional input/output stages at 24 V Input/output mode programmable in 4-channel blocks Short-circuit-proof high-side drivers with diagnosis function 500 mA pulse and 150 mA permanent load driving capability Active flyback circuit

Load diagnosis for driver current, output voltage and impedance (cable fractures, resistance and short circuits) 10-bit A/D converter for the generation of diagnosis measurement values

Safety devices (voltage monitor, temperature sensor with warning and shutdown features, power output enable pin) Programmable interrupt generation with an events storage facility

Variable digital filters for the debouncing of I/O signals Fast 8-bit parallel or serial SPI™-compatible µC interface permits use in buses

Logic supply from 3 V upwards

#### **APPLICATIONS**

Industrial 24 V applications Lamp switches with diagnostic features

Inductive load driver circuits for relays and valves etc.

#### **PACKAGES**

MQFP52

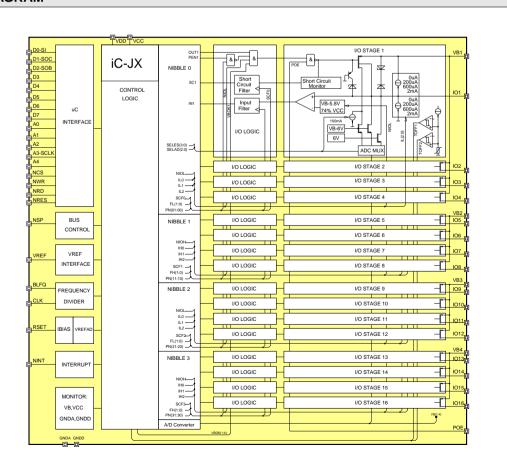

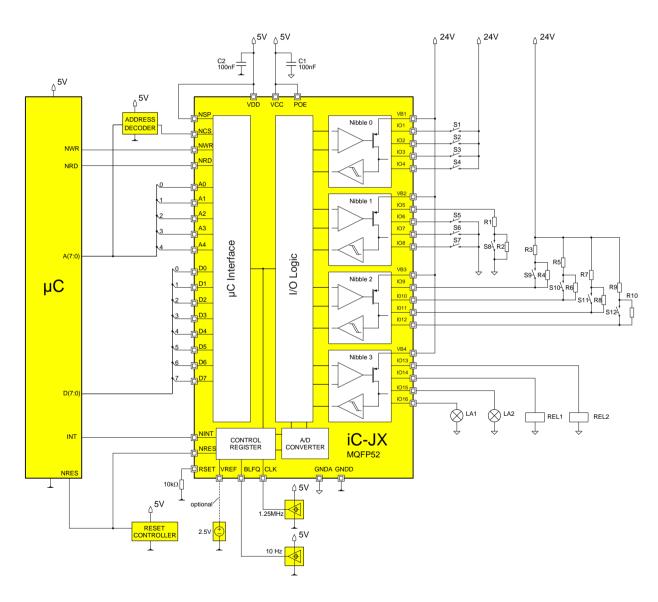

#### **BLOCK DIAGRAM**

Copyright © 2010 iC-Haus http://www.ichaus.com

## 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE Haus

Rev C1, Page 2/36

#### DESCRIPTION

iC-JX is a bidirectional I/O device with 4x4 high-side driver stages. The input or output function can be separately selected for blocks or nibbles of four I/O stages.

Each block can also be individually programmed with various filtering options for the debouncing of I/O pin signals or overcurrent messages, with current sources for the defining of levels at the inputs (lowside sources) or for load diagnosis at the outputs (high-side sources) and also with a flash pulse function.

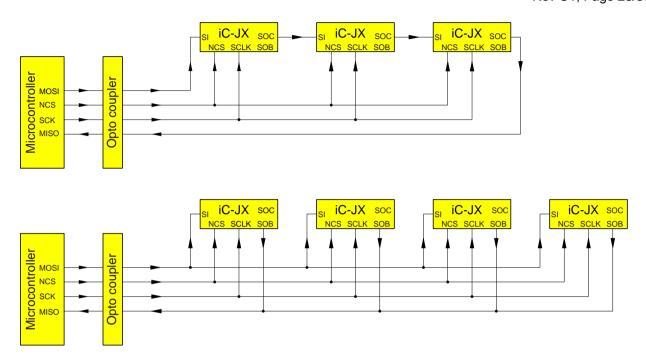

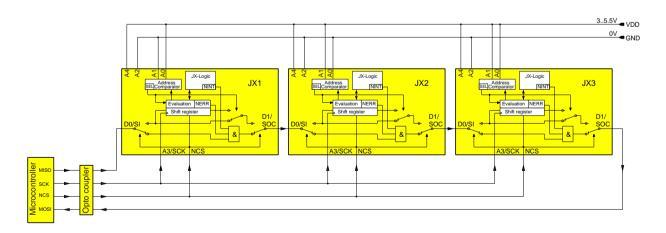

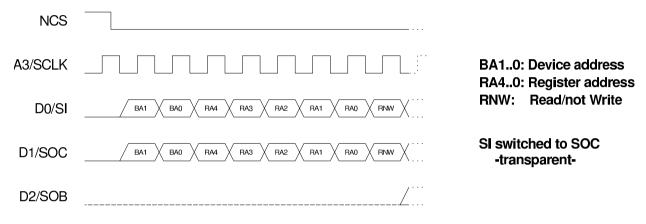

To enable communication with the controller the device includes a parallel interface (with eight data, five address and three control pins) and also an SPIcompatible serial interface (with one pin for the clock, chip selection, data input and data output respectively). The type of interface is selected via pin NSP.

I/O stages with an input function can record logic levels at 24 V where a programmable pull-down current source (of up to 2 mA) either defines the level for open inputs or supplies a bias current for external switch contacts. Connecting safety circuits with integrated serial/parallel resistors to the device also enables leakage currents and short circuits to be pinpointed. The contact status can be read out using the microcontroller interface.

I/O stages with an output function drive various loads (such as lamps, cables or relays, for example) to a common ground with 150 mA of permanent current or 500 mA in pulse operation. Spikes and flyback currents are discharged by the integrated flyback circuits.

For synchronous flash display, as used for indicator lamps in plugboards, for example, a flash pulse enable can be individually set for each output to offload the controller. A common inhibiting input (POE) permits the global shutdown of all outputs and can be operated by an autonomous watchdog circuit.

All output stages are short-circuit-proof and protected against thermal destruction in the event of extreme power dissipation. Each stage has its own temperature sensor which is evaluated in two stages and generates interrupt messages for the controller. The latter is warned before the device is forcibly shutdown. A short circuit also triggers an interrupt message; the current status here can be read out by the controller.

For the purpose of load diagnosis a programmable pull-up current source (of up to 2 mA) can be used to determine an initial load breakage or open loop (caused by a fractured cable, for example) before an output is switched on. The I/O pin status can always be read back via comparators. A load current measurement circuit then permits the load to be assessed; failed valves and faulty or wrongly implemented indicator lamps can be verified in this way. In addition, the analog measurement of voltage at the I/O pins allows safety switches to be analyzed with reference to ground, here without the driver function.

All analog measurements for the load current (per stage), for the I/O pin voltage (per stage, either referenced to Ground or VB), for the driver supply (all VB pins), for the internal voltage reference (VBG) and for the chip temperature are made available to the microcontroller as digital measurements by an integrated A/D converter which has 10 bits of resolution.

An interrupt pipeline which limits the loss of interrupts allows reliable processing of interrupts by the microcontroller. Registers provide information as to current events; messages can be individually enabled for all available interrupt sources.

iC-JX monitors all supply voltages and also the GNDD-GNDA connection to ground.

Monitored separately, undervoltage in the range of 2.5V at analog supply VCC or even short disruption of digital supply VDD causes all registers to be reset and the output stages to be shutdown.

Undervoltage at 24 V driver supply VB triggers a shutdown of the output stages without deleting the contents of the registers.

Diodes protect all inputs and outputs against destruction by ESD. iC-JX is also immune to burst transients according to IEC 1000-4-4 (4 kV; previously IEC 801-4).

## 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE Haus

**PIN FUNCTIONS**

22 1011

23 VB3

24 IO10

27 NINT

28 D0

29 D2

30 D4

31 D6

32 A0

33 A2

34 A4

35 VDD

37 BLFQ

39 CLK

41 IO1

42 IO2

36 NRES Not Reset

38 GNDD Ground (logic)

40 GNDA Ground (analog)

I/O Stage

I/O Stage

25 109

No. Name Function

I/O Stage

I/O Stage

I/O Stage 26 GNDA Ground (analog)

Data Bus

Data Bus

Data Bus

Data Bus

Adress Bus

Adress Bus

Adress Bus

Blink Frequency

Clock (optional)

Not Interrupt

Supply Voltage for I/O Stages 9...12

Supply Voltage (logic, 3...5.5 V)

Rev C1, Page 3/36

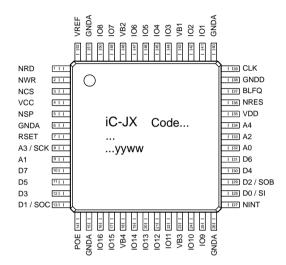

#### **PACKAGES MQFP52 to JEDEC Standard**

#### **PIN CONFIGURATION** MQFP52, pitch 0.65 mm

Orientation of the package label ( JX code...) is subject to change.

|     |       |                                    | :- |      | a consigo                             |

|-----|-------|------------------------------------|----|------|---------------------------------------|

|     |       |                                    | 43 | VB1  | Supply Voltage for I/O Stages 14      |

|     | FUNCT |                                    | 44 | IO3  | I/O Stage                             |

| No. | Name  | Function                           | 45 | IO4  | I/O Stage                             |

| 1   | NRD   | Not Read Enable                    | 46 | IO5  | I/O Stage                             |

| 2   | NWR   | Not Write Enable                   | 47 | 106  | I/O Stage                             |

| 3   | NCS   | Not Chip Select                    | 48 | VB2  | Supply Voltage for I/O Stages 58      |

| 4   | VCC   | Supply Voltage (analog, 35.5 V)    | 49 | 107  | I/O Stage                             |

| 5   | NSP   | Not Serial / Parallel (Mode)       | 50 | IO8  | I/O Stage                             |

| 6   | GNDA  | Ground (analog)                    | 51 | GNDA | Ground (analog)                       |

| 7   | RSET  | Resistor Setting (10 kΩ optional)  |    |      | External Voltage Reference (optional) |

| 8   | A3    | Adress Bus                         |    |      |                                       |

| 9   | A1    | Adress Bus                         |    |      | Additional Pin Function in SPI Mode   |

| 10  | D7    | Data Bus                           |    |      | (NSP = low)                           |

| 11  | D5    | Data Bus                           |    |      |                                       |

| 12  | D3    | Data Bus                           | 3  | NCS  | Not Chip Select                       |

| 13  | D1    | Data Bus                           |    | SCK  | Serial Clock                          |

| 14  | POE   | Power Output Enable                | 9  | A1   | Device ID Bit 1                       |

| 15  | GNDA  | Ground (analog)                    | 13 | SOC  | Serial Out Chain                      |

| 16  | IO16  | I/O Stage                          | 28 | SI   | Serial In                             |

| 17  | IO15  | I/O Stage                          | 29 | SOB  | Serias Out Bus                        |

| 18  | VB4   | Supply Voltage for I/O Stages 1316 | 32 | A0   | Device ID Bit 0                       |

| 19  | IO14  | I/O Stage                          | 33 | A2   | Select Chain / Bus                    |

| 20  | IO13  | I/O Stage                          |    | A4   | Enable Interrupt Report SOC/SOB       |

| 21  | IO12  | I/O Stage                          |    |      |                                       |

|     |       |                                    |    |      |                                       |

Separate supply voltages at VB1..4 are possible. All GNDA pins must be connected up externally. GNDA must be connected to GNDD externally when just one voltage supply is available. VCC and VDD can be powered either mutually or separately.

## 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE Haus

Rev C1, Page 4/36

#### **ABSOLUTE MAXIMUM RATINGS**

Beyond these values damage may occur; device operation is not guaranteed. Absolute Maximum Ratings are no Operating Conditions. Integrated circuits with system interfaces, e.g. via cable accessible pins (I/O pins, line drivers) are per principle endangered by injected interferences, which may compromise the function or durability. The robustness of the devices has to be verified by the user during system development with regards to applying standards and ensured where necessary by additional protective circuitry. By the manufacturer suggested protective circuitry is for information only and given without responsibility and has to be verified within the actual system with respect to actual interferences.

(Legend: x = 1..16, y = 1..4)

| Item | Symbol    | Parameter                                                                                                             | Conditions                                                                                                     |      |      | Unit |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|

| No.  |           |                                                                                                                       |                                                                                                                | Min. | Max. |      |

| G001 | VCC, VDD  | Supply Voltage                                                                                                        |                                                                                                                | -0.3 | 6    | V    |

| G002 | VBy       | Driver Supply Voltage                                                                                                 |                                                                                                                | -0.3 | 40   | V    |

| G003 | V(IOx)    | Voltages at IO116                                                                                                     | IOx = off; see additional remark <sup>1</sup>                                                                  | -10  | 40   | V    |

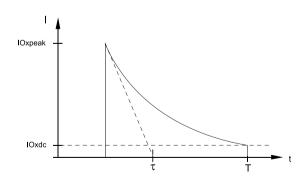

| G004 | Idc(IOx)  | Current in IO116                                                                                                      | see Figure 1                                                                                                   | -500 | 150  | mA   |

| G005 | lpk(IOx)  | Pulse current in IO116                                                                                                | $\begin{aligned} &\text{IOx = hi, } \tau = 2\text{ms, T} \leq 2\text{s} \\ &\text{see Figure 2} \end{aligned}$ | -1.0 |      | Α    |

| G006 | lmax()    | Current in VCC, VDD                                                                                                   |                                                                                                                | -100 | 100  | mA   |

| G007 | Imax(VBy) | Current in VB14                                                                                                       |                                                                                                                | -8   | 8    | Α    |

| G008 | Ic()      | Current in NCS, NWR, NRD, A04,<br>D07, NRES, CLK, BLFQ, POE, NSP,<br>RSET, VREF                                       | D07 with input function                                                                                        | -20  | 20   | mA   |

| G009 | I()       | Current in D07, NINT,                                                                                                 | D07 with output function                                                                                       | -25  | 25   | mA   |

| G010 | llu()     | Pulse current in NCS, NWR, NRD,<br>A04, D07, NRES, CLK, BLFQ,<br>NINT, NSP, POE, IO116, RSET,<br>VREF (latch up test) | Pulse width < 10 µs,<br>all inputs / outputs open                                                              | -100 | 100  | mA   |

| G011 | Vd()      | ESD-voltage, all pins                                                                                                 | HBM 100 pF discharged over 1.5 kΩ                                                                              |      | 2    | kV   |

| G012 | Vb()      | Burst transients at IO116                                                                                             | after IEC 1000-4-4                                                                                             |      | 4    | kV   |

| G013 | Tj        | Chip temperature                                                                                                      |                                                                                                                | -40  | 150  | °C   |

| G014 | Ts        | Storage temperature                                                                                                   |                                                                                                                | -40  | 150  | °C   |

<sup>1)</sup> If the voltage supplies can not be guaranteed to be present at the time signals appear at the pins IO1..IO16, additional diodes or sufficient current limiting ohmic resistors have to be connected in series to the IO-pins to prevent reverse back biasing of the device.

#### THERMAL DATA

Operating conditions: VCC = VDD = 3 ... 5.5 V, VBy = 12 ... 36 V, GNDA = GNDD = 0 V, all inputs on defined logic states (high or low)

| Item | Symbol | Parameter                       | Conditions                            |      |      |      | Unit |

|------|--------|---------------------------------|---------------------------------------|------|------|------|------|

| No.  |        |                                 |                                       | Min. | Тур. | Max. |      |

| T01  | Та     | Ambient temperature             | extended temperature range on request | -40  |      | 85   | °C   |

| T02  | Rthja  | Thermal resistance chip/ambient | package mounted on PCB                |      | 55   |      | K/W  |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol     | Parameter                                                                                 | Conditions                                                                                         | Min. | Тур. | Max.  | Unit |

|-------------|------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|------|-------|------|

| Gene        | ral        |                                                                                           |                                                                                                    | "    |      |       |      |

| 001         | VCC        | Permissible Supply Voltage VCC                                                            |                                                                                                    | 3    |      | 5.5   | V    |

| 002         | I(VCC)     | Supply Current in VCC                                                                     |                                                                                                    |      | 10   | 20    | mA   |

| 003         | I(VCC)     | Supply Current in VCC                                                                     | no supply voltage VBy                                                                              |      |      | 30    | mA   |

| 004         | VDD        | Permissible Supply Voltage VDD                                                            |                                                                                                    | 3    |      | 5.5   | V    |

| 005         | I(VDD)     | Supply Current in VDD (static)                                                            | all logic inputs lo = 0 V or hi=VDD                                                                |      | 3    | 6     | mA   |

| 006         | I(VDD)     | Supply Current in VDD (dynamic)                                                           | continuous reading cycle all 200ns, data word '00' and 'FF' is alternating read, CL(D0 7) = 200 pF |      |      | 30    | mA   |

| 007         | I(VDD)     | Supply Current in VDD                                                                     | all logic inputs lo=0.8V                                                                           |      | 3    |       | mA   |

| 800         | I(VDD)     | Supply Current in VDD                                                                     | all logic inputs hi=2.0V                                                                           |      | 5    |       | mA   |

| 009         | VBy        | Permissible Supply Voltage VB14 (operating range)                                         |                                                                                                    | 12   |      | 36    | V    |

| 010         | I(VBy)     | Supply Current in VB14                                                                    | POE = hi, IOx = hi, unbelastet                                                                     |      | 7    | 20    | mA   |

| 011         | I(VBy)     | Supply Current in VB14                                                                    | IOx = off                                                                                          |      | 5    | 10    | mA   |

| 012         | Vc()lo     | ESD Clamp Voltage lo<br>at VCC, VDD, VB14, RSET,<br>VREF                                  | I() = -10 mA                                                                                       | -1.4 |      | -0.3  | V    |

| 013         | Vc()hi     | ESD Clamp Voltage hi at VCC, VDD                                                          | I() = 10 mA                                                                                        | 6    |      |       | V    |

| 014         | Vc()hi     | ESD Clamp Voltage hi at VB14                                                              | I() = 10 mA                                                                                        | 30   |      | 55    | V    |

| 015         | Vc()lo     | ESD Clamp Voltage lo at IO116                                                             | I() = 10  mA, IOx = off                                                                            | -25  |      | -19   | V    |

| 016         | Vc()lo     | ESD Clamp Voltage hi at IO116                                                             | I() = 10 mA                                                                                        | 30   |      | 55    | V    |

| 017         | Vc()hi     | ESD Clamp Voltage hi at<br>NCS, NWR, NRD, A04, NRES,<br>CLK, BLFQ, D07, NINT, POE,<br>NSP | Vc()hi = V() - VDD,<br>D07 as input,<br>I() = 10 mA                                                | 0.4  |      | 1.5   | V    |

| 018         | Vc()lo     | ESD Clamp Voltage lo at<br>NCS, NWR, NRD, A04, NRES,<br>CLK, BLFQ, D07, NINT, POE,<br>NSP | D07 as input,<br>I() = -10 mA                                                                      | -1.5 |      | -0.4  | V    |

| 019         | Ifl(IOx)   | Leakage Current of I/O Pins (x=116) beyond operating conditions                           | VCC = 0 V and VDD = 0 V,<br>VBy = 230 V)                                                           | -0.2 |      |       | mA   |

| I/O St      | ages: High | -Side Driver IO116                                                                        |                                                                                                    | "    |      |       | u    |

| 101         | Vs()hi     | Saturation Voltage hi                                                                     | Vs()hi = VBy - V(IOx), I(IOx) = -15 mA;<br>see Fig. 1                                              |      |      | 0.2   | V    |

| 102         | Vs()hi     | Saturation Voltage hi                                                                     | Vs()hi = VBy - V(IOx), I(IOx) = -150 mA;<br>see Fig. 1                                             |      |      | 0.6   | V    |

| 103         | Vs()hi     | Saturation Voltage hi for pulse load                                                      | Vs()hi = VBy -V(IOx), I(IOx)= -500 mA, $\tau$ = 2 ms, T $\leq$ 2 s; see Fig. 2                     |      |      | 2     | V    |

| 104         | Isc()hi    | Overcurrent Cut-off                                                                       | V(IOx) = 0 VBy - 3 V                                                                               | -1.6 |      | -0.51 | Α    |

| 105         | It()scs    | Threshold Current for Overcur-<br>rent Message                                            |                                                                                                    | -1.2 |      | -0.51 | А    |

| 106         | Vc()lo     | Free-wheeling Clamp Voltage low                                                           | , ,                                                                                                | -18  |      | -12   | V    |

| 107         | SR()hi     | Slew Rate hi                                                                              | CL = 0 100 pF, I(IOx) = -150mA                                                                     | 5    |      | 17    | V/µs |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 6/36

#### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol      | Parameter                                     | Conditions                                                                                                                   | Min. | Тур. | Max. | Unit |

|-------------|-------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 108         | SR()lo      | Slew Rate lo                                  | CL = 0 100 pF, I(IOx) = -150mA                                                                                               | 5    |      | 17   | V/µs |

| 109         | tplh()      | Propagation Delay until IOx: lo → hi          | V(IOx) > V0(IOx) + 1 V                                                                                                       |      |      | 6    | μs   |

| 110         | tphl()      | Propagation Delay until IOx = off             | V(IOx) < 80 % (VBy - Vs(IOx)hi)                                                                                              |      |      | 6    | μs   |

| I/O Sta     | ages: Curre | nt Sources at IO116                           |                                                                                                                              |      |      |      |      |

| 201         | lpd()       | Pull-down Current Source<br>(200 µA)          | V(IOx) = 3 V VBy;                                                                                                            | 160  | 200  | 240  | μА   |

| 202         | lpd()       | Pull-down Current Source<br>(600 µA)          | V(IOx) = 3 V VBy;                                                                                                            |      | 600  | 690  | μА   |

| 203         | lpd()       | Pull-down Current Source (2 mA)               | V(IOx) = 3 V VBy;                                                                                                            | 1.6  | 2    | 2.4  | mA   |

| 204         | lpu()       | Pull-up Current Source (200 µA)               | IOx = off, V(IOx) = 0 V VBy - 3 V                                                                                            | 150  | 200  | 250  | μΑ   |

| 205         | lpu()       | Pull-up Current Source (600 μA)               | IOx = off, V(IOx) = 0 V VBy - 3 V                                                                                            | 510  | 600  | 690  | μA   |

| 206         | lpu()       | Pull-up Current Source (2 mA)                 | IOx = off, V(IOx) = 0 VVBy - 3 V                                                                                             | 1.6  | 2    | 2.4  | mA   |

| 207         | tp()lon     | Turn-on Time<br>Current Source aktiv          | I(IOx) > 90 % lpd(IOx) resp.<br>I(IOx) > 90 %lpu(IOx)                                                                        |      |      | 5    | μs   |

| 208         | tp()loff    | Turn-off Time<br>Current Source inaktiv       | I(IOx) < 10 % lpd(IOx) resp.<br>I(IOx) < 10 % lpu(IOx)                                                                       |      |      | 5    | μs   |

| 209         | lfu()       | Leakage Current                               | IOx with Input Function or Output Function with IOx = off; VBy = 30 V IL2 = IH2 = IL1 = IH1 = IL0 = IH0 = 0, V(IOx) = 0V VBy | -50  |      | 70   | μA   |

| 210         | Irb()       | Leakage Current                               | Conditions see Item-No. 209;<br>V(IOx) = -10 V 0 V, VBy = 30 V                                                               |      |      |      | mA   |

| 211         | Irb()       | Leakage Current                               | Conditions see Item-No. 209; only Input Function V(IOx) = VBy VBy + 0.3 V                                                    |      |      | 250  | μА   |

| 212         | lrb()       | Leakage Current                               | Conditions see Item-No. 209; only Input Function<br>V(IOx) = VBy + 0.3V VBy + 2V                                             |      |      | 1    | mA   |

| 213         | Irb()       | Leakage Current                               | no supply voltages VBy<br>V(IO) <sub>max</sub> = 36V                                                                         |      |      | 5    | mA   |

| I/O Sta     | ges: Comp   | arator IO 116                                 |                                                                                                                              |      |      |      |      |

| 301         | Vt()hi      | Threshold voltage hi                          | IOx with input function                                                                                                      |      |      | 82   | %VCC |

| 302         | Vt()lo      | Threshold voltage lo                          | IOx with input function                                                                                                      | 66   |      |      | %VCC |

| 303         | Vt()hys     | Hysteresis                                    | IOx with input function, Vt()hys = Vt()hi - Vt()lo                                                                           | 100  |      |      | mV   |

| 304         | Vt()hi      | Threshold voltage hi referenced to VBy        | IOx with output function, Vt()hi = VBy - V(IOx)                                                                              | 5.0  |      |      | V    |

| 305         | Vt()lo      | Threshold voltage lo referenced to VBy        | IOx with output function, Vt()Io = VBy - V(IOx)                                                                              |      |      | 6.7  | V    |

| 306         | Vt()hys     | Hysteresis                                    | IOx with output function, Vt()hys = Vt()lo - Vt()hi                                                                          | 100  |      |      | mV   |

| 307         | tp(IOx-Dx)  | Propagation Delay Input IOx to Data Output Dx | I/O-Filter inaktive                                                                                                          |      |      | 20   | μs   |

| Therm       | al Shutdow  | n                                             |                                                                                                                              |      |      |      |      |

| 401         | Toff1       | Overtemperatur threshold level 1: warning     |                                                                                                                              | 120  |      | 145  | °C   |

| 402         | Ton1        | Level 1 Release                               |                                                                                                                              | 115  |      | 140  | °C   |

| 403         | Thys1       | Level 1 Hysteresis                            | Thys1 = Toff1 - Ton1                                                                                                         | 2    |      | 7    | °C   |

| 404         | Toff2       | Overtemperatur threshold level 2: shutdown    |                                                                                                                              | 140  |      | 165  | °C   |

| 405         | Ton2        | Level 2 Release                               |                                                                                                                              | 120  |      | 145  | °C   |

| 406         | Thys2       | Level 2 Hysteresis                            | Thys2 = Toff2 - Ton2                                                                                                         |      |      | 35   | °C   |

| 407         | ΔΤ          | Temperature Difference Level 2 to Level 1     | $\Delta T = Toff2 - Toff1$                                                                                                   | 13   |      | 35   | °C   |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 7/36

#### **ELECTRICAL CHARACTERISTICS**

| ltem<br>No. | Symbol              | Parameter                                                    | Conditions                                                                                                                                                                    | Min.              | Тур.                       | Max.              | Unit   |

|-------------|---------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------|-------------------|--------|

| Bias a      | and Low Vo          | Itage Detection                                              |                                                                                                                                                                               | "                 |                            |                   |        |

| 501         | VCCon,<br>VDDon     | Turn-on Threshold VCC, VDD (Power-on release)                |                                                                                                                                                                               | 2.4               | 2.6                        | 2.9               | V      |

| 502         | VCCoff,<br>VDDoff   | Undervoltage Threshold VCC,<br>VDD (Power-down reset)        |                                                                                                                                                                               | 2.3               | 2.5                        | 2.8               | V      |

| 503         | VCChys,<br>VDDhys   | Hysteresis                                                   | VCChys = VCCon - VCCoff,<br>VDDhys = VDDon - VDDoff                                                                                                                           | 60                | 100                        | 140               | mV     |

| 504         | tmin()lv            | Power Down Time required for low voltage detection           | VCC = 0.8 V VCCoff,<br>VDD = 0.8 V VDDoff                                                                                                                                     | 1                 |                            |                   | μs     |

| 505         | tpoff               | Propagation Delay until Reset after Low Voltage at VCC, VDD  |                                                                                                                                                                               |                   |                            | 12                | μs     |

| 506         | Vrefad              | Reference Voltage for A/D-<br>Converter                      |                                                                                                                                                                               | 2.6               | 2.75                       | 3.0               | V      |

| A/D-C       | onverter            |                                                              |                                                                                                                                                                               |                   |                            |                   |        |

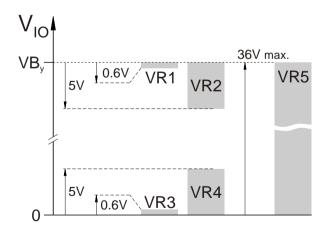

| 701         | VR1                 | ADC - Measurement Range 1                                    | Current and voltage measurement High at IO, SELAD = '0b001' resp. '0b010', EME = 0                                                                                            | VBy -<br>0.6 V    |                            | VBy               | V      |

| 702         | VR2                 | ADC - Measurement Range 2                                    | Voltage measurement High at IO,<br>SELAD = '0b010', EME = 1                                                                                                                   | VBy -<br>5V       |                            | VBy               | V      |

| 703         | VR3                 | ADC - Measurement Range 3                                    | Voltage measurement Low at IO, SELAD = '0b100', EME = 0                                                                                                                       | 0                 |                            | 0.6               | V      |

| 704         | VR4                 | ADC - Measurement Range 4                                    | Voltage measurement Low at IO SELAD = '0b100'; VB or VBG measurement SELAD = '0b101' or. '0b110', EME = 1                                                                     | 0                 |                            | 5                 | V      |

| 705         | VR5                 | ADC - Measurement Range 5                                    | Total voltage measurement range SELAD = '0b011'                                                                                                                               |                   |                            | VB                | V      |

| 706         | VR6                 | ADC - Measurement Range 6                                    | Temperature measurement SELAD = '0b111'                                                                                                                                       | -40               |                            | 125               | °C     |

| 707         | Vbitlo              | Bit-Equivalent of voltage                                    | EME = 0                                                                                                                                                                       |                   | 0.6                        |                   | mV     |

| 708         | Vbithi              | Bit-Equivalent of voltage                                    | EME = 1                                                                                                                                                                       |                   | 5.4                        |                   | mV     |

| 709         | Dtemp1              | Digital value of temperature measurement 1                   | SVREF = 0, TEMP = (774-Dtemp1)/TKtemp1<br>Tj = -40°C<br>Tj = 27°C<br>Tj = 95°C                                                                                                | 826<br>670<br>519 | 863<br>712<br>563          | 900<br>755<br>608 |        |

| 710         | TKtemp1             | Temperature coefficient 1                                    | SVREF = 0                                                                                                                                                                     | 2.16              | 2.22                       | 2.27              | 1/°C   |

| 711         | Dtemp2              | Digital value of temperature measurement 2                   | SVREF = 1, V(VREF) = 2.5V ±0.2%<br>TEMP = (861-Dtemp2)/TKtemp2<br>Tj = -40°C<br>Tj = 27°C<br>Tj = 95°C                                                                        | 931<br>761<br>585 | 957<br>800<br>632          | 984<br>839<br>679 |        |

| 712         | TKtemp2             | Temperature coefficient 2                                    | SVREF = 1, V(VREF) = 2.5V ±0.2%                                                                                                                                               | 2.26              | 2.41                       | 2.55              | 1/°C   |

| 713         | f <sub>ICLK</sub>   | Internal oscillating frequency                               |                                                                                                                                                                               | 0.9               | 1.25                       | 1.5               | MHz    |

| 714         | t <sub>SAR1</sub>   | Conversion time SAR-converter 1                              | SELAD = '0b001'                                                                                                                                                               |                   | 154 /<br>f <sub>ICLK</sub> |                   | μs     |

| 715         | t <sub>SAR2</sub>   | Conversion time SAR-converter 2                              | SELAD = '0b010' resp. '0b100'                                                                                                                                                 |                   | 90 /<br>f <sub>ICLK</sub>  |                   | μs     |

| 716         | t <sub>SAR3</sub>   | Conversion time SAR-converter 3                              | Total voltage measurement SELAD = '0b011';<br>VBy voltage measurement SELAD = '0b101';<br>VBG voltage measurement SELAD = '0b110';<br>temperature measurement SELAD = '0b111' |                   | 26 /<br>f <sub>ICLK</sub>  |                   | μs     |

| 717         | D <sub>VBG,1</sub>  | Digital value of VBG measure-<br>ment (external reference)   | SELAD = '0b110', SVREF = 1                                                                                                                                                    | 480               | 520                        | 560               |        |

| 718         | D <sub>VBY,1</sub>  | Digital value of VBy measure-<br>ment (external reference)   | SVREF = 1, V(VBy) = 36 V, SELAD = '0b101'                                                                                                                                     | 940               | 990                        | 1022              |        |

| 719         | DR <sub>VBY,1</sub> | Relative value of VBy<br>measurement<br>(external reference) | SVREF = 1; DR <sub>VBY,1</sub> = D <sub>VBY,1</sub> (V) / D <sub>VBY,1</sub><br>V(VBy) = 24 V, SELAD = '0b101'<br>V(VBy) = 12 V, SELAD = '0b101'                              | 64.6<br>31.3      | 66.6<br>33.3               | 68.6<br>35.2      | %<br>% |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 8/36

#### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol              | Parameter                                                   | Conditions                                                                                                                                                                                                                                                                   | Min.         | Тур.         | Max.         | Unit   |

|-------------|---------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------|

| 720         | D1 <sub>IO,1</sub>  | Digital value using VR1 range (external reference)          | SELAD = '0b010', EME = '0b0', SVREF = 1,<br>V(IOx) = V(VBy) - 0.6V                                                                                                                                                                                                           | 840          | 900          | 1022         |        |

| 721         | DR1 <sub>IO,1</sub> | Digital relative value using VR1 range (external reference) | $ \begin{array}{l} \text{SELAD = '0b010', EME = '0b0', SVREF = 1;} \\ \text{DR1}_{\text{IO,1}} = \text{D1}_{\text{IO,1}}(\text{V}) / \text{D1}_{\text{IO,1}}; \\ \text{V(IOx)} = \text{V(VBy)} - 0.3\text{V} \\ \text{V(IOx)} = \text{V(VBy)} - 0.1\text{V} \\ \end{array} $ | 46<br>12     | 49<br>15     | 52<br>18     | %<br>% |

| 722         | D2 <sub>IO,1</sub>  | Digital absolute value using VR2 range (external reference) | SELAD = '0b010', EME = '0b1', SVREF = 1,<br>V(IOx) = V(VBy) - 5.0 V                                                                                                                                                                                                          | 870          | 930          | 1022         |        |

| 723         | DR2 <sub>IO,1</sub> | Digital relative value using VR2 range (external reference) | $ \begin{aligned} & \text{SELAD = '0b010', EME = '0b1', SVREF = 1;} \\ & \text{DR2}_{\text{IO,1}} & = \text{D2}_{\text{IO,1}}(\text{V}) / \text{D2}_{\text{IO,1}}; \\ & \text{V(IOx) = V(VBy)} - 2.5  \text{V} \\ & \text{V(IOx) = V(VBy)} - 0.6  \text{V} \end{aligned} $   |              | 50<br>11.5   | 52<br>14     | %<br>% |

| 724         | D3 <sub>IO,1</sub>  | Digital absolute value using VR3 range (external reference) | SELAD = '0b100', EME = '0b0', SVREF = 1,<br>V(IOx) = 0.6 V;                                                                                                                                                                                                                  | 880          | 940          | 1022         |        |

| 725         | DR3 <sub>IO,1</sub> | Digital relative value using VR3 range (external reference) | SELAD = '0b100', EME = '0b0', SVREF = 1;<br>DR3 <sub>IO,1</sub> = D3 <sub>IO,1</sub> (V) / D3 <sub>IO,1</sub> ;<br>V(IOx) = 0.3 V<br>V(IOx) = 0.1 V                                                                                                                          |              | 50<br>16     | 52<br>18.5   | %<br>% |

| 726         | D4 <sub>IO,1</sub>  | Digital absolute value using VR4 range (external reference) | SELAD = '0b100', EME = '0b1', SVREF = 1;<br>V(IOx) = 5.0V                                                                                                                                                                                                                    | 870          | 930          | 1022         |        |

| 727         | DR4 <sub>IO,1</sub> | Digital relative value using VR4 range (external reference) | SELAD = '0b100', EME = '0b1', SVREF = 1;<br>DR4 <sub>IO,1</sub> = D4 <sub>IO,1</sub> (V) / D4 <sub>IO,1</sub><br>V(IOx) = 2.5V<br>V(IOx) = 0.6V<br>48<br>9.5                                                                                                                 |              | 50<br>11.5   | 52<br>14     | %<br>% |

| 728         | D5 <sub>IO,1</sub>  | Digital absolute value using VR5 range (external reference) | SELAD = '0b011', SVREF = 1, V(IOx) = 36.0V                                                                                                                                                                                                                                   | 930          | 980          | 1022         |        |

| 729         | DR5 <sub>IO,1</sub> | Digital relative value using VR5 range (external reference) | SELAD = '0b011', SVREF = 1;<br>DR5 <sub>IO,1</sub> = D5 <sub>IO,1</sub> (V) / D5 <sub>IO,1</sub><br>V(IOx) = 24.0V<br>V(IOx) = 5.0V                                                                                                                                          | 64.6<br>11.8 | 66.6<br>13.8 | 68.6<br>15.8 | %<br>% |

| 730         | DC <sub>IO,1</sub>  | Digital value of current measurement (external reference)   | SELAD = '0b001', SVREF = 1, I(IOx) = 150mA                                                                                                                                                                                                                                   | 700          | 800          | 1022         |        |

| 731         | DRC <sub>IO,1</sub> | Relative value of current measurement (external reference)  | SELAD = '0b001', SVREF = 1;<br>DRC <sub>IO,1</sub> = DC <sub>IO,1</sub> (I) / DC <sub>IO,1</sub><br>I(IOx) = 75mA                                                                                                                                                            | 48<br>6.2    | 51<br>9.2    | 54<br>12.2   | %<br>% |

| 732         | D <sub>VBg,0</sub>  | Digital value of VBG measurement (internal reference)       | SELAD = '0b110', SVREF = 0                                                                                                                                                                                                                                                   | 435          | 460          | 485          |        |

| 733         | D <sub>VBY,0</sub>  | Digital value of VBG measurement (internal reference)       | SVREF = 0, V(VBy) = 36V, SELAD = '0b101'                                                                                                                                                                                                                                     | 830          | 880          | 1022         |        |

| 734         | DR <sub>VBY,0</sub> | Relative value using VR1 range (internal reference)         | $SVREF = 0$ , $SELAD = '0b101$ ; $DR_{VBY,0} = D_{VBY,0}(V) / D_{VBY,0}$ $V(VBy) = 24V$ $V(VBy) = 12V$                                                                                                                                                                       | 64.6<br>31.3 | 66.6<br>33.3 | 68.6<br>35.3 | %<br>% |

| 735         | D1 <sub>IO,0</sub>  | Digital value using VR1 range (internal reference)          | SELAD = '0b010', EME = '0b0', SVREF = 0,<br>V(IOx) = V(VBy) - 0.6V                                                                                                                                                                                                           | 760          | 820          | 1022         |        |

| 736         | DR1 <sub>IO,0</sub> | Relative value using VR1 range (internal reference)         | nge   SELAD = '0b010', EME = '0b0', SVREF = 0;<br>  DR1 <sub>IO,0</sub> = D1 <sub>IO,0</sub> (V) / D1 <sub>IO,0</sub><br>  V(IOx) = V(VBy) - 0.3V                                                                                                                            |              | 49<br>15     | 52<br>18     | %<br>% |

| 737         | D2 <sub>IO,0</sub>  | Digital value using VR2 range (internal reference)          | SELAD = '0b010', EME = '0b1', SVREF = 0,<br>V(IOx) = V(VBy) - 5.0V                                                                                                                                                                                                           | 790          | 840          | 1022         |        |

| 738         | DR2 <sub>IO,0</sub> | Relative value using VR2 range (internal reference)         | SELAD = '0b010', EME = '0b1', SVREF = 0;<br>DR2 <sub>IO,0</sub> = D2 <sub>IO,0</sub> (V) / D2 <sub>IO,0</sub><br>V(IOx) = V(VBy) - 2.5V<br>V(IOx) = V(VBy) - 0.6V                                                                                                            | 48<br>9.5    | 50<br>11.5   | 52<br>14     | %<br>% |

| 739         | D3 <sub>IO,0</sub>  | Digital value using VR3 range (internal reference)          | SELAD = '0b100', EME = '0b0', SVREF = 0,<br>V(IOx) = 0.6V                                                                                                                                                                                                                    | 790          | 840          | 1022         |        |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 9/36

#### **ELECTRICAL CHARACTERISTICS**

| Item<br>No. | Symbol              | Parameter                                                                                                    | Conditions                                                                                                                          | Min.         | Тур.         | Max.         | Unit   |

|-------------|---------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|--------|

| 740         | DR3 <sub>IO,0</sub> | Relative value using VR3 range (internal reference)                                                          | SELAD = '0b100', EME = '0b0', SVREF = 0;<br>$DR3_{IO,0} = D3_{IO,0}(V) / D3_{IO,0}$<br>V(IOx) = 0.3V<br>V(IOx) = 0.1V               | 48<br>14.5   | 50<br>16     | 52<br>18.5   | %<br>% |

| 741         | D4 <sub>IO,0</sub>  | Digital value using VR4 range (internal reference)                                                           | SELAD = '0b100', EME = '0b1', SVREF = 0,<br>V(IOx) = 5.0V                                                                           | 790          | 840          | 1022         |        |

| 742         | DR4 <sub>IO,0</sub> | Relative value using VR4 range (internal reference)                                                          | SELAD = '0b100', EME = '0b1', SVREF = 0;<br>$DR4_{IO,0} = D4_{IO,0}(V) / D4_{IO,0}$<br>V(IOx) = 2.5V<br>V(IOx) = 0.6V               |              | 50<br>11.5   | 52<br>14     | %<br>% |

| 743         | D5 <sub>IO,0</sub>  | Digital value using VR5 range (internal reference)                                                           | SELAD = '0b011', SVREF = 0<br>V(IOx) = 36.0V                                                                                        |              | 870          | 1022         |        |

| 744         | DR5 <sub>IO,0</sub> | Relative value using VR5 range (internal reference)                                                          | SELAD = '0b011', SVREF = 0;<br>DR5 <sub>IO,0</sub> = D5 <sub>IO,0</sub> (V) / D5 <sub>IO,0</sub><br>V(IOx) = 24.0V<br>V(IOx) = 5.0V | 64.6<br>11.8 | 66.6<br>13.8 | 68.6<br>15.8 | %<br>% |

| 745         | DC <sub>IO,0</sub>  | Digital value of current measure-<br>ment (internal reference)                                               | SELAD = '0b001', SVREF = 0, I(IOx) = 150mA                                                                                          | 720          | 820          | 1022         |        |

| 746         | DRC <sub>IO,0</sub> | Digital value of current measurement (internal reference)                                                    | SELAD = '0b001', SVREF = 0;<br>DRC <sub>IO,0</sub> = DC <sub>IO,0</sub> (I) / DC <sub>IO,0</sub><br>I(IOx) = 75mA<br>I(IOx) = 15mA  |              | 51<br>9.2    | 54<br>12.2   | %<br>% |

| Input       | RSET                | 1                                                                                                            |                                                                                                                                     | ı            | ı            |              |        |

| B01         | V(RSET)             | Voltage at RSET                                                                                              |                                                                                                                                     | 1.15         | 1.22         | 1.30         | V      |

| B02         | R(RSET)             | Range value for RSET                                                                                         |                                                                                                                                     | 9            | 10           | 14           | kΩ     |

| Burst       | -Indication         |                                                                                                              |                                                                                                                                     |              |              |              |        |

| C01         | VSPon               | Input On-Threshold for burst recognition                                                                     |                                                                                                                                     | 1.3          |              | 2.9          | V      |

| C02         | VSPoff              | Input Off-Threshold for Burst-recognition                                                                    |                                                                                                                                     | 1.4          |              | 3            | V      |

| C03         | tpoff               | Delay time to Reset after spike at VCC, VDD                                                                  | Spike duration: 10 ns                                                                                                               | 2            |              | 110          | μs     |

| Pin m       | onitoring G         | NDA, GNDD                                                                                                    |                                                                                                                                     | J.           | J            |              |        |

| H01         | Vt()gnd             | Threshold voltage for open ciruit detection on pins GNDA, GNDD                                               |                                                                                                                                     | 35           |              | 65           | mV     |

| H02         | tmin()gnd           | Minimum duration for open circuit detection                                                                  | V(GNDA,GNDD) = 0 V Vt()gnd                                                                                                          | 1            |              |              | μs     |

| H03         | tpoff               | Delay time to reset after open circuit detection at GNDA, GNDD                                               |                                                                                                                                     |              |              | 15           | μs     |

| Under       | rvoltage det        | ection VB                                                                                                    |                                                                                                                                     |              |              |              |        |

| I01         | VByon               | Undervoltage message VB14 on                                                                                 |                                                                                                                                     | 10.6         | 11.2         | 11.8         | V      |

| 102         | VByoff              | Undervoltage message VB14 off                                                                                |                                                                                                                                     | 10.0         | 10.6         | 11.2         | V      |

| 103         | VByhys              | Hysteresis                                                                                                   | VByhys = VByon - VByoff                                                                                                             | 400          |              |              | mV     |

| 104         | tmin()lv            | Minimum duration for Power-<br>Down detection                                                                | VBy = 0.8 V VByoff                                                                                                                  | 1            |              |              | μs     |

| 105         | tpoff               | Delay time for undervoltage message VB14                                                                     |                                                                                                                                     |              |              | 6            | μs     |

| μC-Int      | trface, I/O-L       | ogic, Frequency divider, Interrup                                                                            | t                                                                                                                                   |              |              |              |        |

| K01         | Vt()hi              | Threshold voltage High at<br>Schmitt-Trigger-Inputs<br>NCS, NWR, NRD, A04, NRES,<br>CLK, BLFQ, D07, NSP, POE | D07 with input function                                                                                                             |              |              | 2            | V      |

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 10/36

#### **ELECTRICAL CHARACTERISTICS**

Operating conditions: VCC = VDD = 3 ... 5.5 V, VBy = 12 ... 36 V, GNDA = GNDD = 0 V, RSET =  $10\,k\Omega$  ±1% . All inputs on defined logic states (high or low), Tj = -40 ... 125 °C unless otherwise stated. Functionality and parameters beyond operating conditions (for example w.r. to independent voltage supplies) are to be verified within the individual application by FMEA methods.

| Item  | Symbol          | Parameter                                                                                                   | Conditions                                                                                   |      |      |      | Unit |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| No.   |                 |                                                                                                             |                                                                                              | Min. | Тур. | Max. |      |

| K02   | Vt()lo          | Threshold voltage Low at<br>Schmitt-Trigger-Inputs<br>NCS, NWR, NRD, A04, NRES,<br>CLK, BLFQ, D07, NSP, POE | D07 with input function                                                                      | 0.8  |      |      | V    |

| K03   | Vt()hys         | Schmitt-Trigger-Hysteresis at<br>inputs NCS, NWR, NRD, A04,<br>NRES, CLK, BLFQ, D07, NSP,<br>POE            | Vt()hys = Vt()hi - Vt()lo;<br>D07 mit Eingangsfunktion                                       | 150  |      |      | mV   |

| K04   | Vs()hi          | Saturation voltage high an NINT, Dx                                                                         | Vs()hi = VDD - V( );<br>I( ) = -4 mA                                                         |      |      | 0.8  | V    |

| K05   | Vs()lo          | Saturation voltage low an NINT, Dx                                                                          | I( ) = 4 mA                                                                                  |      |      | 0.49 | V    |

| K06   | lpd()           | Pull Down current sources at A04, NRES, CLK, BLFQ, D07, POE                                                 | V() = 1V VDD                                                                                 | 2    |      | 70   | μA   |

| K07   | lpu()           | Pull Up current sources at NSP, NCS, NWR, NRD                                                               | V() = 0V VDD - 1 V                                                                           | -70  |      | 2    | μA   |

| K08   | tp(POE-<br>IOx) | Delay time output enable:<br>POE to IOx disabled                                                            | RL = 240 $\Omega$ 1 k $\Omega$ , POE: hi $\rightarrow$ lo to V(IOx) < 80 % (VBy - Vs(IOx)hi) |      |      | 6    | μs   |

| K09   | tw()lo          | Permissible pulse width for enable/disable at POE                                                           |                                                                                              | 600  |      |      | ns   |

| K10   | tw()            | Permissible burst pulse width at POE                                                                        |                                                                                              |      |      | 100  | ns   |

| K11   | tmin()nres      | minimum duration for reset at NRES                                                                          |                                                                                              | 200  |      |      | ns   |

| Frequ | ency BLFQ       | , CLK                                                                                                       |                                                                                              |      |      |      |      |

| P01   | td()            | maximum frequency at CLK                                                                                    |                                                                                              |      |      | TBD  | MHz  |

| P02   | td()            | maximum frequency at BLFQ                                                                                   |                                                                                              |      |      | TBD  | MHz  |

#### **Characteristics: Diagrams**

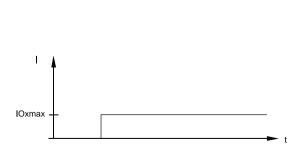

Figure 1: DC load

Figure 2: Pulse load

Rev C1, Page 11/36

#### OPERATING REQUIREMENTS: Parallel µC Interface

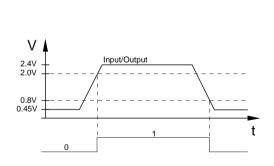

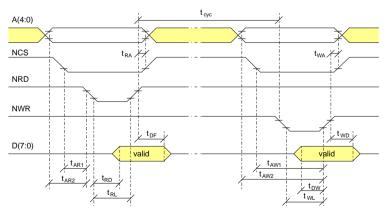

Operating Conditions: VCC = VDD = 3...5.5 V, VBy = 12...36 V, GNDA = GNDD = 0 V, RSET =  $10 \text{ k}\Omega \pm 1 \%$ Ta = 0...70 °C, CL() = 150 pF, input level lo = 0.8 V, hi = 2.2 V, reference levels according to figure 3

| ltem    | Symbol                              | Parameter                                                                                                                                                                                                                                    | Conditions   |      |      | Unit |

|---------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|

| No.     |                                     |                                                                                                                                                                                                                                              |              | Min. | Max. |      |

| Read (  | Cycle                               |                                                                                                                                                                                                                                              |              |      |      |      |

| 1001    | t <sub>AR1</sub> , t <sub>AR2</sub> | Setup Time: NCS, A04 set before NRD hi $\rightarrow$ lo                                                                                                                                                                                      | see Figure 4 | 30   |      | ns   |

| 1002    | t <sub>RA</sub>                     | Hold Time: NCS, A04 set before NRD lo → hi                                                                                                                                                                                                   | see Figure 4 | 0    |      | ns   |

| 1003    | t <sub>RD</sub>                     | Wait Time : Data valid after NRD hi $\rightarrow$ lo                                                                                                                                                                                         | see Figure 4 |      | 120  | ns   |

| 1004    | t <sub>DF</sub>                     | Hold Time: Data Bus high impedance after NRD lo $\rightarrow$ hi                                                                                                                                                                             | see Figure 4 |      | 65   | ns   |

| 1005    | t <sub>RL</sub>                     | Required Read Signal Duration at NRD                                                                                                                                                                                                         |              | 50   |      | ns   |

| Write ( | Cycle                               |                                                                                                                                                                                                                                              |              |      |      |      |

| 1006    | t <sub>AW1</sub> , t <sub>AW2</sub> | Setup Time: NCS, A04 set before NWR lo $\rightarrow$ hi                                                                                                                                                                                      | see Figure 4 | 30   |      | ns   |

| 1007    | t <sub>DW</sub>                     | Setup time :<br>Data valid before NWR lo → hi                                                                                                                                                                                                | see Figure 4 | 100  |      | ns   |

| 1008    | t <sub>WA</sub>                     | Hold time:<br>NCS, A04 stable after NWR lo → hi                                                                                                                                                                                              | see Figure 4 | 10   |      | ns   |

| 1009    | t <sub>WD</sub>                     | Hold time:<br>Data valid after NWR lo → hi                                                                                                                                                                                                   | see Figure 4 | 10   |      | ns   |

| I010    | t <sub>WL</sub>                     | Required Write Signal Duration at NWR                                                                                                                                                                                                        | see Figure 4 | 50   |      | ns   |

| Read/\  | Vrite Timin                         | g                                                                                                                                                                                                                                            |              |      |      |      |

| I011    | t <sub>cyc</sub>                    | Recovery Time between cycles: NRD lo $\rightarrow$ hi to NRD hi $\rightarrow$ lo, NRD lo $\rightarrow$ hi to NWR hi $\rightarrow$ lo, NWR lo $\rightarrow$ hi to NWR hi $\rightarrow$ lo, NWR lo $\rightarrow$ hi to NWR hi $\rightarrow$ lo | see Figure 4 | 165  |      | ns   |

Figure 3: Reference levels for displayed values of time

Figure 4: Read and write cycle for the parallel interface

Rev C1, Page 12/36

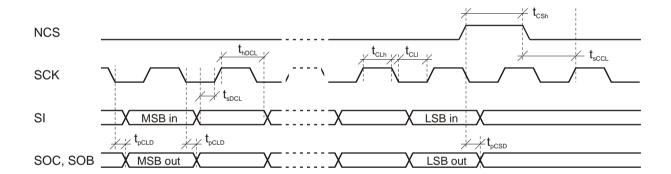

#### OPERATING REQUIREMENTS: Serial µC Interface

Operating Conditions: VCC = VDD = 3...5.5 V, VBy = 12...36 V, GNDA = GNDD = 0 V, RSET = 10 k $\Omega$  ±1 % Ta = 0...70 °C, CL() = 150 pF, input level lo = 0.8 V, hi = 2.2 V, reference levels according to figure 3

| Item  | Symbol            | Parameter                                                                  | Conditions   |      |      | Unit |

|-------|-------------------|----------------------------------------------------------------------------|--------------|------|------|------|

| No.   |                   |                                                                            |              | Min. | Max. |      |

| Grupp | e 2.0 EN          |                                                                            |              |      |      |      |

| l1111 | t <sub>sCCL</sub> | Setup time: NCS hi $\rightarrow$ lo to SCK(A3) lo $\rightarrow$ hi         | see Figure 5 | 50   |      | ns   |

| l112  | t <sub>sDCL</sub> | Setup time: SI(D0) stabil before SCK(A3) lo $\rightarrow$ hi               | see Figure 5 | 40   |      | ns   |

| I113  | t <sub>hDCL</sub> | Hold time: SI(D0) stabil after SCK(A3) lo $\rightarrow$ hi                 | see Figure 5 | 30   |      | ns   |

| I114  | t <sub>CLh</sub>  | Clock duration SCK(A3) hi                                                  | see Figure 5 | 100  |      | ns   |

| I115  | t <sub>CLI</sub>  | Clock duration SCK(A3) lo                                                  | see Figure 5 | 100  |      | ns   |

| I116  | t <sub>CSh</sub>  | Pulse duration NCS hi                                                      | see Figure 5 | 100  |      | ns   |

| l117  | t <sub>pCLD</sub> | Delay time: SOC(D1) resp. SOB(D2) stable after SCK(A3) hi $\rightarrow$ lo | see Figure 5 | 0    | 50   | ns   |

| l118  | t <sub>pCSD</sub> | Delay time:<br>SOC(D1) resp. SOB(D2) high<br>impedance after NCS lo → hi   | see Figure 5 | 0    | 50   | ns   |

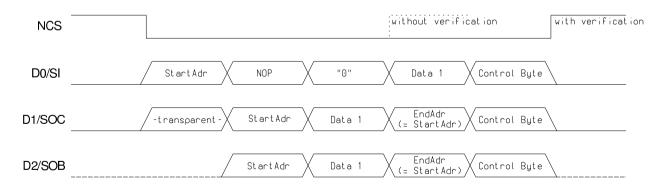

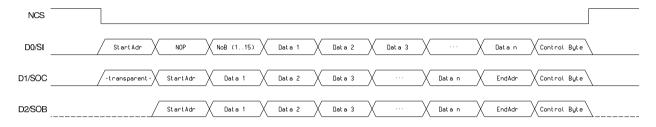

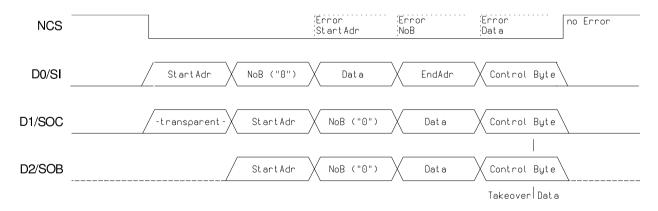

Figure 5: µC interface in SPI mode

# 16-FOLD 24 V HIGH-SIDE DRIVER WITH µC INTERFACE (CHaus

Rev C1, Page 13/36

#### **PROGRAMMING**

| Register Ove                         | erview                                                                                    | Page 14       | PN10<br>SEBLQ                                                                                | Flash Frequency Settings Flash Frequency Reference                                      |

|--------------------------------------|-------------------------------------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                      | erInput Register, Status I/O-Pin                                                          | Page 15       |                                                                                              | System Clock                                                                            |

|                                      |                                                                                           |               |                                                                                              | Page 24                                                                                 |

| _                                    | nput Messages<br>Change of Input Messages                                                 | Page 15       | EOI<br>BYPSCF<br>SCF30                                                                       | Bypass SC Filter                                                                        |

| DCHI<br>IET21                        | Input Change Interrupt Overtemperatur Interrupt                                           | Page 16       |                                                                                              | rd 5 Page 24 Select I/O-Stage for AD Converter                                          |

| ISCS                                 | Overcurrent Interrupt                                                                     |               | Control Wor                                                                                  | rd 6 Page 25                                                                            |

| ET21<br>SCS                          | Overtemperatur<br>Overcurrent                                                             |               | Settings for ADC-Measurements Extended Measurement Enable Enable ADC-Measurement Select VREF |                                                                                         |

| IEOC                                 | ADC Interrupt                                                                             |               | SVREF                                                                                        | Select VIXEI                                                                            |

| ISD<br>IUSD<br>IUSA                  | Interrupt - Bursts on VDD Interrupt - Undervoltage at VDD Interrupt - Undervoltage at VCC |               | Interconnec<br>IBA<br>USVB<br>NRESA                                                          | tion Error, Device-ID Page 25<br>Interconnection Error<br>Undervoltage VB<br>NRES = '0' |

| EOC<br>USD<br>USA                    | ADC End-Of-Conversion<br>Undervoltage VDD<br>Undervoltage VCC                             |               | DID40                                                                                        | Device ID                                                                               |

|                                      | Overcurrent-Messages, Interrup<br>Overcurrent-Status, actual                              |               |                                                                                              |                                                                                         |