# Am79C30A/32A

# Digital Subscriber Controller™ (DSC™) Circuit

# **DISTINCTIVE CHARACTERISTICS**

- Combines CCITT I.430 S/T-Interface Transceiver, D-Channel LAPD Processor, Audio

- Processor (DSC device only), and IOM-2 Interface in a single chip

- Special operating modes allow realization of CCITT I.430 power-compliant terminal equipment

- S- or T-Interface Transceiver

- Level 1 Physical Layer Controller

- Supports point-to-point, short and extended passive bus configurations

- Provides multiframe support

- Certified protocol software support available

- CMOS technology, TTL compatible

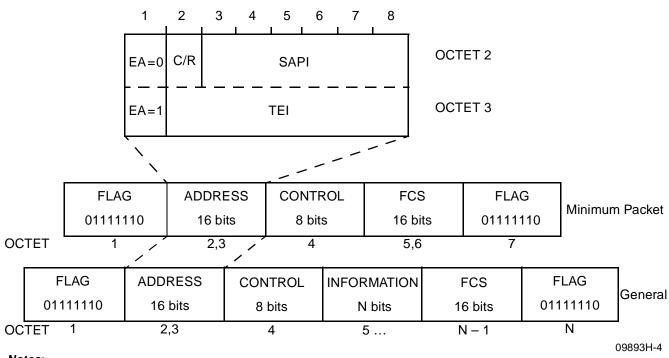

- D-channel processing capability

- Flag generation/detection

- CRC generation/checking

- Zero insertion/deletion

- Four 2-byte address detectors

- 32-byte receive and 16-byte transmit FIFOs

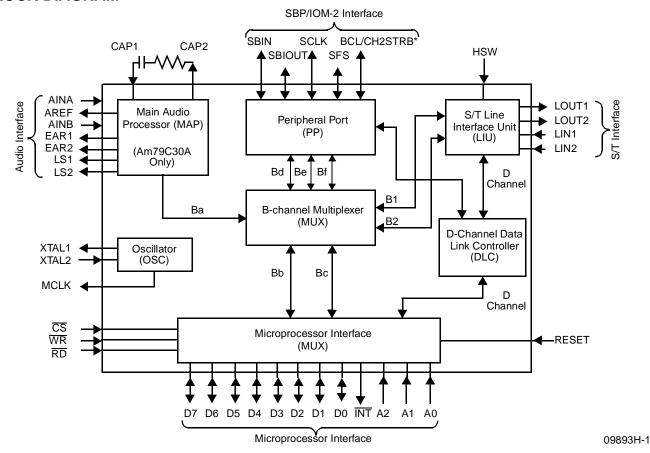

### **BLOCK DIAGRAM**

Publication# 09893 Rev: H Amendment/0 Issue Date: December 1998

# **DISTINCTIVE CHARACTERISTICS (continued)**

- Audio processing capability (DSC circuit only)

- Registers for implementation of software-based speaker phone algorithms

- Dual audio inputs

- Earpiece and loudspeaker drivers

- Codec/filter with A/μ selection

- Programmable gain and equalization filters

- Programmable sidetone level

- Programmable DTMF, single tone, progress tone, and ringer tone generation

- Programmable on-chip microphone amplifier

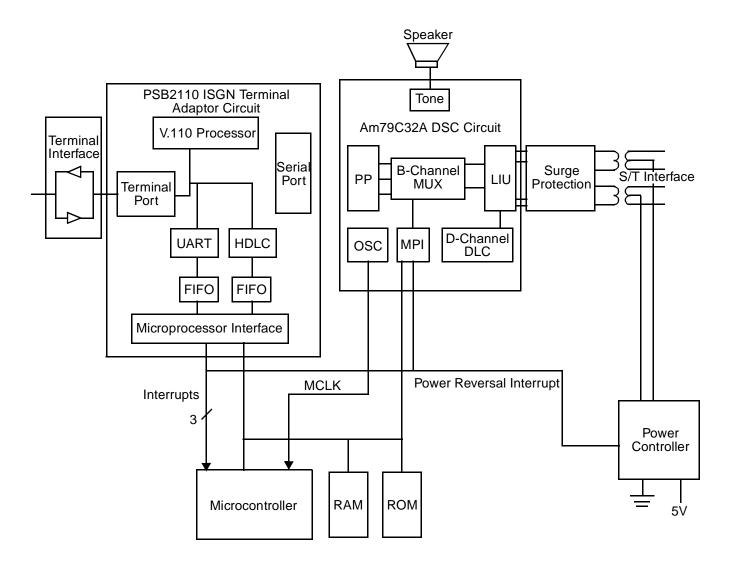

- Pin and software compatible with the Am79C32A ISDN Data Controller (IDC™) Circuit. The Am79C32A is used in data-only applications.

### **GENERAL DESCRIPTION**

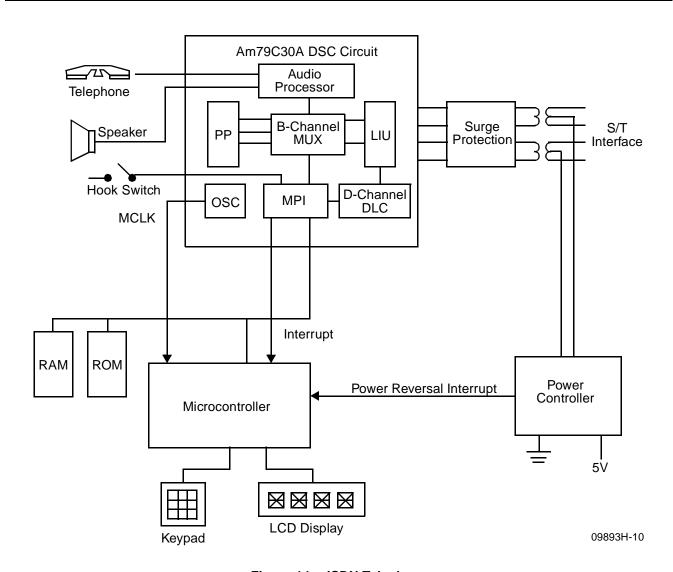

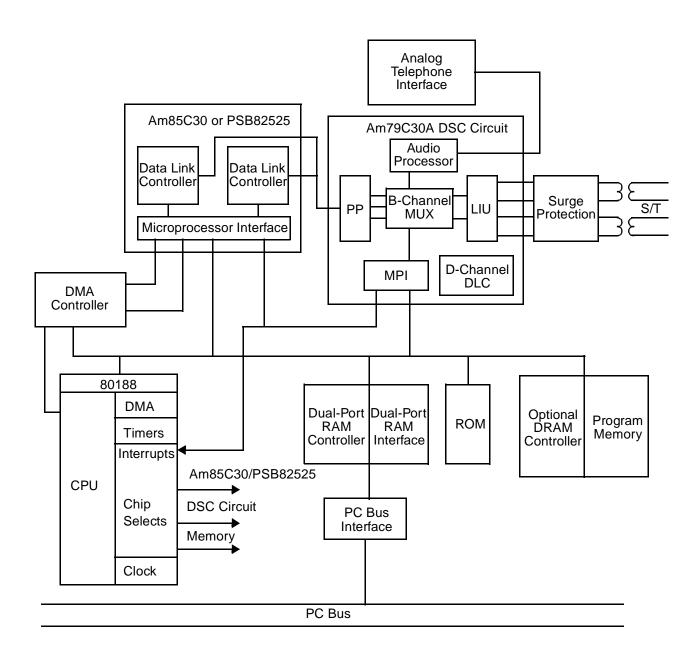

The Am79C30A Digital Subscriber Controller (DSC) Circuit and Am79C32A ISDN Data Controller (IDC) Circuit, shown in the Block Diagram, allow the realization of highly-integrated Terminal Equipment for the ISDN. The Am79C30A/32A is fully compatible with the CCITT-I-series recommendations for the S and T reference points, ensuring that the user of the device may design TEs which conform to the international standards.

The Am79C30A/32A provides a 192-Kbit/s full duplex digital path over four wires between the TE located on the subscriber's premises and the NT or PABX line-card. All physical layer functions and procedures are implemented in accordance with CCITT Recommendation I.430, including framing, synchronization, maintenance, and multiple terminal contention. Both point-to-point and point-to-multipoint configurations are supported.

The Am79C30A/32A processes the ISDN basic rate bit stream, which consists of B1 (64 Kbit/s), B2 (64 Kbit/s), and D (16 Kbit/s) channels. The B channels are routed to and from different sections of the Am79C30A/32A

under software control. The D channel is partially processed by the DSC/IDC circuit and is passed to the microprocessor for further processing.

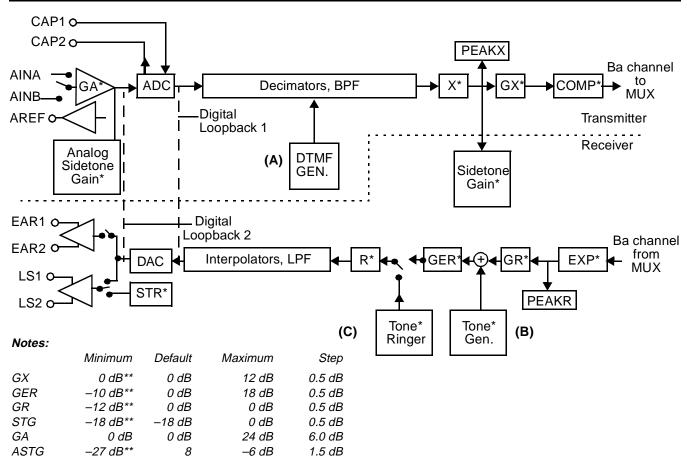

The Main Audio Processor (MAP) uses Digital Signal Processing (DSP) to implement a high performance codec/filter function. The MAP interface supports a loudspeaker, an earpiece, and two separate audio inputs. Programmable on-chip gain is provided to simplify use of low output level microphones. The user may alter frequency response and gain of the MAP receive and transmit paths. Tone generators are included to implement ringing, call progress, and DTMF signals.

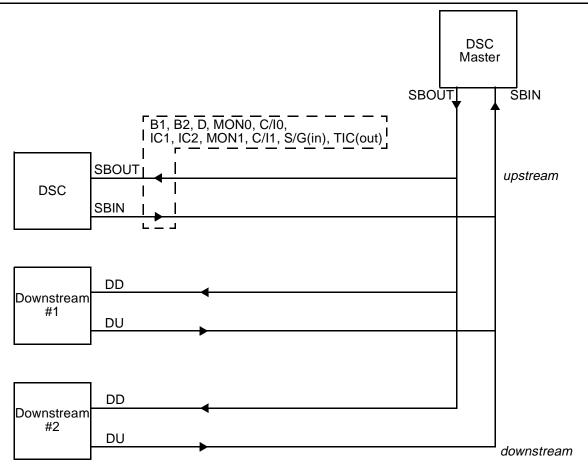

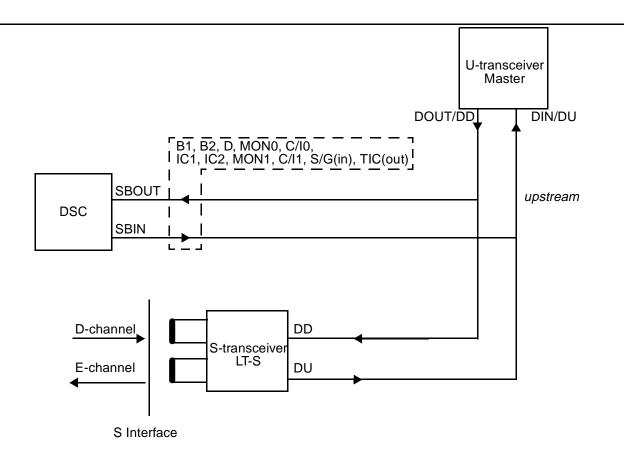

A Peripheral Port (PP) is provided to allow the B channels to be routed off-chip for processing by other peripherals. This port is configurable as either an industry-standard IOM-2 port, or as a serial bus port (SBP).

The TE design process is simplified by the availability of certified protocol software packages, which provide complete system solutions through OSI Layer 3.

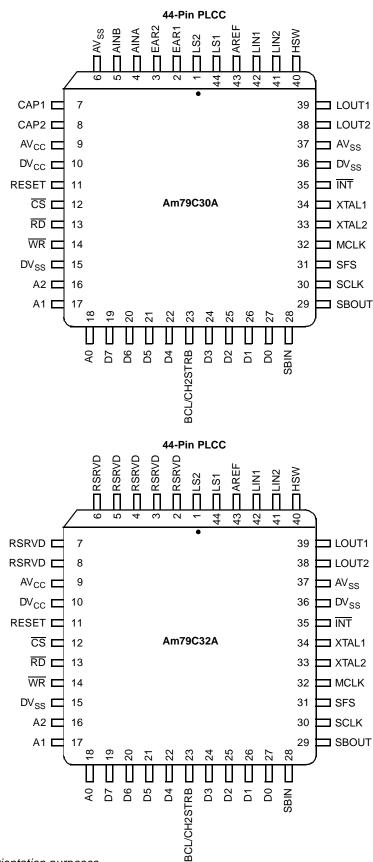

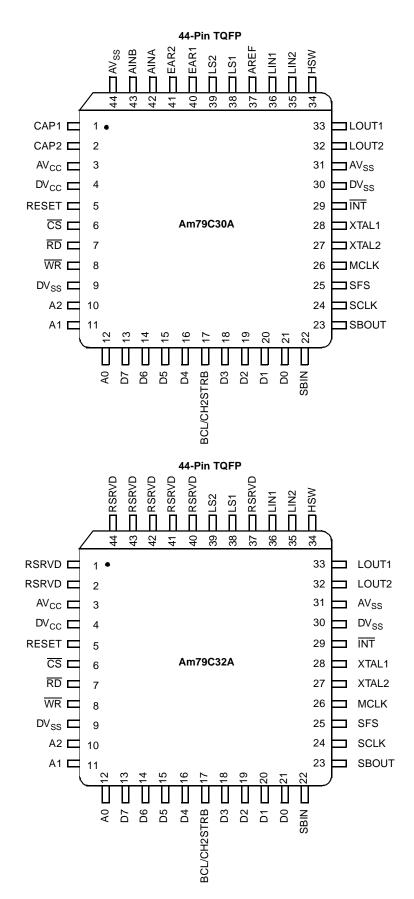

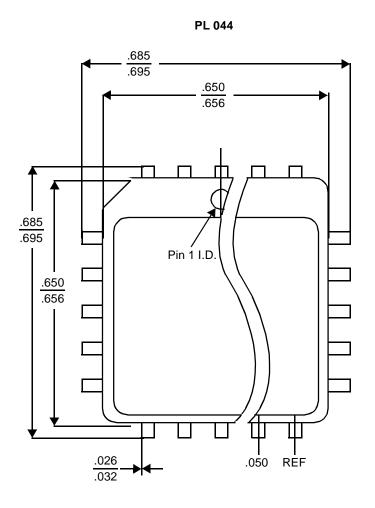

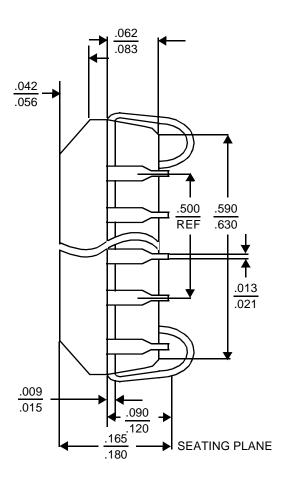

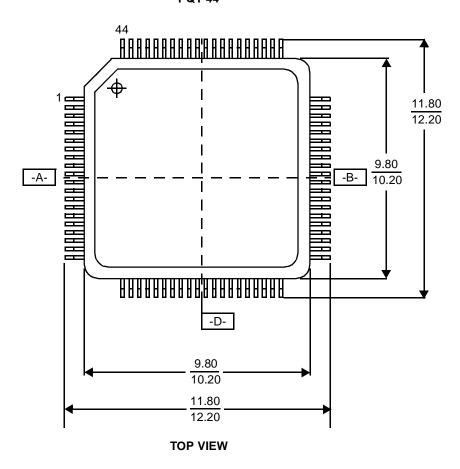

# **CONNECTION DIAGRAMS**

# **Top View**

# Note:

- 1. Pin 1 is marked for orientation purposes.

- 2. RSRVD = Reserved pin; should not be connected externally to any signal or supply.

# **CONNECTION DIAGRAMS (continued)**

# **Top View**

Note:

Pin 1 is marked for orientation purposes.

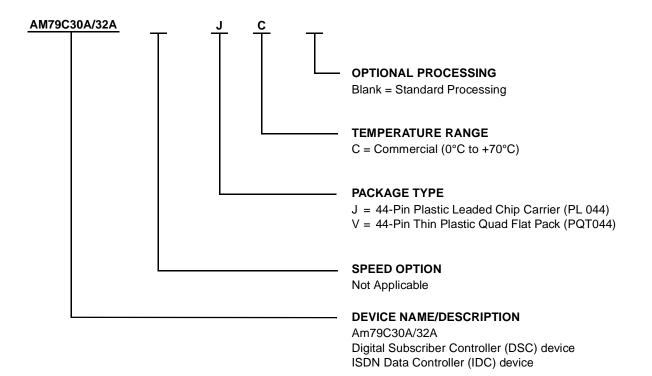

# **ORDERING INFORMATION**

# **Standard Products**

AMD<sup>®</sup> standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |        |  |  |  |  |

|--------------------|--------|--|--|--|--|

| AM79C30A           | JC, VC |  |  |  |  |

| AM79C32A           | JC, VC |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

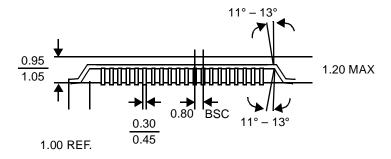

Reference Appendix C, Figures 1 & 2, for specific mechanical dimensions of the two packages.

# PIN DESCRIPTION\*

Line Interface Unit (LIU)

#### **HSW**

# **Hook-Switch (Input)**

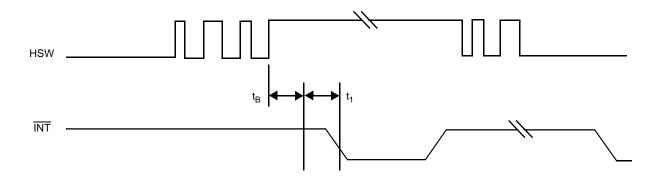

The HSW signal indicates if the hook-switch is on or off hook. This signal may be generated with a mechanical switch wired to ground with a pull-up resistor to  $V_{CC}$ . Any change in the HSW state causes an interrupt.

# LIN1, LIN2 Subscriber Line Input (Differential Inputs)

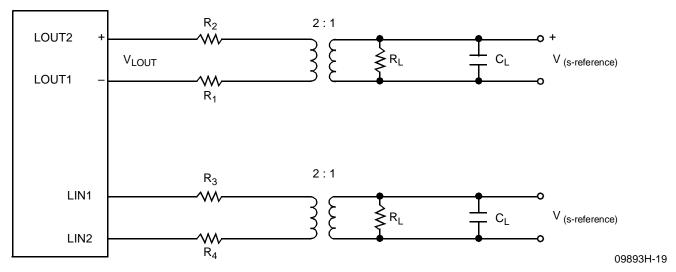

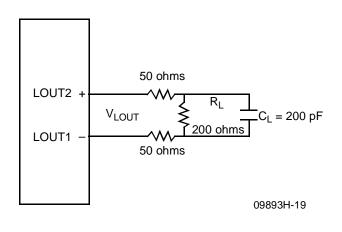

The LIN1 and LIN2 inputs interface to the subscriber (S reference point) via an isolation transformer. LIN2 is the positive input; LIN1 is the negative input. These pins are not TTL compatible.

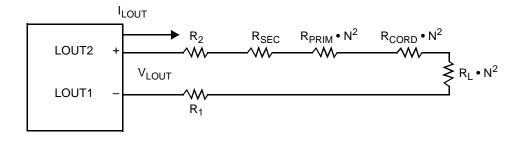

# LOUT1, LOUT2 Subscriber Line Output (Differential Outputs)

The LOUT1 and LOUT2 line driver output signals interface to the subscriber line at the S reference point via an isolation transformer and resistors. LOUT2 is the positive S-interface driver (sources current during a High mark), and LOUT1 is the negative S-interface driver (sources current during Low mark). For multi-point applications, all TEs must maintain the same polarity on the S Interface. These pins are not TTL compatible.

# **Main Audio Processor (MAP)**

All MAP pins are analog, and therefore are not TTL compatible.

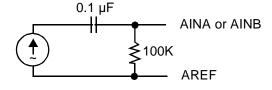

# AINA, AINB Analog (Inputs)

These analog inputs allow for two separate analog (audio) inputs to the transmit path of the codec/filter.Input signals on either of these pins must be referenced to AREF.

#### **AREF**

# **Analog Reference (Output)**

This is a nominal 2.25-V reference voltage output for biasing the analog inputs. When the MAP is disabled, this pin is high impedance.

#### CAP1, CAP2

# Capacitor/Resistor (CAP1, Input; CAP2, Output)

An external resistor and capacitor are connected in series between these pins. These components are needed for the integrator in the Analog-to-Digital Converter (ADC).

### EAR1, EAR2

# **Earpiece Interface (Differential Outputs)**

EAR1 and EAR2 are the outputs from the receive path of the codec/filter. These differential outputs can directly drive a minimum load of 130 ohms.

### **LS1, LS2**

### **Loudspeaker Interface (Differential Outputs)**

LS1 and LS2 are push-pull outputs which can directly drive a minimum load of 40 ohms.

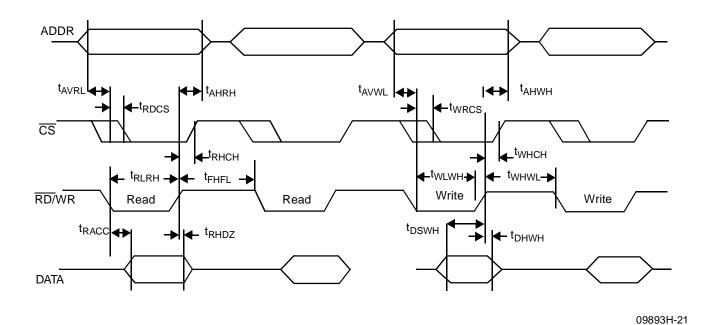

# **Microprocessor Interface (MPI)**

#### A2-A0

# **Address Line (Inputs)**

A2, A1, and A0 signals select source and destination registers for read and write operations on the data bus.

#### CS

### **Chip Select (Input)**

CS must be Low to read or write to the Am79C30A/32A. Data transfer occurs over the bidirectional data lines (D7–D0).

# D7-D0

# Data Bus (Bidirectional with High-Impedance State)

The eight bidirectional data bus lines are used to exchange information with the microprocessor. D0 is the least significant bit (LSB) and D7 is the most significant bit (MSB). A High on the data bus line corresponds to a logic 1, and Low corresponds to a logic 0. These lines act as inputs when both  $\overline{\text{WR}}$  and  $\overline{\text{CS}}$  are active and as outputs when both  $\overline{\text{RD}}$  and  $\overline{\text{CS}}$  are active. When  $\overline{\text{CS}}$  is inactive or both  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  are inactive, the D7–D0 pins are in a high-impedance state.

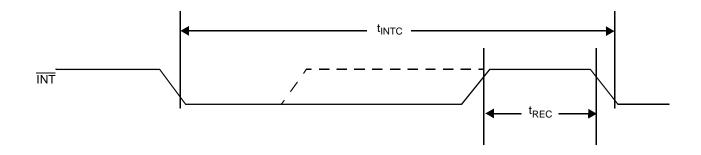

# INT

### Interrupt (Output)

An active Low output on the  $\overline{\text{INT}}$  pin informs the external microprocessor that the Am79C30A/32A needs interrupt service.  $\overline{\text{INT}}$  is updated once every 125 µs. The  $\overline{\text{INT}}$  pin remains active until the Interrupt Register (IR) is read or the Am79C30A/32A is reset.

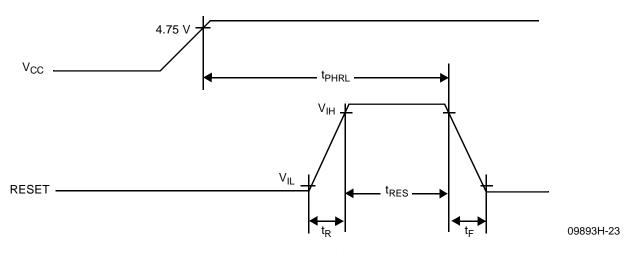

# RESET

# Reset (Input)

Reset is an active High signal which causes the Am79C30A/32A to immediately terminate its present activity and initialize to the reset condition. When reset returns Low, the Am79C30A/32A enters the Idle mode. The MCLK output remains active while RESET is held High.

#### Note:

<sup>\*</sup> All signal levels are TTL compatible unless otherwise stated.

# $\overline{\mathsf{RD}}$

# Read (Input)

The active Low read signal is conditioned by  $\overline{\text{CS}}$  and indicates that internal information is to be transferred onto the data bus. A number of internal registers are user accessible. The contents of the accessed register are transferred onto the data bus after the High to Low transition of the  $\overline{\text{RD}}$  input.

# $\overline{\mathsf{WR}}$

### Write (Input)

The active Low write signal is conditioned by  $\overline{\text{CS}}$  and indicates that external information on the data bus is to be transferred to an internal register. The contents of the data bus are loaded on the Low to High transition of the  $\overline{\text{WR}}$  input.

# Oscillator (OSC)

### **MCLK**

# **Master Clock (Output)**

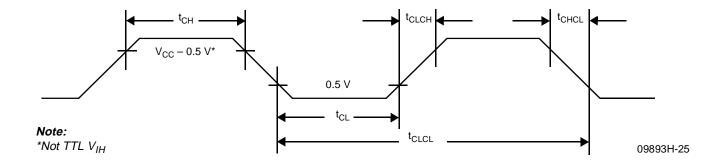

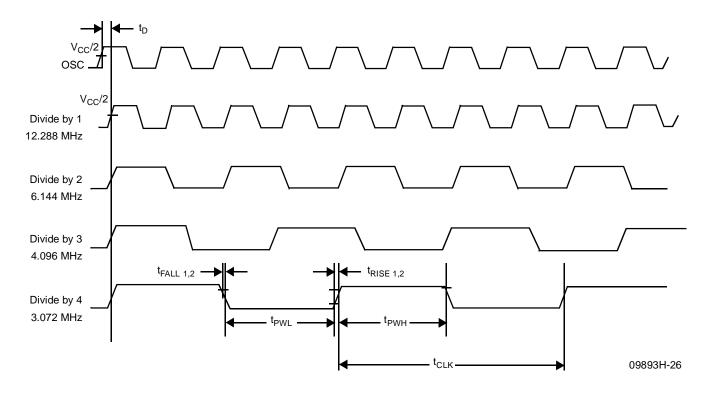

The MCLK output is available for use as the system clock for the microprocessor. MCLK is derived from the 12.288-MHz crystal via a programmable divider in the Am79C30A/32A which provides the following MCLK output frequencies: 12.288, 6.144, 4.096, 3.072, 1.536, 0.768, and 0.384 MHz.

# XTAL1, XTAL2 External Crystal (Output, Input)

XTAL1 and XTAL2 are connected to an external parallel resonant crystal for the on-chip oscillator. XTAL2 can also be connected to an external source instead of a crystal, in which case XTAL1 should be left disconnected. The frequency must be 12.288 MHz, ± 80 ppm.

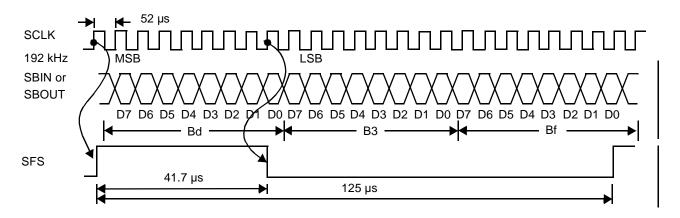

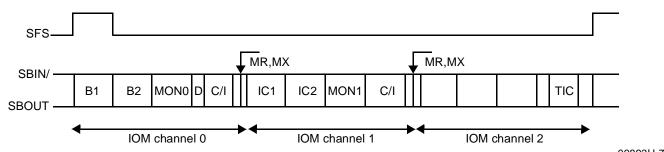

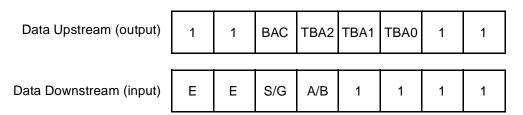

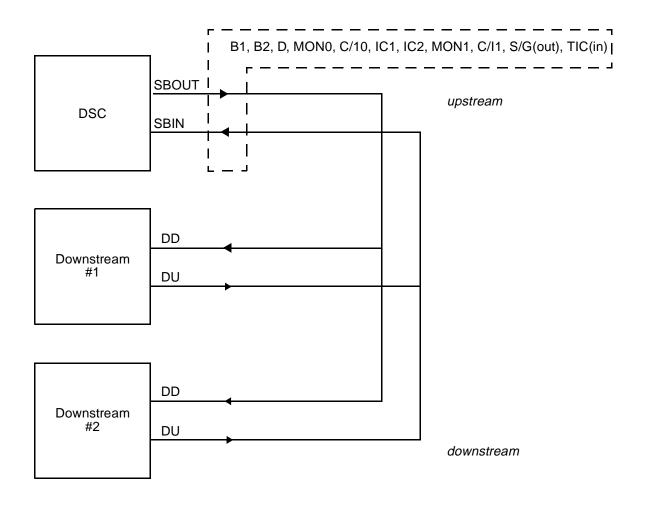

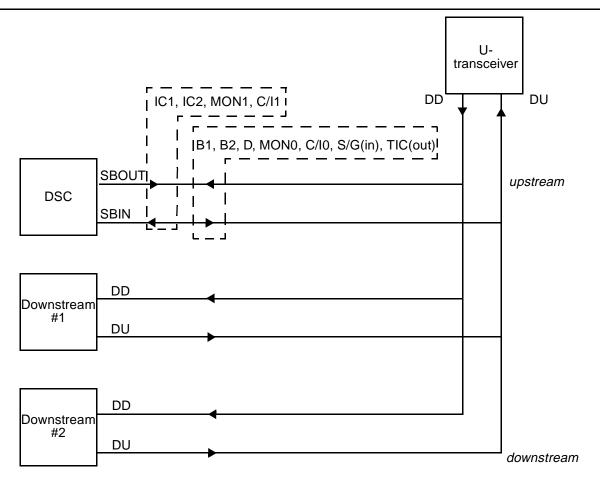

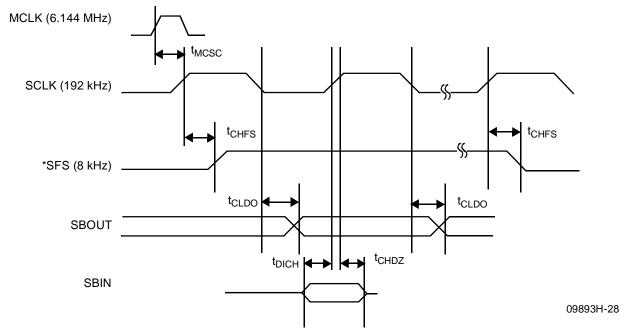

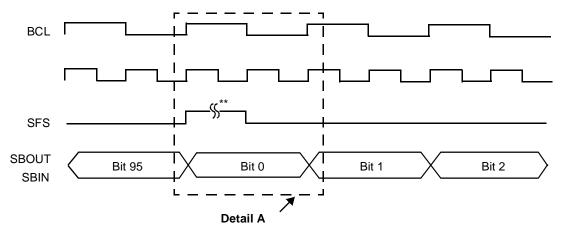

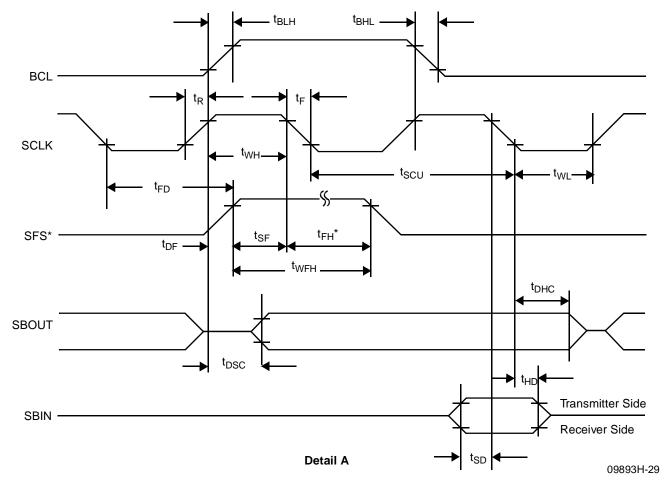

# Peripheral Port (PP)

#### **SBIN**

# Serial Data (Input/Output)

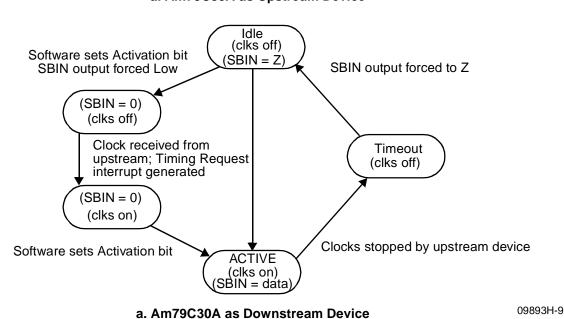

When the Peripheral Port is programmed to SBP mode, SBIN operates as an input for serial data. When the Peripheral Port is programmed to IOM-2 mode, SBIN functions as the data input except in the special case of IOM-2 Slave mode, when it becomes an open-drain output during part or all of the IOM-2 frame, or when deactivated.

### SBOUT Serial Data (Input/Output)

When the Peripheral Port is programmed to SBP mode, SBOUT operates as an output for serial data. When the

Peripheral Port is programmed to IOM-2 mode, SBOUT functions as the data output except in the special case of IOM-2 Slave mode when it becomes an input during part or all of the IOM-2 frame.

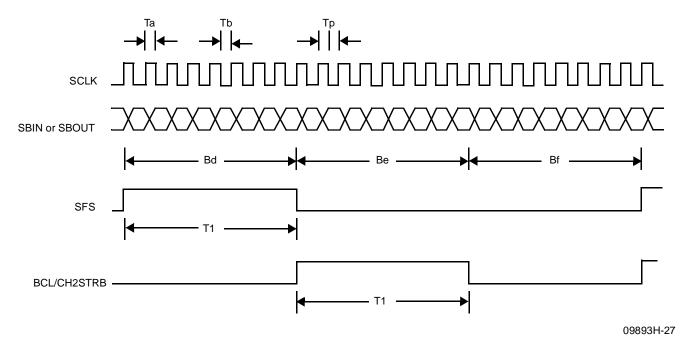

#### SCLK

# Serial Data Clock (Input/Output)

When the PP is programmed to SBP mode, SCLK outputs a 192-kHz data clock, which may be inverted under software control. When the PP is programmed to IOM-2 Master mode, SCLK outputs a 1.536-MHz 2X data clock. In IOM-2 Slave mode, SCLK functions as the clock input. The SCLK pin defaults to a high-impedance state upon reset, but becomes active after any MUX connection is made or if the PP is programmed to IOM-2 Master mode.

#### **SFS**

### Serial Frame Sync (Input/Output)

In SBP mode, SFS outputs an 8-kHz frame synchronization signal. SFS is an output in IOM-2 Master mode, and an input in IOM-2 Slave mode. As an output, SFS is active for 8-bit periods. The SFS pin defaults to a high-impedance state upon reset, but becomes active after any MUX connection is made or if the PP is programmed to IOM-2 Master mode. For SBP mode, the active signal state is Low during Idle and 8 kHz in Active Data Only and Active Voice and Data modes.

# BCL/CH2STRB Bit Clock/SBP Channel 2 Strobe (Output, Three-state)

In SBP mode, this pin provides a strobe during the 8-bit times of the second 64-kbit/s data channel. In IOM-2 Master mode, this pin provides a 768-kHz bit clock to aid in the connection of non-IOM-2 devices to the port. In IOM-2 Slave mode, this pin is high-impedance.

# **Power Supply Pins**

### **PLCC/TQFP Packages**

AV<sub>CC</sub> +5-V analog power supply, ±5%

AV<sub>SS</sub> Analog ground DV<sub>SS</sub> Digital ground

DV<sub>CC</sub> +5-V digital power supply, ±5%

#### Note:

For best performance, decoupling capacitors should be installed between  $V_{CC}$  and  $V_{SS}$  as close to the chip as possible. Do not use separate supplies for analog and digital power and ground connections.

# **OPERATIONAL DESCRIPTION**

### **Overview of Power Modes**

The minimization of power consumption is a key factor in the design of Terminal Equipment for the ISDN, and the DSC/IDC circuit employs two basic approaches to power management:

- The power consumption of the DSC/IDC circuit itself is managed by using four basic power modes which allow unused functional blocks to be disabled. The INIT register may be programmed to select Active Voice and Data, Active Data Only, Idle, or Power-Down mode, depending upon which DSC/IDC device resources are required at the time.

- 2. The power consumption of the controlling micro-processor system may be controlled by driving the processor clock with the DSC/IDC circuit MCLK output. A wide range of MCLK operating frequencies may be selected, and a special Clock Speed-Up function is provided which increases the speed of MCLK upon the occurrence of a key event, without processor intervention. Control of MCLK frequency and Clock Speed-up is accomplished by programming the INIT and INIT2 registers, as described later.

### **Active Voice and Data Mode**

In Active Voice and Data mode all functional blocks of the DSC/IDC circuit are available. Device registers may be accessed through the MPI, the LIU and DLC are available, the OSC is running, the Peripheral Port is available, MUX connections may be made, the Secondary Tone Ringer may be activated, and the MAP is operational (DSC circuit only).

# **Active Data Only Mode**

Active Data Only mode is similar to Active Voice and Data mode, except that the MAP (DSC circuit only) is disabled to reduce system power consumption. This increases the amount of power available for the Secondary Tone Ringer or microprocessor system during the phases of call setup and teardown, or during a data-only telephone call.

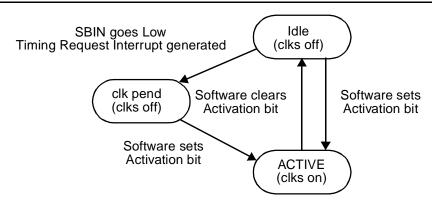

### Idle Mode

Idle mode is the RESET default mode of DSC/IDCcircuit operation, and represents an operational state in which power consumption is reduced, yet the microprocessor system is operational to program DSC/IDC circuit registers or perform other required background tasks. Idle mode may also be entered by appropriate programming of the INIT register.

In Idle mode, the MCLK output is available to drive the microprocessor system, the MPI is available for programming of DSC/IDC registers, and the LIU is available to initiate or respond to S/T interface activity. The HSW hookswitch interrupt is also available in Idle mode.

Idle mode reduces DSC/IDC circuit power consumption by disabling the MUX, DLC, and MAP functional blocks. The Peripheral Port is also disabled, except that an IOM-2 activation request interrupt is possible, and the SFS and SCLK outputs may still be activated. The SFS and SCLK outputs are high impedance upon RE-SET, but become active after any MUX connection is programmed. The DLC read-only registers are cleared when the DSC/IDC circuit enters the Idle mode.

### **Power-Down Mode**

Power-Down mode consumes the least power of all the DSC/IDC power options, and differs from Idle mode in that all clocks, including the XTAL oscillator, are stopped. Most functional blocks are disabled, except for those required to recognize key external events that will force the DSC/IDC circuit to return to Idle mode.

The Power-Down mode is not available unless the Power-Down Enable bit is set in the INIT2 register; see the INIT2 register description for further details.

### **Entering the Power-Down Mode**

The Power-Down mode is entered by appropriate programming of the INIT and INIT2 registers. Selection of the Power-Down mode causes the DSC/IDCcircuit to begin an internal countdown of at least 250 MCLK cycles after which the MCLK and XTAL1 outputs are both stopped and held High, and the XTAL2input will be disregarded. The purpose of this countdown cycle is to allow the microprocessor time for housekeeping operations before its clock is stopped. If an interrupt causes the DSC INT pin to go Low during the countdown, the Power-Down mode bits in the INIT register will be reset and the countdown will be canceled.

If the LIU is enabled and in any state other than F3 at the end of the countdown, MCLK is stopped but the oscillator continues to run. This allows the LIU to identify the incoming signal and either (1) generate an interrupt and force the DSC/IDC circuit to Idle mode when activation is complete, or (2) move to the F3 state and stop the oscillator once the line goes idle.

#### **Exiting the Power-Down Mode**

The DSC/IDC circuit will exit the Power-Down mode and enter the Idle mode if any of the following events occur:

- The DSC/IDC circuit receives a hardware reset via the RESET pin.

- The CS and WR pins are both pulled Low at the same time, as would occur during a normal write operation from the microprocessor to the DSC circuit. No data will be transferred by this operation.

- The HSW hookswitch pin changes state, and the hookswitch interrupt is enabled.

- The LIU receiver is enabled, detects an incoming signal on the S/T Interface, and achieves activation as indicated by a transition to state F7. Both the INT pin and the F7 transition interrupt must be enabled for Power-Down mode to be exited. If the LIU is enabled, it may restart the oscillator so that it can identify the activity on the interface. If the activity is determined to be noise, the LIU will stop the oscillator and continue to monitor the line without an interrupt or returning to Idle mode.

- The IOM-2 Interface is enabled as a clock master and the SBIN input pin goes Low. This indicates that a slave device wants to activate the IOM-2 Interface and communicate with the DSC circuit. Both the INT pin and the IOM-2 timing request interrupts must be enabled for Power-Down mode to be exited.

- The IOM-2 Interface is enabled as a clock slave and the SCLK input pin goes High. This indicates that the master device is activating the IOM-2 Interface and the DSC circuit must wake up in order to monitor the data. Both the INT pin and the IOM-2 timing request interrupts must be enabled for Power-Down mode to be exited.

If the DSC/IDC circuit is awakened by any condition other than RESET, the MCLK output will be restored to its previously programmed frequency, and will not generate any shortened or spurious output cycles. If the DSC/IDC circuit is revived by RESET, MCLK will default to its normal 6.144-MHz rate. The DSC/IDC circuit provides a minimum of two MCLK cycles prior to activating the interrupt pin when exiting Power-Down mode.

# **MCLK Frequency Control**

The MCLK frequency selection bits in the INIT register are unchanged from Revision D. However, additional MCLK frequencies are available by programming bits in the INIT2 register. No shortened or spurious clock pulses that might disrupt the external microprocessor will result when the MCLK frequency is changed.

In order to reduce the probability of errant software disrupting system operation, the INIT2 register requires two consecutive writes before the value will be entered into the register. Note that there will be no MCLK countdown as is the case for entering Power-Down mode if INIT2 is programmed to cause MCLK to STOP, and there will be no shortened or spurious MCLK pulses.

# **MCLK Clock Speed-up Function**

A programmable automatic MCLK speed-up option is provided that will force a hardware reset of INIT2 bits 3-0, which will cause the MCLK frequency to be restored to the value programmed in the INIT register.

There are two events that will trigger the clock speed-up function:

- The DLC receive FIFO threshold has been reached; or.

- 2. a second packet begins to be received while data from a prior packet is still in the receive FIFO.

The second packet case requires provision of an interrupt; see the DLC register section for further information. The clock speed-up function allows the user to program a very slow MCLK frequency using INIT2 when D-channel activity is minimal. If a burst of activity is seen on the D channel and it exceeds the programmed threshold of the receive FIFO or threatens to overrun the receive FIFO status buffers, MCLK will instantly toggle back to the higher frequency programmed in the INIT register. This eliminates the latency incurred if an interrupt has to be serviced to change the clock speed, and allows the overall system power to be reduced during typical voice connections. Note that automatic clock speed-up will not function unless at least one of the associated interrupts are enabled so the processor can be informed that the clock speed has been altered.

# **Global Register Functions**

# INIT Register (INIT) default = 00H

Address = Indirect 21 Hex, Read/Write

Table 1. INIT Register

|   |   |   | В | it |   |   |   |                                |  |  |

|---|---|---|---|----|---|---|---|--------------------------------|--|--|

| 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | Function                       |  |  |

| Χ | Χ | Χ | Χ | Χ  | Χ | 0 | 0 | Idle mode                      |  |  |

| Χ | Χ | Χ | Χ | Χ  | Χ | 0 | 1 | Active Voice and Data mode     |  |  |

| Х | Χ | Χ | Χ | Χ  | Χ | 1 | 0 | Active Data Only mode          |  |  |

| Х | Χ | Χ | Χ | Χ  | Χ | 1 | 1 | Power-Down mode                |  |  |

| Х | Χ | Χ | Χ | Χ  | 0 | Χ | Χ | INT output enabled             |  |  |

| Х | Χ | Χ | Χ | Χ  | 1 | Χ | Χ | INT output disabled            |  |  |

| Х | Χ | 0 | 0 | 0  | Χ | Χ | Χ | MCLK frequency = 6.144 MHz     |  |  |

| Х | Χ | 0 | 0 | 1  | Χ | Χ | Χ | MCLK frequency = 12.288 MHz    |  |  |

| Х | Χ | 0 | 1 | 0  | Χ | Χ | Χ | MCLK frequency = 3,072 MHz     |  |  |

| Χ | Χ | 0 | 1 | 1  | Χ | Χ | Χ | MCLK frequency = 6.144 MHz     |  |  |

| Χ | Χ | 1 | 0 | 0  | Χ | Χ | Χ | MCLK frequency = 4.096 MHz     |  |  |

| Χ | Χ | 1 | 0 | 1  | Χ | Χ | Χ | MCLK frequency = 6.144 MHz     |  |  |

| Χ | Χ | 1 | 1 | 0  | Χ | Χ | Χ | MCLK frequency = 6.144 MHz     |  |  |

| Х | Χ | 1 | 1 | 1  | Χ | Χ | Χ | MCLK frequency = 6.144 MHz     |  |  |

| Χ | 0 | Χ | Χ | Χ  | Χ | Χ | Χ | DLC receiver abort disabled    |  |  |

| Χ | 1 | Χ | Χ | Χ  | Χ | Χ | Χ | DLC receiver abort enabled     |  |  |

| 0 | Χ | Χ | Χ | Χ  | Χ | Χ | Χ | DLC transmitter abort disabled |  |  |

| 1 | Χ | Χ | Χ | Χ  | Χ | Χ | Χ | DLC transmitter abort enabled  |  |  |

# INIT2 Register (INIT2) default = 00H

Address = Indirect 20 Hex, Read/Write

A special write procedure must be followed in order to modify the contents of the INIT2 Register, since the INIT2 Register includes control bits which could result in the stopping of the microprocessor clock. This procedure greatly reduces the probability of errant software disabling the system, and is described as follows:

- 1. Write the INIT2 address to the Command Register.

- 2. Write to the Data Register (INIT2 is not yet updated).

- 3. Write the INIT2 address to the Command Register.

- 4. Write to the Data Register (INIT2 is updated).

The writes must take place without any intervening indirect accesses to the DSC/IDC circuit.

Table 2. INIT2 Register

Dia

|   |   |   | В | it |   |   |   |                                                                                                                |  |  |  |

|---|---|---|---|----|---|---|---|----------------------------------------------------------------------------------------------------------------|--|--|--|

| 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | Function                                                                                                       |  |  |  |

| 0 | 0 | Х | Х | Х  | Х | Х | Х | Reserved, must be written to 0;<br>READs are undefined                                                         |  |  |  |

| 0 | 0 | 0 | X | X  | X | X | X | Power-Down disabled; writing 11 to the INIT Register will put the DSC/IDC circuit into Idle mode               |  |  |  |

| 0 | 0 | 1 | X | X  | X | X | X | Power-Down enabled; writing<br>11 to the INIT Register will put<br>the DSC/IDC circuit into<br>Power-Down mode |  |  |  |

| 0 | 0 | Χ | 0 | Χ  | Χ | Χ | Χ | Multiframe Interrupt filter disabled                                                                           |  |  |  |

| 0 | 0 | X | 1 | X  | Χ | X | Х | Multiframe Interrupt filter enabled (see LIU section for detailed description)                                 |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 0 | Χ | Χ | Clock speed-up option disabled                                                                                 |  |  |  |

| 0 | 0 | X | X | X  | 1 | X | X |                                                                                                                |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 0 | 0 | 0 | MCLK frequency determined by INIT Register                                                                     |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 0 | 0 | 1 | MCLK frequency is 1.536 MHz                                                                                    |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 0 | 1 | 0 | MCLK frequency is 768 kHz                                                                                      |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 0 | 1 | 1 | MCLK frequency is 384 kHz                                                                                      |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 1 | 0 | 0 | MCLK stopped in High state                                                                                     |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 1 | 0 | 1 | Reserved                                                                                                       |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 1 | 1 | 0 | Reserved                                                                                                       |  |  |  |

| 0 | 0 | Χ | Χ | Χ  | 1 | 1 | 1 | Reserved                                                                                                       |  |  |  |

# **RESET Operation**

The Am79C30A/32A can be reset by driving the RESET pin High. When power is first supplied to the DSC/IDC circuit, a reset must be performed. This initializes the DSC/IDC circuit to its default condition as defined in Table 3.

Table 3. Reset Pin Conditions

| Pin Name | State Following RESET |

|----------|-----------------------|

| D7-D0    | High Impedance        |

| MCLK     | 6.144 MHz             |

| INT      | Logical 1             |

| SBOUT    | High Impedance        |

| SFS      | High Impedance        |

| SCLK     | High Impedance        |

| LS1, LS2 | High Impedance        |

| EAR1     | High Impedance        |

| EAR2     | High Impedance        |

| AREF     | High Impedance        |

| LOUT1    | High Impedance        |

| LOUT2    | High Impedance        |

### **Receive and Transmit Abort Commands**

The microprocessor has the option via INIT Register bits 6 and 7 to abort the receive and transmit D-channel packets. When the microprocessor sets one of these bits, the Am79C30A/32A aborts the respective operation. The frame abort sequence is defined in greater detail later. (See the Data Link Controller section on page 36.)

# Interrupt Handling

The Am79C30A/32A generates either no interrupt or only one interrupt every 125  $\mu$ s. Once asserted,  $\overline{INT}$  remains active until the microprocessor responds by interrogating the Am79C30A/32A's Interrupt Register (IR) (see Table 4). Reading the IR in response to an activated  $\overline{INT}$  pin deactivates the  $\overline{INT}$  pin and clears the IR.

If an event causing an interrupt occurs while the IR is being read by the microprocessor, the effect of the event is held until the microprocessor has completed its read cycle. A reset clears all conditions causing interrupts.

Bits 0, 1, and 4 of the IR, if set, advise the microprocessor that the respective buffer is ready for reading or writing. If bit 0 is set due to an empty buffer, the D-channel Transmit buffer must be serviced within 375  $\mu$ s. If bit 1 is set and the D-channel Receive buffer is full, the buffer must be serviced within 425  $\mu$ s. This is to prevent erroneous data transfers causing transmitter underrun and receiver overrun errors. If bit 4 is set then the Bb or

Bc buffers must be accessed within 122.4  $\mu$ s. This is to prevent erroneous data transfers. Only one interrupt is used to signal accessibility for both B channels of the S Interface. Since the data transfer must occur synchronously to the S Interface, any data access to either Bb or Bc or both must be made within the122.4  $\mu$ s limit.

Note that even though only a single interrupt is issued, either or both S-Interface B channels must be serviced. IR bits 2, 3, 5, 6, and 7, if set, indicate that a bit has been set in the associated status or error register. All of the interrupts generated by the Am79C30A/32A can be

individually disabled. In the case of IR bit 7, the interrupt can also be masked by setting PPIER bit 7 to 0.

DMR1, DMR2, DMR3, LMR2, MCR4, and MF control the mask conditions that affect the INT pin. The INT pin is activated only by interrupts that are not disabled. The Interrupt Register reflects the status of enabled interrupts. The INT pin can be disabled by setting INIT Register bit 2 to a logical 1.

The Am79C30A/32A has facilities that allow the microprocessor to read the status registers (status update is inhibited during status read) or the IR at any time during functional operation.

Table 4. Format of the Interrupt Register (IR), Read Only

| Bit | Interrupt Genera   | ated/Action Required                                             | Interrupt Mask |

|-----|--------------------|------------------------------------------------------------------|----------------|

| 0   | D-channel transm   | nit threshold interrupt/load D-channel Transmit buffer           | DMR1 bit 0     |

| 1   | D-channel receive  | e threshold interrupt/read D-channel Receive buffer              | DMR1 bit 1     |

| 2   | D-channel status   | interrupt/read DSR1                                              |                |

|     | Source             | Cause                                                            |                |

|     | DSR1 bit 0         | Valid Address (VA) or End of Address (EOA)                       | DMR3 bit 0     |

|     | DSR1 bit 1         | When a closing flag is received or a receive error occurs        | DMR1 bit 3     |

|     | DSR1 bit 6         | When a closing flag is transmitted DMR3 bit 1                    | DMR3 bit 1     |

| 3   | D-channel error in | nterrupt/read DER and DSR2 bit 2                                 |                |

|     | Source             | Cause                                                            |                |

|     | DER bit 0          | Current received packet has been aborted                         | DMR2 bit 0     |

|     | DER bit 1          | Non-integer number of bytes received                             | DMR2 bit 1     |

|     | DER bit 2          | Collision abort detected                                         | DMR2 bit 2     |

|     | DER bit 3          | FCS error                                                        | DMR2 bit 3     |

|     | DER bit 4          | Overflow error                                                   | DMR2 bit 4     |

|     | DER bit 5          | Underflow error                                                  | DMR2 bit 5     |

|     | DER bit 6          | Overrun error                                                    | DMR2 bit 6     |

|     | DER bit 7          | Underrun error                                                   | DMR2 bit 7     |

|     | DSR2 bit 2         | Receive packet lost                                              | DMR3 bit 6     |

| 4   | Bb or Bc byte ava  | ailable or buffer empty interrupt/read or write Bb or Bc buffers | MCR4 bit 3     |

| 5   | LIU status interru | pt/read LSR                                                      |                |

|     | Source             | Cause                                                            |                |

|     | LSR bit 3          | Change of state to F3                                            | LMR2 bit 3     |

|     | LSR bit 4          | Change of state from/to F7                                       | LMR2 bit 6     |

|     | LSR bit 5          | Change of state from/to F8                                       | LMR2 bit 4     |

|     | LSR bit 7          | HSW change of state                                              | LMR2 bit 5     |

| 6   | D-channel status   | interrupt/read DSR2                                              |                |

|     | Source             | Cause                                                            |                |

|     | DSR2 bit 0         | Last byte of received packet                                     | DMR3 bit 2     |

|     | DSR2 bit 1         | Receive byte available                                           | DMR3 bit 3     |

|     | DSR2 bit 3         | Last byte transmitted                                            | DMR3 bit 4     |

|     | DSR2 bit 4         | Transmit buffer available                                        | DMR3 bit 5     |

|     | DSR2 bit 7         | Start of second packet                                           | EFCR bit 1     |

| 7   | Multiframe or PP   | interrupt/read MFSB and PPSR                                     |                |

|     | Source             | Cause                                                            |                |

|     | MFSB bit 5         | S-data available                                                 | MF bit 1       |

|     | MFSB bit 6         | Q-bit buffer empty                                               | MF bit 2       |

|     | MFSB bit 7         | Multiframe change of state (in/out of sync)                      | MF bit 3       |

|     | PPSR bit 0         | Monitor receive, data available                                  | PPIER bit 0    |

|     | PPSR bit 1         | Monitor transmit, buffer available                               | PPIER bit 1    |

|     | PPSR bit 2         | Monitor EOM received                                             | PPIER bit 2    |

|     | PPSR bit 3         | Monitor abort received                                           | PPIER bit 3    |

|     | PPSR bit 4         | C/I channel 0, data change                                       | PPIER bit 4    |

|     | PPSR bit 5         | C/I channel 1, data change                                       | PPIER bit 5    |

|     | PPSR bit 6         | IOM-2 timing request                                             | PPIER bit 6    |

# **FUNCTIONAL DESCRIPTION**

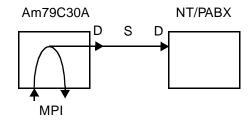

# **Microprocessor Interface (MPI)**

The Am79C30A/32A can be connected to any general purpose 8-bit microprocessor via the MPI. The MCLK from the Am79C30A/32A can be used as the clock for the microprocessor. The MPI is an interrupt-driven interface containing all the circuitry necessary for access to the internal programmable registers, status registers, coefficient RAM, and transmit/receive buffers.

### **MPI External Interface**

External connections to the MPI are shown in Table 5.

Table 5. MPI External Interface

| Name  | Direction     | Function       |

|-------|---------------|----------------|

| D7-D0 | Bidirectional | Data Bus       |

| A2-A0 | Inputs        | Address Line   |

| RD    | Input         | Read Enable    |

| WR    | Input         | Write Enable   |

| cs    | Input         | Chip Select    |

| RESET | Input         | Initialization |

| INT   | Output        | Interrupt      |

# **Direct Registers**

Access to the Direct Registers of the Am79C30A/32A is controlled by the state of the  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A2, A1, and A0 input pins, as defined below by Table 6.

# **Indirect Registers**

To read from or write to any of the Indirect Registers, an indirect address command is first written to the Command Register (CR). One or more data bytes may then be transferred to or from the selected register through the Data Register (DR).

Registers within certain groups can be accessed quickly by using internal circuitry which automatically increments the indirect value. In Table 7, the bytes transferred numbers are the number of bytes which are read or written to the DR after the CR has been loaded. Whenever the CR is loaded, any previous commands are automatically terminated.

Table 6. Direct Register Access Guide

| CS | RD | WR | A2 | A1 | A0 | Register(s) Accessed                                  | Mode |

|----|----|----|----|----|----|-------------------------------------------------------|------|

| 0  | 1  | 0  | 0  | 0  | 0  | Command Register (CR)                                 | W    |

| 0  | 0  | 1  | 0  | 0  | 0  | Interrupt Register (IR)                               | R    |

| 0  | 1  | 0  | 0  | 0  | 1  | Data Register (DR)                                    | W    |

| 0  | 0  | 1  | 0  | 0  | 1  | Data Register (DR)                                    | R    |

| 0  | 0  | 1  | 0  | 1  | 0  | D-channel Status Register 1 (DSR1)                    | R    |

| 0  | 0  | 1  | 0  | 1  | 1  | D-channel Error Register (DER) (2-byte FIFO)          | R    |

| 0  | 1  | 0  | 1  | 0  | 0  | D-channel Transmit buffer (DCTB) (8- or 16-byte FIFO) | W    |

| 0  | 0  | 1  | 1  | 0  | 0  | D-channel Receive buffer (DCRB) (8- or 32-byte FIFO)  | R    |

| 0  | 1  | 0  | 1  | 0  | 1  | Bb-channel Transmit buffer (BBTB)                     |      |

| 0  | 0  | 1  | 1  | 0  | 1  | Bb-channel Receive buffer (BBRB)                      | R    |

| 0  | 1  | 0  | 1  | 1  | 0  | Bc-channel Transmit buffer (BCTB)                     | W    |

| 0  | 0  | 1  | 1  | 1  | 0  | Bc-channel Receive buffer (BCRB)                      | R    |

| 0  | 0  | 1  | 1  | 1  | 1  | D-channel Status Register 2 (DSR2)                    | R    |

| 1  | Х  | Х  | Х  | Х  | Х  | No access (X = logical 0 or 1)                        | _    |

#### Note:

The  $\overline{RD}$  and  $\overline{WR}$  signals must never both be Low under normal operating conditions.

Table 7. Indirect Register Access Guide

| Operation<br>Block | Register                                          | Register<br>Number | Indirect Name | Mode | Address | Byte Sequence        |

|--------------------|---------------------------------------------------|--------------------|---------------|------|---------|----------------------|

| INIT               | Initialization Register                           | 1                  | INIT          | R/W  | 21H     | One byte transferred |

| INIT               | Initialization Register 2                         | 2                  | INIT2         | R/W  | 20H     | One byte transferred |

| LIU                | LIU Status Register                               | 1                  | LSR           | R    | A1H     | One byte transferred |

| LIU                | LIU Priority Register                             | 2                  | LPR           | R/W  | A2H     | One byte transferred |

| LIU                | LIU Mode Register 1                               | 3                  | LMR1          | R/W  | A3H     | One byte transferred |

|                    |                                                   |                    |               |      |         | One byte transferred |

| LIU                | LIU Mode Register 2                               | 4                  | LMR2          | R/W  | A4H     | One byte transferred |

| LIU                | _                                                 | 5                  | Perform 2-4   | -    | A5H     |                      |

| LIU                | Multiframe Register                               | 6                  | MF            | R/W  | A6H     | One byte transferred |

| LIU                | Multiframe S-bit/Status Register                  | 7                  | MFSB          | R    | A7H     | One byte transferred |

| LIU                | Multiframe Q-bit buffer                           | 8                  | MFQB          | W    | A8H     | One byte transferred |

| MUX                | MUX Control Register 1                            | 1                  | MCR1          | R/W  | 41H     | One byte transferred |

| MUX                | MUX Control Register 2                            | 2                  | MCR2          | R/W  | 42H     | One byte transferred |

| MUX                | MUX Control Register 3                            | 3                  | MCR3          | R/W  | 43H     | One byte transferred |

| MUX                | MUX Control Register 4                            | 4                  | MCR4          | R/W  | 44H     | One byte transferred |

| MUX                | _                                                 | 5                  | Perform 1-4   | _    | 45H     | MCR1, 2, 3, 4        |

| MAP                | X filter Coefficient Register                     | 1                  | X Coeff.      | R/W  | 61H     | h0 LSB, h0 MSBh7 MSB |

| MAP                | R filter Coefficient Register                     | 2                  | R Coeff.      | R/W  | 62H     | h0 LSB, h0 MSBh7 MSB |

| MAP                | GX Gain Coefficient Register                      | 3                  | GX Coeff.     | R/W  | 63H     | LSB, MSB             |

| MAP                | GR Gain Coefficient Register                      | 4                  | GR Coeff.     | R/W  | 64H     | LSB, MSB             |

| MAP                | GER Gain Coefficient Register                     | 5                  | GER Coeff.    | R/W  | 65H     | LSB, MSB             |

| MAP                | Sidetone Gain Coefficient Register                | 6                  | STG Coeff.    | R/W  | 66H     | LSB, MSB             |

| MAP                | Frequency Tone Generator Register 1, 2            | 7                  | FTGR1,FTGR2   | R/W  | 67H     | FTGR1, 2             |

| MAP                | Amplitude Tone Generator Register 1, 2            | 8                  | ATGR1,ATGR2   | R/W  | 68H     | ATGR1, 2             |

| MAP                | MAP Mode Register 1                               | 9                  | MMR1          | R/W  | 69H     | One byte transferred |

| MAP                | MAP Mode Register 2                               | 10                 | MMR2          | R/W  | 6AH     | One byte transferred |

| MAP                | _                                                 | 11                 | Perform 1–10  | _    | 6BH     | 46 bytes loaded 1–10 |

| MAP                | MAP Mode Register 3                               | 12                 | MMR3          | R/W  | 6CH     | One byte transferred |

| MAP                | Secondary Tone Ringer Amplitude                   | 13                 | STRA          | R/W  | 6DH     | One byte transferred |

| MAP                | Secondary Tone Ringer Frequency                   | 14                 | STRF          | R/W  | 6EH     | One byte transferred |

| MAP                | Transmit Peak Register                            | 15                 | PEAKX         | R    | 70H     | One byte transferred |

| MAP                | Receive Peak Register                             | 16                 | PEAKR         | R    | 71H     | One byte transferred |

| MAP                | _                                                 | 17                 | Perform 15–16 | R    | 72H     | One byte transferred |

| DLC                | First Received Byte Address<br>Registers 1, 2, 3  | 1                  | FRAR 1, 2, 3  | R/W  | 81H     | FRAR1, 2             |

| DLC                | Second Received Byte Address<br>Registers 1, 2, 3 | 2                  | SRAR1, 2, 3   | R/W  | 82H     | SRAR1, 2             |

| DLC                | Transmit Address Register                         | 3                  | TAR           | R/W  | 83H     | LSB, MSB             |

| DLC                | D-channel Receive Byte Limit<br>Register          | 4                  | DRLR          | R/W  | 84H     | LSB, MSB             |

| DLC                | D-channel Transmit Byte Count<br>Register         | 5                  | DTCR          | R/W  | 85H     | LSB, MSB             |

Table 7. Indirect Register Access Guide (Continued)

| Operation<br>Block | Register                                     | Register<br>Number | Indirect Name | Mode | Address | Byte Sequence               |

|--------------------|----------------------------------------------|--------------------|---------------|------|---------|-----------------------------|

| DLC                | D-channel Mode Register 1                    | 6                  | DMR1          | R/W  | 86H     | One byte transferred        |

| DLC                | D-channel Mode Register 2                    | 7                  | DMR2          | R/W  | 87H     | One byte transferred        |

| DLC                | _                                            | 8                  | Perform 1-7   | _    | 88H     | 4 bytes loaded 1–7          |

| DLC                | D-channel Receive Byte Count<br>Register     | 9                  | DRCR          | R    | 89H     | LSB, MSB                    |

| DLC                | Random Number Generator Register             | 10                 | RNGR1 (LSB)   | R/W  | 8AH     | One byte transferred        |

| DLC                | Random Number Generator Register             | 11                 | RNGR2 (MSB)   | R/W  | 8BH     | One byte transferred        |

| DLC                | First Received Byte Address<br>Register 4    | 12                 | FRAR4         | R/W  | 8CH     | One byte transferred        |

| DLC                | Second Received Byte Address<br>Register 4   | 13                 | SRAR4         | R/W  | 8DH     | One byte transferred        |

| DLC                | D-channel Mode Register 3                    | 14                 | DMR3          | R/W  | 8EH     | One byte transferred        |

| DLC                | D-channel Mode Register 4                    | 15                 | DMR4          | R/W  | 8FH     | One byte transferred        |

| DLC                | _                                            | 16                 | Perform 12–15 | _    | 90H     | FRAR4, SRAR4, DMR3,<br>DMR4 |

| DLC                | Address Status Register                      | 17                 | ASR           | R    | 91H     | One byte transferred        |

| DLC                | Extended FIFO Control Register               | 18                 | EFCR          | R/W  | 92H     | One byte transferred        |

| PP                 | Peripheral Port Control Register 1           | 1                  | PPCR1         | R/W  | C0H     | One byte transferred        |

| PP                 | Peripheral Port Status Register              | 2                  | PPSR          | R    | C1H     | One byte transferred        |

| PP                 | Peripheral Port Interrupt Enable<br>Register | 3                  | PPIER         | R/W  | C2H     | One byte transferred        |

| PP                 | Monitor Transmit Data Register               | 4                  | MTDR          | W    | СЗН     | One byte transferred        |

| PP                 | Monitor Receive Data Register                | 5                  | MRDR          | R    | СЗН     | One byte transferred        |

| PP                 | C/I Transmit Data Register 0                 | 6                  | CITDR0        | W    | C4H     | One byte transferred        |

| PP                 | C/I Receive Data Register 0                  | 7                  | CIRDR0        | R    | C4H     | One byte transferred        |

| PP                 | C/I Transmit Data Register 1                 | 8                  | CITDR1        | W    | C5H     | One byte transferred        |

| PP                 | C/I Receive Data Register 1                  | 9                  | CIRDR1        | R    | C5H     | One byte transferred        |

| PP                 | Peripheral Port Control Register 2           | 10                 | PPCR2         | R/W  | C8H     | One byte transferred        |

| PP                 | Peripheral Port Control Register 3           | 11                 | PPCR3         | R/W  | C9H     | One byte transferred        |

# **Line Interface Unit (LIU)**

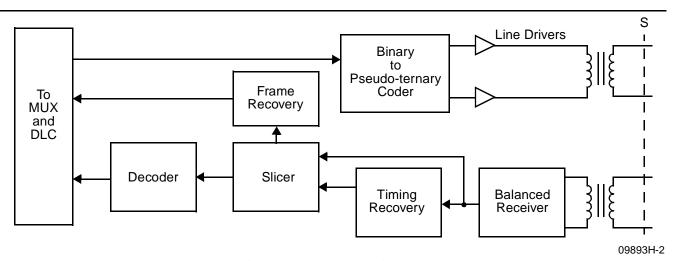

The LIU connects to the four-wire S Interface through a pair of isolation transformers, one for the transmit and one for the receive direction, as shown in Figure 1.

The receiver section of the LIU consists of a differential receiver, circuitry for bit timing recovery, circuitry for detecting High and Low marks, and a frame recovery circuit for frame synchronization. The receiver converts the received pseudo-ternary coded signals to binary before delivering them to the other blocks of the Am79C30A/32A. It also performs collision detection (E-and D-bit comparison) per the CCITT recommenda-

tions so several TEs can be connected to the same S Interface.

The transmitter consists of a binary to pseudo-ternary encoder and a differential line driver which meets the CCITT recommendations for the S Interface.

The Am79C30A/32A can establish multiframe synchronization, receive S bits, and transmit Q bits synchronized to the received frame.

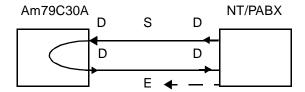

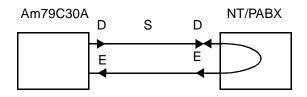

### **External Interface**

The LIU can be connected to both point-to-point and point-to-multipoint configurations at the CCITT S reference point. The point-to-point configuration consists of one TE connected to the NT or PABX linecard. The

point-to-multipoint configuration can have multiple TEs connected to one NT.

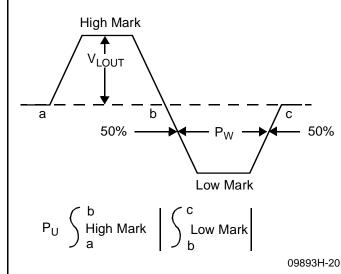

#### **Line Code**

Pseudo-ternary coding is used for both transmitting and receiving over the S Interface. In this type of coding, a binary 1 is represented by a space (zero voltage), and a binary 0 is represented by a High mark or a Low mark. Two consecutive binary 0s are represented by alternate marks to reduce DC offset on the line. A mark followed, either immediately or separated by spaces, by a mark of the same polarity, is defined as a code violation. Code violations are used to identify the boundaries of the frame.

#### Note:

The DSC defines "Any Signal" as any frame with at least three marks above receive threshold.

#### **Frame Structures**

In both transmit and receive directions, the bits are grouped into frames of 48 bits each. The frame structure is identical for both point-to-point and point-to-multipoint configurations. Each frame transmitted at 4 kHz consists of several groups of bits.

#### Multiframing

If multiframing is enabled, the Am79C30A/32A recognizes and establishes multiframe synchronization based on the monitoring of the  $F_A$  (Q-bit control) and M (M-bit control) bits. The Am79C30A/32A also receives and compiles S bits, and transmits Q bits synchronized to the received frame.

### **Establishment of Multiframe Synchronization**

When the enable multiframe synchronization bit (bit 0 of the Multiframe Register) is set and the LIU is in either state F6 or F7, the LIU monitors the  $F_A$  (Q-bit control) and M (M-bit control) bits. When three consecutive multiframes with the M bits and  $F_A$  bits set as defined in Table 8 are received, the multiframe synchronized bit

(bit 7 of the Multiframe Register) and multiframe change of state bit (bit 7 of the Multiframe S bit/Status buffer) are set. Note that S-bit data is received, compiled, and transferred to the user after attaining synchronization at the start of the next multiframe.

# S-Bit Reception

The default operation of the DSC/IDC circuit is that the LIU will receive and pass multiframe data to the user in 5-bit increments four times per multiframe, regardless of the value of the data. After multiframe synchronization has been requested and established the microprocessor can read the Multiframe S bit/Status buffer (MFSB) once the S-bit available bit (MFSB bit 5) is set. The S-data available bit is set to a logical 1 when the Am79C30A/32A has received five S bits (one S bit per S-interface frame) synchronized to the setting of the F<sub>A</sub>-bit to a logical 1 and transferred them into the MFSB. Once the S-bit available bit is set, the MFSB must be accessed within 1.25 ms or succeeding S data will be lost.

Subsequent to the original definition of the DSC/IDC circuit, the CCITT has defined a structure for the 20 multiframe bits, which specifies five 4-bit channels. Furthermore, the idle code for these channels has been defined as 0000. An enhanced mode of multiframe reception has been included, which may be enabled by setting INIT2 bit 4 to a 1. This enhanced mode reduces processor overhead by generating an interrupt only upon the reception of a non-zero S-channel word. INIT2 bit 4 will be automatically cleared by hardware when the five received data bits in the MFSB are not all 0s, as long as MF bit 1 (interrupt enable) is set. This allows subsequent valid all-zero words to be received. Furthermore, when the first five S bits of the multiframe are loaded into the MFSB, bit 4 of the MF register will be set, which allows identification of the position of received words within the multiframe.

Figure 1. LIU Block Diagram

**Table 8. Multiframing Structures**

| Frame Number | NT-to-TE Q Control Bit FA | NT-to-TE M Bit (M) | NT-to-TE S Bit (S) | TE-to-NT FA Bit (Q Bit) |

|--------------|---------------------------|--------------------|--------------------|-------------------------|

| 1            | 1                         | 1                  | SC11               | Q1                      |

| 2            | 0                         | 0                  | SC21               | 0                       |

| 3            | 0                         | 0                  | SC31               | 0                       |

| 4            | 0                         | 0                  | SC41               | 0                       |

| 5            | 0                         | 0                  | SC51               | 0                       |

| 6            | 1                         | 0                  | SC12               | Q2                      |

| 7            | 0                         | 0                  | SC22               | 0                       |

| 8            | 0                         | 0                  | SC32               | 0                       |

| 9            | 0                         | 0                  | SC42               | 0                       |

| 10           | 0                         | 0                  | SC52               | 0                       |

| 11           | 1                         | 0                  | SC13               | Q3                      |

| 12           | 0                         | 0                  | SC23               | 0                       |

| 13           | 0                         | 0                  | SC33               | 0                       |

| 14           | 0                         | 0                  | SC43               | 0                       |

| 15           | 0                         | 0                  | SC53               | 0                       |

| 16           | 1                         | 0                  | SC14               | Q4                      |

| 17           | 0                         | 0                  | SC24               | 0                       |

| 18           | 0                         | 0                  | SC34               | 0                       |

| 19           | 0                         | 0                  | SC44               | 0                       |

| 20           | 0                         | 0                  | SC54               | 0                       |

| 1            | 1                         | 1                  | SC11               | Q1                      |

| 2            | 0                         | 0                  | SC21               | 0                       |

| etc.         |                           |                    |                    |                         |

#### Transmission of Q bits

The microprocessor can load the Multiframe Q-bit buffer (MFQB) once the Q-bit buffer empty bit (bit 6 of the Multiframe S bit/Status buffer) is set. The Q-bit buffer empty bit is set to a logical 1 at reset or when data that has been written to the Multiframe Q-bit buffer is transferred to the LIU. The Q-bit buffer empty bit is cleared to a logical 0 when the Multiframe S-bit/Status buffer is read. After multiframing has been requested and established, the Am79C30A/32A transfers the data written into the Q-bit Register to the LIU, synchronized to the multiframe, irrespective of the receipt of valid Q-control bits. If the microprocessor does not reload the Q-bit Register for retransmissions, the Q-bit pattern is repeated in the next multiframe.

If multiframing is enabled but multiframe synchronization is not established, the LIU transmits the value loaded in MFQB bit 4 in all Q bits. The default value of MFQB bit 4 is a logical 0 which satisfies the CCITT recommendations. When synchronization is achieved, the contents of MFQB bits 3 to 0 are transmitted according to Table 8.

#### Loss of Multiframe Synchronization

The Am79C30A/32A continuously monitors the FA (Q-bit control) and the M bits to ensure multiframe synchronization. Once multiframe synchronization is established, multiframe synchronization is lost if three consecutive invalid multiframes are received, or the LIU is no longer in state F6 or F7, or multiframing is disabled. When loss of multiframe synchronization occurs, bit 7 of the Multiframe Register is set to a logical 0, and bit 7 of the Multiframe S bit/Status buffer is set to a logical 1. The Am79C30A/32A also terminates the reception of S bits and transmission of Q bits until multiframing synchronization is re-established.

# **HSW**

The hookswitch circuitry on the DSC circuit provides the attached microprocessor with a way of converting an external mechanical hookswitch into a software status condition capable of generating an interrupt. Debounce and glitch rejection are provided internal to the DSC circuit. The logic rejects glitches less than 162 ns and provides debounce of 16 ms. HSW status reporting is disabled after RESET. It is enabled by any of the following: taking the device out of Idle mode, a write to a MUX Control Register (MCR3–MCR1), or unmasking the HSW interrupt.

# **LIU Registers**

The LIU contains the registers shown in Table 9.

Table 9. LIU Registers

| Registers                           | No./Registers | Mnemonic   |

|-------------------------------------|---------------|------------|

| LIU Status Register                 | 1             | LSR        |

| LIU Priority Register               | 1             | LPR        |

| LIU Mode Registers                  | 2             | LMR1, LMR2 |

| Multiframe Register                 | 1             | MF         |

| Multiframe S-bit/Status<br>Register | 1             | MFSB       |

| Multiframe Q-bit buffer             | 1             | MFQB       |

### LIU Status Register (LSR), Read Only

Address = Indirect A1H

The LSR format is shown in Table 10.

Table 10. LIU Status Register

| Bit | Logical 1                                                                                                                       | Generates<br>Interrupt |

|-----|---------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 0-2 | Binary values 000 through 110 represent the LIU activation circuitry's current state (F2 through F8, respectively) bit 2 is MSB | No                     |

| 3   | Change of state to F3                                                                                                           | If LMR2 bit 3 = 1      |

| 4   | Change of state from/to F7                                                                                                      | If LMR2 bit 6 = 1      |

| 5   | Change of state from/to F8                                                                                                      | If LMR2 bit 4 = 1      |

| 6   | HSW state                                                                                                                       | No                     |

| 7   | HSW change of state                                                                                                             | If LMR2 bit 5 = 1      |

When the microprocessor reads the LSR, bits 3, 4, 5, and 7 are cleared. The other bits retain the current status of the LIU. bits 0 to 2 are defined such that state F2 (see CCITT I.430 state matrix tables) is coded as 0, F3

as 1, F4 as 2, and so on, where bit 0 is the LSB. The LIU interrupts the microprocessor via bit 4 of the LSR when activation has been achieved (that is, when the LIU moves to state F7 upon receipt of INFO 4). During reset the LSR is 0.

Even though the LIU Status Register (LSR) is read-only, no default value upon power-up is given due to the uncertain state of bit 6 (Hookswitch State). Following RESET, the LIU State is F2 and the HSW bit reflects the HSW pin, producing a power-up value of either 00H or 40H.

### LIU D-Channel Priority Register (LPR), Read/Write

The LPR contains the priority level for D-channel access. Its default value after reset is 0.

The D-channel access procedure of the Am79C30A/ 32A uses the priority level programmed in the LPR. The priority mechanism defined by the CCITT I-series recommendations is fully implemented if the LPR is programmed via the microprocessor to conform to the priority class of the Layer-2 frame to be transmitted. The LPR has 16 possible programmable priority levels. The priority levels are numbered 0-15. Priority Level 0 corresponds to counting eight 1s in the echo channel, priority Level 1 corresponds to counting ten 1s in the echo channel, priority Level 2 corresponds to counting twelve 1s, etc. The DSC circuit automatically handles transitions between the programmed priority level n and the associated odd value n + 1. The priority is incremented following a successfully transmitted packet, and decremented when the higher count has been satisfied.

The LPR format is shown in Table 11.

Table 11. LIU Priority Register

| Bits       | Description                                  |

|------------|----------------------------------------------|

| 3, 2, 1, 0 | D-channel access priority level bit 0 is LSB |

| 7, 6, 5, 4 | Reserved, reads logical 0                    |

# LIU Mode Register (LMR1), Read/Write

Address = Indirect A3H

LMR1 is defined in Table 12.

Table 12. LIU Mode Register 1

| Bit | Logical 1                          | Logical 0 (default value)          |

|-----|------------------------------------|------------------------------------|

| 0   | Enable B1 transmit                 | Disable B1 transmit                |

| 1   | Enable B2 transmit                 | Disable B2 transmit                |

| 2   | Disable F transmit                 | Enable F transmit                  |

| 3   | Disable F <sub>A</sub> transmit    | Enable F <sub>A</sub> transmit     |

| 4   | Activation request                 | No activation request              |

| 5   | Go from F8 to F3                   | No transition                      |

| 6   | Enable receiver/transmitter        | Disable receiver/transmitter       |

| 7   | Reserved; must be set to logical 0 | Reserved; must be set to logical 0 |

#### Notes:

The F and  $F_A$  bits in LMR1 (bits 2 and 3) should be enabled during the activation procedure so the Am79C30A/32A can respond with INFO 3.

LMR1 bit 4 is used to transfer the signals PH-AR and Expiry of Timer from the microprocessor to the LIU (see CCITT I.430 state diagram—activation request). PH-AR is defined as bit 4 being a logical 1 and Expiry of Timer is defined as the transition of bit 4 from a logical 1 to a logical 0. This bit must not be set until the LIU, as reflected in the LSR, is in state F3, F6, or F7 and the receiver has been enabled for a minimum of 250 µs.

LMR1 bit 6 is primarily used to disable the receiver when the terminal does not require access to the S Interface signals. This bit is cleared by reset and must be written to logical 1 in order to receive activation from the S Interface, or to request activation.

# LIU Mode Register 2 (LMR2), Read/Write

Address = Indirect A4H

LMR2 is used to select the operations found in Table 13.

Table 13. LIU Mode Register 2

| Bit | Logical 1                                 | Logical 0 (Default Value)                  |

|-----|-------------------------------------------|--------------------------------------------|

| 0   | D-channel loopback at Am79C30A/32A enable | D-channel loopback at Am79C30A/32A disable |

| 1   | D-channel loopback at LIU enable          | D-channel loopback at LIU disable          |

| 2   | D-channel back-off disable                | D-channel back-off enable                  |

| 3   | F3 change of state interrupt enable       | F3 change of state interrupt disable       |

| 4   | F8 change of state interrupt enable       | F8 change of state interrupt disable       |

| 5   | HSW interrupt enable                      | HSW interrupt disable                      |

| 6   | F7 change of state interrupt enable       | F7 change of state interrupt disable       |

| 7   | Reserved; must be set to logical 0        | Reserved; must be set to logical 0         |

The three D-channel loopback controls defined in LMR2 bits 0, 1, and 2 are explained below:

Bit 0, D-channel loopback at Am79C30A/32A enable:

This remote loopback is provided for maintenance purposes from the NT's perspective. The NT transmits D-channel bits to the Am79C30A/32A where they are internally looped (with the Data Link Controller) and transmitted back to the NT. The incoming D-channel data can be accessed by the microprocessor; however, the microprocessor cannot send data on the outgoing D channel.

Any difference between the transmitted D-channel bits and the received E-channel bits to/from the Am79C30A/32A (normally detected as an error which halts the transmission) is ignored, thereby allowing the transmission to continue.

Bit 1, D-channel loopback at LIU enable:

This local loopback is provided for local testing. Data on the incoming D channel is ignored. The data from the microprocessor is processed by the DLC and then looped back to the microprocessor.

Bit 2, D-channel back-off disable:

This loopback is provided for maintenance purposes from the TE's perspective. The Am79C30A/32A transmits D-channel bits to the NT where they are looped and transmitted back to the Am79C30A/32A in the E channel. The operation is normal except differences between the D and E channels do not halt the transmission.

# Multiframe Register (MF), Read/Write

Address = Indirect A6H

Table 14. Multiframe Register

| Bit  | Logical 1                                   | Logical 0 (Default Value)               |  |  |

|------|---------------------------------------------|-----------------------------------------|--|--|

| 0    | Enable Multiframe sync                      | Disable Multiframe sync                 |  |  |

| 1    | Enable S-data available interrupt           | Disable interrupt                       |  |  |

| 2    | Enable Q-bit buffer empty interrupt         | Disable interrupt                       |  |  |

| 3    | Enable Multiframe change of state interrupt | Disable interrupt                       |  |  |

| 4    | First subframe                              | Not first subframe                      |  |  |

| 5, 6 | Not used, reads logical 0                   | Not used, reads logical 0               |  |  |

| 7    | Multiframe synchronized (read only)         | Multiframe not synchronized (read only) |  |  |

# Multiframe S-bit/Status Buffer (MFSB), Read Only

Address = Indirect A7H

Table 15. Multiframe S-Bit/Status Buffer

| Bit | Description                | Generates Interrupt |

|-----|----------------------------|---------------------|

| 0   | S1                         | No                  |

| 1   | S2                         | No                  |

| 2   | S3                         | No                  |

| 3   | S4                         | No                  |

| 4   | S5                         | No                  |

| 5   | S-data available           | If MF bit 1 = 1     |

| 6   | Q-bit buffer empty         | If MF bit 2 = 1     |

| 7   | Multiframe change of state | If MF bit 3 = 1     |

The MFSB reset default value is 40H.

# Multiframe Q-bit Buffer (MFQB), Write Only

Address = Indirect A8H

Table 16. Multiframe Q-Bit Buffer

| Bit     | Description                                                                          |

|---------|--------------------------------------------------------------------------------------|

| 0       | Q1 (default = 1)                                                                     |

| 1       | Q2 (default = 1)                                                                     |

| 2       | Q3 (default = 1)<br>Q4 (default = 1)                                                 |

| 3       | Q4 (default = 1)                                                                     |

| 4       | Q-bit value when multiframing enabled but synchronization not achieved (default = 0) |

| 5, 6, 7 | Not used                                                                             |

# Multiplexer (MUX)

The MUX contains the registers found in Table 17.

Table 17. MUX Registers

| Register                 | No./Registers | Mnemonic                  |

|--------------------------|---------------|---------------------------|

| MUX Control<br>Registers | 4             | MCR1, MCR2, MCR3,<br>MCR4 |

The Multiplexer is used to selectively route 64-Kbit/s full-duplex B channels between the LIU (Line Interface Unit), MAP (Main Audio Processor), MPI (Microprocessor Interface), and the PP (Peripheral Port).

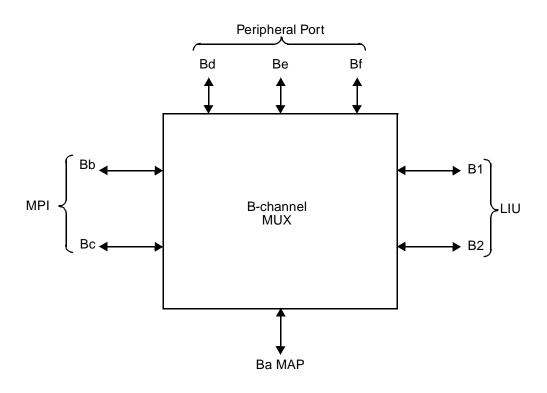

The logical channels available at the MUX are shown in Figure 2, They are:

- 1. From/to the LIU channels B1 and B2

- 2. From/to the MAP channel Ba

- 3. From/to the MPI channels Bb and Bc

- 4. From/to the PP channels Bd, Be, and Bf

For any specific application, the MUX can be programmed by the microprocessor to route any three B-channel ports to any other three B-channel ports. Programmable bidirectional bit reversal is provided for both of the MPI data channels Bb and Bc.

# MUX Control Registers 1, 2, and 3 (MCR1, MCR2, and MCR3), Read/Write

Addresses = Indirect 41H, 42H, 43H

The MUX can support three bidirectional paths. The contents of the MUX Control Registers MCR1, MCR2, and MCR3 direct the flow of data between the eight MUX logical B channels (see Figure 2). These three MCRs are programmed to connect any two B-channel ports together by writing the appropriate channel code into an MCR. These MCRs have the same format, where bits 7–4 indicate port 1 and bits 3–0 indicate port 2. In each of these three MCR registers, the channel codes found in Table 18 are used for both ports 1 and 2.

Table 18. MCR Register Channel Codes

| Code | Channel                       |  |  |  |  |  |  |  |

|------|-------------------------------|--|--|--|--|--|--|--|

| 0000 | No connection (default value) |  |  |  |  |  |  |  |

| 0001 | B1 (LIU)                      |  |  |  |  |  |  |  |

| 0010 | B2 (LIU)                      |  |  |  |  |  |  |  |

| 0011 | Ba (MAP)                      |  |  |  |  |  |  |  |

| 0100 | Bb (MPI)                      |  |  |  |  |  |  |  |

| 0101 | Bc (MPI)                      |  |  |  |  |  |  |  |

| 0110 | Bd (PP channel 1)             |  |  |  |  |  |  |  |

| 0111 | Be (PP channel 2)             |  |  |  |  |  |  |  |

| 1000 | Bf (PP channel 3)             |  |  |  |  |  |  |  |

For example, to connect B1(LIU) with Bb (MPI) and B2 (LIU) with Ba (MAP), the contents of the MCRs would be:

|          | F | 0 | rt 1 | 1 | ı | 90 | rt 2 | 2 |                         |

|----------|---|---|------|---|---|----|------|---|-------------------------|

| Register | 7 | 6 | 5    | 4 | 3 | 2  | 1    | 0 | Channel Connection      |

| MCR1     | 0 | 0 | 0    | 1 | 0 | 1  | 0    | 0 | B1 (LIU) ← Bb (MPI)     |

| MCR2     | 0 | 0 | 1    | 0 | 0 | 0  | 1    | 1 | B2 (LIU) ← Ba (MAP)     |

| MCR3     | 0 | 0 | 0    | 0 | 0 | 0  | 0    | 0 | No connect ← No connect |

09893H-3

Figure 2. MUX Logical Channels

Therefore, in this example, MCR1 provides a data link from the S Interface and MCR2 sets up a voice connection across the S Interface.

To loopback a channel, the same channel code is used for port 1 and port 2. For example, to loopback B1, B2, and Ba, the MCRs would be:

|          | F | 0 | rt 1 | 1 | F | 901 | rt 2 | 2 |                    |

|----------|---|---|------|---|---|-----|------|---|--------------------|

| Register | 7 | 6 | 5    | 4 | 3 | 2   | 1    | 0 | Channel Connection |

| MCR1     | 0 | 0 | 0    | 1 | 0 | 0   | 0    | 1 | B1 (LIU) Loopback  |

|          |   |   |      |   |   |     |      |   | B2 (LIU) Loopback  |

| MCR3     | 0 | 0 | 1    | 1 | 0 | 0   | 1    | 1 | Ba (MAP) Loopback  |

MCR3 has higher priority than MCR2. MCR2 has higher priority than MCR1.

If multiple connections are made to the same port, the data from the connecting ports in the highest priority

MCR will overwrite the data from the connecting port in the lower priority MCR, for example:

|          | F | 90 | rt 1 | 1 | ı | 901 | rt 2 | 2 |                            |

|----------|---|----|------|---|---|-----|------|---|----------------------------|

| Register | 7 | 6  | 5    | 4 | 3 | 2   | 1    | 0 | Channel Connection         |

| MCR1     | 0 | 0  | 0    | 0 | 0 | 0   | 0    | 0 | No connect                 |

| MCR2     | 0 | 0  | 0    | 1 | 0 | 1   | 0    | 0 | B1 (LIU) ← Bb (MPI)        |

| MCR3     | 0 | 1  | 0    | 0 | 0 | 0   | 1    | 1 | Bb (MPI) <b>←</b> Ba (MAP) |

The final data transfers are:

B1 (LIU) receives Bb (MPI), Ba (MAP) receives Bb (MPI),

Bb (MPI) receives Ba (MAP).

Therefore, the data transfer from B1 (LIU) to Bb (MPI) is lost in the arrangement proposed in MCR2.

# MUX Control Register 4 (MCR4), Read/Write

Address = Indirect 44H

The MUX Control Register 4 (MCR4) can prevent interrupt generation by masking the output of IR bit 4. MCR4 has the format shown in Table 19.

Table 19. MUX Control Register 4

| Bit | Logical 1                                                    | Logical 0 (Default Value)                           |

|-----|--------------------------------------------------------------|-----------------------------------------------------|

| 0–2 | Reserved, must be set to logical 0                           | Reserved, must be set to logical 0                  |

| 3   | Enable Bb- or Bc-channel byte available interrupt (IR Bit 4) | Disable interrupt                                   |

| 4   | Reverse bit order of Bb (LSB transmitted/received first)     | No Bb bit reversal (MSB transmitted/received first) |

| 5   | Reverse bit order of Bc (LSB transmitted/received first)     | No Bc bit reversal (MSB transmitted/received first) |

| 6   | Reserved, must be set to logical 0                           | Reserved, must be set to logical 0                  |

| 7   | Reserved, must be set to logical 0                           | Reserved, must be set to logical 0                  |

# Main Audio Processor (MAP)

(Am79C30A only)

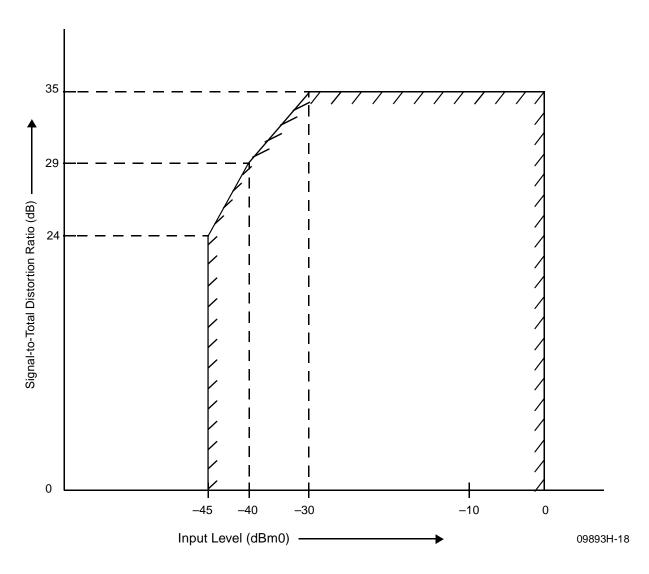

#### Overview