# International Rectifier

Data Sheet No. PD 97408A August 18, 2009

# IRS26072DSPbF HIGH AND LOW SIDE DRIVER

#### **Features**

- Floating channel designed for bootstrap operation

- Integrated bootstrap diode suitable for Complimentary PWM switching schemes only

- IRS26072DSPBF is suitable for sinusoidal motor control applications

- IRS26072DSPBF is NOT recommended for Trapezoidal motor control applications

- Fully operational to 600 V

- Tolerant to negative transient voltage, dV/dt immune

- Gate drive supply range from 10 V to 20 V

- Under-Voltage lockout for both channels

- 3.3 V, 5 V, and 15 V input logic compatible

- Matched propagation delay for both channels

- Lower di/dt gate driver for better noise immunity

- Outputs in phase with inputs

- RoHS compliant

## **Typical Applications**

- Motor Control

- Air Conditioners/ Washing Machines

- General Purpose Inverters

- Micro/Mini Inverter Drivers

#### **Product Summary**

| , , , , , , , , , , , , , , , , , , ,        |                          |  |  |  |

|----------------------------------------------|--------------------------|--|--|--|

| Topology                                     | high and low side driver |  |  |  |

| V <sub>OFFSET</sub>                          | ≤ 600 V                  |  |  |  |

| V <sub>OUT</sub>                             | 10 V – 20 V              |  |  |  |

| I <sub>o+</sub> & I <sub>o-</sub> (typical)  | 200 mA & 350 mA          |  |  |  |

| t <sub>ON</sub> & t <sub>OFF</sub> (typical) | 200 ns                   |  |  |  |

## Package Options

| Table of Contents                              | Page |

|------------------------------------------------|------|

| <u>Description</u>                             | 3    |

| Simplified Block Diagram                       | 3    |

| Typical Application Diagram                    | 4    |

| Qualification Information                      | 5    |

| Absolute Maximum Ratings                       | 6    |

| Recommended Operating Conditions               | 6    |

| Static Electrical Characteristics              | 7    |

| Dynamic Electrical Characteristics             | 7    |

| Functional Block Diagram                       | 8    |

| Input/Output Pin Equivalent Circuit Diagram    | 9    |

| Lead Definitions                               | 10   |

| Lead Assignments                               | 10   |

| Application Information and Additional Details | 11   |

| Parameter Temperature Trends                   | 21   |

| Package Details                                | 25   |

| Tape and Reel Details                          | 26   |

| Part Marking Information                       | 27   |

| Ordering Information                           | 28   |

## **Description**

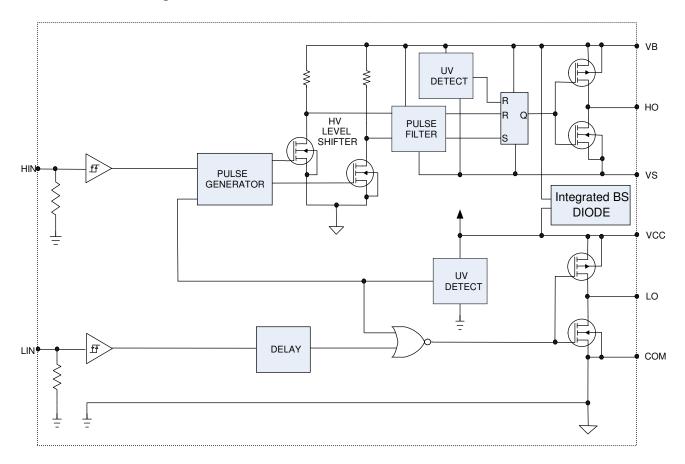

The IRS26072D is a high voltage, high speed power MOSFET and IGBT driver with independent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction. Logic inputs are compatible with CMOS or LSTTL outputs, down to 3.3 V. The output drivers feature a high-pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive N-channel power MOSFETs or IGBTs in the high side configuration up to 600 V.

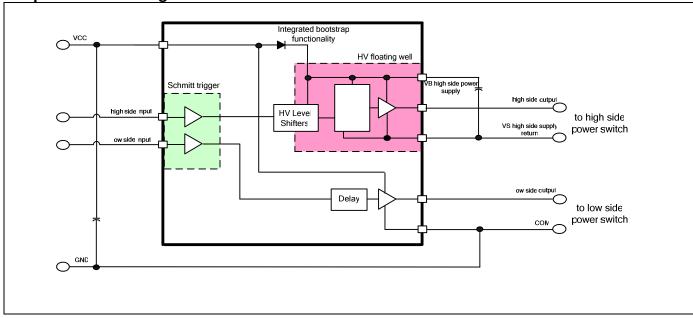

**Simplified Block Diagram**

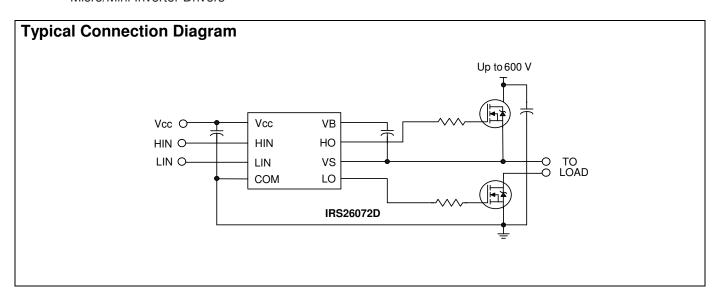

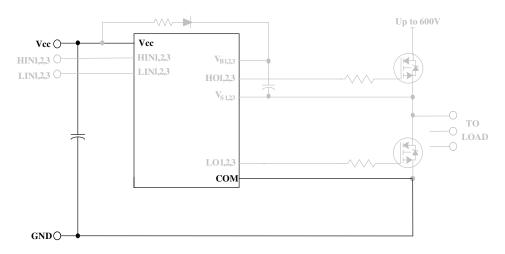

# **Typical Application Diagram**

## Qualification Information<sup>†</sup>

| Qualification Level        |                  | Industrial <sup>††</sup>                                                                                                                             |  |  |

|----------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                            |                  | Comments: This IC has passed JEDEC industrial qualification. IR consumer qualification level is granted by extension of the higher Industrial level. |  |  |

| Moisture Sensitivity Level |                  | MSL2, 260°C<br>(per IPC/JEDEC J-STD-020)                                                                                                             |  |  |

| ESD                        | Human Body Model | Class 2 (per JEDEC standard JESD22-A114)                                                                                                             |  |  |

| E3D                        | Machine Model    | Class B (per EIA/JEDEC standard EIA/JESD22-A115)                                                                                                     |  |  |

| IC Latch-Up Test           |                  | Class I, Level A<br>(per JESD78)                                                                                                                     |  |  |

| RoHS Compliant             |                  | Yes                                                                                                                                                  |  |  |

<sup>†</sup> Qualification standards can be found at International Rectifier's web site <a href="http://www.irf.com/">http://www.irf.com/</a> †† Higher qualification ratings may be available should the user have such requirements. Please contact your International Rectifier sales representative for further information.

#### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM unless otherwise specified. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                | Min.                 | Max.            | Units |

|---------------------|-------------------------------------------|----------------------|-----------------|-------|

| $V_{B}$             | High side floating supply voltage         | -0.3                 | 620             |       |

| $V_S$               | High side floating supply offset voltage  | $V_B - 20^{\dagger}$ | $V_{B} + 0.3$   |       |

| $V_{HO}$            | High side floating output voltage         | V <sub>S</sub> - 0.3 | $V_{B} + 0.3$   | V     |

| $V_{CC}$            | Low side and logic fixed supply voltage   | -0.3                 | 20 <sup>†</sup> | •     |

| $V_{LO}$            | Low side output voltage                   | -0.3                 | $V_{CC} + 0.3$  |       |

| V <sub>IN</sub>     | Logic and analog input voltages           | -0.3                 | $V_{CC} + 0.3$  |       |

| $PW_{HIN}$          | High-side input pulse width               | 500                  | _               | ns    |

| dV <sub>S</sub> /dt | Allowable offset supply voltage slew rate | _                    | 50              | V/ns  |

| $P_D$               | Package power dissipation @ TA ≤ +25 °C   | _                    | 0.625           | W     |

| Rth <sub>JA</sub>   | Thermal resistance, junction to ambient   | _                    | 200             | °C/W  |

| $T_J$               | Junction temperature                      | _                    | 150             |       |

| T <sub>S</sub>      | Storage temperature -50 150               |                      | 150             | ∞     |

| TL                  | Lead temperature (soldering, 10 seconds)  | _                    | 300             |       |

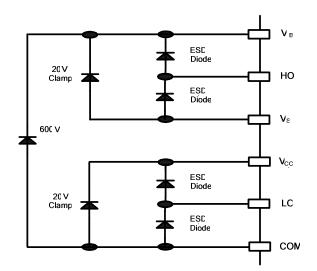

<sup>†</sup> All supplies are fully tested at 25 V. An internal 20 V clamp exists for each supply.

## **Recommended Operating Conditions**

For proper operation, the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to COM unless otherwise specified. The  $V_S$  offset ratings are tested with all supplies biased at 15 V.

| Symbol             | Definition                                                       | Min.               | Max.                | Units |

|--------------------|------------------------------------------------------------------|--------------------|---------------------|-------|

| V <sub>B</sub>     | High side floating supply voltage                                | V <sub>S</sub> +10 | V <sub>S</sub> + 20 |       |

| $V_S$              | Static high side floating supply offset voltage <sup>†</sup>     | -8                 | 600                 |       |

| V <sub>S</sub> (t) | Transient high side floating supply offset voltage <sup>††</sup> | -50                | 600                 |       |

| V <sub>HO</sub>    | High side floating output voltage                                | Vs                 | V <sub>B</sub>      | V     |

| $V_{CC}$           | Low side and logic fixed supply voltage                          | 10                 | 20                  |       |

| V <sub>LO</sub>    | Low side output voltage                                          | 0                  | V <sub>CC</sub>     |       |

| V <sub>IN</sub>    | Logic input voltage                                              | 0                  | V <sub>CC</sub>     |       |

| T <sub>A</sub>     | Ambient temperature                                              | -40                | 125                 | ℃     |

<sup>†</sup> Logic operation for  $V_S$  of -8 V to 600 V. Logic state held for  $V_S$  of -8 V to  $-V_{BS}$ .

<sup>††</sup> Operational for transient negative V<sub>S</sub> of -50 V with a 50 ns pulse width. Guaranteed by design. Refer to the Application Information section of this datasheet for more details.

## **Static Electrical Characteristics**

$(V_{CC}\text{-COM}) = (V_B\text{-}V_S) = 15 \text{ V}$  and  $T_A = 25 \,^{\circ}\text{C}$  unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to COM. The  $V_O$  and  $I_O$  parameters are referenced to COM and  $V_S$  and are applicable to the output leads LO and HO respectively. The  $V_{CCUV}$  and  $V_{BSUV}$  parameters are referenced to COM and  $V_S$  respectively.

| Symbol                                     | Definition                                                                        |      | Тур.           | Max.       | Units | Test Conditions                 |

|--------------------------------------------|-----------------------------------------------------------------------------------|------|----------------|------------|-------|---------------------------------|

| V <sub>IH</sub>                            | Logic "1" input voltage                                                           | 2.5  | _              | _          |       |                                 |

| V <sub>IL</sub>                            | Logic "0" input voltage                                                           |      | _              | 0.8        |       |                                 |

| $V_{\text{IN},\text{TH+}}$                 | Input positive going threshold                                                    | _    | 1.9            | _          |       |                                 |

| $V_{IN},_{TH}$                             | Input negative going threshold                                                    | _    | 1              | _          |       |                                 |

| V <sub>OH</sub>                            | High level output voltage                                                         | _    | 0.8            | 1.4        |       | 1 20 m A                        |

| $V_{OL}$                                   | Low level output voltage                                                          | _    | 0.2            | 0.6        | V     | $I_O = 20 \text{ mA}$           |

| V <sub>CCUV+</sub><br>V <sub>BSUV+</sub>   | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply under-voltage positive going threshold | 8.0  | 8.9            | 9.8        |       |                                 |

| V <sub>CCUV</sub> -<br>V <sub>BSUV</sub> - | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply under-voltage negative going threshold | 6.9  | 7.7            | 8.5        |       |                                 |

| V <sub>CCUVH</sub><br>V <sub>BSUVH</sub>   | $V_{\text{CC}}$ and $V_{\text{BS}}$ supply under-voltage hysteresis               | 0.35 | 1.2            | _          |       |                                 |

| $I_{LK}$                                   | Offset supply leakage current                                                     | _    | 1              | 50         | ^     | $V_{B} = V_{S} = 600 \text{ V}$ |

| $I_{QBS}$                                  | Quiescent V <sub>BS</sub> supply current                                          | _    | 45             | 70         | μΑ    | V <sub>IN</sub> = 0 V or 5 V    |

| I <sub>QCC</sub>                           | Quiescent V <sub>CC</sub> supply current                                          | _    | 1.1            | 1.8        | mA    | V <sub>IN</sub> = 0 V OI 5 V    |

| I <sub>IN+</sub>                           | Logic "1" input bias current                                                      | _    | 5              | 20         |       | $V_{IN} = 5 V$                  |

| I <sub>IN-</sub>                           | Logic "0" input bias current — 2                                                  |      | $V_{IN} = 0 V$ |            |       |                                 |

| l <sub>o+</sub>                            | Output high short circuit pulsed current                                          |      | 200            |            | mA    | V <sub>O</sub> = 0 V or 15 V    |

| I <sub>o-</sub>                            | Output low short circuit pulsed current 250 350 —                                 |      | IIIA           | PW ≤ 10 μs |       |                                 |

| R <sub>BS</sub>                            | Bootstrap resistance ††                                                           |      | 200            | _          | Ω     |                                 |

<sup>&</sup>lt;sup>††</sup> Integrated bootstrap diode is suitable for Complimentary PWM schemes only. IRS26072D is suitable for sinusoidal motor control applications. IRS26072D is NOT recommended for Trapezoidal motor control applications. Refer to the Integrated Bootstrap Functionality section of this datasheet for more details.

## **Dynamic Electrical Characteristics**

$V_{CC} = V_B = 15 \text{ V}$ ,  $V_S = COM$ ,  $T_A = 25 \,^{\circ}C$  and  $C_L = 1000 \, pF$  unless otherwise specified.

| Symbol           | Definition                                | Min. | Тур. | Max. | Units | Test Conditions        |

|------------------|-------------------------------------------|------|------|------|-------|------------------------|

| t <sub>on</sub>  | Turn-on propagation delay                 | 100  | 200  | 300  |       |                        |

| t <sub>off</sub> | Turn-off propagation delay                | 100  | 200  | 300  |       |                        |

| t <sub>r</sub>   | Turn-on rise time                         | _    | 150  | 220  | ns    | $V_{IN} = 0V$ and $5V$ |

| t <sub>f</sub>   | Turn-off fall time                        | _    | 50   | 80   | 113   |                        |

| MT               | ton, toff propagation delay matching time | _    | _    | 50   |       |                        |

| PM               | PW pulse width distortion <sup>†</sup>    | _    | 1    | 75   |       | PW input =10μs         |

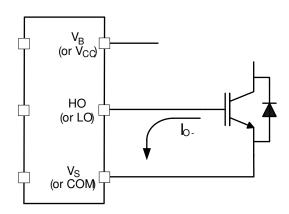

† PM is defined as PW<sub>IN</sub> - PW<sub>OUT</sub>.

# **Functional Block Diagram**

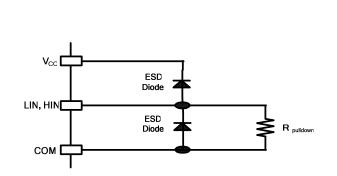

# Input/Output Pin Equivalent Circuit Diagrams

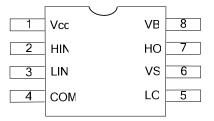

## **Lead Definitions**

| Symbol | Description                                                                    |

|--------|--------------------------------------------------------------------------------|

| VCC    | Low side and logic power supply                                                |

| VB     | High side floating power supply                                                |

| VS     | High side floating supply return                                               |

| HIN    | Logic input for high side gate driver output HO, input is in-phase with output |

| LIN    | Logic input for low side gate driver output LO, input is in-phase with output  |

| НО     | High side gate driver output                                                   |

| LO     | Low side gate driver output                                                    |

| COM    | Low side supply return                                                         |

# **Lead Assignments**

## **Application Information and Additional Details**

- IGBT/MOSFET Gate Drive

- Switching and Timing Relationships

- Matched Propagation Delays

- Input Logic Compatibility

- Under-Voltage Lockout Protection

- Truth Table: Under-Voltage lockout

- Integrated Bootstrap Functionality

- Bootstrap Power Supply Design

- Tolerant to Negative V<sub>S</sub> Transients

- PCB Layout Tips

- Additional Documentation

#### **IGBT/MOSFET Gate Drive**

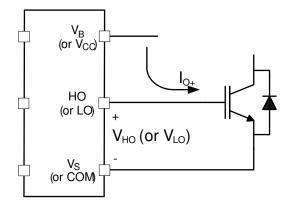

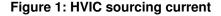

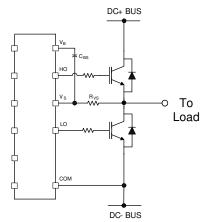

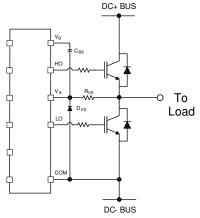

The IRS26072D HVIC is designed to drive high side and low side MOSFET or IGBT power devices. Figures 1 and 2 show the definition of some of the relevant parameters associated with the gate driver output functionality. The output current that drives the gate of the external power switches is defined as  $I_{\rm O}$ . The output voltage that drives the gate of the external power switches is defined as  $V_{\rm HO}$  for the high side and  $V_{\rm LO}$  for the low side; this parameter is sometimes generically called  $V_{\rm OUT}$  and in this case the high side and low side output voltages are not differentiated.

Figure 2: HVIC sinking current

#### **Switching and Timing Relationships**

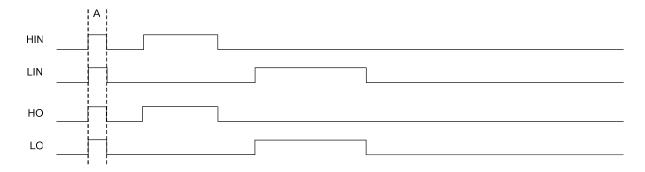

The relationship between the input and output signals of the IRS26072D HVIC is shown in Figure 3. The definitions of some of the relevant parameters associated with the gate driver input to output transmission are given.

Figure 3: Switching time waveforms

During interval A of Figure 4 the HVIC receives the command to turn on both the high and low side switches at the same time; correspondingly, the high and low side signals HO and LO turn on simultaneously.

Figure 4: Input/output timing diagram

#### **Matched Propagation Delays**

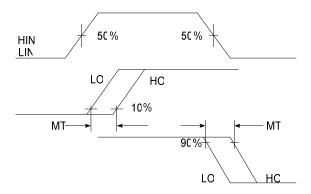

The IRS26072D HVIC is designed for propagation delay matching. With this feature, the input to output propagation delays  $t_{ON}$ ,  $t_{OFF}$  are the same for the low side and the high side channels; the maximum difference being specified by the delay matching parameter MT as defined in Figure 6.

Figure 6: Delay Matching Waveform Definition

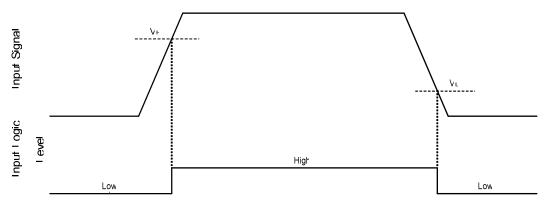

#### Input Logic Compatibility

The IRS26072D HVIC is designed with inputs compatible with standard CMOS and TTL outputs with 3.3 V and 5 V logic level signals. Figure 7 shows how an input signal is logically interpreted.

Figure 7: HIN & LIN input thresholds

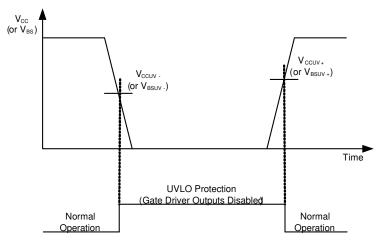

#### **Under-Voltage Lockout Protection**

The IRS26072D HVIC provides under-voltage lockout protection on both the  $V_{CC}$  low side and logic fixed power supply and the VBS high side floating power supply. Figure 8 illustrates this concept by considering the  $V_{CC}$  (or  $V_{BS}$ ) plotted over time: as the waveform crosses the UVLO threshold, the under-voltage protection is entered or exited.

Upon power up, should the  $V_{CC}$  voltage fail to reach the  $V_{CCUV_+}$  threshold, the gate driver outputs LO and HO will remain disabled. Additionally, if the  $V_{CC}$  voltage decreases below the  $V_{CCUV_-}$  threshold during normal operation, the under-voltage lockout circuitry will shutdown the gate driver outputs LO and HO.

Upon power up, should the  $V_{BS}$  voltage fail to reach the  $V_{BSUV}$  threshold, the gate driver output HO will remain disabled. Additionally, if the  $V_{BS}$  voltage decreases below the  $V_{BSUV}$  threshold during normal operation, the undervoltage lockout circuitry will shutdown the high side gate driver output HO.

The UVLO protection ensures that the HVIC drives external power devices only with a gate supply voltage sufficient to fully enhance them. Without this protection, the gates of the external power switches could be driven with a low voltage, which would result in power switches conducting current while with a high channel impedance, which would produce very high conduction losses possibly leading to power device failure.

Figure 8: UVLO protection

#### **Truth Table: Under-Voltage lockout**

Table 2 provides the truth table for the IRS26072D HVIC.

The 1<sup>st</sup> line shows that for  $V_{CC}$  below the UVLO threshold both the gate driver outputs LO and HO are disabled. After  $V_{CC}$  returns above  $V_{CCUV}$ , the gate driver outputs return functional.

The  $2^{nd}$  line shows that for  $V_{BS}$  below the UVLO threshold, the gate driver output HO is disabled. After  $V_{BS}$  returns above  $V_{BSIIV}$ , HO remains low until a new rising transition of HIN is received.

The last line shows the normal operation of the HVIC.

|                      | vcc vbs             |                     | outputs |     |

|----------------------|---------------------|---------------------|---------|-----|

|                      | VCC                 | V B3                | LO      | НО  |

| UVLO V <sub>cc</sub> | <v<sub>CCUV</v<sub> |                     | 0       | 0   |

| UVLO V <sub>BS</sub> | 15 V                | <v<sub>BSUV</v<sub> | LIN     | 0   |

| Normal operation     | 15 V                | 15 V                | LIN     | HIN |

Table 2: UVLO truth table

#### **Integrated Bootstrap Functionality**

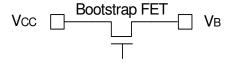

The IRS26072D HVIC embeds an integrated bootstrap FET that eliminates the need of external bootstrap diodes and resistors allowing an alternative drive of the bootstrap supply for a wide range of applications. A bootstrap FET is connected between the high side floating power supply VB and the low side and logic fixed power supply VCC (see Fig. 9).

Figure 9: Simplified Bootstrap FET connection

The bootstrap FET is suitable for complimentary PWM switching schemes only. Complimentary PWM refers to PWM schemes where the HIN & LIN input signals are alternately switched on and off. IRS26072D is suitable for sinusoidal motor control and the integrated bootstrap feature can be used either in parallel with the external bootstrap network (diode and resistor) or as a replacement of it. The use of the integrated bootstrap as a replacement of the external bootstrap network may have some limitations at very high PWM duty cycle, corresponding to very short LIN pulses, due to the bootstrap FET equivalent resistance R<sub>BS</sub>. IRS26072D is NOT recommended for trapezoidal motor control, even if an external bootstrap network is employed in parallel.

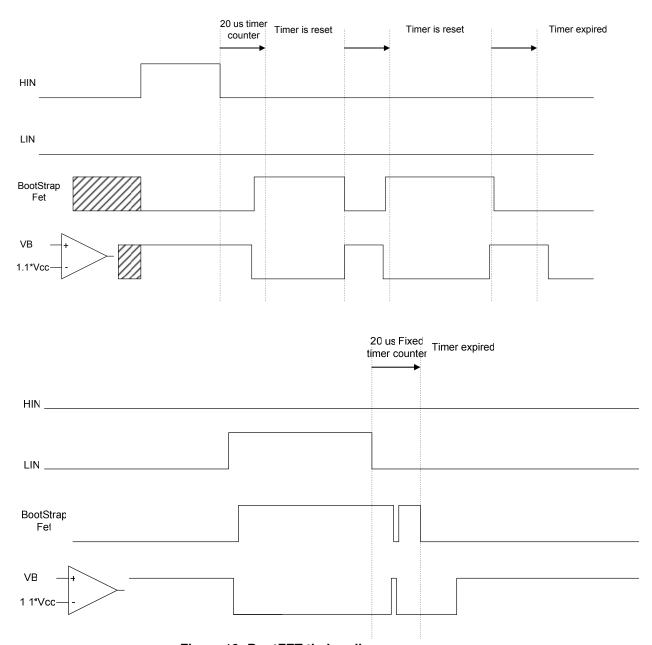

The bootstrap FET is conditioned as follows:

- bootstrap turns-off (immediately) or stays off when either:

- HO goes/stays high;

- V<sub>B</sub> goes/ stays high (> 1.1\*V<sub>CC</sub>);

- bootstrap turns-on when:

- LO is high (low side is on) AND V<sub>B</sub> is low (<1.1\*V<sub>CC</sub>);

- LO and HO are low after a transition of LIN from high to low AND V<sub>B</sub> goes low (<1.1\*V<sub>CC</sub>) before a fixed time of 20us;

- LO and HO are low after a transition of HIN from high to low AND V<sub>B</sub> goes low (<1.1\*V<sub>CC</sub>) before

a re-triggerable time of 20us. In this case the time counter is kept in reset state until VB goes

high (>1.1V<sub>CC</sub>).

In Figure 10 the BootFET timing diagram details are represented.

Figure 10: BootFET timing diagram

#### **Bootstrap Power Supply Design**

For information related to the design of the bootstrap power supply while using the integrated bootstrap functionality of the IRS26072D, please refer to Application Note 1123 (AN-1123) entitled "Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality." This application note is available at <a href="https://www.irf.com">www.irf.com</a>.

For information related to the design of a standard bootstrap power supply (i.e., using an external discrete diode) please refer to Design Tip 04-4 (DT04-4) entitled "Using Monolithic High Voltage Gate Drivers." This design tip is available at <a href="www.irf.com">www.irf.com</a>.

#### **Tolerant to Negative VS Transients**

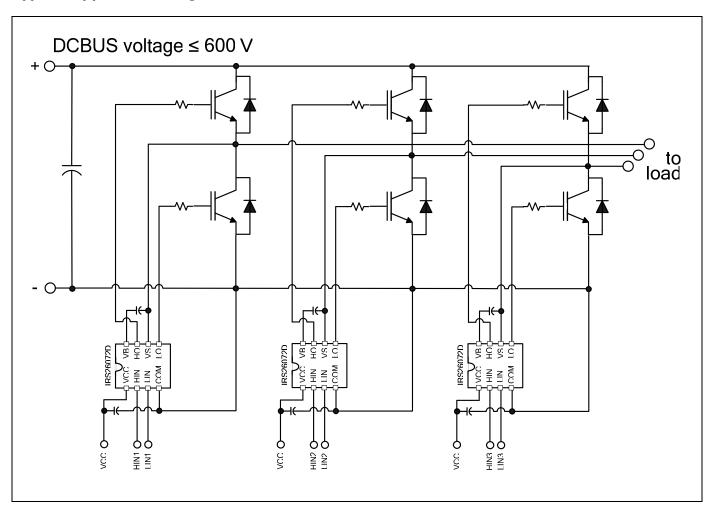

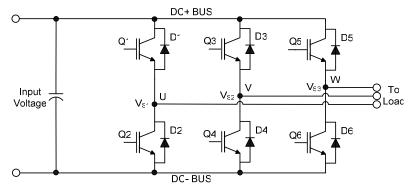

A common problem in today's high-power switching converters is the transient response of the switch node's voltage as the power devices switch on and off quickly while carrying a large current. A typical 3-phase inverter circuit is shown in Figure 11; where we define the power switches and diodes of the inverter.

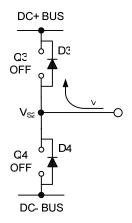

If the high-side switch (e.g., the IGBT Q1 in Figures 12 and 13) switches off, while the U phase current is flowing to an inductive load, a current commutation occurs from high-side switch (Q1) to the diode (D2) in parallel with the low-side switch of the same inverter leg. At the same instance, the voltage node  $V_{S1}$ , swings from the positive DC bus voltage to the negative DC bus voltage.

Figure 11: Three phase inverter

Figure 12: Q1 conducting

Figure 13: D2 conducting

Also when the V phase current flows from the inductive load back to the inverter (see Figures 14 and 15), and Q4 IGBT switches on, the current commutation occurs from D3 to Q4. At the same instance, the voltage node,  $V_{S2}$ , swings from the positive DC bus voltage to the negative DC bus voltage.

Figure 14: D3 conducting

Figure 15: Q4 conducting

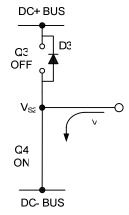

However, in a real inverter circuit, the  $V_S$  voltage swing does not stop at the level of the negative DC bus, rather it swings below the level of the negative DC bus. This undershoot voltage is called "negative  $V_S$  transient".

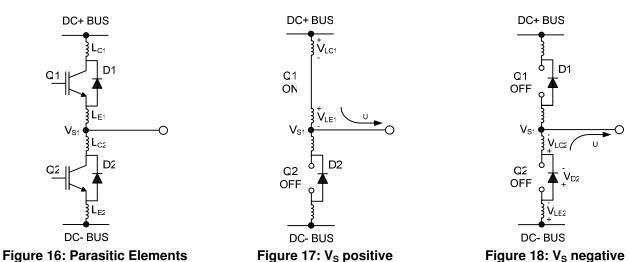

The circuit shown in Figure 16 depicts one leg of the three phase inverter; Figures 17 and 18 show a simplified illustration of the commutation of the current between Q1 and D2. The parasitic inductances in the power circuit from the die bonding to the PCB tracks are lumped together in  $L_C$  and  $L_E$  for each IGBT. When the high-side switch is on,  $V_{S1}$  is below the DC+ voltage by the voltage drops associated with the power switch and the parasitic elements of the circuit. When the high-side power switch turns off, the load current momentarily flows in the low-side freewheeling diode due to the inductive load connected to  $V_{S1}$  (the load is not shown in these figures). This current flows from the DC- bus (which is connected to the COM pin of the HVIC) to the load and a negative voltage between  $V_{S1}$  and the DC- Bus is induced (i.e., the COM pin of the HVIC is at a higher potential than the  $V_S$  pin).

In a typical motor drive system, dV/dt is typically designed to be in the range of 3-5 V/ns. The negative  $V_S$  transient voltage can exceed this range during some events such as short circuit and over-current shutdown, when di/dt is greater than in normal operation.

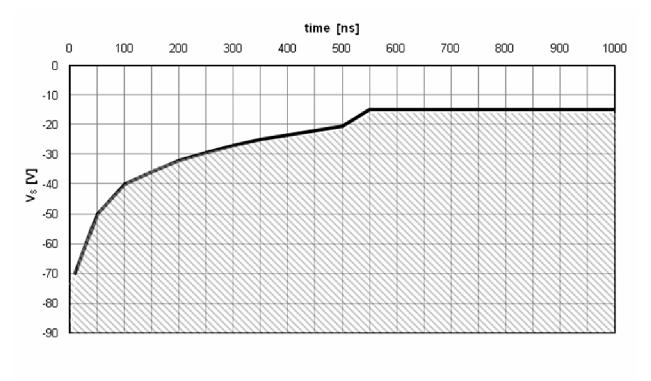

International Rectifier's HVICs have been designed for the robustness required in many of today's demanding applications. An indication of the IRS26072D's robustness can be seen in Figure 19, where there is represented the IRS26072D Safe Operating Area at  $V_{BS}$ =15V based on repetitive negative  $V_S$  spikes. A negative  $V_S$  transient voltage falling in the grey area (outside SOA) may lead to IC permanent damage; vice versa unwanted functional anomalies or permanent damage to the IC do not appear if negative Vs transients fall inside SOA.

At  $V_{BS}$ =15V in case of -V<sub>S</sub> transients greater than -16.5 V for a period of time greater than 50 ns; the HVIC will hold by design the high-side outputs in the off state for 4.5  $\mu$ s.

Figure 19: Negative V<sub>S</sub> transient SOA @ VBS=15V

Even though the IRS26072D has been shown able to handle these large negative VS transient conditions, it is highly recommended that the circuit designer always limit the negative  $V_{\rm S}$  transients as much as possible by careful PCB layout and component use.

#### **PCB Layout Tips**

<u>Distance between high and low voltage components:</u> It's strongly recommended to place the components tied to the floating voltage pins ( $V_B$  and  $V_S$ ) near the respective high voltage portions of the device. Please see the Case Outline information in this datasheet for the details.

<u>Ground Plane:</u> In order to minimize noise coupling, the ground plane should not be placed under or near the high voltage floating side.

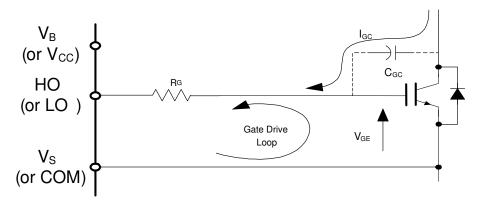

Gate Drive Loops: Current loops behave like antennas and are able to receive and transmit EM noise (see Figure 20). In order to reduce the EM coupling and improve the power switch turn on/off performance, the gate drive loops must be reduced as much as possible. Moreover, current can be injected inside the gate drive loop via the IGBT collector-to-gate parasitic capacitance. The parasitic auto-inductance of the gate loop contributes to developing a voltage across the gate-emitter, thus increasing the possibility of a self turn-on effect.

Figure 20: Antenna Loops

<u>Supply Capacitor:</u> It is recommended to place a bypass capacitor between the VCC and COM pins. This connection is shown in Figure 21. A ceramic 1  $\mu$ F ceramic capacitor is suitable for most applications. This component should be placed as close as possible to the pins in order to reduce parasitic elements.

Figure 21: Supply capacitor

Routing and Placement: Power stage PCB parasitic elements can contribute to large negative voltage transients at the switch node; it is recommended to limit the phase voltage negative transients. In order to avoid such conditions, it is recommended to 1) minimize the high-side source to low-side collector distance, and 2) minimize the low-side emitter to negative bus rail stray inductance. However, where negative  $V_S$  spikes remain excessive, further steps may be taken to reduce the spike. This includes placing a resistor (5  $\Omega$  or less) between the  $V_S$  pin and the switch node (see Figure 22), and in some cases using a clamping diode between COM and  $V_S$  (see Figure 23). See DT04-4 at www.irf.com for more detailed information.

Figure 22: V<sub>S</sub> resistor

Figure 23: V<sub>S</sub> clamping diode

#### **Additional Documentation**

Several technical documents related to the use of HVICs are available at <a href="www.irf.com">www.irf.com</a>; use the Site Search function and the document number to quickly locate them. Below is a short list of some of these documents.

DT97-3: Managing Transients in Control IC Driven Power Stages

AN-1123: Bootstrap Network Analysis: Focusing on the Integrated Bootstrap Functionality

DT04-4: Using Monolithic High Voltage Gate Drivers

AN-978: HV Floating MOS-Gate Driver ICs

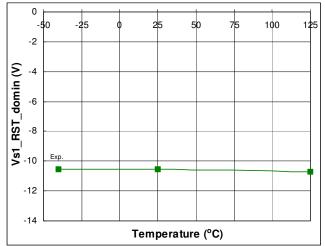

## **Parameter Temperature Trends**

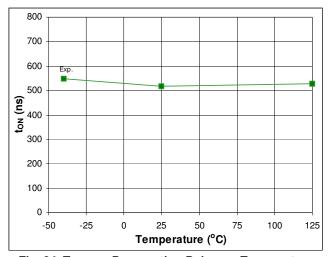

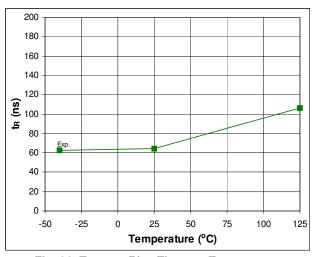

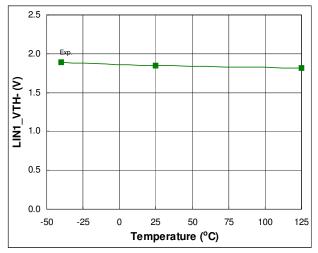

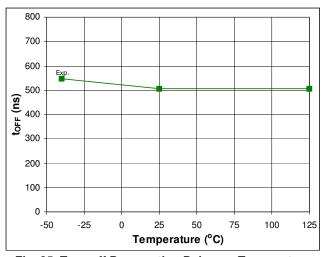

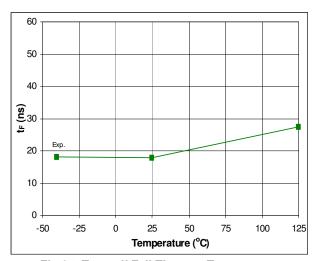

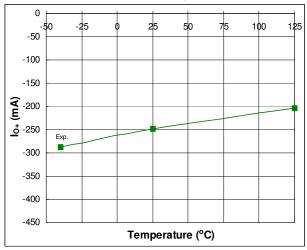

Figures 24-41 provide information on the experimental performance of the IRS26072D HVIC. The line plotted in each figure is generated from actual experimental data. A small number of individual samples were tested at three temperatures (-40 °C, 25 °C, and 125 °C) in order to generate the experimental curve. The line labeled Exp. consist of three data points (one data point at each of the tested temperatures) that have been connected together to illustrate the understood temperature trend. The individual data points on the curve were determined by calculating the averaged experimental value of the parameter (for a given temperature).

Fig. 24. Turn-on Propagation Delay vs. Temperature

Fig. 26. Turn-on Rise Time vs. Temperature

Fig. 28. Input Negative Going Threshold vs. Temperature

Fig. 25. Turn-off Propagation Delay vs. Temperature

Fig.27. Turn-off Fall Time vs. Temperature

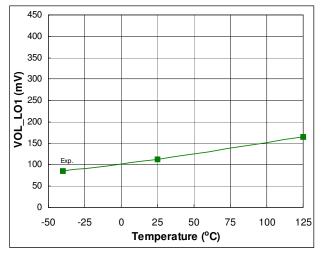

Fig. 29. Low Level Output Voltage vs. Temperature

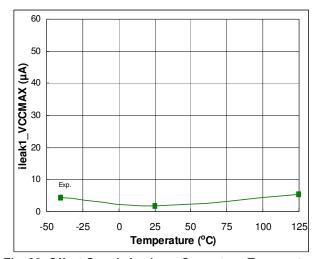

Fig. 30. Offset Supply Leakage Current vs. Temperature

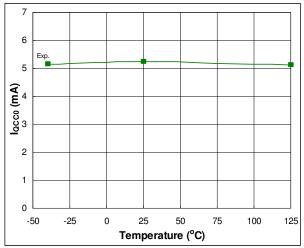

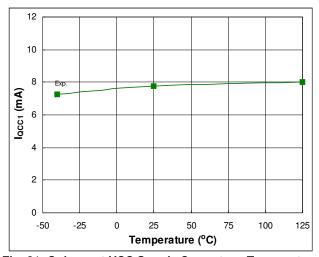

Fig. 32. Quiescent VCC Supply Current vs. Temperature

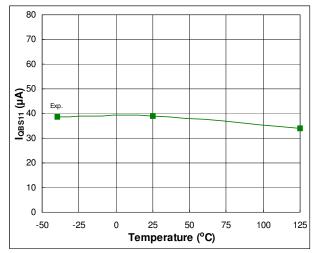

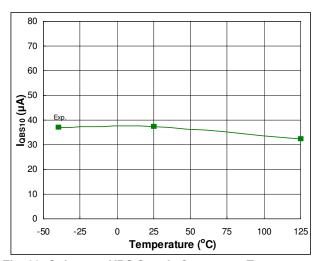

Fig. 34. Quiescent VBS Supply Current vs. Temperature

Fig. 31. Quiescent VCC Supply Current vs. Temperature

Fig. 33. Quiescent VBS Supply Current vs. Temperature

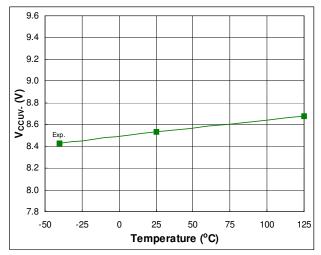

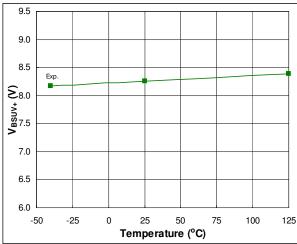

Fig. 35. VCC Supply Under-voltage Negative Going Threshold vs. Temperature

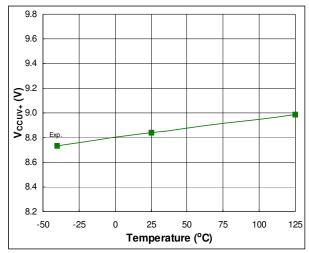

Fig. 36. VCC Supply Under-voltage Positive Going Threshold vs. Temperature

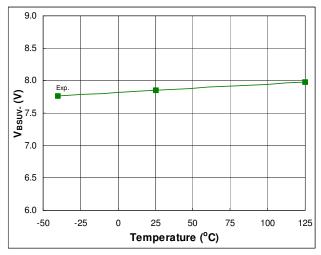

Fig. 38. VBS Supply Under-voltage Positive Going Threshold vs. Temperature

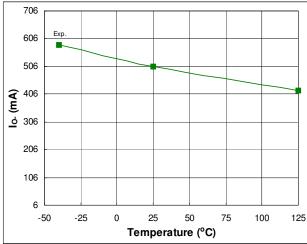

Fig. 40. Output Low Short Circuit Pulsed Current vs. Temperature

Fig. 37. VBS Supply Under-voltage Negative Going Threshold vs. Temperature

Fig. 39. Output High Short Circuit Pulsed Current vs. Temperature

Fig. 41. Max -Vs vs. Temperature

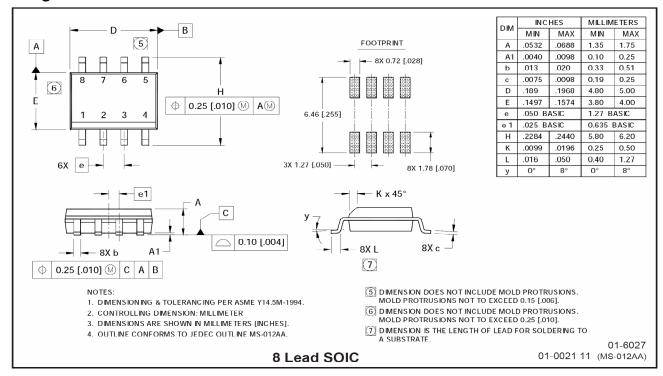

## **Package Details**

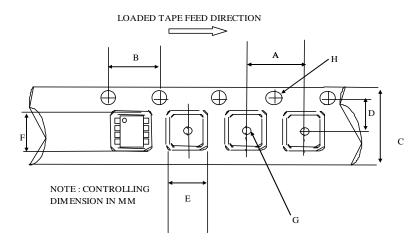

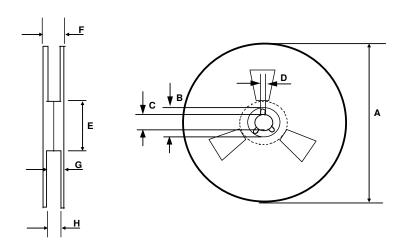

## **Tape and Reel Details**

CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | lmp   | erial |  |

|------|--------|-------|-------|-------|--|

| Code | Min    | Max   | Min   | Max   |  |

| Α    | 7.90   | 8.10  | 0.311 | 0.318 |  |

| В    | 3.90   | 4.10  | 0.153 | 0.161 |  |

| С    | 11.70  | 12.30 | 0.46  | 0.484 |  |

| D    | 5.45   | 5.55  | 0.214 | 0.218 |  |

| E    | 6.30   | 6.50  | 0.248 | 0.255 |  |

| F    | 5.10   | 5.30  | 0.200 | 0.208 |  |

| G    | 1.50   | n/a   | 0.059 | n/a   |  |

| Н    | 1.50   | 1.60  | 0.059 | 0.062 |  |

REEL DIMENSIONS FOR 8SOICN

|      | Metric |        | Imp    | erial  |

|------|--------|--------|--------|--------|

| Code | Min    | Max    | Min    | Max    |

| Α    | 329.60 | 330.25 | 12.976 | 13.001 |

| В    | 20.95  | 21.45  | 0.824  | 0.844  |

| С    | 12.80  | 13.20  | 0.503  | 0.519  |

| D    | 1.95   | 2.45   | 0.767  | 0.096  |

| E    | 98.00  | 102.00 | 3.858  | 4.015  |

| F    | n/a    | 18.40  | n/a    | 0.724  |

| G    | 14.50  | 17.10  | 0.570  | 0.673  |

| Н    | 12.40  | 14.40  | 0.488  | 0.566  |

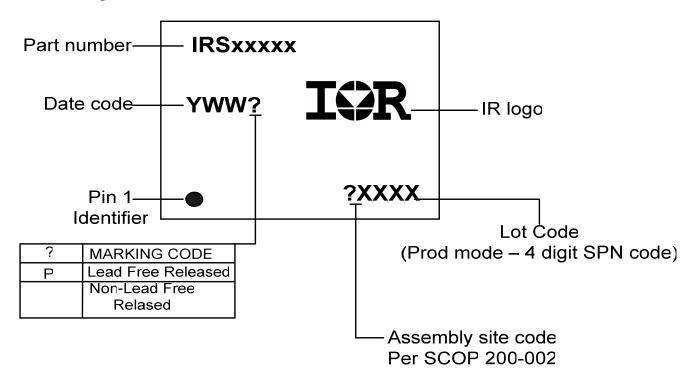

# **Part Marking Information**

## **Ordering Information**

|                  |              | Standard F    | Pack     | G. L. P. (V. I       |

|------------------|--------------|---------------|----------|----------------------|

| Base Part Number | Package Type | Form          | Quantity | Complete Part Number |

| VD G0 (0.50D     | SOIC 8       | Tube/Bulk     | XXX      | IRS26072D SPBF       |

| IRS26072D        | 3010 8       | Tape and Reel | XXX      | IRS26072D STRPBF     |

The information provided in this document is believed to be accurate and reliable. However, International Rectifier assumes no responsibility for the consequences of the use of this information. International Rectifier assumes no responsibility for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of International Rectifier. The specifications mentioned in this document are subject to change without notice. This document supersedes and replaces all information previously supplied.

For technical support, please contact IR's Technical Assistance Center <a href="http://www.irf.com/technical-info/">http://www.irf.com/technical-info/</a>

#### WORLD HEADQUARTERS:

233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105