Rev B1, Page 1/22

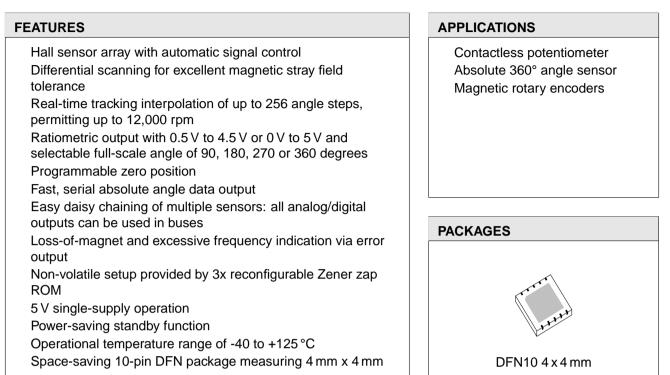

### DESCRIPTION

iC-MP consists of a quadruple Hall sensor array which has been optimized for the magnetic measurement of an axis angle. The array permits errortolerant adjustment of the magnet, reducing the time and effort required assembly. The integrated signal conditioning unit provides a differential sine/cosine signal at its outputs. The sensor generates one sine cycle per full rotation of the magnet, enabling the angle to be clearly determined. At the same time the internal amplitude control unit produces a regulated output amplitude of 2 Vpp, regardless of variations in the magnetic field strength, supply voltage and temperature. Furthermore, error signals are provided which report any magnet loss and an excessively high RPM speed.

With the aid of the integrated 8-bit sine-to-digital converter the axis angle is determined from the

sine/cosine signals. The absolute position angle is output via the serial interface together with a bit indicating an error. The maximum resolution of 8 bits is maintained up to revolutions of 12,000 rpm.

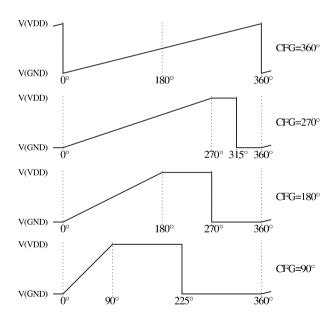

The absolute angle is converted back to a linear analog output voltage using the internal D/A converter. The analog output voltage range can be programmed to be either rail to rail or 10% to 90% of the supply voltage. The angular range of the analog signal is configurable to 90°, 180°, 270° or 360°.

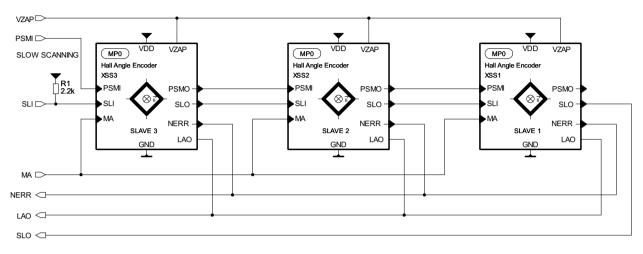

iC-MP can be easily cascaded, enabling scanning of multiple axes. In Fast Scanning Mode all devices connected in a queue are read consecutively. In Slow Scanning Mode (Power Save Mode) each individual device is booted up before the serial data or analog output voltage is put on the common bus.

Rev B1, Page 3/22

### CONTENTS

| PACKAGES                                            | 4  | OPERATING MODES                          | 11              |

|-----------------------------------------------------|----|------------------------------------------|-----------------|

| ABSOLUTE MAXIMUM RATINGS                            | 5  | PROGRAMMING MODE                         | <b>12</b><br>14 |

| THERMAL DATA                                        | 5  | Calculating the position offset          | 14<br>15        |

| ELECTRICAL CHARACTERISTICS                          | 6  | FAST SCANNING MODE                       | 16              |

| SENSOR PRINCIPLE                                    | 8  | SLOW SCANNING MODE                       | 18              |

| HALL SENSOR POSITION AND INTERNAL<br>ANALOG SIGNALS | 8  | APPLICATION CIRCUITS Stand-alone example | <b>20</b><br>20 |

| LINEAR ANALOG OUTPUT (LAO)                          | 9  | TEST MODES                               | 21              |

| SERIAL OUTPUT (SLO)                                 | 10 | DESIGN REVIEW: Notes On Chip Functions   | 21              |

Rev B1, Page 4/22

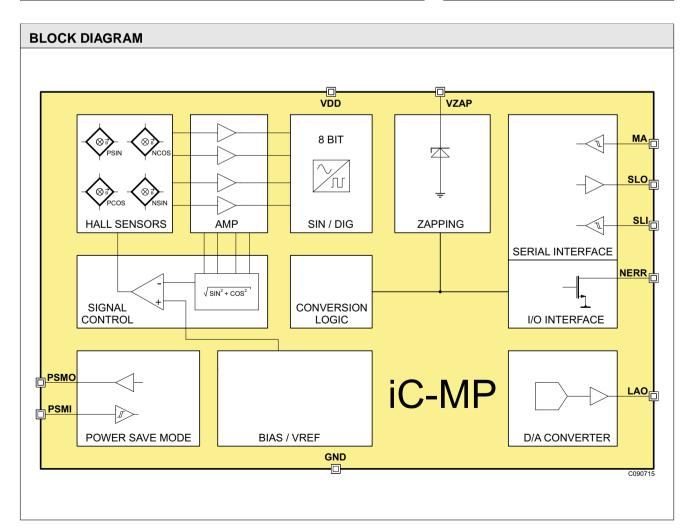

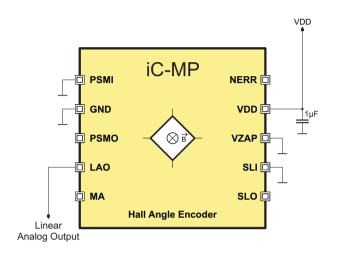

### PACKAGES

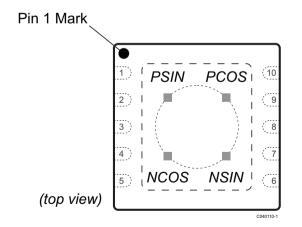

### **PIN CONFIGURATION DFN10**

#### PIN FUNCTIONS No. Name Function

- 1 PSMI Power Save Mode Input

- 2 GND Ground

- 3 PSMO Power Save Mode Output

- 4 LAO Linear Analog Output

- 5 MA Serial Clock Input

- 6 SLO Serial Data Output

- 7 SLI Serial Data Input

- 8 VZAP Zapping Voltage Input

- 9 VDD +5 V Supply Voltage

- 10 NERR Error Message Output (low active) / Serial ROM Data Output

- TP Thermal Pad

The *thermal pad* must be connected to ground potential on the PCB. Orientation of the logo (**@** MP CODE ...) is subject to alteration.

Rev B1, Page 5/22

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these ratings device damage may occur.

| ltem | Symbol | Parameter                                                    | Conditions                                    |      |              | Unit |

|------|--------|--------------------------------------------------------------|-----------------------------------------------|------|--------------|------|

| No.  |        |                                                              |                                               | Min. | Max.         |      |

| G001 | V()    | Supply Voltage at VDD                                        |                                               | -0.3 | 6            | V    |

| G002 | I()    | Current in VDD                                               |                                               | -20  | 20           | mA   |

| G003 | V()    | Voltage at pins PSMI, PSMO, LAO,<br>MA, SLO, SLI, NERR       |                                               | -0.3 | VDD +<br>0.3 | V    |

| G004 | V()    | Voltage at pin VZAP                                          |                                               | -0.3 | 8            | V    |

| G005 | I()    | Current in pins PSMI, PSMO, LAO,<br>MA, SLO, SLI, NERR, VZAP |                                               | -10  | 10           | mA   |

| G006 | I()    | Current in pins PSMI, PSMO, LAO,<br>MA, SLO, SLI, NERR, VZAP | Pulse width < 10µs                            | -100 | 100          | mA   |

| G007 | Vd()   | ESD Susceptibility at all pins                               | HBM, 100 pF discharged through $1.5  k\Omega$ |      | 2            | kV   |

| G008 | Tj     | Junction Temperature                                         |                                               | -40  | 125          | °C   |

| G009 | Ts     | Storage Temperature Range                                    |                                               | -40  | 125          | °C   |

### THERMAL DATA

Operating conditions: VDD =  $5 V \pm 10 \%$

| Item | Symbol | Parameter                           | Conditions                                                                    |      |      |      | Unit |

|------|--------|-------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| No.  | -      |                                     |                                                                               | Min. | Тур. | Max. |      |

| T01  | Та     | Operation Ambient Temperature Range |                                                                               | -40  |      | 125  | °C   |

| T02  | Rthja  |                                     | Package mounted on PCB, thermal pad at approx. 2 cm <sup>2</sup> cooling area |      | 40   |      | K/W  |

Rev B1, Page 6/22

### **ELECTRICAL CHARACTERISTICS**

| tem<br>No. | Symbol       | Parameter                                                                                   | Conditions                                                                                                              | Min. | Тур.               | Max.      | Unit                     |

|------------|--------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----------|--------------------------|

| Gener      | ral          |                                                                                             |                                                                                                                         |      | , <b>,</b> ,       |           |                          |

| 001        | VDD          | Supply Voltage                                                                              |                                                                                                                         | 4.5  | 5                  | 5.5       | V                        |

| 002        | I(VDD)       | Supply Current in VDD                                                                       | PSMI = lo, other pins open                                                                                              |      | 8                  | 12        | mA                       |

| 003        | I(VDD)sb     | Standby Supply Current                                                                      | PSMI = hi                                                                                                               |      |                    | 200       | μA                       |

| 004        | VDDon        | Power-On Threshold                                                                          | Increasing voltage VDD                                                                                                  | 3.0  |                    | 4.1       | V                        |

| 005        | VDDoff       | Power-Down Threshold                                                                        | Decreasing voltage VDD                                                                                                  | 2.6  |                    | 3.9       | V                        |

| 006        | VDDhys       | Hysteresis                                                                                  | VDDhys = VDDon - VDDoff                                                                                                 | 200  |                    |           | mV                       |

| 007        | ton()1       | Turn-On Delay Following<br>Power-On                                                         | Time to data valid after enabling, VDD: VDDoff $\rightarrow$ VDDon                                                      |      |                    | 1         | ms                       |

| 008        | ton()2       | Turn-On Delay Following Standby Time to data valid after standby, PSMI: hi $\rightarrow$ lo |                                                                                                                         |      |                    | 900       | μs                       |

| 009        | Vc()hi       | Clamp Voltage hi at<br>PSMI, MA, SLI, NERR                                                  | VDD = 0 V; I() = 1 mA                                                                                                   | 0.3  |                    | 1.6       | V                        |

| 010        | Vc()hi       | Clamp Voltage hi at<br>PSMO, LAO, SLO                                                       | VDD = 0 V; I() = 4 mA                                                                                                   | 0.3  |                    | 1.6       | V                        |

| 011        | Vc()lo       | Clamp Voltage lo at<br>PSMI, PSMO, LAO, MA, SLO,<br>SLI, NERR, VDD, VZAP                    | I() = -4 mA                                                                                                             | -1.5 |                    | -0.3      | V                        |

| Hall S     | ensor Array  | ý                                                                                           |                                                                                                                         |      |                    |           |                          |

| 101        | Hext         | Operating Magnetic Field<br>Strength                                                        | At surface of chip                                                                                                      | 20   | 50                 | 100       | kA/m                     |

| 102        | RPM          | Permissible RPM Speed                                                                       |                                                                                                                         |      |                    | 12000     | rpm                      |

| 103        | ferr()       | Excessive Frequency Alarm                                                                   | ENERR(1) = 1; NERR: hi $\rightarrow$ lo                                                                                 |      | 1                  |           | kHz                      |

| 104        | fmag()       | Magnetic Field Frequency                                                                    |                                                                                                                         |      |                    | 200       | Hz                       |

| 105        | dsens        | Diameter of Hall Sensor Array                                                               |                                                                                                                         |      | 2                  |           | mm                       |

| 106        | xpac         | Chip Placement Tolerance                                                                    | Versus DFN10 package outlines                                                                                           | -0.2 |                    | 0.2       | mm                       |

| 107        | $\phi$ pac   | Chip Tilt Angle                                                                             | Versus DFN10 package outlines                                                                                           | -3   |                    | 3         | DEG                      |

| 108        | hpac         | Distance Surface of Package to<br>Surface of Chip                                           | DFN10 package                                                                                                           |      | 400                |           | μm                       |

| Sine-      | Fo-Digital C | onverter                                                                                    |                                                                                                                         |      |                    |           |                          |

| 301        | RES          | Converter Resolution                                                                        | Per 360 degree                                                                                                          |      | 8                  |           | bit                      |

| 302        | HYS          | Converter Hysteresis                                                                        |                                                                                                                         |      | 1.4                |           | DEG                      |

| 303        | AAabs        | Absolute Angle Accuracy                                                                     | Magnet with 4 mm in diameter, axis centered to chip                                                                     | -3   |                    | 3         | DEG                      |

|            |              | nd Ratiometric Output LAO                                                                   |                                                                                                                         |      |                    |           |                          |

| 401        | RES()        | D/A Converter Resolution                                                                    | MODE(1:0) = 00 (range 360°)<br>MODE(1:0) = 01 (range 270°)<br>MODE(1:0) = 10 (range 180°)<br>MODE(1:0) = 11 (range 90°) |      | 8<br>7.5<br>7<br>6 |           | bit<br>bit<br>bit<br>bit |

| 402        | lload()      | Permissible Output Current                                                                  |                                                                                                                         | -1   |                    | 1         | mA                       |

| 403        | dV0()hi      |                                                                                             | dV0()hi = V(VDD) - V(LAO), MODE(3) = 0;<br>I() = -1 mA<br>I() = 0 mA                                                    |      |                    | 170<br>85 | mV<br>mV                 |

| 404        | dV0()lo      | Output Voltage Io, Rail-To-Rail                                                             | MODE(3) = 0;<br>I() = 1 mA<br>I() = 0 mA                                                                                |      |                    | 170<br>85 | mV<br>mV                 |

| 405        | dV1()hi      | Output Voltage hi, 10/90% Range                                                             |                                                                                                                         | 85   |                    | 95        | %VDD                     |

| 406        | dV1()lo      | Output Voltage Io, 10/90% Range                                                             |                                                                                                                         | 5    |                    | 15        | %VDD                     |

| 407        | llk()        | Leakage Current                                                                             | V(LAO) = 0VDD, PSMI = hi                                                                                                | -5   |                    | 5         | μA                       |

| 408        | SR()hi       | Slew Rate hi                                                                                | V(LAO): 20% $\rightarrow$ 80% of range                                                                                  | 2    |                    |           | V/µs                     |

| 409        | SR()lo       | Slew Rate lo                                                                                | $V(LAO): 80\% \rightarrow 20\%$ of range                                                                                | 2    |                    |           | V/µs                     |

|            | ng Input VZ  |                                                                                             |                                                                                                                         |      | 1                  | I         | ·· ••                    |

| 501        | Vt1()hi      | Voltage Threshold hi vs. GND                                                                |                                                                                                                         |      |                    | 2         | V                        |

| 502        | Vt1()Io      | Voltage Threshold lo vs. GND                                                                |                                                                                                                         | 0.8  |                    | -         | V                        |

Rev B1, Page 7/22

### ELECTRICAL CHARACTERISTICS

| ltem<br>No. | Symbol       | Parameter                               | Conditions                                                  | Min.  | Тур. | Max.      | Unit     |

|-------------|--------------|-----------------------------------------|-------------------------------------------------------------|-------|------|-----------|----------|

| 503         | Vt1()hys     | Threshold Hysteresis                    | Vt1()hys = Vt1()hi – Vt1()lo                                | 230   | 51   | 400       | mV       |

| 504         | Vt2()hi      | Voltage Threshold hi vs. VDD            | Vt2()hi = V() - VDD,<br>VDD = 5 V ±5%, Tj = 10 40 °C        |       |      | 1.3       | V        |

| 505         | Vt2()lo      | Voltage Threshold lo vs. VDD            | Vt2()Io = V() - VDD;<br>VDD = 5 V ±5%, Tj = 10 40 °C        | 0.7   |      |           | V        |

| 506         | Vt2()hys     | Threshold Hysteresis                    | Vt2()hys = Vt2()hi - Vt2()lo                                | 20    |      | 150       | mV       |

| 507         | Vzap()       | Permissible Zapping Voltage             | VDD = 5 V ±5%, Tj = 10 40 °C                                | 7.3   | 7.4  | 7.5       | V        |

| 508         | Izap()       | Required Zapping Current                | VDD = 5 V ±5%, Tj = 10 40 °C                                |       |      | 90        | mA       |

| Serial      | Interface ar | nd Power Save Mode Inputs: MA,          | SLI, PSMI                                                   |       |      |           |          |

| 601         | Vt()hi       | Input Threshold Voltage hi              |                                                             |       |      | 2         | V        |

| 602         | Vt()lo       | Input Threshold Voltage lo              |                                                             | 0.8   |      |           | V        |

| 603         | Vt()hys      | Input Hysteresis                        | Vt()hys = Vt()hi – Vt()lo                                   | 230   |      |           | mV       |

| 604         | lpu()        | Input Pull-up Current                   | V() = 0VDD - 1V                                             | -240  | -120 | -10       | μA       |

| 605         | fclk(MA)     | Permissible Clock Frequency at MA       | Normal mode                                                 | 0.080 |      | 10        | MHz      |

| 606         | tzap(MA)     | Permissible Zapping Cycle at MA         | Programming mode,<br>VDD = 5 V ±5%, Tj = 10 40 °C           | 4.5   | 5    | 5.5       | μs       |

| 607         | tout(MA)     | Interface Timeout                       | Time from MA last edge to SLO lo $\rightarrow$ hi           |       |      | 15        | μs       |

| Serial      | Interface ar | d Power Save Mode Outputs: SI           |                                                             |       |      |           | <u> </u> |

| 701         | Vs()hi       | Saturation Voltage hi                   | Vs()hi = VDD - V(), I() = -4 mA                             |       |      | 0.4       | V        |

| 702         | Vs()lo       | Saturation Voltage lo                   | I() = 4 mA                                                  |       |      | 0.4       | V        |

| 703         | Isc()hi      | Short-Circuit Current hi                | V() = 0 V                                                   | -90   |      | -10       | mA       |

| 704         | Isc()lo      | Short-Circuit Current lo                | V() = VDD                                                   | 10    |      | 90        | mA       |

| 705         | tr()         | Rise Time                               | $CL() = 50 \text{ pF}, V(): 20 \rightarrow 80\%$            |       |      | 60        | ns       |

|             | tf()         | Fall Time                               | $CL() = 50 \text{ pF}, V(): 80 \rightarrow 20\%$            |       |      | 60        | ns       |

|             | erface NER   |                                         | $ OL()  = SOP1, \forall (): SO \rightarrow ZO7S$            |       |      | 00        | 113      |

|             | Vs()lo       | Saturation Voltage lo                   | I() = 4 mA                                                  |       |      | 0.4       | V        |

|             | llk()        | Leakage Current                         | V() = 0VDD, PSMI = hi                                       | -5    |      | 5         | μA       |

| 803         | lik()        | Short-Circuit Current lo                | V() = VDD                                                   | 4.5   |      | 90        | mA       |

|             | 0            | ERR, LAO, PSMO (iC-Haus device          | 0                                                           | 4.5   |      | 90        |          |

|             |              | · · · ·                                 |                                                             | 45    | 50   | <b>FF</b> | %VDD     |

| 902         |              | Reference Voltage at LAO                | Op. mode: Test 2                                            | 45    | 50   | 55        | 7        |

| 904         | Vpp(PSIN)    | Pos. Sine Sensor AC Signal at NERR      | Op. mode: Test 0                                            |       | 2    |           | Vpp      |

| 905         | , ,          | Pos. Sine Sensor DC Signal<br>at NERR   | Op. mode: Test 0                                            |       | VREF |           | V        |

| 906         |              | Pos. Cosine Sensor AC Signal<br>at LAO  | Op. mode: Test 0                                            |       | 2    |           | Vpp      |

| 907         | Vdc(PCOS)    | Pos. Cosine Sensor DC Signal<br>at LAO  | Op. mode: Test 0                                            |       | VREF |           | V        |

| 908         | Vpp(NSIN)    | Neg. Sine Sensor AC Signal<br>at NERR   | Op. mode: Test 1                                            |       | 2    |           | Vpp      |

| 909         | Vdc(NSIN)    | Neg. Sine Sensor DC Signal<br>at NERR   | Op. mode: Test 1                                            |       | VREF |           | V        |

| 910         |              | Neg. Cosine Sensor AC Signal<br>at LAO  | Op. mode: Test 1                                            |       | 2    |           | Vpp      |

| 911         | , ,          | Neg. Cosine Sensor DC Signal<br>at LAO  | Op. mode: Test 1                                            |       | VREF |           | V        |

| 912         | dVoff()      | Diff. Sine and Cosine Signal<br>Offsets | dVoff() = V(PSIN) - V(NSIN),<br>dVoff() = V(PCOS) - V(NCOS) | -50   |      | 50        | mV       |

| 913         | VR()         | Sine/Cosine AC Signal Ratio             | VR() = V(PSIN) / V(PCOS),<br>VR() = V(NSIN) / V(NCOS)       | 0.95  |      | 1.05      |          |

Rev B1, Page 8/22

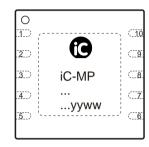

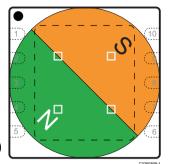

### SENSOR PRINCIPLE

Figure 1: Sensor principle

In conjunction with a rotating permanent magnet, the iC-MP module can be used to create a complete en-

coder system or a contactless potentiometer. A diametrically magnetized, cylindrical permanent magnet made of neodymium iron boron (NdFeB) or samarium cobalt (SmCo) generates optimum sensor signals. The diameter of the magnet should be in the range of 3 mm to 6 mm.

The iC-MP has four Hall sensors adapted for angle determination and to convert the magnetic field into a measurable Hall voltage. Only the z-component of the magnetic field is evaluated, whereby the field lines pass through two opposing Hall sensors in the opposite direction. Figure 1 shows an example of field vectors.

The arrangement of the Hall sensors is selected so that the mounting of the magnets relative to iC-MP is extremely tolerant. Two Hall sensors combined provide a differential Hall signal. When the magnet is rotated around the longitudinal axis, sine and cosine output voltages are produced which can be used to determine angles.

#### HALL SENSOR POSITION AND INTERNAL ANALOG SIGNALS

The Hall sensors are placed in the center of the DFN10 package at 90° to one another and arranged in a circle with a diameter of 2 mm as shown in Figure 2.

Figure 2: Position of the Hall sensors

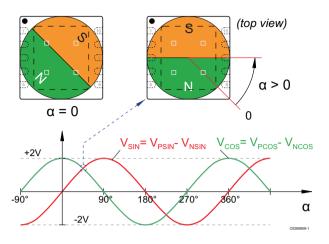

When a magnetic south pole comes close to the surface of the package the resulting magnetic field has a positive component in the +z direction (i.e. from the top of the package) and the individual Hall sensors each generate their own positive signal voltage. In order to calculate the angle position of a diametrically polarized magnet placed above the device a difference in signal is formed between opposite pairs of Hall sensors, resulting in the sine being  $V_{SIN} = V_{PSIN} - V_{NSIN}$  and the cosine  $V_{COS} = V_{PCOS} - V_{NCOS}$ . The zero angle position of the magnet is marked by the resulting cosine voltage value being at a maximum and the sine voltage value at zero.

This is the case when the south pole of the magnet is exactly above the PCOS sensor and the north pole is above sensor NCOS, as shown in Figure 3. Sensors PSIN and NSIN are placed along the pole boundary so that neither generate a Hall signal.

When the magnet is rotated counterclockwise the poles then also cover the PSIN and NSIN sensors, resulting in the sine and cosine signals shown in Figure 4 being produced. The signals are internal but can be made externally available for test purposes (see chapter 'TEST MODES').

# **i** Haus

Rev B1, Page 9/22

(Top view)

Figure 3: Zero position of the magnet

Figure 4: Pattern of the internal analog sensor signals with the angle of rotation

### LINEAR ANALOG OUTPUT (LAO)

The LAO pin provides a linear analog output voltage representing the actual position. The output voltage can be either rail to rail or within a range of 10% to 90% of the supply voltage VDD, depending on the programmed configuration. In 10%-to-90% mode a short-circuit with VDD or GND is recognizable.

The zero position therefore begins at the minimum voltage (either GND or 10% of VDD) and reaches its maximum (either VDD or 90% of VDD) at the selected angular range limit (90°, 180°, 270° or 360°), depending on the chosen configuration.

LAO is tristate when the device is disabled.

Figure 5: Linear analog output voltage

Rev B1, Page 10/22

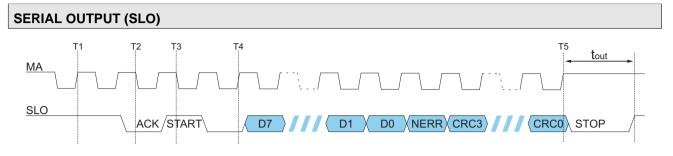

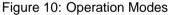

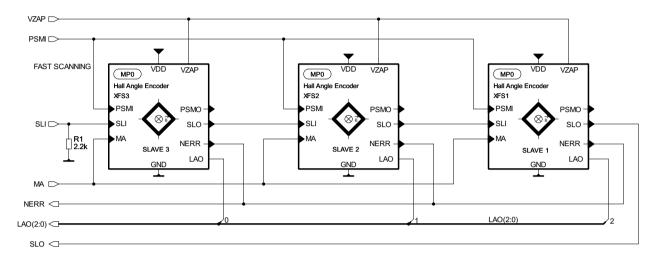

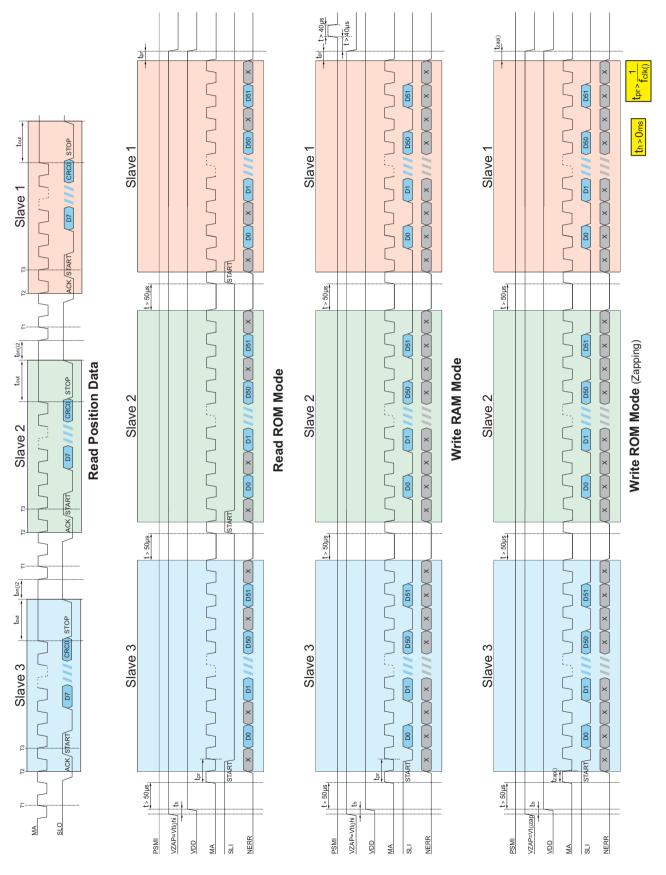

Figure 6: Serial data timing

D0 to D7 make up the absolute position data with respect to the programmed position offset (OFFSET1 xor OFFSET2 xor OFFSET3).

The absolute position is latched by a low to high transition at MA (see T1).

After an acknowledge (T2) at SLO iC-MP requests processing time until the start condition (T3) is sent. Processing time must be provided in Slow Scanning Mode during startup.

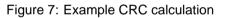

With rising edge T4 at the clock pin the most significant bit (D7) is placed on the serial data line SLO. After T5 has elapsed the controller can stop clocking at MA and the device is ready to latch a new position after a timeout ( $t_{out}$ ). If the controller continues to clock in a daisy chain in Fast Scanning Mode after T5 has elapsed, the second device (slave 2) outputs the position latched at T1 at pin SLO.

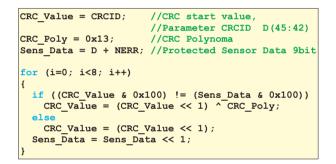

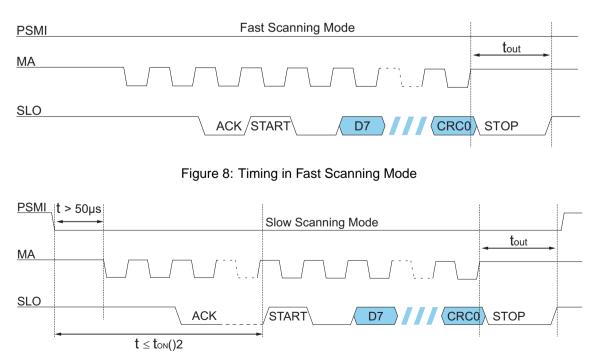

The absolute position data (D0-D7) is binary coded. The position data and the error bit (NERR) are CRC protected. The CRC polynomial is  $X^4$ +X+1 = 0x13.

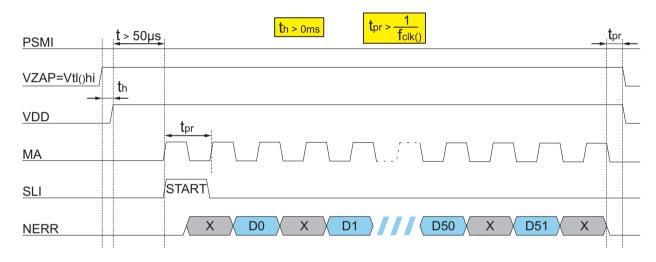

Figure 9: Timing in Slow Scanning Mode

Rev B1, Page 11/22

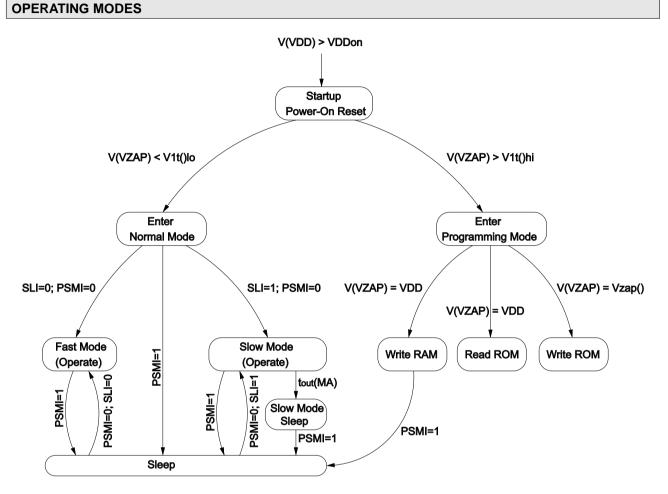

Figure 10 shows the different modes of iC-MP. There are two major modes of operation:

#### • Normal Mode:

Readout position data and error bit. Normal mode is subdivided into two minor modes of operation:

- Fast Scanning Mode: iC-MP is always activated.

- Slow Scanning Mode (Power Save Mode): iC-MP goes into Slow Mode Sleep following the first transmission of sensor data via the serial interface.

- Programming Mode:

iC-MP can be configured in programming mode. See

the chapter on 'PROGRAMMING MODE' for further details. There are three minor modes:

- Read ROM: iC-MP's Zener zap ROM structure is read.

- Write RAM: iC-MP's internal registers can be temporarily programmed for test purposes.

- Write ROM:

iC-MP's zapping structure is programmed.

A Power-On Reset is required after a Read ROM and Write ROM instruction. Each state is quit by a Power-On Reset.

Rev B1, Page 12/22

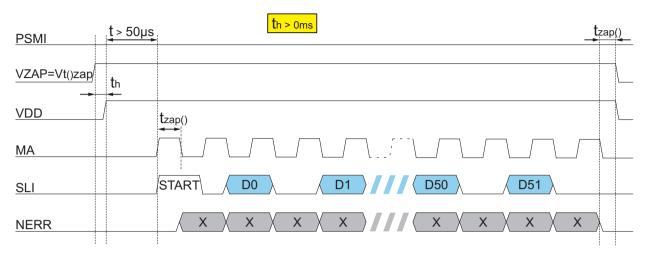

### **PROGRAMMING MODE**

When pulling the VZAP pin to high during startup, the programming mode is entered (see 'OPERATING MODES'). In this mode there are three different categories of operation:

• Write ROM Mode (V(VZAP) =  $V_{zap}$ (), according to ELEC.CHAR., no. 507):

In Write ROM Mode each Zener zap diode is burned (= zapped) immediately on the rising edge of MA. See Figure 13 for details. For the conditions of operation of Write ROM Mode, see ELEC.CHAR., 'Zapping Input VZAP'.

- Write RAM Mode (V(VZAP) = VDD): In Write RAM Mode the iC-MP reacts as in Write ROM Mode but there is no zapping of the Zener zap diodes. This mode can be used to temporarily program iC-MP (non-permanent) for test purpose.

- Read ROM (V(VZAP) = VDD): In Read ROM Mode the content of the Zener zap diodes is read out. A Read ROM operation overwrites iC-MP's RAM content.

Figure 11: Serial timing of Read ROM Mode

Figure 12: Serial timing of Write RAM Mode

Rev B1, Page 13/22

Figure 13: Serial timing of Write ROM Mode

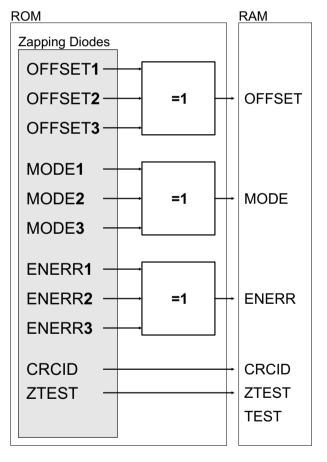

Figure 13 shows the serial timing of a Write ROM operation (burning the Zener zap diodes). The bit stream is described in Table 4. Each Zener zap diode can be programmed once with a logic of '1'. The default value of the Zener zap diodes is a logic '0' (with the exception of ZTEST(1:0)). The resulting parameter (OFF-SET, MODE and ENERR) are generated by an xor operation of the three sets of bits (see Figure 15).

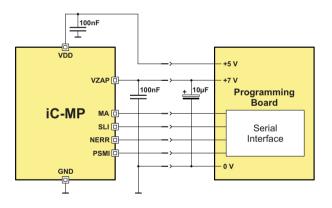

Figure 14: In-circuit programming

A 100 nF ceramic block capacitor must be placed on the board directly between iC-MP's VZAP and GND pins. A 10  $\mu$ F capacitor must also be present at the end of the programming line as close to the connector as possible (see Figure 14). During programming, up to 90 mA flow from pin VZAP to pin GND, making it necessary to ensure proper PCB layout to minimize voltage drops.

Figure 15: ROM construction

Rev B1, Page 14/22

| D(51:0) | Parameter    | Description                                            |

|---------|--------------|--------------------------------------------------------|

| 7:0     | OFFSET1(7:0) | Offset of the first set                                |

| 11:8    | MODE1(3:0)   | Mode of the first set, see Table 5 and 6               |

| 13:12   | ENERR1(1:0)  | Error mask of the first set, see Table 8               |

| 21:14   | OFFSET2(7:0) | Offset of the second set                               |

| 25:22   | MODE2(3:0)   | Mode of the second set, see Table 5 and 6              |

| 27:26   | ENERR2(1:0)  | Error mask of the second set, see Table 8              |

| 35:28   | OFFSET3(7:0) | Offset of the third set                                |

| 39:36   | MODE3(3:0)   | Mode of the third set, see Table 5 and 6               |

| 41:40   | ENERR3(1:0)  | Error mask of the third set, see table 8               |

| 45:42   | CRCID(3:0)   | CRC ID                                                 |

| 47:46   | ZTEST(1:0)   | Zener zap diodes, for<br>iC-Haus test purposes<br>only |

| 51:48   | TEST(3:0)    | See 'TEST MODES'                                       |

#### Table 4: Programming Datastream

| MODE1(1:0) | D(9:8)           |  |

|------------|------------------|--|

| MODE2(1:0) | D(23:22)         |  |

| MODE3(1:0) | D(37:36)         |  |

| Code       | Full Scale Angle |  |

| 00         | 360°             |  |

| 01         | 270°             |  |

| 10         | 180°             |  |

| 11         | 90°              |  |

Table 5: Linear Analog Output - Mode Bit 1:0

| MODE1(2)                                   | D(10)    |  |  |  |

|--------------------------------------------|----------|--|--|--|

| MODE2(2)                                   | D(24)    |  |  |  |

| MODE3(2)                                   | D(38)    |  |  |  |

| Code                                       | Rotation |  |  |  |

| 0                                          | CW*      |  |  |  |

| 1                                          | CCW*     |  |  |  |

| *) CW = clockwise, CCW = counter-clockwise |          |  |  |  |

#### Table 6: Mode Bit 2

| MODE1(3) | D(11)               |  |  |  |

|----------|---------------------|--|--|--|

| MODE2(3) | D(25)               |  |  |  |

| MODE3(3) | D(39)               |  |  |  |

| Code     | Range               |  |  |  |

| 0        | (0 % - 100 %) * VDD |  |  |  |

| 1        | (10% - 90%) * VDD   |  |  |  |

Table 7: Linear Analog Output - Mode Bit 3

### ENERR

The parameter ENERR indicates two kind of errors. If the magnetic field strength is at low a 'Loss of Magnet' is generated. An 'Excessive Frequency Alarm' is generated when the revolution per minute is to high. Parameter ENERR handles the various error types.

| ENERR1(1:              | <b>0)</b> D(13:12)                           |  |  |

|------------------------|----------------------------------------------|--|--|

| ENERR2(1:              | <b>0)</b> D(27:26)                           |  |  |

| ENERR3(1:              | <b>0)</b> D(41:40)                           |  |  |

| Code                   | Error                                        |  |  |

| 00                     | No Error                                     |  |  |

| 01                     | Loss of Magnet*                              |  |  |

| 10                     | Excessive Frequency Alarm                    |  |  |

| 11                     | Excessive Frequency Alarm or Loss of Magnet* |  |  |

| *) see 'DESIGN REVIEW' |                                              |  |  |

Table 8: Error masks

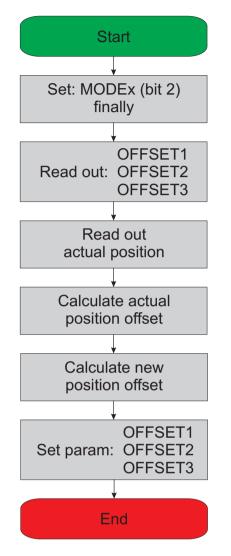

### Calculating the position offset

Before iC-MP outputs the actual position via the serial interface or the linear analog output (LAO), an offset is added internally. This offset consists of the following parameters:

OFFSET = OFFSET1 xor OFFSET2 xor OFFSET3

The offset is programmed in several stages (see Figure 16). It is important that the direction of rotation is programmed prior to this (MODE Bit 2). To determine the actual configured offset, all three offset parameters must be read out. After these parameters have been xored the actual offset is determined:

Actual Offset = OFFSET1 xor OFFSET2 xor OFFSET3

To calculate the new offset the actual position at the required offset is required. The formula used to calculate this new offset is as follows:

New Offset = 256 - Actual Position + Actual Offset

Rev B1, Page 15/22

Figure 16: Principle of offset calculation

### CRCID

The CRCID parameter contains the CRC start value. Configuring the CRC starting value enables a data value to be clearly assigned to a slave, as the CRC check fails with a faulty configuration of the master or an exchange sequence. For example, the controller assigns a start value for each slave and writes these to the CRCID slave parameter.

For CRC calculation, see 'SERIAL OUTPUT (SLO)'.

Rev B1, Page 16/22

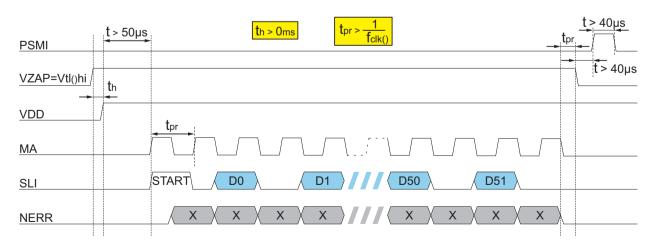

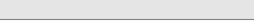

### FAST SCANNING MODE

In Fast Scanning Mode all devices are active at the same time. With a start condition at MA the absolute position of all devices is latched and all absolute positions are transferred as one long data word (see page 17). Parameter CRCID can be used for improved differentiation of the individual data words. See 'PRO-GRAMMING MODE'.

Rev B1, Page 17/22

Rev B1, Page 18/22

### SLOW SCANNING MODE

Figure 18: Slow Scanning Mode

In Slow Scanning Mode only one device is activated in a chain. This device transmits its absolute position on the SLO bus and the analog output voltage to the LAO bus. After an timeout at SLI, the next device is enabled (PSMO hi  $\rightarrow$  lo). The devices needs some time after activation to find the actual position.

Parameter CRCID can be used for improved differen-

tiation of the individual data words. See 'PROGRAM-MING MODE'.

The chain is reset by a logic high at the PSMI pin (see page 19).

### Application hints:

See 'DESIGN REWIEW'.

Rev B1, Page 19/22

**ic** Haus

Rev B1, Page 20/22

### **APPLICATION CIRCUITS**

#### Stand-alone example

Figure 19: Circuit for stand-alone operation

Figure 19 shows an example circuit for stand-alone operation of iC-MP. The device is in Fast Scanning Mode. If the device is also to be programmed, pins PSMI, SLI and VZAP should be connected to GND by a pull-down resistor (e.g.  $2.2 \text{ k}\Omega$ ).

#### **TEST MODES**

iC-MP has several test settings which make internal reference quantities and the amplified, differential Hall voltages of the sensor pairs accessible at external pins for measurement purposes. This signals enables a chip/package to be adjusted in relation to the magnet.

Test modes can be triggered by programming the parameter TEST (D(51:48)). The individual test modes are listed in the following table.

See 'ELECTRICAL CHARACTERISTICS'.

| Op. Mode | TEST(3:0)      | Pin NERR |         | Pin LAO | Pin PSMO | Comments |

|----------|----------------|----------|---------|---------|----------|----------|

|          |                | analog   | digital |         |          |          |

| Normal   | 0ddd           | -        | NERR    | LAO     | PSMO     |          |

| Test 0   | 1000           | PSIN     | -       | PCOS    | PSMO     |          |

| Test 1   | 1001           | NSIN     | -       | NCOS    | PSMO     |          |

| Test 2   | 1010           | GAIN     | -       | VREF    | PSMO     |          |

| Notes    | d = don't care | 1        |         |         |          |          |

Table 9: Test modes

#### **DESIGN REVIEW: Notes On Chip Functions**

| iC-MP Y |                                           |                                                                                                                            |

|---------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| No.     | Function, Parameter/Code                  | Description and Application Notes                                                                                          |

| 1       | Slow Scanning Mode<br>(without a magnet): | Serial Interface Mode is discontinued without a magnet<br>- The start bit is not available<br>- The daisy chain is stopped |

#### Table 10: Notes on chip functions regarding iC-MP chip releas Y

iC-Haus expressly reserves the right to change its products and/or specifications. An Infoletter gives details as to any amendments and additions made to the relevant current specifications on our internet website www.ichaus.de/infoletter; this letter is generated automatically and shall be sent to registered users by email

Copying – even as an excerpt – is only permitted with iC-Haus approval in writing and precise reference to source. iC-Haus does not warrant the accuracy, completeness or timeliness of the specification on this site and does not assume liability for any errors or omissions in the materials. The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

IC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. IC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

As a general rule our developments, IPs, principle circuitry and range of Integrated Circuits are suitable and specifically designed for appropriate use in technical applications, such as in devices, systems and any kind of technical equipment, in so far as they do not infringe existing patent rights. In principle the range of use is limitless in a technical sense and refers to the products listed in the inventory of goods compiled for the 2008 and following export trade statistics issued annually by the Bureau of Statistics in Wiesbaden, for example, or to any product in the product catalogue published for the 2007 and following exhibitions in Hanover (Hannover-Messe).

We understand suitable application of our published designs to be state-of-the-art technology which can no longer be classed as inventive under the stipulations of patent law. Our explicit application notes are to be treated only as mere examples of the many possible and extremely advantageous uses our products can be put to.

Rev B1, Page 22/22

### **ORDERING INFORMATION**

| Туре                      | Package | Order Designation              |

|---------------------------|---------|--------------------------------|

| iC-MP<br>Evaluation Board | DFN10   | iC-MP DFN10<br>iC-MP EVAL MP1D |

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Am Kuemmerling 18 D-55294 Bodenheim GERMANY Tel.: +49 (61 35) 92 92-0 Fax: +49 (61 35) 92 92-192 Web: http://www.ichaus.com E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.com/sales\_partners