### **Features**

- . A Family of Devices with User Memories of 1 Kbit to 64 Kbit

- Contactless 13.56 MHz RF Communications Interface

- ISO/IEC 14443-2:2001 Type B Compliant

- ISO/IEC 14443-3:2001 Type B Compliant Anticollision Protocol

- Tolerant of Type A Signaling for Multi-Protocol Applications

- Integrated 82 pF Tuning Capacitor

- User EEPROM Memory Configurations:

- 64 Kbits Configured as Sixteen 512 byte (4 Kbit) User Zones [AT88SC6416CRF]

- 32 Kbits Configured as Sixteen 256 byte (2 Kbit) User Zones [AT88SC3216CRF]

- 16 Kbits Configured as Sixteen 128 byte (1 Kbit) User Zones [AT88SC1616CRF]

- 8 Kbits Configured as Eight 128 byte (1 Kbit) User Zones [AT88SC0808CRF]

- 4 Kbits Configured as Four 128 byte (1 Kbit) User Zones [AT88SC0404CRF]

- 2 Kbits Configured as Four 64 byte (512 bit) User Zones [AT88SC0204CRF]

- 1 Kbits Configured as Four 32 byte (256 bit) User Zones [AT88SC0104CRF]

- Byte, Page, and Partial Page Write Modes

- Self Timed Write Cycle

- 256 byte (2 Kbit) Configuration Memory

- User Programmable Application Family Identifier (AFI)

- User-defined Anticollision Polling Response

- User-defined Keys and Passwords

- . High Security Features

- Selectable Access Rights by Zone

- 64-bit Mutual Authentication Protocol (under license of ELVA)

- Encrypted Checksum

- Stream Encryption

- Four Key Sets for Authentication and Encryption

- Four or Eight 24-bit Password Sets

- Password and Authentication Attempts Counters

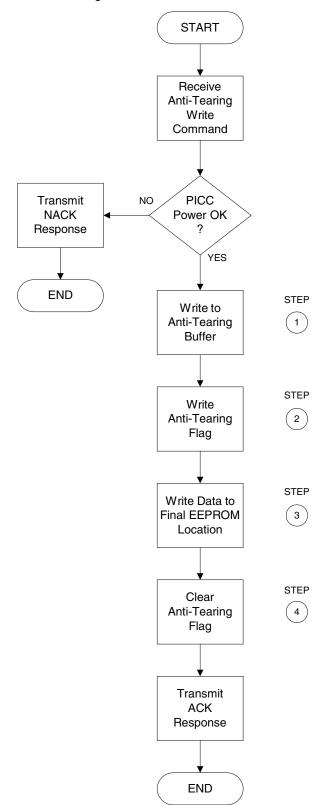

- Anti-tearing Function

- Tamper Sensors

- High Reliability

- Endurance: 100,000 Write Cycles

- Data Retention: 10 Years

# **CryptoRF Specification**

AT88SC0104CRF AT88SC0204CRF AT88SC0404CRF AT88SC0808CRF AT88SC1616CRF AT88SC3216CRF AT88SC6416CRF

|          | Features                                           | 1  |

|----------|----------------------------------------------------|----|

| 1        | Introduction                                       | 4  |

|          | 1.1 Description                                    | 4  |

|          | 1.2 Block Diagram                                  | 4  |

|          | 1.3 Communications                                 | 5  |

|          | 1.4 Scope                                          | 5  |

|          | 1.5 Conventions                                    | 5  |

| 2        | User Memory                                        | 7  |

| 3        | Configuration Memory                               | 7  |

| 4        | Command Set                                        | 8  |

|          | 4.1 Anticollision Command Definitions              | 9  |

|          | 4.2 REQB / WUPB Polling Commands [\$05]            | 9  |

|          | 4.3 Slot MARKER Command [\$s5]                     | 12 |

|          | 4.4 ATTRIB Command [\$1D]                          | 14 |

|          | 4.5 HLTB Command [\$50]                            | 16 |

|          | 4.6 Active State Command Definitions               | 17 |

|          | 4.7 Set User Zone Command [\$c1]                   | 18 |

|          | 4.8 Read User Zone Command [\$c2]                  | 21 |

|          | 4.9 Read User Zone (Large Memory) Command [\$c2]   | 24 |

|          | 4.10 Write User Zone Command [\$c3]                | 27 |

|          | 4.11 Write User Zone (Large Memory) Command [\$c3] | 30 |

|          | 4.12 Write System Zone Command [\$c4]              | 33 |

|          | 4.13 Read System Zone Command [\$c6]               | 37 |

|          | 4.14 Verify Crypto Command [\$c8]                  | 40 |

|          | 4.15 Send Checksum Command [\$c9]                  | 41 |

|          | 4.16 DESELECT Command [\$cA]                       | 42 |

|          | 4.17 IDLE Command [\$cB]                           | 43 |

|          | 4.18 Check Password Command [\$cC]                 | 44 |

| <b>5</b> | Transaction Flow                                   | 47 |

| 6        | Absolute Maximum Ratings*                          | 48 |

| 7        | Reliability                                        | 48 |

| 8        | Electrical Characteristics                         | 49 |

|          | 8.1 Tamper Detection                               | 49 |

| Annex: A Terms and Abbreviations 50                                |

|--------------------------------------------------------------------|

| Annex: B Standards and Reference Documents 53                      |

| Annex: C User Memory Maps54                                        |

| Annex: D Configuration Memory Maps65                               |

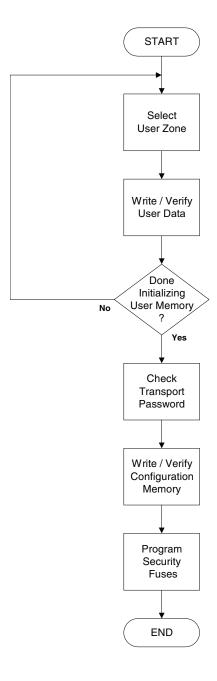

| Annex: E Device Personalization 69                                 |

| Annex: F Security Fuses72                                          |

| Annex: G Configuration of Password and Access Control Registers 74 |

| Annex: H Using Password Security78                                 |

| Annex: I Understanding Anti-Tearing83                              |

| Annex: J Personalization of the Anticollision Registers 87         |

| Annex: K Understanding Anticollision92                             |

| Annex: L The ISO/IEC 14443 Type B RF Signal Interface 94           |

| Annex: M RF Specifications and Characteristics 98                  |

| Annex: N Transaction Time 102                                      |

| Annex: O Ordering Information 104                                  |

| Annex: P Errata 106                                                |

| Devision Vistam                                                    |

### 1. Introduction

# 1.1 Description

The CryptoRF® family integrates a 13.56 Mhz RF interface with CryptoMemory® security features. This product line is ideal for RF tags and contactless smart cards that can benefit from advanced security and cryptographic features. The device is optimized as a contactless secure memory for secure data storage without the requirement of an internal microprocessor.

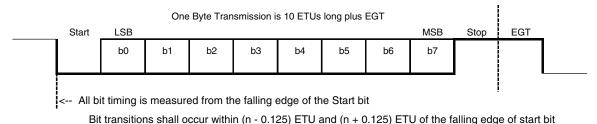

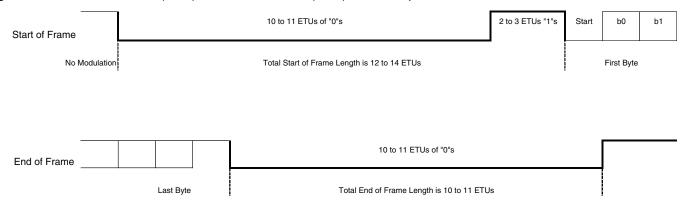

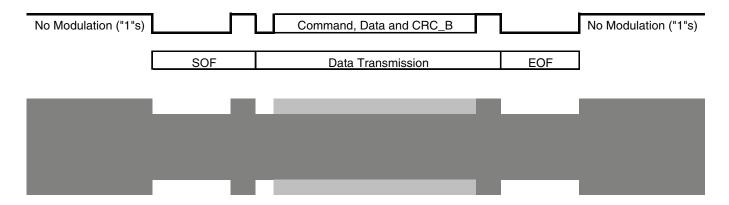

For communications the RF interface utilizes the ISO/IEC 14443–2 and –3 Type B bit timing and signal modulation schemes, and the ISO/IEC 14443-3 Slot-MARKER Anticollision Protocol. Data is exchanged half duplex at a 106k bit per second rate, with a two byte CRC\_B providing error detection capability. The RF interface powers the other circuits, no battery is required. Full compliance with the ISO/IEC 14443 –2 and –3 standards results in anticollision interoperability with the AT88RF020 2 Kbit RFID EEPROM product and provides both a proven RF communication interface, and a robust anticollision protocol.

The seven products in this family contain 1 Kbits to 64 Kbits of User Memory plus 2 Kbits of Configuration Memory. The 2 Kbits of Configuration Memory contains read/write password sets, four crypto key sets, security access registers for each user zone, and password/key registers for each zone.

The CryptoRF command set is optimized for a multicard RF communications environment. A programmable AFI register allows this IC to be used in numerous applications in the same geographic area with seamless discrimination of cards assigned to a particular application during the anticollision process.

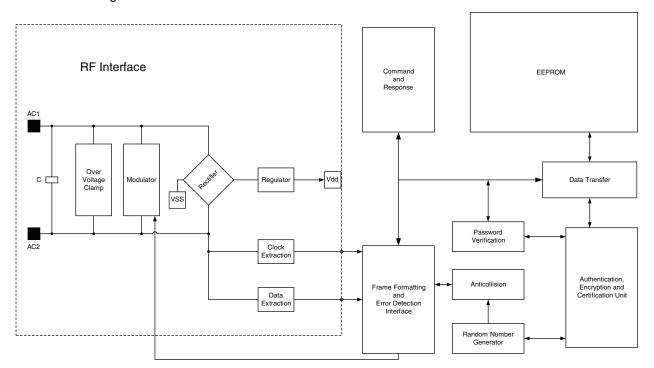

# 1.2 Block Diagram

Figure 1-1. Block Diagram

### 1.3 Communications

All personalization and communication with this device is performed through the RF interface. The IC includes an integrated tuning capacitor, enabling it to operate with only the addition of a single external coil antenna.

The RF communications interface is fully compliant with the electrical signaling and RF power specifications in ISO/IEC 14443-2 for Type B only. Anticollision operation and frame formatting are compliant with ISO/IEC 14443-3 for Type B only.

# 1.4 Scope

This *CryptoRF Specification* document includes all specifications for the normal mode of CryptoRF operation. This document may be freely distributed without any formal user agreements. The Authentication and Encryption modes of operation are not described in this document.

The Authentication and Encryption modes specifications are described in the document *CryptoRF Specification Addendum for Secure Applications*, which is available only under Non-Disclosure and Limited Licensing Agreements (NDA and LLA). Contact your regional Atmel sales office to obtain this secure document.

#### 1.5 Conventions

ISO/IEC 14443 nomenclature is used in this specification where applicable. The following abbreviations are utilized throughout this document. Additional terms are defined in Annex A.

- PCD: Proximity Coupling Device is the reader/writer and antenna.

- PICC: Proximity Integrated Circuit Card is the tag/card containing the IC and antenna.

- **RFU:** Reserved for Future Use is any feature, memory location, or bit that is held as reserved for future use by the ISO standards committee or by Atmel.

- \$xx: Hexadecimal Number denotes a hex number "xx" (Most Significant Bit on left).

- xxxxb: Binary Number denotes a binary number "xxxx" (Most Significant Bit on left).

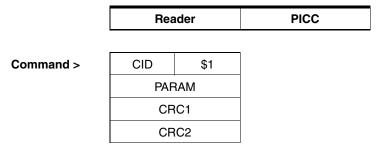

Each command / response exchange between the PCD and PICC is formatted as shown in Figure 1-2. The bytes are shown in the order in which they are transmitted, with PCD transmissions in the left column, and PICC transmissions in the right column.

Each byte contains one or more fields as indicated by lines drawn vertically within the byte. The field in the left half of the byte is the upper nibble of the byte, and the field to the right is the lower nibble of the byte. In Figure 1-2, five fields contain values (\$1D, \$00, \$F, \$51, \$0), four fields contain field names ("Addr", "XX", "CID", "Data"), and four fields contain error detection codes (CRC1, CRC2).

Figure 1-2. Example Command and Response Format

|                        | Rea | ader | PI       | CC  |   |  |    |     |

|------------------------|-----|------|----------|-----|---|--|----|-----|

|                        |     |      | <b>-</b> |     |   |  |    |     |

| Command First Byte >   | \$  | ID   |          |     |   |  |    |     |

| Command Second Byte >  | \$( | 00   |          |     |   |  |    |     |

| Command Third Byte >   | AD  | DR   |          |     |   |  |    |     |

| Command Fourth Byte >  | \$F | XX   |          |     |   |  |    |     |

| Command Fifth Byte >   | \$  | 51   |          |     |   |  |    |     |

| CRC First Byte >       | CF  | RC1  |          |     |   |  |    |     |

| CRC Second Byte >      | CF  | C2   |          |     |   |  |    |     |

| TR2 >                  |     |      | _        |     |   |  |    |     |

| Response First Byte >  |     |      | \$0      | CID |   |  |    |     |

| Response Second Byte > |     |      |          |     | I |  | DA | ιΤΑ |

| CRC First Byte >       |     |      | CR       | C1  |   |  |    |     |

| CRC Second Byte >      |     |      | CRC2     |     |   |  |    |     |

The CRC error detection codes are calculated using all of the previous bytes in the command or response and are appended to each command and response to allow detection of RF communication errors. These bytes are required by ISO/IEC 14443-3:2001 and are usually calculated and verified in the reader hardware.

# 2. User Memory

The User EEPROM Memory characteristics are summarized in Table 2-1 below. User Memory is divided into equally sized User Zones. Access to the User Zones is allowed only after security requirements have been met. These security requirements are defined by the user in the configuration memory during personalization of the device. The default configuration is open read/write access to all user memory zones.

Table 2-1.

CryptoRF User Memory Characteristics

| CryptoRF      | <b>User Memory Size</b> |       | User Memory | Organization | Write Characteristics |                    |

|---------------|-------------------------|-------|-------------|--------------|-----------------------|--------------------|

| Part Number   | Bits                    | Bytes | # Zones     | Bytes/Zone   | Standard Write        | Anti-Tearing Write |

| AT88SC0104CRF | 1K                      | 128   | 4           | 32           | 1 to 16 Bytes         | 1 to 8 Bytes       |

| AT88SC0204CRF | 2K                      | 256   | 4           | 64           | 1 to 16 Bytes         | 1 to 8 Bytes       |

| AT88SC0404CRF | 4K                      | 512   | 4           | 128          | 1 to 16 Bytes         | 1 to 8 Bytes       |

| AT88SC0808CRF | 8K                      | 1K    | 8           | 128          | 1 to 16 Bytes         | 1 to 8 Bytes       |

| AT88SC1616CRF | 16K                     | 2K    | 16          | 128          | 1 to 16 Bytes         | 1 to 8 Bytes       |

| AT88SC3216CRF | 32K                     | 4K    | 16          | 256          | 1 to 32 Bytes         | 1 to 8 Bytes       |

| AT88SC6416CRF | 64K                     | 8K    | 16          | 512          | 1 to 32 Bytes         | 1 to 8 Bytes       |

# 3. Configuration Memory

The configuration memory consists of 2048 bits of EEPROM memory used for storing system data, passwords, keys, codes, and access control registers for each user zone. Access rights to the configuration memory are defined in the control logic and cannot be altered by the user. These access rights include the ability to program certain portions of the configuration memory and then lock the data written through use of the security fuses. The Read System Zone and Write System Zone commands are used to access the configuration memory.

Table 3-1.

Configuration Memory Characteristics

| CryptoRF      | Password Sets | Key Sets | OTP Memory            | Transport Password |            |  |

|---------------|---------------|----------|-----------------------|--------------------|------------|--|

| Part Number   |               | •        | Free For Customer Use | PW Index           | Password   |  |

| AT88SC0104CRF | 4 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$10 14 7C |  |

| AT88SC0204CRF | 4 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$20 C2 8B |  |

| AT88SC0404CRF | 4 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$30 1D D2 |  |

| AT88SC0808CRF | 8 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$40 7F AB |  |

| AT88SC1616CRF | 8 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$50 44 72 |  |

| AT88SC3216CRF | 8 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$60 78 AF |  |

| AT88SC6416CRF | 8 Sets        | 4 Sets   | 27 Bytes              | \$07               | \$70 BA 2E |  |

### 4. Command Set

The CryptoRF command set contains two types of commands: Anticollision commands, and Active State commands. Anticollision commands are explicitly defined in ISO/IEC 14443-3:2001. The CryptoRF Active State commands are Atmel defined commands that are compliant with the ISO/IEC 14443-3:2001 requirements.

The CryptoRF Active State commands contain the CID code that is assigned to a card when it is selected during the anticollision process. See the ATTRIB command for coding of the CID bits.

**Table 4-1.** Coding of the Command Byte for the Anticollision Command Set

| Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Command Name | Hexidecimal |

|-------|--------|-------|-------|-------|-------|-------|-------|--------------|-------------|

| 0     | 0      | 0     | 0     | 0     | 1     | 0     | 1     | REQB/WUPB    | \$05        |

|       | Slot N | umber |       | 0     | 1     | 0     | 1     | Slot MARKER  | \$s5        |

| 0     | 0      | 0     | 1     | 1     | 1     | 0     | 1     | ATTRIB       | \$1D        |

| 0     | 1      | 0     | 1     | 0     | 0     | 0     | 0     | HLTB         | \$50        |

**Table 4-2.** Coding of the Command byte for the CryptoRF Active State Command Set.

| Bit 7 | Bit 6                              | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Command Name      | Hexidecimal |

|-------|------------------------------------|-------|-------|-------|-------|-------|-------|-------------------|-------------|

|       | CI                                 | D     |       | 0     | 0     | 0     | 1     | Set User Zone     | \$c1        |

|       | CI                                 | D     |       | 0     | 0     | 1     | 0     | Read User Zone    | \$c2        |

|       | CI                                 | D     |       | 0     | 0     | 1     | 1     | Write User Zone   | \$c3        |

|       | CI                                 | D     |       | 0     | 1     | 0     | 0     | Write System Zone | \$c4        |

|       | CI                                 | D     |       | 0     | 1     | 1     | 0     | Read System Zone  | \$c6        |

|       | CI                                 | D     |       | 1     | 0     | 0     | 0     | Verify Crypto     | \$c8        |

|       | CI                                 | D     |       | 1     | 0     | 0     | 1     | Send Checksum     | \$c9        |

|       | CI                                 | D     |       | 1     | 0     | 1     | 0     | DESELECT          | \$cA        |

|       | CI                                 | D     |       | 1     | 0     | 1     | 1     | IDLE              | \$cB        |

|       | CI                                 | D     |       | 1     | 1     | 0     | 0     | Check Password    | \$cC        |

|       | All Other Values Are Not Supported |       |       |       |       |       |       |                   |             |

### 4.1 Anticollision Command Definitions

Commands in this section are arranged in order by the hexadecimal code in the command byte.

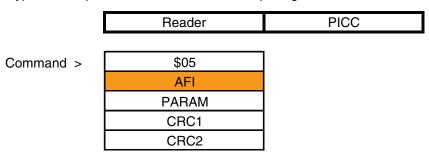

# 4.2 REQB / WUPB Polling Commands [\$05]

The REQB / WUPB command is used to search for PICCs in the RF field. The command and response are ISO/IEC 14443-3:2001 compliant.

|           | Reader | PICC |

|-----------|--------|------|

|           |        |      |

| Command > | \$05   |      |

|           | AFI    |      |

|           | PARAM  |      |

|           | CRC1   |      |

|           | CRC2   |      |

#### ATQB Response >

| \$50       | SUCCESS RESPONSE      |

|------------|-----------------------|

| PUPI 0     | System Zone Byte \$00 |

| PUPI 1     | System Zone Byte \$01 |

| PUPI 2     | System Zone Byte \$02 |

| PUPI 3     | System Zone Byte \$03 |

| APP 0      | System Zone Byte \$04 |

| APP 1      | System Zone Byte \$05 |

| APP 2      | System Zone Byte \$06 |

| APP 3      | System Zone Byte \$07 |

| Protocol 1 | \$00                  |

| Protocol 2 | System Zone Byte \$08 |

| Protocol 3 | \$51                  |

| CRC1       |                       |

| CRC2       |                       |

|            | =                     |

### 4.2.1 Operation

The "Request B" (REQB) and "Wake-Up B" (WUPB) commands are used to probe the RF field for Type B PICCs as the first step in the anticollision process. The response to an REQB or WUPB command is the "Answer to Request B" (ATQB). PICCs in the Active State are not permitted to answer this command.

### 4.2.2 Command Field Descriptions

**AFI:** The Application Family Identifier (AFI) is used to select the family and sub-family of cards which the PCD is targeting. Only PICCs with a matching AFI code are permitted to answer an REQB or WUPB command. Table 4-3 describes the AFI matching criteria. An AFI of \$00 activates all Type B PICCs.

**Table 4-3.** AFI matching criteria for polling commands received by the PICC.

| AFI<br>High Bits | AFI<br>Low Bits | REQB/WUPB Polling produces a PICC response from: |

|------------------|-----------------|--------------------------------------------------|

| \$0              | \$0             | All Families and sub-families                    |

| "X"              | \$0             | All sub-families of Family "X"                   |

| "X"              | "Y"             | Only sub-family "Y" of Family "X"                |

| \$0              | "Y"             | Proprietary sub-family "Y" Only                  |

"Y" = \$1 to \$F

"X" = \$1 to \$F

**PARAM:** The PARAM byte is used to send two parameters to the PICC. The parameter "N", which assigns the number of anticollision slots, and the REQB / WUPB selection bit.

**Figure 4-1.** Coding of the PARAM byte in the REQB/WUPB command.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | RW    |       | N     |       |

**Table 4-4.** Coding of "N", the number of anticollision slots, in the PARAM byte.

| Bit 2 | Bit 1 | Bit 0 | N   |

|-------|-------|-------|-----|

| 0     | 0     | 0     | 1   |

| 0     | 0     | 1     | 2   |

| 0     | 1     | 0     | 4   |

| 0     | 1     | 1     | 8   |

| 1     | 0     | 0     | 16  |

| 1     | 0     | 1     | RFU |

| 1     | 1     | Х     | RFU |

**Table 4-5.** Coding of the REQB / WUPB selection bit in the PARAM byte.

| Bit 3 | Command |

|-------|---------|

| 0     | REQB    |

| 1     | WUPB    |

**CRC:** Communication error detection bytes.

### 4.2.3 Response Field Descriptions

**PUPI:** PseudoUnique PICC Identifier. This is the card ID used for anticollision, stored in the System Zone.

**APP:** Application Data. Information about the card or application, stored in the System Zone.

The fourth byte of the application data field, APP3, is programmed by Atmel with a memory density code at the factory to permit easy identification of different card sizes. The memory density codes programmed by Atmel are shown in Table 4-6.

Table 4-6.

Default value of APP3 is the CryptoRF Memory Density Code

| Device Number | Density Code |

|---------------|--------------|

| AT88SC0104CRF | \$02         |

| AT88SC0204CRF | \$12         |

| AT88SC0404CRF | \$22         |

| AT88SC0808CRF | \$33         |

| AT88SC1616CRF | \$44         |

| AT88SC3216CRF | \$54         |

| AT88SC6416CRF | \$64         |

**Protocol:** ISO/IEC 14443 communication capabilities reported to the PCD.

CRC: Communication error detection bytes.

#### 4.2.4 Error Handling

If an REQB or WUPB command containing errors is received by the PICC, it is ignored and no response is send.

# 4.3 Slot MARKER Command [\$s5]

The Slot MARKER command can be used to separately identify multiple PICCs in the RF field. The command and response are ISO/IEC 14443-3:2001 compliant..

| Rea | der | PICC |

|-----|-----|------|

|     |     | 1    |

| "S" | \$5 |      |

| CR  | C1  |      |

| CR  | C2  |      |

ATQB Response >

Command >

|            | -                     |

|------------|-----------------------|

| \$50       | SUCCESS RESPONSE      |

| PUPI 0     | System Zone Byte \$00 |

| PUPI 1     | System Zone Byte \$01 |

| PUPI 2     | System Zone Byte \$02 |

| PUPI 3     | System Zone Byte \$03 |

| APP 0      | System Zone Byte \$04 |

| APP 1      | System Zone Byte \$05 |

| APP 2      | System Zone Byte \$06 |

| APP 3      | System Zone Byte \$07 |

| Protocol 1 | \$00                  |

| Protocol 2 | System Zone Byte \$08 |

| Protocol 3 | \$51                  |

| CRC1       |                       |

| CRC2       |                       |

|            |                       |

#### 4.3.1 Operation

12

Slot MARKER is an optional command used to perform ISO/IEC 14443-3 Type B anticollision using the timeslot approach. Immediately after an REQB or WUPB command with "N" greater than 1 is issued, and the ATQB response (if any) is received, the PCD will transmit Slot MARKER commands with slot values "S" of 2 to "N" to define the start of each timeslot for anticollision. If the random number "R" selected by the PICC matches "S" then the PICC responds with ATQB. PICCs in the Active State are not permitted to answer this command.

### 4.3.2 Command Field Descriptions

**S:** The slot number "S" is encoded within the command byte as shown in Table 4-7.

**CRC:** Communication error detection bytes.

### 4.3.3 Response Field Descriptions

**Table 4-7.** Coding of the slot number within the Slot MARKER command byte.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Slot          |

|-------|-------|-------|-------|---------------|

| 0     | 0     | 0     | 0     | Not Supported |

| 0     | 0     | 0     | 1     | 2             |

| 0     | 0     | 1     | 0     | 3             |

| 0     | 0     | 1     | 1     | 4             |

| 0     | 1     | 0     | 0     | 5             |

| 0     | 1     | 0     | 1     | 6             |

| 0     | 1     | 1     | 0     | 7             |

| 0     | 1     | 1     | 1     | 8             |

| 1     | 0     | 0     | 0     | 9             |

| 1     | 0     | 0     | 1     | 10            |

| 1     | 0     | 1     | 0     | 11            |

| 1     | 0     | 1     | 1     | 12            |

| 1     | 1     | 0     | 0     | 13            |

| 1     | 1     | 0     | 1     | 14            |

| 1     | 1     | 1     | 0     | 15            |

| 1     | 1     | 1     | 1     | 16            |

**PUPI:** PseudoUnique PICC Identifier. This is the card ID used for anticollision, stored in the System Zone.

**APP:** Application Data. Information about the card or application, stored in the System Zone.

**Protocol:** ISO/IEC 14443 communication capabilities reported to the PCD.

**CRC:** Communication error detection bytes.

#### 4.3.4 Error Handling

If a Slot MARKER command containing errors is received by the PICC, it is ignored and no response is send.

# 4.4 ATTRIB Command [\$1D]

The ATTRIB command is used to select a PICC for a transaction. The command and response are ISO/IEC 14443-3:2001 compliant.

|                       | Re   | PI    |   |

|-----------------------|------|-------|---|

|                       |      |       |   |

| Command >             | \$   | 31D   | İ |

|                       | PU   | JPI 0 | İ |

| PUPI of PCI >         | PU   | JPI 1 | İ |

|                       | PU   | JPI 2 | İ |

|                       | PU   | JPI 3 | İ |

| Param 1 >             | 9    | 500   | İ |

| Param 2 >             | \$0  | TBmax | İ |

| Param 3 >             | 9    | 500   | İ |

| Param 4 Assigns CID > | \$0  | CID   | İ |

|                       | CRC1 |       | 1 |

|                       | CRC2 |       | İ |

Operation

4.4.1

14

Sending the ATTRIB command (with a matching PUPI) after an ATQB response places the PICC in the Active State and assigns the Card ID Number (CID) to the PICC. PICCs already in the Active State or Halt State are not permitted to answer this command.

CRC1

CID

SUCCESS RESPONSE

\$0

### 4.4.2 Command Field Descriptions

ATTRIB Response >

**PUPI:** PseudoUnique PICC Identifier. This is the card ID used for anticollision, stored in the System Zone.

**Param:** ISO/IEC 14443 communication capabilities reported to the PICC. The contents of Param Bytes 1, 2, and 3 are not used by the CryptoRF family.

**TBmax:** A parameter sent by the PCD reporting the receive buffer size of the PCD. Default value is \$0.

**CID:** The Card ID Number (CID) in ATTRIB Param Byte 4 and in the ATTRIB Response is encoded as shown in Table 4-8. Each PICC is assigned a unique CID when it is placed in the Active State. CryptoRF Active State commands use the assigned CID to direct the commands to the desired PICC.

**Table 4-8.** Coding of the Card ID in the ATTRIB command and response.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | CID           |  |

|-------|-------|-------|-------|---------------|--|

| 0     | 0     | 0     | 0     | Not Supported |  |

| 0     | 0     | 0     | 1     | 1             |  |

| 0     | 0     | 1     | 0     | 2             |  |

| 0     | 0     | 1     | 1     | 3             |  |

| 0     | 1     | 0     | 0     | 4             |  |

| 0     | 1     | 0     | 1     | 5             |  |

| 0     | 1     | 1     | 0     | 6             |  |

| 0     | 1     | 1     | 1     | 7             |  |

| 1     | 0     | 0     | 0     | 8             |  |

| 1     | 0     | 0     | 1     | 9             |  |

| 1     | 0     | 1     | 0     | 10            |  |

| 1     | 0     | 1     | 1     | 11            |  |

| 1     | 1     | 0     | 0     | 12            |  |

| 1     | 1     | 1 1   |       | 13            |  |

| 1     | 1     | 1     | 0     | 14            |  |

| 1     | 1     | 1     | 1     | Not Supported |  |

**CRC:** Communication error detection bytes.

### 4.4.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**CRC:** Communication error detection bytes.

### 4.4.4 Error Handling

If an ATTRIB command containing transmission errors is received by the PICC, it is ignored and no response is send.

# 4.5 **HLTB Command** [\$50]

The HLTB command places a PICC in the Halt State, where it is not allowed to answer an REQB command. The command and response are ISO/IEC 14443-3 compliant.

|               | Reader                   | PICC |

|---------------|--------------------------|------|

|               |                          |      |

| Command >     | \$50                     |      |

|               | PUPI 0                   |      |

| PUPI of PCI > | PUPI 1                   |      |

|               | PUPI 2                   |      |

|               | PUPI 3                   |      |

|               | CRC1                     |      |

|               | CRC2                     |      |

| PUPI of PCI > | PUPI 2<br>PUPI 3<br>CRC1 |      |

**HLTB Response >**

| \$00 | SUCCESS RESPONSE |

|------|------------------|

| CRC1 |                  |

| CRC2 |                  |

### 4.5.1 Operation

Sending the "Halt B" (HLTB) command (with a matching PUPI) after an ATQB response places the PICC in the Halt State. A PICC in the Halt State will only respond to a WUPB command. PICCs in the Active State or already in the Halt State are not permitted to answer this command.

### 4.5.2 Command Field Descriptions

**PUPI:** PseudoUnique PICC Identifier. This is the card ID used for anticollision, stored in the System Zone.

CRC: Communication error detection bytes.

### 4.5.3 Response Field Descriptions

CRC: Communication error detection bytes.

### 4.5.4 Error Handling

If a HLTB command containing errors is received by the PICC, it is ignored and no response is send.

### 4.6 Active State Command Definitions

Commands in this section are arranged in order by the hexadecimal code in the command byte.

**Table 4-9.** Coding of the Command byte for the CryptoRF Active State Command Set

| Bit 7 Bit 6 Bit 5 Bi | t 4 Bit 3 | Bit 2       | Bit 1      | Bit 0    | Command Name      | Hexidecimal |

|----------------------|-----------|-------------|------------|----------|-------------------|-------------|

| CID                  | 0         | 0           | 0          | 1        | Set User Zone     | \$c1        |

| CID                  | 0         | 0           | 1          | 0        | Read User Zone    | \$c2        |

| CID                  | 0         | 0           | 1          | 1        | Write User Zone   | \$c3        |

| CID                  | 0         | 1           | 0          | 0        | Write System Zone | \$c4        |

| CID                  | 0         | 1           | 1          | 0        | Read System Zone  | \$c6        |

| CID                  | 1         | 0           | 0          | 0        | Verify Crypto     | \$c8        |

| CID                  | 1         | 0           | 0          | 1        | Send Checksum     | \$c9        |

| CID                  | 1         | 0           | 1          | 0        | DESELECT          | \$cA        |

| CID                  | 1         | 0           | 1          | 1        | IDLE              | \$cB        |

| CID                  | 1         | 1           | 0          | 0        | Check Password    | \$cC        |

|                      |           | All Other \ | /alues are | Not Supp | orted             |             |

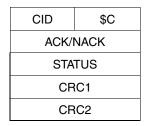

### 4.6.1 Response Format

The response to each Active State command consists of five bytes or more. The first byte of the response is the command byte echoed back to the PCD. The second byte is the ACK/NACK byte which reports success or failure of the command execution. The final two bytes of the response are always the CRC bytes. The CRC bytes are preceded by a STATUS byte which reports error codes or PICC status codes. Any data bytes returned by the command are located between the ACK/NACK and STATUS bytes.

Table 4-10. Coding of the ACK/NACK byte of the PICC response

| Bit 7                  | Bit 6                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                                              | Bit 0                                | Response Decode                 |  |

|------------------------|---------------------------|-------|-------|-------|-------|----------------------------------------------------|--------------------------------------|---------------------------------|--|

| 0                      | 0                         | 0     | 0     | 0     | 0     | 0                                                  | 0                                    | ACK                             |  |

| 0                      | 0                         | 0     | 0     | 0     | 0     | 0                                                  | 1                                    | NACK, See STATUS byte for cause |  |

| Pas                    | Password Attempts Counter |       | 0     | 0     | 0     | 1                                                  | NACK, Check Password Attempt Failure |                                 |  |

| Auth. Attempts Counter |                           | 0     | 0     | 0     | 1     | NACK, Authentication or Encryption Attempt Failure |                                      |                                 |  |

The STATUS byte reports reasons for failure of an operation, and provides feedback to the host application indicating status of the PICC. The PICC ignores commands that do not have a matching CID. Invalid command codes are also ignored.

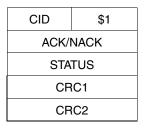

# 4.7 Set User Zone Command [\$c1]

The Set User Zone command selects the user memory area to be addressed by the Read User Zone and Write User Zone commands.

Echo Command >

### 4.7.1 Operation

Before reading and writing data to the user memory, the host must select a User Zone with this command. Only one User Zone may be selected at a time. At the time the zone is selected the host also chooses whether anti-tearing should be active for this zone. If anti-tearing is activated, then all writes to the User Zone will utilize anti-tearing until a new Set User Zone command is received. Only PICCs in the Active State are permitted to answer this command.

#### 4.7.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

**PARAM:** Selects the User Zone and sets anti-tearing on or off. When the anti-tearing bit (bit 7) is set to 1b then anti-tearing is enabled, when set to 0b normal writes are selected.

Figure 4-2. Coding of the PARAM byte of the Set User Zone command

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| AT    | 0     | 0     | 0     |       | User  | Zone  |       |

**Table 4-11.** Coding of the User Zone number within the PARAM byte

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | User Zone |

|-------|-------|-------|-------|-----------|

| 0     | 0     | 0     | 0     | 0         |

| 0     | 0     | 0     | 1     | 1         |

| 0     | 0     | 1     | 0     | 2         |

| 0     | 0     | 1     | 1     | 3         |

| 0     | 1     | 0     | 0     | 4         |

| 0     | 1     | 0     | 1     | 5         |

| 0     | 1     | 1     | 0     | 6         |

| 0     | 1     | 1     | 1     | 7         |

| 1     | 0     | 0     | 0     | 8         |

| 1     | 0     | 0     | 1     | 9         |

| 1     | 0     | 1     | 0     | 10        |

| 1     | 0     | 1     | 1     | 11        |

| 1     | 1     | 0     | 0     | 12        |

| 1     | 1     | 0     | 1     | 13        |

| 1     | 1     | 1     | 0     | 14        |

| 1     | 1     | 1     | 1     | 15        |

**CRC:** Communication error detection bytes.

### 4.7.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

NACK: Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

CRC: Communication error detection bytes.

# 4.7.4 Error Handling

If a Set User Zone command containing transmission errors is received by the PICC, it is ignored and no response is send.

Table 4-12.

Status Codes returned in the Set User Zone response

| Error/Status Message    | Status Code | Туре |

|-------------------------|-------------|------|

| No Errors               | \$00        | ACK  |

| User Zone PARAM Invalid | \$A1        | NACK |

#### 4.8 Read User Zone Command [\$c2]

The Read User Zone command reads data from the currently selected User Zone. See Read User Zone (Large Memory) command for the AT88SC6416CRF read command information.

|                | Rea | der      | PIC  | CC    |                  |

|----------------|-----|----------|------|-------|------------------|

|                |     |          |      |       |                  |

| Command >      | CID | \$2      |      |       |                  |

|                | \$0 | 00       |      |       |                  |

|                | AD  | DR       |      |       |                  |

|                | "[  | <u>"</u> |      |       |                  |

|                | CR  | C1       |      |       |                  |

|                | CR  | C2       |      |       |                  |

|                |     | i        |      |       | 1                |

| Echo Command > |     |          | CID  | \$2   | FAILURE RESPONSE |

|                |     | 1        | NA   | CK    |                  |

|                |     |          | STA  | TUS   | < Error Code     |

|                |     |          | CR   | C1    |                  |

|                |     |          | CR   | C2    |                  |

|                |     | I        | ı    |       | ]                |

| Echo Command > |     |          | CID  | \$2   | SUCCESS RESPONSE |

|                |     |          | AC   |       |                  |

|                |     | li li    | DAT  |       |                  |

|                |     |          | DAT  | A 2   |                  |

|                |     |          |      |       |                  |

|                |     |          | DATA |       |                  |

|                |     |          |      | "L+1" |                  |

|                |     |          | STA  |       | < Status Code    |

|                |     |          | CR   |       |                  |

|                |     |          | CR   | C2    |                  |

#### 4.8.1 Operation

The Read User Zone command reads data from the device's currently selected User Zone.

The data byte address is internally incremented as each byte is read from memory. If the data byte address increments beyond the end of the current zone during a read, then the address will "roll over" to the first byte of the same zone. Only PICCs in the Active State are permitted to answer this command.

### 4.8.2 Command Field Descriptions

CID: The Card ID assigned by the ATTRIB command.

ADDR: The starting address of the data to read.

L: The number of bytes to read minus 1. L cannot exceed the size of the user zone.

Reading more than 64 bytes in a single operation is not recommended. In a typical application environment, optimal transaction time is achieved by reading no more than 32 data bytes in a single operation.

CRC: Communication error detection bytes.

### 4.8.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

**DATA:** The data bytes read from user memory.

STATUS: PICC status code.

CRC: Communication error detection bytes.

# 4.8.4 Error Handling

If a Read User Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

Table 4-13.

Status Codes returned in the Read User Zone response

| Error/Status Message                             | Status Code | Туре     |

|--------------------------------------------------|-------------|----------|

| No errors                                        | \$00        | ACK      |

| Access Denied (User Zone Not Set)                | \$99        | NACK     |

| Address Invalid                                  | \$A2        | NACK     |

| Length Invalid                                   | \$A3        | NACK     |

| Authentication or Encryption Activation Required | \$A9        | NACK     |

| Password Required                                | \$D9        | NACK     |

| Memory Access Error                              | \$EE        | ACK/NACK |

# 4.9 Read User Zone (Large Memory) Command [\$c2]

The Read User Zone (Large Memory) command reads data from the currently selected User Zone. This command format applies to the AT88SC6416CRF device only.

|                | Rea | ader | PIC  | CC  |                  |

|----------------|-----|------|------|-----|------------------|

|                |     |      | _    |     | _                |

| Command >      | CID | \$2  |      |     |                  |

|                | ADE | DR H |      |     |                  |

|                | ADI | DR L |      |     |                  |

|                | "   | L"   |      |     |                  |

|                | CF  | RC1  |      |     |                  |

|                | CF  | RC2  |      |     |                  |

|                |     |      |      |     | _                |

| Echo Command > |     |      | CID  | \$2 | FAILURE RESPONSE |

|                |     |      | NA   | CK  |                  |

|                |     |      | STA  |     | < Error Code     |

|                |     |      | CR   | C1  |                  |

|                |     |      | CR   | C2  |                  |

|                |     |      |      |     |                  |

| Echo Command > |     |      | CID  | \$2 | SUCCESS RESPONSE |

|                |     |      | AC   |     |                  |

|                |     |      | DAT  |     |                  |

|                |     |      | DAT  | A 2 |                  |

|                |     |      |      |     | _                |

|                |     |      | DATA |     |                  |

|                |     |      | DATA |     |                  |

|                |     |      | STA  |     | < Status Code    |

|                |     |      | CR   |     |                  |

|                |     |      | CR   | C2  |                  |

# 4.9.1 Operation

24

The Read User Zone (Large Memory) command operates identically to the standard Read User Zone command, but utilizes a two byte address to support large memory sizes. The Read User Zone command reads data from the device's currently selected User Zone. The data byte address is internally incremented as each byte is read from memory. If the data byte address increments beyond the end of the current zone during a read, then the address will "roll over" to the first byte of the same zone. Only PICCs in the Active State are permitted to answer this command.

### 4.9.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

**ADDR:** The two byte starting address of the location to be written.

Figure 4-3. Format of the ADDR H byte of the Write User Zone (Large Memory) command

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | A8    |

L: The number of bytes to read minus 1. L cannot exceed the size of the user zone.

Reading more than 64 bytes in a single operation is not recommended. In a typical application environment, optimal transaction time is achieved by reading no more than 32 data bytes in a single operation.

CRC: Communication error detection bytes.

### 4.9.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

**DATA:** The data bytes read from user memory.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

# 4.9.4 Error Handling

If a Read User Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

**Table 4-14.** Status Codes returned in the Read User Zone (Large Memory) response.

| Error/Status Message                             | Status Code | Туре     |

|--------------------------------------------------|-------------|----------|

| No Errors                                        | \$00        | ACK      |

| Access Denied (User Zone Not Set)                | \$99        | NACK     |

| Address Invalid                                  | \$A2        | NACK     |

| Length Invalid                                   | \$A3        | NACK     |

| Authentication or Encryption Activation Required | \$A9        | NACK     |

| Password Required                                | \$D9        | NACK     |

| Memory Access Error                              | \$EE        | ACK/NACK |

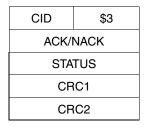

### 4.10 Write User Zone Command [\$c3]

The Write User Zone command writes data into the currently selected User Zone. See Write User Zone (Large Memory) command for the AT88SC6416CRF write command information.

|           | Rea  | ider  | PICC |

|-----------|------|-------|------|

|           |      |       |      |

| Command > | CID  | \$3   |      |

|           | \$0  | 00    |      |

|           | AD   | DR    |      |

|           | "]   | "     |      |

|           | DAT  | TA 1  |      |

|           | DAT  | TA 2  |      |

|           |      |       |      |

|           | DAT  | A "L" |      |

|           | DATA | "L+1" |      |

|           | CR   | C1    |      |

|           | CR   | C2    |      |

Echo Command >

#### 4.10.1 Operation

The Write User Zone command writes data in the device's currently selected User Zone. As each byte is clocked in to the memory the lower bits of the address are internally incremented. The upper address bits are not incremented, so the page address remains constant.

Write operations cannot cross page boundaries; a Write User Zone command can only write data bytes within a single physical memory page. Attempts to write beyond the end of the page boundary will wrap to the beginning of the same page. Only PICCs in the Active State are permitted to answer this command.

#### 4.10.2 Command Field Descriptions

CID: The Card ID assigned by the ATTRIB command.

**ADDR:** The starting address of the location to be written.

L: The number of bytes to read minus 1. "L" cannot exceed the physical page size of the memory. In anti-tearing mode the maximum number of bytes that can be written is 8 bytes. If the

Access Register enables Write Lock mode or Program Only mode, the maximum number of bytes that can be written is 1 byte.

Table 4-15. Write Characteristics of CryptoRF

| CryptoRF      | Write Cha      | racteristics       |

|---------------|----------------|--------------------|

| Part Number   | Standard Write | Anti-Tearing Write |

| AT88SC0104CRF | 1 to 16 Bytes  | 1 to 8 Bytes       |

| AT88SC0204CRF | 1 to 16 Bytes  | 1 to 8 Bytes       |

| AT88SC0404CRF | 1 to 16 Bytes  | 1 to 8 Bytes       |

| AT88SC0808CRF | 1 to 16 Bytes  | 1 to 8 Bytes       |

| AT88SC1616CRF | 1 to 16 Bytes  | 1 to 8 Bytes       |

| AT88SC3216CRF | 1 to 32 Bytes  | 1 to 8 Bytes       |

**DATA:** The data bytes to be written into user memory.

CRC: Communication error detection bytes.

### 4.10.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

ACK: Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

#### 4.10.4 Error Handling

If a Write User Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

Table 4-16.

Status Codes returned in the Write User Zone response

| Error/Status Message                             | Status Code | Туре     |

|--------------------------------------------------|-------------|----------|

| No Errors                                        | \$00        | ACK      |

| Write Pending - Checksum Required                | \$0C        | ACK      |

| One Byte Written (Write Lock Mode)               | \$1B        | ACK      |

| Access Denied (User Zone Not Set)                | \$99        | NACK     |

| Access Denied ( Security Fuses Invalid)          | \$99        | NACK     |

| Address Invalid                                  | \$A2        | NACK     |

| Length Invalid                                   | \$A3        | NACK     |

| Authentication or Encryption Activation Required | \$A9        | NACK     |

| Data Written (Program Only Mode)                 | \$B0        | ACK      |

| Access Denied (Write Lock Mode)                  | \$B9        | NACK     |

| Password Required                                | \$D9        | NACK     |

| Modify Forbidden                                 | \$E9        | NACK     |

| Memory Access Error                              | \$EE        | ACK/NACK |

# 4.11 Write User Zone (Large Memory) Command [\$c3]

The Write User Zone command writes data into the currently selected User Zone. This command format applies to the AT88SC6416CRF device only.

| Reader | PICC |

|--------|------|

|        |      |

#### Command >

| CID      | \$3   |

|----------|-------|

| ADD      | R H   |

| ADE      | DR L  |

| "[       | "     |

| DAT      | TA 1  |

| DATA 2   |       |

|          |       |

| DATA "L" |       |

| DATA     | "L+1" |

| CR       | C1    |

| CR       | C2    |

#### Echo Command >

| CID    | \$3  |  |

|--------|------|--|

| ACK/I  | NACK |  |

| STATUS |      |  |

| CRC1   |      |  |

| CR     | C2   |  |

#### 4.11.1 Operation

The Write User Zone (Large Memory) command operates identically to the standard Write User Zone command, but utilizes a two byte address to support large memory sizes. The Write User Zone command writes data in the device's currently selected User Zone. As each byte is clocked in to the memory the lower bits of the address are internally incremented. The upper address bits are not incremented, so the page address remains constant.

Write operations cannot cross page boundaries; a Write User Zone command can only write data bytes within a single physical memory page. Attempts to write beyond the end of the page boundary will wrap to the beginning of the same page. Only PICCs in the Active State are permitted to answer this command.

### 4.11.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

**ADDR:** The two byte starting address of the location to be written.

Figure 4-4. Format of the ADDR H byte of the Write User Zone (Large Memory) command

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | A8    |

L: The number of bytes to read minus 1. "L" cannot exceed the physical page size of the memory. In anti-tearing mode the maximum number of bytes that can be written is 8 bytes. If the Access Register enables Write Lock mode or Program Only mode, the maximum number of bytes that can be written is 1 byte.

Table 4-17. Write Characteristics of Large Memory CryptoRF

| CryptoRF      | Write Characteristics |                    |  |

|---------------|-----------------------|--------------------|--|

| Part Number   | Standard Write        | Anti-Tearing Write |  |

| AT88SC6416CRF | 1 to 32 Bytes         | 1 to 8 Bytes       |  |

**DATA:** The data bytes to be written into user memory.

CRC: Communication error detection bytes.

### 4.11.3 Response Field Descriptions

CID: The PICC transmits it's assigned card ID in the response.

ACK: Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

# 4.11.4 Error Handling

If a Write User Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

Table 4-18.

Status Codes returned in the Write User Zone (Large Memory) response

| Error/Status Message                             | Status Code | Туре     |

|--------------------------------------------------|-------------|----------|

| No Errors                                        | \$00        | ACK      |

| Write Pending - Checksum Required                | \$0C        | ACK      |

| One Byte Written (Write Lock Mode)               | \$1B        | ACK      |

| Access Denied (User Zone Not Set)                | \$99        | NACK     |

| Access Denied ( Security Fuses Invalid)          | \$99        | NACK     |

| Address Invalid                                  | \$A2        | NACK     |

| Length Invalid                                   | \$A3        | NACK     |

| Authentication or Encryption Activation Required | \$A9        | NACK     |

| Data Written (Program Only Mode)                 | \$B0        | ACK      |

| Access Denied (Write Lock Mode)                  | \$B9        | NACK     |

| Password Required                                | \$D9        | NACK     |

| Modify Forbidden                                 | \$E9        | NACK     |

| Memory Access Error                              | \$EE        | ACK/NACK |

# 4.12 Write System Zone Command [\$c4]

The Write System Zone command writes data to the configuration memory. This command is also used to program the security fuses.

Command >

| CID        | \$4  |  |

|------------|------|--|

| PAF        | RAM  |  |

| AD         | DR   |  |

| "]         | ,,   |  |

| DAT        | TA 1 |  |

| DATA 2     |      |  |

|            |      |  |

| DATA "L"   |      |  |

| DATA "L+1" |      |  |

| CRC1       |      |  |

| CRC2       |      |  |

Echo Command >

| CID    | \$4  |  |

|--------|------|--|

| ACK/I  | NACK |  |

| STATUS |      |  |

| CRC1   |      |  |

| CRC2   |      |  |

### 4.12.1 Operation

The Write System Zone command writes data into the configuration memory. As each byte is clocked in to the memory the lower bits of the address are internally incremented. The upper address bits are not incremented, so the page address remains constant.

Write operations cannot cross page boundaries; a Write System Zone command can only write data bytes within a single physical memory page. Attempts to write beyond the end of the page boundary will wrap to the beginning of the same page. Only PICCs in the Active State are permitted to answer this command.

A special mode of the Write System Zone programs the security fuses. Once programmed, the fuses cannot be erased.

### 4.12.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

**PARAM:** The PARAM byte selects the type of write operation to be performed.

**Table 4-19.** PARAM byte options for the Write System Zone command

| Command                            | PARAM | ADDR      | "L"            | DATA        |  |

|------------------------------------|-------|-----------|----------------|-------------|--|

| Write System Zone                  | \$00  | address   | # of bytes - 1 | "L+1" bytes |  |

| Write System Zone w/ AT            | \$80  | address   | # of bytes - 1 | "L+1 bytes" |  |

| Write Fuse Byte                    | \$01  | fuse addr | \$00           | 1 bytes     |  |

| All Other Values Are Not Supported |       |           |                |             |  |

Table 4-20.

Coding of ADDR for Fuse Programming Only

| Hex  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Fuse |

|------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| \$07 | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     | SEC  |

| \$06 | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 0     | FAB  |

| \$04 | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 0     | СМА  |

| \$00 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | PER  |

**ADDR:** The starting address of the data to write. When performing a fuse byte write the ADDR byte contains the address of the fuse; only one fuse may be programmed per Write System Zone command.

L: The number of bytes to read minus 1. L cannot exceed the physical page size of the memory. In anti-tearing mode the maximum number of bytes that can be written is 8 bytes. If the Access Register enables Write Lock Mode or Program Only Mode, the maximum number of bytes that can be written is 1 byte.

Table 4-21.

Write Characteristics of CryptoRF configuration memory

| CryptoRF      | Write Characteristics |                    |  |  |

|---------------|-----------------------|--------------------|--|--|

| Part Number   | Standard Write        | Anti-Tearing Write |  |  |

| AT88SC0104CRF | 1 to 16 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC0204CRF | 1 to 16 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC0404CRF | 1 to 16 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC0808CRF | 1 to 16 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC1616CRF | 1 to 16 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC3216CRF | 1 to 32 Bytes         | 1 to 8 Bytes       |  |  |

| AT88SC6416CRF | 1 to 32 Bytes         | 1 to 8 Bytes       |  |  |

**DATA:** The data bytes to be written into configuration memory.

One byte of data is required to be sent when writing the fuse byte, however the contents of this byte are ignored.

CRC: Communication error detection bytes.

### 4.12.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

### 4.12.4 Error Handling

If a Write System Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

**Table 4-22.** Status Codes returned in the Write System Zone response

| Error/Status Message              | Status Code | Туре     |

|-----------------------------------|-------------|----------|

| No Errors                         | \$00        | ACK      |

| PARAM Invalid                     | \$A1        | NACK     |

| Address Invalid                   | \$A2        | NACK     |

| Length Invalid                    | \$A3        | NACK     |

| Access Denied (Write Not Allowed) | \$BA        | NACK     |

| Memory Access Error               | \$EE        | ACK/NACK |

Table 4-23.

Status Codes returned in the Write System Zone response for Fuse Writes

| Error/Status Message                   | Status Code | Туре     |

|----------------------------------------|-------------|----------|

| Fuse Byte (Successful Fuse Byte Write) | fuse byte   | ACK      |

| Fuse Address Invalid                   | \$A2        | NACK     |

| Password Required                      | \$D9        | NACK     |

| Fuse Access Denied                     | \$DF        | NACK     |

| Access Denied (Fuse Order Incorrect)   | \$E9        | NACK     |

| Memory Access Error                    | \$EE        | ACK/NACK |

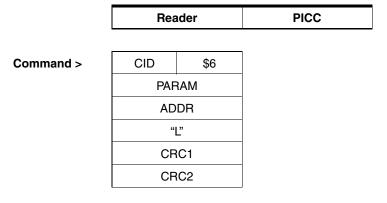

## 4.13 Read System Zone Command [\$c6]

The System Read command allows reading of system data from the configuration memory, from the security fuses, or from the checksum register.

Echo Command >

CID

\$6

FAILURE RESPONSE

NACK

< Error Code</td>

CRC1

CRC2

Echo Command >

### 4.13.1 Operation

The Read System Zone command reads from the devices configuration memory. The data byte address is internally incremented as each byte is read from the memory. If the data byte address increments into a segment where read access is forbidden, the "fuse byte" is transmitted in place of the forbidden data.

Depending on the value of the PARAM byte, the host may read the data in the configuration memory, the fuses, or a checksum. Only PICCs in the Active State are permitted to answer this command.

#### 4.13.2 Command Field Descriptions

CID: The Card ID assigned by the ATTRIB command.

**PARAM:** The PARAM byte selects the type of read operation to be performed.

**Table 4-24.** PARAM byte options for the Read System Zone command

| Command                            | PARAM | ADDR    | "L"            |  |  |

|------------------------------------|-------|---------|----------------|--|--|

| Read System Zone                   | \$00  | address | # of bytes - 1 |  |  |

| Read Fuse Byte                     | \$01  | \$FF    | \$00           |  |  |

| Read Checksum \$02 \$FF \$01       |       |         |                |  |  |

| All Other Values Are Not Supported |       |         |                |  |  |

**ADDR:** The starting address of the data to read.

L: The number of bytes to read minus 1. L cannot exceed 240 bytes.

Reading more than 64 bytes in a single operation is not recommended. In a typical application environment, optimal transaction time is achieved by reading no more than 32 bytes in a single operation.

CRC: Communication error detection bytes.

### 4.13.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**DATA:** The data bytes read from the configuration memory.

Since access rights vary throughout the system zone, the host may provide an authorized starting address, but a length that causes the device to reach forbidden data. In this case, the device will transmit the authorized bytes, but unauthorized bytes will be replaced by the "fuse byte". An "Access Denied" status code \$BA or \$BC will be returned to indicate that some of the bytes returned were replaced by the "fuse byte".

**Figure 4-5.** Coding of the data byte received when reading the fuse byte

| F 7 | F6  | F 5 | F 4 | F 3 | F 2 | F 1 | F0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RFU | RFU | RFU | RFU | SEC | PER | CMA | FAB |

When the Read Fuse Byte option is activated, only a single data byte is returned. When the Read Checksum option is activated, two bytes are returned.

**ACK:** Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

CRC: Communication error detection bytes.

### 4.13.4 Error Handling

If a Read System Zone command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response..

Table 4-25. Status Codes returned in the Read System Zone response

| Error/Status Message                   | Status Code | Туре     |

|----------------------------------------|-------------|----------|

| No Errors                              | \$00        | ACK      |

| PARAM Invalid                          | \$A1        | NACK     |

| Address Invalid                        | \$A2        | NACK     |

| Length Invalid                         | \$A3        | NACK     |

| Byte Access Denied (Read Not Allowed)  | \$BA        | ACK/NACK |

| Byte Access Denied (Password Required) | \$BC        | ACK/NACK |

| Memory Access Error                    | \$EE        | ACK/NACK |

# 4.14 Verify Crypto Command [\$c8]

The Verify Crypto command is used in the Authentication mode and the Encryption mode only. See the document *CryptoRF Specification Addendum for Secure Applications* for information.

## 4.15 Send Checksum Command [\$c9]

The Send Checksum command is used in the Authentication mode and the Encryption mode only. See the document *CryptoRF Specification Addendum for Secure Applications* for information.

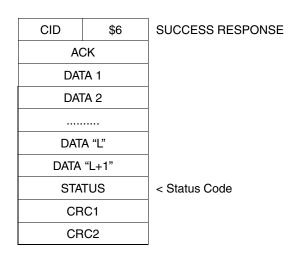

## 4.16 DESELECT Command [\$cA]

The DESELECT command places a PICC in the Halt State.

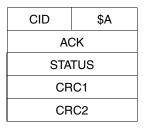

Echo Command >

### 4.16.1 Operation

Sending the DESELECT command (with a matching CID) to a PICC in the Active State places the PICC in the Halt State. The User Zone, password, and authentication registers are cleared before the PICC enters the Halt State. Only PICCs in the Active State are permitted to answer this command.

### 4.16.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

CRC: Communication error detection bytes.

### 4.16.3 Response Field Descriptions

CID: The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

#### 4.16.4 Error Handling

42

If a DESELECT command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

**Table 4-26.** Status Codes returned in the DESELECT response

| Error/Status Message | Status Code | Туре |

|----------------------|-------------|------|

| No errors            | \$00        | ACK  |

## 4.17 IDLE Command [\$cB]

The IDLE command resets the PICC and places it in the Idle State.

Echo Command >

### 4.17.1 Operation

Sending the IDLE command (with a matching CID) to a PICC in the Active State resets the PICC and places it in the Idle State. The User Zone, password, and authentication registers are cleared before the PICC enters the Idle State. The PICC responds only to successful IDLE commands. Only PICCs in the Active State are permitted to answer this command.

### 4.17.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

CRC: Communication error detection bytes.

### 4.17.3 Response Field Descriptions

CID: The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

STATUS: PICC status code.

**CRC:** Communication error detection bytes.

### 4.17.4 Error Handling

If an IDLE command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response.

**Table 4-27.** Status Codes returned in the IDLE response

| Error/Status Message | Status Code | Туре |

|----------------------|-------------|------|

| No errors            | \$00        | ACK  |

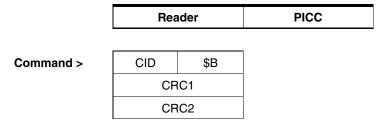

## 4.18 Check Password Command [\$cC]

The Check Password command transmits a password for validation.

|           | Reader |          | PICC |

|-----------|--------|----------|------|

|           |        |          |      |

| Command > | CID    | \$C      |      |

|           | Passwo | rd Index |      |

|           | PV     | V 1      |      |

|           | PV     | V 2      |      |

|           | PV     | V 3      |      |

|           | CR     | IC1      |      |

|           | CR     | IC2      |      |

|           |        |          |      |

Echo Command >

| CID \$C  |  |  |

|----------|--|--|

| ACK/NACK |  |  |

| STATUS   |  |  |

| CRC1     |  |  |

| CRC2     |  |  |

#### 4.18.1 Operation

To read or write data in User Zones that require a password for access the host must carry out a password validation operation. The host uses the Check Password command to send the password for validation against the password selected with the Password Index byte. Only PICCs in the Active State are permitted to answer this command.

If the Check Password is successful, the Password Attempts Counter (PAC) is cleared and the ACK response is issued. Only one password is active at any time. If the Check Password fails, the PAC is incremented and a NACK response is issued. The Check Password success or failure is memorized and active until the PICC is powered down, removed from the Active state, or until a new Check Password is received. If the password trials limit is reached, subsequent Check Password commands will be rejected.

### 4.18.2 Command Field Descriptions

**CID:** The Card ID assigned by the ATTRIB command.

**Password Index:** Identifies the password register that the PICC will check the transmitted password against.

Table 4-28. Coding of the Password Index for 1K, 2K, and 4K bit CryptoRF devices

| Password Index                     | Check Password   |  |

|------------------------------------|------------------|--|

| \$10                               | Password Read 0  |  |

| \$11                               | Password Read 1  |  |

| \$12                               | Password Read 2  |  |

| \$17                               | Password Read 7  |  |

| \$00                               | Password Write 0 |  |

| \$01                               | Password Write 1 |  |

| \$02                               | Password Write 2 |  |

| \$07                               | Password Write 7 |  |

| All Other Values Are Not Supported |                  |  |

.

Table 4-29. Coding of the Password Index for 8K bit and larger CryptoRF devices

| Password Index Check Passwor       |                  |  |

|------------------------------------|------------------|--|

| \$10                               | Password Read 0  |  |

| \$11                               | Password Read 1  |  |

| \$12                               | Password Read 2  |  |

| \$13                               | Password Read 3  |  |

| \$14                               | Password Read 4  |  |

| \$15                               | Password Read 5  |  |

| \$16                               | Password Read 6  |  |

| \$17                               | Password Read 7  |  |

| \$00                               | Password Write 0 |  |

| \$01                               | Password Write 1 |  |

| \$02                               | Password Write 2 |  |

| \$03                               | Password Write 3 |  |

| \$04                               | Password Write 4 |  |

| \$05                               | Password Write 5 |  |

| \$06                               | Password Write 6 |  |

| \$07                               | Password Write 7 |  |

| All Other Values Are Not Supported |                  |  |

PW: The password bytes.

CRC: Communication error detection bytes.

### 4.18.3 Response Field Descriptions

**CID:** The PICC transmits it's assigned card ID in the response.

**ACK:** Acknowledge, the command executed correctly.

**NACK:** Not Acknowledge, the command did not execute correctly.

STATUS: PICC status code.

CRC: Communication error detection bytes.

### 4.18.4 Error Handling

If a Check Password command containing transmission errors is received by the PICC, it is ignored and no response is send. The PICC reports errors in the status byte of the response..

Table 4-30. Status Codes returned in the Check Password response

|                                          | 1           |          |

|------------------------------------------|-------------|----------|

| Error/Status Message                     | Status Code | Туре     |

| No errors                                | \$00        | ACK      |

| Password Index Invalid                   | \$A1        | NACK     |

| Check Password Failure                   | \$D9        | NACK     |

| Memory Access Error (Security Operation) | \$F9        | NACK     |

| Memory Access Error                      | \$EE        | ACK/NACK |

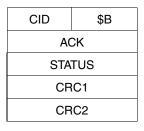

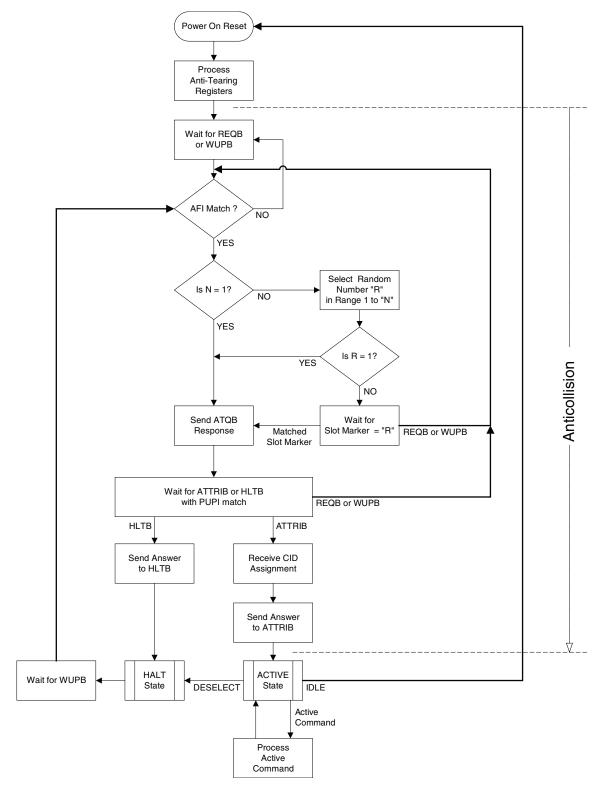

## 5. Transaction Flow

Figure 5-1. Flowchart of a Typical CryptoRF Transaction

In a typical CryptoRF transaction the host performs anticollision, selects a User Zone, and reads or writes the user memory. When a User Zone requires a password, authentication, or encryption the host performs the required security operation before accessing the User Zone. Note that the Set User Zone command may be sent before or after the security operation.

## 6. Absolute Maximum Ratings\*

\* NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Absolute Maximum Rating          |                 |

|----------------------------------|-----------------|

| Operating Temperature (junction) | -40°C to +85°C  |

| Storage Temperature (ambient)    | -65°C to +150°C |

| HBM ESD (Antenna Pins only)      | 2000V minimum   |

The maximum temperature ratings in this section are applicable to CryptoRF in wafer form. When assembled into a package the CryptoRF temperature ratings may be reduced to reflect the limitations of the package. However the CryptoRF absolute maximum ratings should not be exceeded for any package.

# 7. Reliability

| Parameter                    | Min       | Тур | Max         | Units        |

|------------------------------|-----------|-----|-------------|--------------|

| Write Endurance (each Byte)  | 100,000   |     |             | Write Cycles |

| Anti-Tearing Write Endurance | 50,000    |     |             | Writes       |

| Data Retention (at 55°C)     | 10        |     |             | Years        |

| Data Retention (At 35°C)     | 30        | 50  |             | Years        |

| Read Endurance               | Unlimited |     | Read Cycles |              |

CryptoRF is fabricated with Atmel's high reliability CMOS EEPROM manufacturing technology. The write endurance and data retention EEPROM reliability ratings apply to each byte of the user and configuration memory.

The optional CryptoRF anti-tearing functions use a single anti-tearing EEPROM buffer memory. Every anti-tearing write operation utilizes the same buffer. The anti-tearing write endurance specification is a limitation in the total number of anti-tearing write operations that can be performed by each die.

## 8. Electrical Characteristics

| Symbol              | Parameter                                          | Min | Normal | Max | Units |