## High Power SPDT Switch with Logic Control

# CXG1134AEN

## Description

The CXG1134AEN is a high power and high Isolation SPDT switch MMIC. This IC can be used in wireless communication systems. The CXG1134AEN can be operated by one CMOS control line. The Sony GaAs J-FET process is used for low insertion loss and on-chip logic circuit. (Applications : Cellular handsets ; PDC, CDMA)

#### Features

- ♦ Low insertion loss : 0.25dB @900MHz, 0.35dB @1.9GHz

- ◆ High linearity : IIP3 (typ.) = 70dBm

- ◆ 1 CMOS compatible control line

- Small package size : 10-pin VSON

#### Package

10 pin VSON (Plastic)

## Structure

GaAs J-FET MMIC

## **Absolute Maximum Ratings**

(Ta = 25°C)

| <ul> <li>Bias voltage</li> </ul>          | Vdd  | 7             | V  |

|-------------------------------------------|------|---------------|----|

| <ul> <li>Control voltage</li> </ul>       | Vctl | 5             | V  |

| <ul> <li>Operating temperature</li> </ul> | Topr | – 35 to + 85  | °C |

| <ul> <li>Storage temperature</li> </ul>   | Tstg | – 65 to + 150 | °C |

This IC is ESD sensitive device. Special handling precautions are required.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

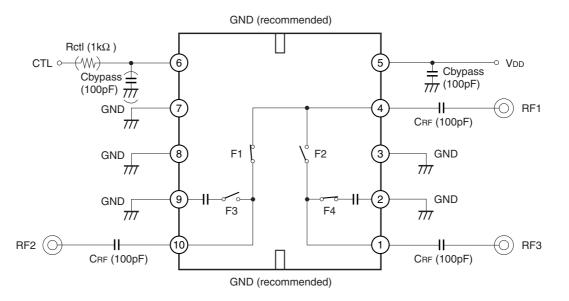

## **Block Diagram and Recommended Circuit**

When using this IC, the following external parts should be used :

- Rctl : This resistor is used to improve ESD performance.  $1k\Omega$  is recommended.

- CRF : This capacitor is used for RF de-coupling and must be used for all applications. 100pF is recommended.

Cbypass : This capacitor is used for DC line filtering. 100pF is recommended.

#### Truth Table

| On Pass   | CTL | F1  | F2  | F3  | F4  |

|-----------|-----|-----|-----|-----|-----|

| RF1 – RF2 | Н   | ON  | OFF | OFF | ON  |

| RF1 – RF3 | L   | OFF | ON  | ON  | OFF |

### **DC Bias Condition**

(Ta = 25°C)

| Item     | Min. | Тур. | Max. | Unit |

|----------|------|------|------|------|

| Vctl (H) | 2.2  | 3.0  | 3.6  | V    |

| Vctl (L) | 0    |      | 0.4  | V    |

| Vdd      | 2.7  | 3.0  | 3.6  | V    |

## **Electrical Characteristics**

| ٦)  | Га | = | 25°C) | ) |

|-----|----|---|-------|---|

| ( ) | а  | - | 250)  | / |

| Item                        | Symbol | Condition                | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|--------------------------|------|------|------|------|

| Insertion loss              | IL     | 900MHz                   |      | 0.25 | 0.50 | dB   |

| Isolation                   | ISO.   | 900MHz                   | 28   | 32   |      | dB   |

| VSWR                        | VSWR   | 900MHz                   |      | 1.2  | 1.4  | _    |

| Harmonics                   | 2fo    | *1                       |      | - 75 | - 60 | dBc  |

| namonics                    | 3fo    | *1                       |      | - 75 | - 60 | dBc  |

| 1dB compression input power | P1dB   | VDD = 3.0V, 0/3V control | 32   | 35   |      | dBm  |

| Switching speed             | TSW    |                          |      | 2    | 5    | μs   |

| Control current             | Ictl   | Vctl (High) = 3V         |      | 10   | 30   | μΑ   |

| Bias current                | Idd    | VDD = 3V                 |      | 50   | 100  | μΑ   |

<sup>\*1</sup> Pin = 30dBm, 900MHz, VDD = 3.0V, 0/3V control

## Package Outline

(Unit : mm)

**10PIN VSON(PLASTIC)** + 0.1 0.8 - 0.05 0.6 2.5 □ 0.05 S A S  $0.35 \pm 0.1$ 10 6 ШЦ  $0.5 \pm 0.2$ 2.5 2.7 Π Π PIN 1 INDEX 5 В 0.4 <u>x2</u>  $0.35 \pm 0.1$ □0.15 S B 0.8 0.15 S A B  $0.225 \pm 0.03$ 0.05 M S AB  $0.2 \pm 0.01$ 0.03 ± 0.03 (Stand Off) Λ Solder Plating  $0.13 \pm 0.025$ + 0.09 0.14 - 0.03 TERMINAL SECTION NOTE:1) The dimensions of the terminal section apply to the

ranges of 0.1mm and 0.25mm from the end of a terminal.

PACKAGE STRUCTURE

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | COPPER ALLOY   |

| PACKAGE MASS     | 0.013g         |

#### LEAD PLATING SPECIFICATIONS

| ITEM               | SPEC.           |

|--------------------|-----------------|

| LEAD MATERIAL      | COPPER ALLOY    |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |

| PLATING THICKNESS  | 5-18µm          |

P

| SONY CODE  | VSON-10P-01 |

|------------|-------------|

| EIAJ CODE  |             |

| JEDEC CODE |             |